Automatyzacja i robotyzacja

procesów produkcyjnych

Instrukcja laboratoryjna

Technika cyfrowa

Opracował: mgr inż. Krzysztof Bodzek

Cel ćwiczenia.

Celem ćwiczenia jest zapoznanie studenta z zapisem liczb stosowanym w układach

cyfrowych. Ponadto przedstawienie podstawowych elementów wykorzystywanych w

elektronice:

bramek cyfrowych – AND, NAND, NOT, OR, NOR

sposobów minimalizacji funkcji logicznej – algebra boola

przerzutników – SR, JK

Wprowadzenie.

Układy cyfrowe wykorzystywane są praktycznie w każdej dziedzinie związanej

z automatyzacją procesów sterowania. Na korzyść układów cyfrowych w porównaniu z

układami analogowymi przemawia przede wszystkim większa odporność na zakłócenia, brak

wpływu starzenia się elementów, większe możliwości i większa elastyczność.

Zapis liczb stosowany w technice cyfrowej

W technice cyfrowej najczęściej stosowane są dwa rodzaje zapisu liczb: binarny oraz

szesnastkowy.

Zapis binarny to suma kolejnych potęg liczby dwa z odpowiednimi wagami przy

poszczególnych potęgach. Dla przykładu liczba 145 przedstawiona w dwóch systemach:

107=1*10

2

+0*10

1

+7*10

0

107d= 1*2

6

+1 *2

5

+0*2

4

+1*2

3

+1*2

2

+1*2

1

+1*2

0

=1101011b

Pojedyncza liczba 1 lub 0 to bit informacji. W praktyce stosuje się grupowanie w 8, 16, 32 itd.

bitowe liczby. 8 bitowa liczba nazywana jest bajtem. Dla przykładu liczba 102 zapisana jako

bajt informacji: 01101011b.

Idea zapisu szesnastkowego jest bardzo podobna do przedstawionych powyżej

zapisów z tym, że podstawą potęgi jest liczba 16. A współczynniki przy potęgach przyjmują

wartości: 0-9 oraz A-10, B-11, C-12, D-13, E-14, F-15. W praktyce stosuję się grupowanie po

cztery bity liczb w systemie dwójkowym, i tak:

107d= 0110 1011 b

107d=6

B

h

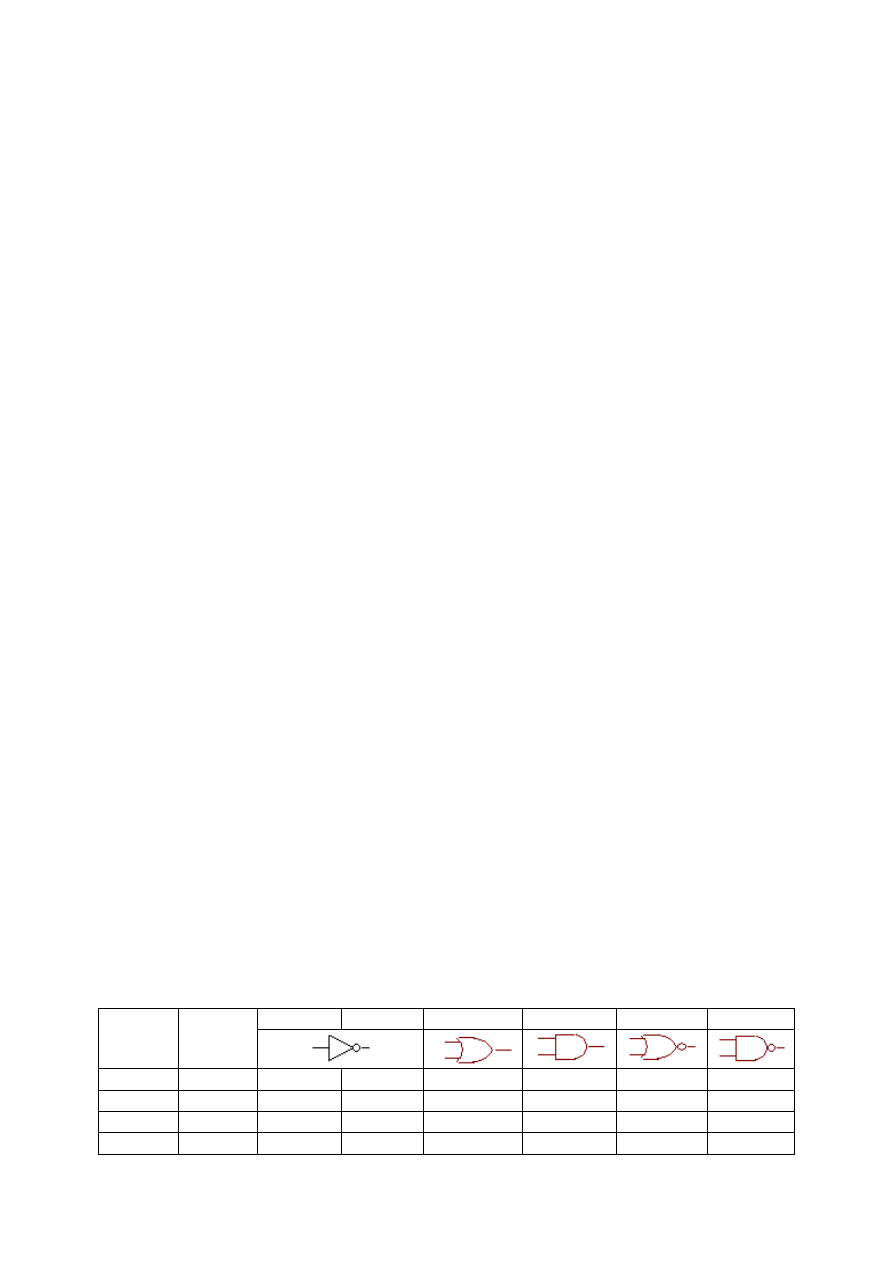

Bramki logiczne

Bramka logiczne to elementy, zazwyczaj układu scalone, pozwalające realizować

prostą funkcję logiczną, której argumenty i wynik mogą przybierać wartości 1 (stan wysoki)

lub 0 (stan niski). Podstawowe bramki logiczne realizują funkcję sumy (OR), iloczynu (AND)

i negacji (INV). Dodatkowo wykorzystuje się dwie bramki będące negacją sumy (NOR) oraz

negacją iloczynu (NAND). Tablica prawdy bramek logicznych przedstawiona jest poniżej:

A

B

INVA

INV B

OR

AND

NOR

NAND

0

0

1

1

0

0

1

1

0

1

1

0

1

0

0

1

1

0

0

1

1

0

0

1

1

1

0

0

1

1

0

0

Podstawowe prawa algebry Boole’a

W celu minimalizacji ilości bramek cyfrowych należy się posługiwać

wzoramiobowiązującymi w logice dwuwartościowej. Poniżej zestawione zostały podstawowe

zależności:

a+b = b+a

a*b = b*a

a*(b+c) = a*b + a*c

a+b*c = (a+b)*(a+c)

(a+b)+c = a+(b+c)

(a*b)*c = a*(b*c)

a+0 = a

a*1 = a

a+1 = 1

a*0 = 0

a+a = a

a*a = a

a+͞a=1

a

∗͞a=0

Prawa de Morgana

͞a͞+͞b=͞a*͞b

͞a͞*͞b=͞a+͞b

Wykorzystanie algebry Boole’a zostało przedstawione poniżej.

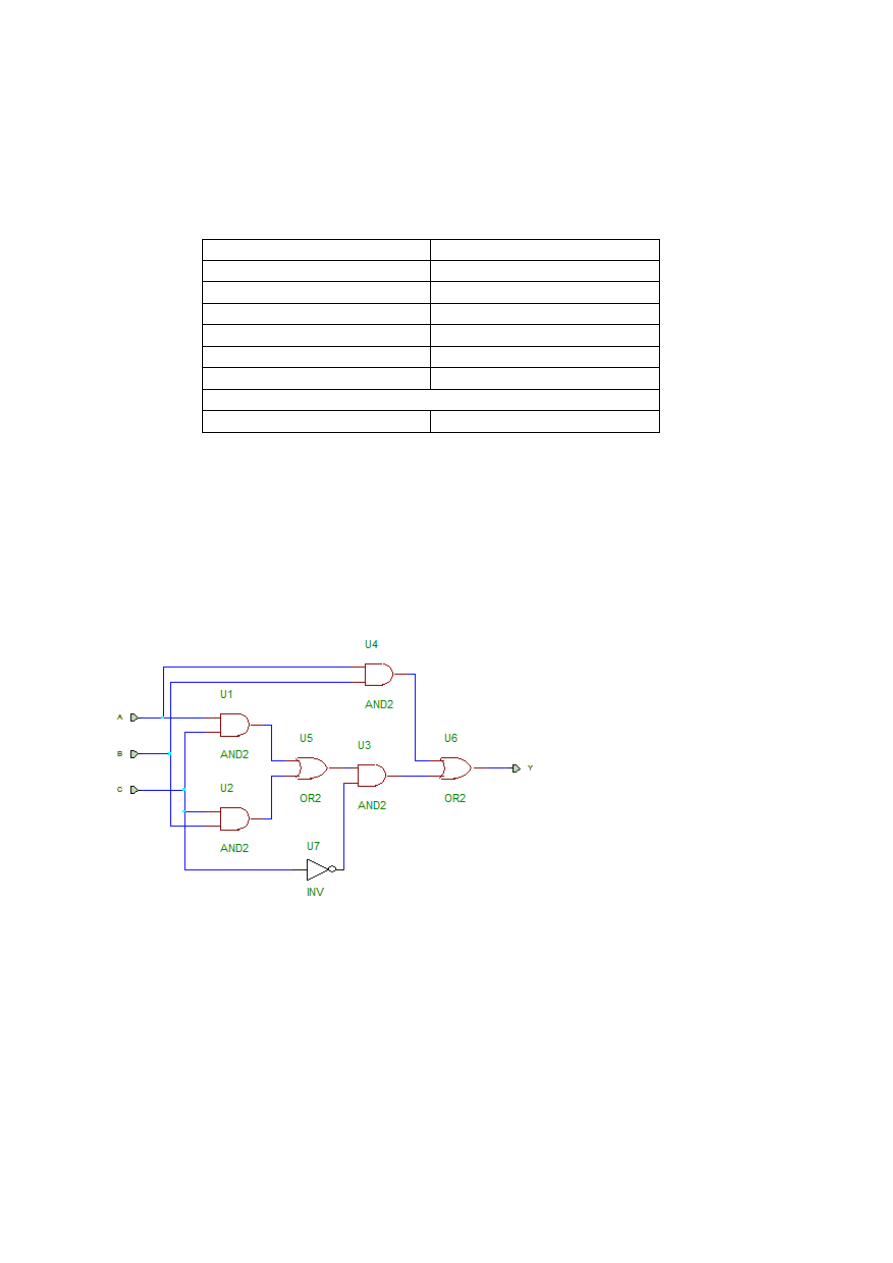

Realizowana funkcja logiczna ma postać:

Y=(a*c+b*c)*͞c+a*b

Realizacja funkcji Y została przedstawiona na poniższym schemacie:

Korzystając z algebry Boole’a można funkcję uprościć:

Y=(a*c+b*c)*͞c+a*b=(a+b)*c*͞c+a*b=(a+b)*0+a*b=a*b

Przedstawiona funkcja uprościła się do iloczynu logicznego Y=a*b. Obydwie postacie funkcji

logicznej są sobie równoważne.

Przerzutniki

Na ćwiczeniach zapoznamy się z dwoma rodzajami przerzutników: asynchronicznym

SR oraz synchronicznym JK. Są to najczęściej

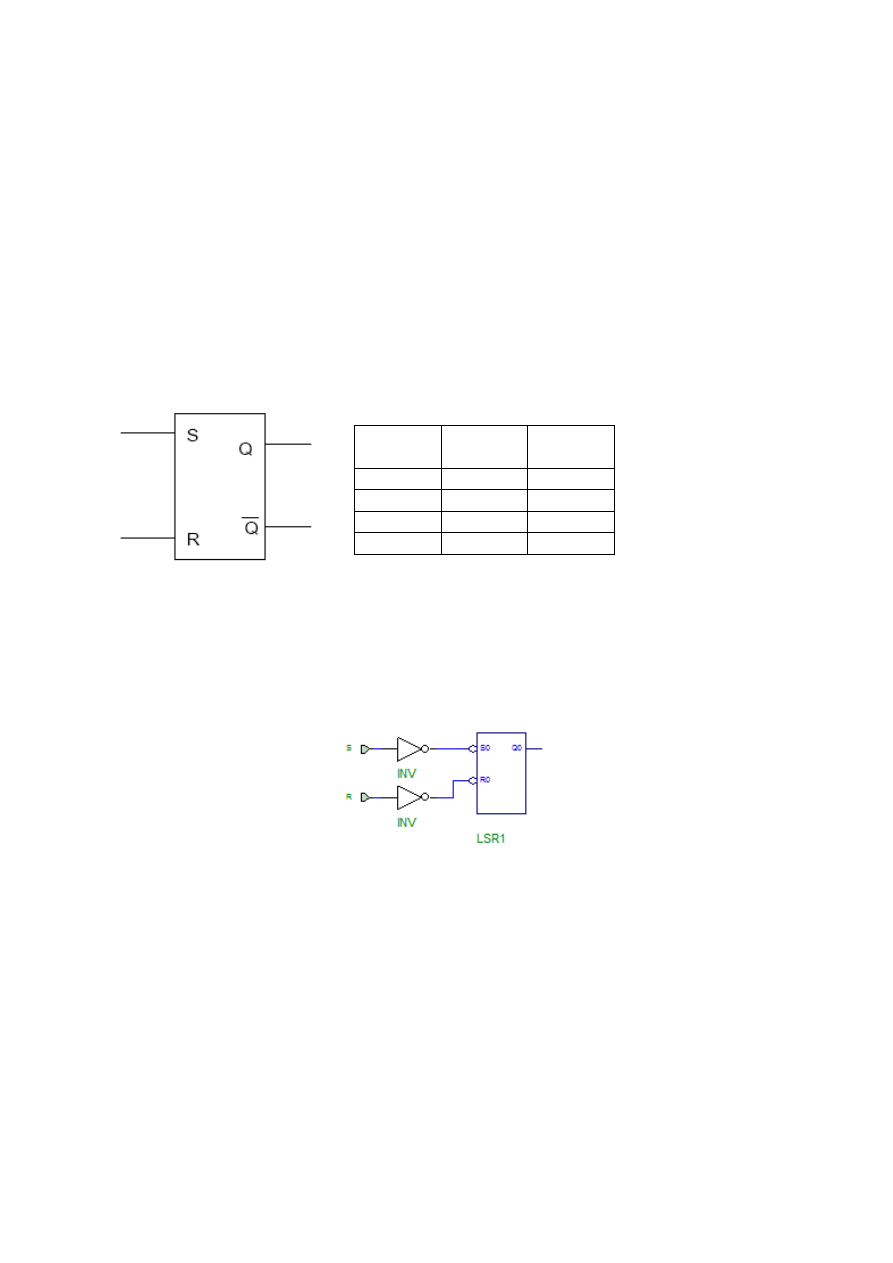

Przerzutnik SR

Przerzutnik SR posiada dwa wejścia: ustawiające S (Set) oraz kasujące R (Reset). Na

wyjściu przerzutnika SR pojawia się sygnał wysoki w momencie podania sygnału wysokiego

na wejście S. Sygnał ten jest utrzymywany do momentu podania sygnału wysokiego na

wejście R. Przerzutnik ten może być traktowany jak podstawowa komórka pamięci. Poniżej

znajduje się symbol przerzutnika oraz tablica prawdy.

W bibliotece oprogramowania Active-CAD występuje przerzutnik typu RS z zanegowanymi

wejściami (symbol LSR1), w którym sygnałami aktywnymi są sygnały na poziomie niskim

(logiczny stan 0). Aby przerzutnik ten działał zgodnie z przedstawioną powyżej tablicą

prawdy na jego wejściach muszą znaleźć się dwa inwertery, co pokazano na rysunku.

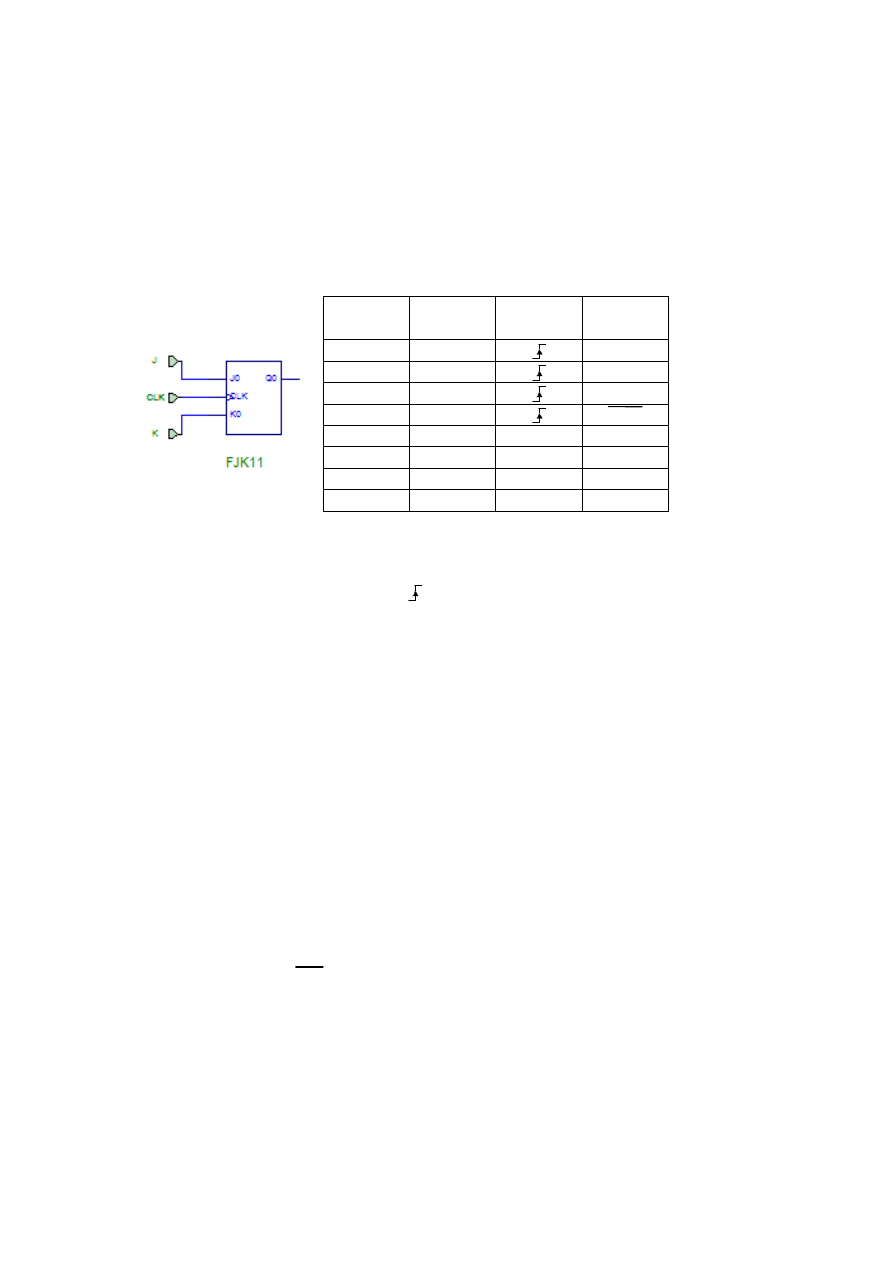

Przerzutnik JK

Przerzutnik JK jest układem trójwejściowym o wejściu zegarowym CLK (ang. Clock)

i dwóch wejściach danych: wejściu ustawiającym J i wejściu kasującym K. Przerzutnik ten w

zależności od stanów sygnałów na wejściach J i K zachowuje się w następujący sposób:

wejścia J = 0, K = 0 – przerzutnik jest w stanie pamiętania,

wejście J = 1, K = 0 –przerzutnik ustawia wyjście Q w stan 1,

wejście J = 0, K = 1 –przerzutnik ustawia wyjście Q w stan 0,

wejście J = 1, K = 1 – przerzutnik neguje sygnał wyjściowy.

Zmiany na wyjściu przerzutnika JK następują synchronicznie ze zboczem narastającym

sygnału na wejściu CLK, po czym przerzutnik utrzymuje stan wyjściowy aż do chwili

pojawienia się kolejnego zbocza narastającego w sygnale wejściowym. Przypadek, w którym

S

R

Q

0

0

Q

n-1

0

1

0

1

0

1

1

1

X

oba wejścia J i K są w stanie wysokim, jest najczęściej wykorzystywany w praktyce. W tym

stanie przerzutnik neguje sygnał wyjściowy przy każdym zboczu narastającym sygnału

zegarowego. Dzięki temu częstotliwość sygnału wyjściowego jest dwukrotnie niższa niż

częstotliwość sygnału wejściowego. Łącząc szeregowo przerzutniki JK uzyskuje się układy

pozwalające na dzielenie częstotliwości sygnału wejściowego oraz tworzenie układów

zliczających liczbę impulsów wejściowych.

Na rysunku pokazano przerzutnik JK, dostępny w bibliotece programu Active-CAD – symbol

FJK11 oraz jego tablicę prawdy. Symbol oznacza zbocze narastające sygnału zegarowego,

natomiast (-) oznacza inne stany wejścia zegarowego.

Przebieg ćwiczenia.

Student wykonuje kolejno zadania:

Zadanie 1.

Korzystając z programu ActiveCAD wyznaczyć tablicę prawdy następujących funkcji

logicznych:

Y=a+b*͞c

Y=( ͞a͞*͞b)+c

Zadanie 2.

Uprościć funkcje logiczne korzystając z praw algebry Boole’a:

Y = (a+b)*c+b*c+a

Y = a+b(c+͞b)+a*͞b

Zadanie 3.

Zaprojektować i przetestować 2-bitowy licznik impulsów korzystając z przerzutników JK:

zliczający w dół

zliczający w górę

S

R

CLK

Q

0

0

Q

n-1

0

1

0

1

0

1

1

1

Q

n-1

0

0

(-)

Q

n-1

0

1

(-)

Q

n-1

1

0

(-)

Q

n-1

1

1

(-)

Q

n-1

Zadanie 4.

Korzystając z gotowego licznika binarnego 4-bitowego zliczającego w górę CBU14,

zaprojektować i przetestować działanie licznika dziesiętnego. Na wyjściu licznika

dziesiętnego pojawiają się liczby od 0-9.

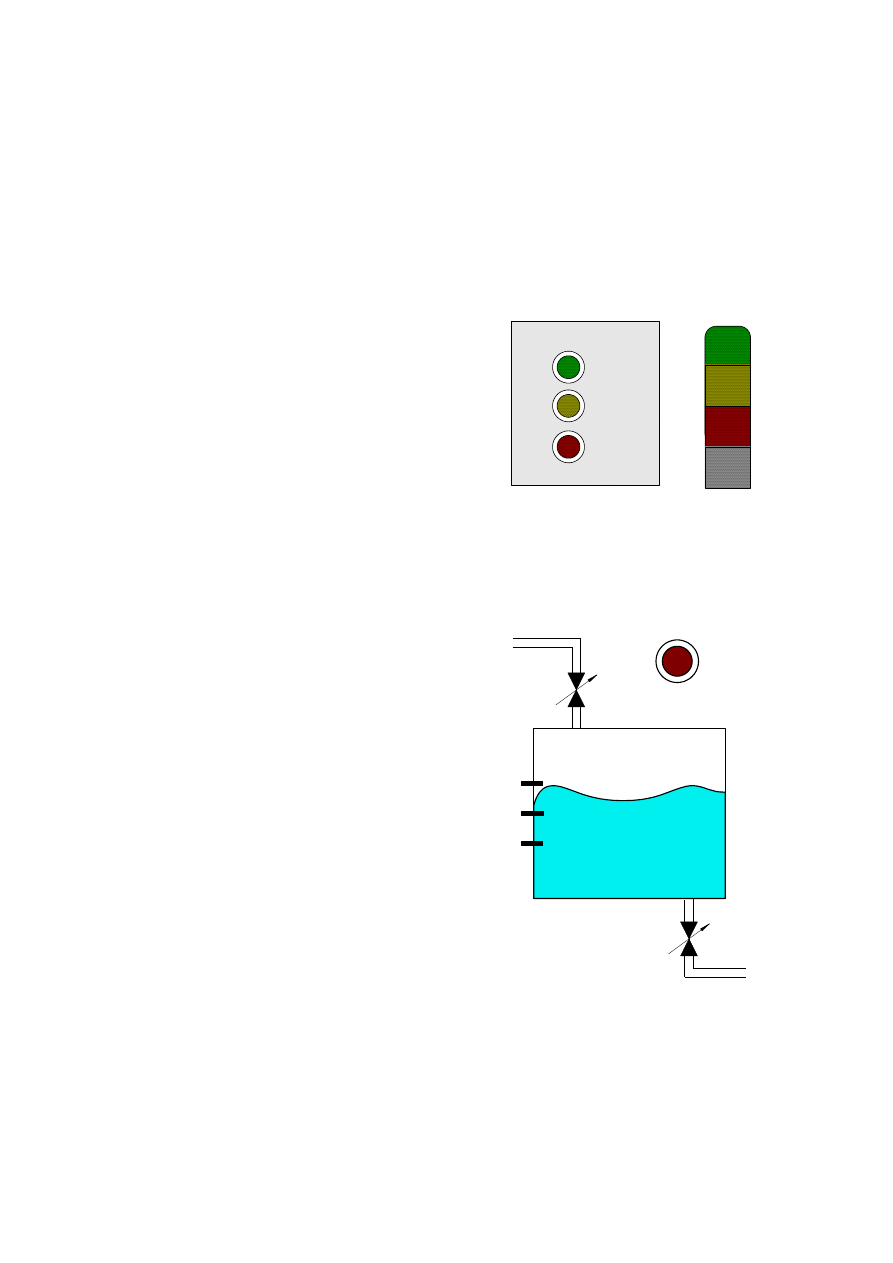

Zadanie 5.

Zaprojektować układ wyboru rodzaju pracy układu napędowego. Układ napędowy może

pracować w trzech stanach:

praca automatyczna – aktywne jest wyjście

Q1oraz zielona lampka stanu pracy W1

praca ręczna – aktywne jest wyjście Q2 oraz

żółta lampka stanu pracy W2

stop – wyjścia Q1 oraz Q2 są nieaktywne.

Aktywna jest czerwona lampka stanu pracy W3

Przyciski stanu pracy A, B, C są przyciskami astabilnymi (informacja o ich naciśnięciu jest

tracona z chwilą oderwania palca od przycisku).

Zadanie 6.

Zaprojektować

układ

sterowania

napełnianiem basenu kąpielowego. Dopływ

wody do basenu jest sterowany zaworem Q1.

Zawór Q2 to spust wody. Lustro wody powinno

być

utrzymane

pomiędzy

poziomami

maksymalnym i minimalny. W tym przypadku

zawory Q1 oraz Q2 powinny być otwarte w celu

wymiany wody. Dodatkowo sprawdzana jest

poprawność działania czujników poziomu wody.

W przypadku błędnego działania czujników (np.

A=1, B=0) woda powinna być wylana z basenu

a awaria sygnalizowana lampką Q3.

Automatyczna

Ręczna

Stop

A

B

C

W1

W2

W3

A

B

C

Q1

Q2

awaria

Q3

Zaliczenie ćwiczenia.

Warunkiem zaliczenia jest wykonanie co najmniej 3 zadań znajdujących się w niniejszej

instrukcji. Zaliczający powinien umieć uprościć funkcję logiczną korzystając z algebry

Boole’a oraz zrealizować ją za pomocą podstawowych elementów logicznych. Ponadto znać

zasadę działania przerzutników SR oraz JK. Umieć wykorzystać przerzutniki do

zaprojektowania układów pamiętających oraz liczących.

Wyszukiwarka

Podobne podstrony:

Podstawy Robotyki lab3 id 36832 Nieznany

AKiSO lab3 id 53767 Nieznany

Lab3 9 id 259553 Nieznany

JPPO Lab3 id 228822 Nieznany

PAiRAII Instr 2008 lab3 id 3455 Nieznany

Podstawy Robotyki lab3 id 36832 Nieznany

AKiSO lab3 id 53767 Nieznany

BD 1st 2 4 lab3 tresc 1 1 id 81 Nieznany

lab3 Instrukcja P3 id 750620 Nieznany

LAB3 Sw i zast OFT doc id 10525 Nieznany

lab3 java3 id 750622 Nieznany

Algorytmy Lab3 Tablice id 57743 Nieznany (2)

lab3 sciaga id 259590 Nieznany

Lab3 Linux id 259637 Nieznany

BD 1st 2 4 lab3 tresc 1 1 id 81 Nieznany

Abolicja podatkowa id 50334 Nieznany (2)

4 LIDER MENEDZER id 37733 Nieznany (2)

katechezy MB id 233498 Nieznany

metro sciaga id 296943 Nieznany

więcej podobnych podstron