1

1

Dr inż.. Piotr Dębiec „Układy Logiczne” DM, sem. 3

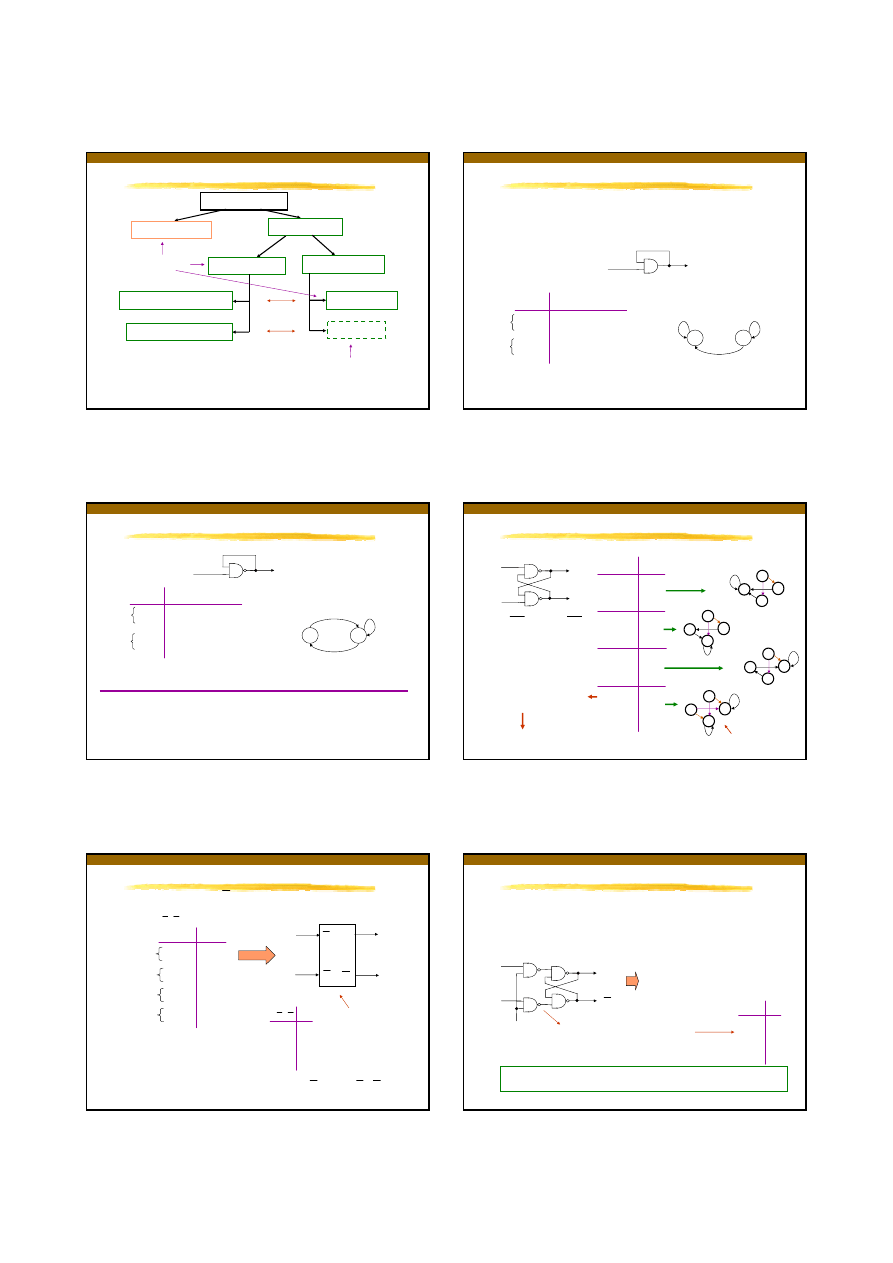

Wstęp do układów sekwencyjnych

Układy logiczne

Kombinacyjne

Sekwencyjne

Asynchroniczne

Synchroniczne

Wyzwalane zboczem

Wyzwalane poziomem

Potencjałowe

Impulsowe

Pytanie 1:

Czym różni się architektura układu sekwencyjnego

od kombinacyjnego ?

bramki impulsowe

bramki standardowe

2

Dr inż.. Piotr Dębiec „Układy Logiczne” DM, sem. 3

Wstęp do układów sekwencyjnych

Odpowiedź:

Występowaniem sprzężeń zwrotnych w połącze-

niach bramek

Pytanie 2:

Jaki ma to wpływ na zachowanie układu ?

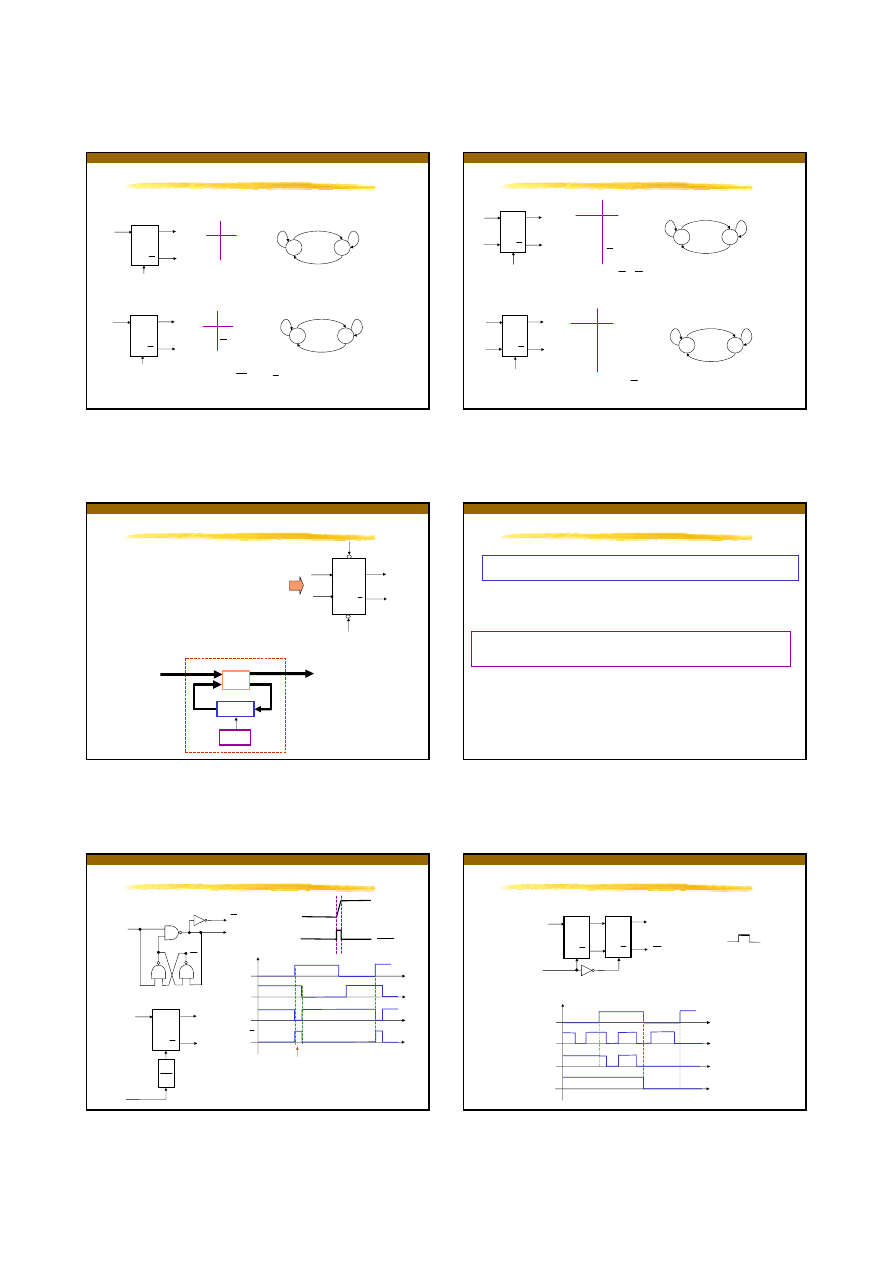

Przykład 1

∆

t

t

x

t

y

t

x

t

y

t

t

t

y

x

y

t

=

∆

+

0

0 0

- AND

0

1 0

- stan niestabilny

1

0 0

- AND

1

1 1

- AND

Zastosowanie:

do

zapamiętania

faktu co najmniej jednokrotnego wystąpienia

zmiany stanu z „1” na „0” na wejściu.

0

1

1

0,1

0

Graf:

układ stabilny

pamiętanie

zerowanie

3

Dr inż.. Piotr Dębiec „Układy Logiczne” DM, sem. 3

Wstęp do układów sekwencyjnych

∆

t

t

x

t

y

Przykład 2

t

x

t

y

t

t

t

y

x

y

t

=

∆

+

0

0 1

- stan niestabilny

0

1 1

- NAND

1

0 1

- stan niestabilny

1

1 0

- stan niestabilny

układ niestabilny dla x=

1

0

1

0

0,1

1

Graf:

ustawianie

oscylacje

Zastosowanie:

brak

3 typy zachowania układów sekwencyjnych:

• niestabilne

(oscylacje)

• kombinacyjne

(zerowanie, ustawianie)

• bistabilne

(pamiętanie)

4

Dr inż.. Piotr Dębiec „Układy Logiczne” DM, sem. 3

Wstęp do układów sekwencyjnych

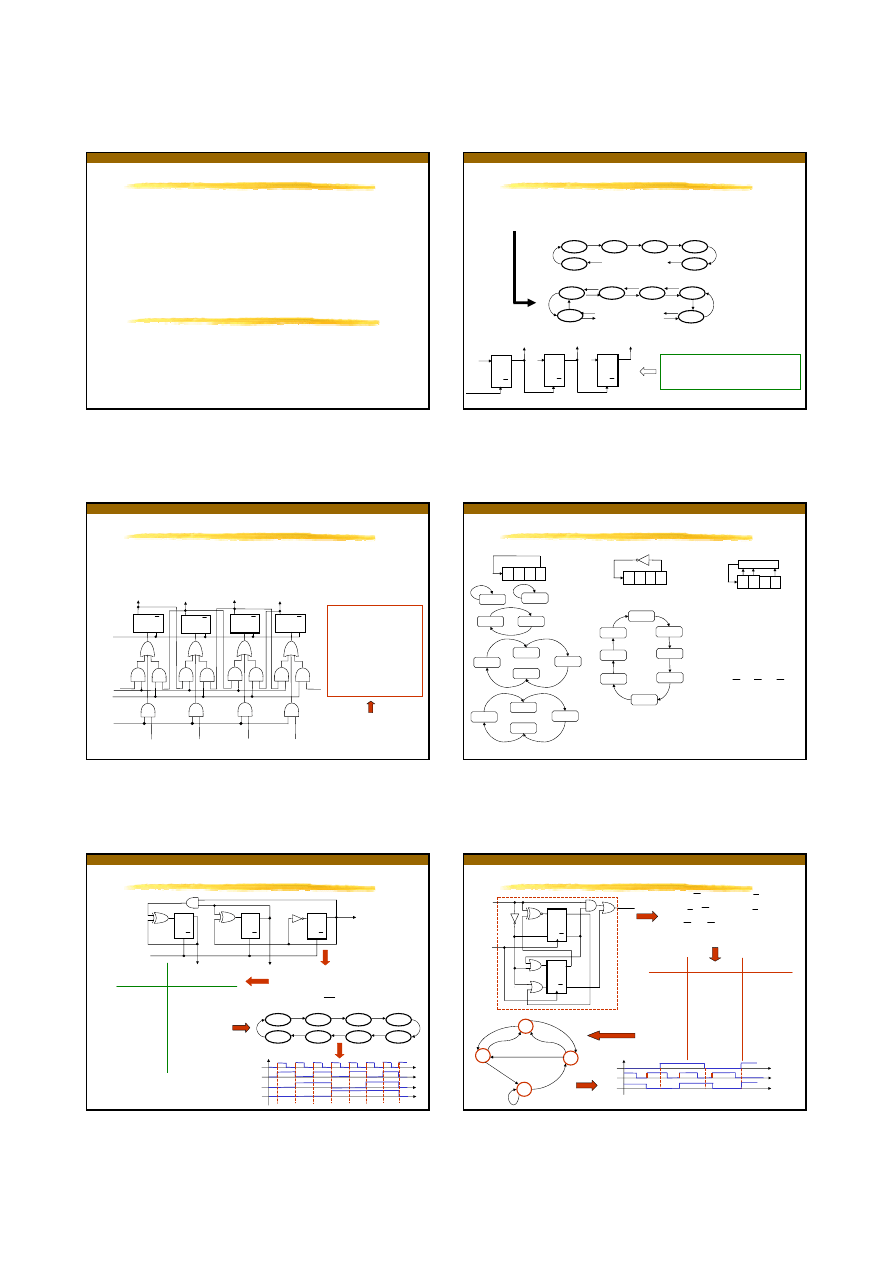

Przykład układu (asynchronicznego) stosowanego w praktyce

t

x

1

t

x

2

t

y

1

t

y

2

t

t

t

y

x

y

2

1

1

1

=

+

t

t

t

y

x

y

1

2

1

2

=

+

t

x

1

t

x

2

t

y

1

1

1

+

t

y

t

y

2

1

2

+

t

y

0 0 0 0 1 1

0 0 0 1 1 1

0 0 1 0 1 1

0 0 1 1 1 1

0 1 0 0 1 1

0 1 0 1 1 1

0 1 1 0 1 0

0 1 1 1 1 0

1 0 0 0 1 1

1 0 0 1 0 1

1 0 1 0 1 1

1 0 1 1 0 1

1 1 0 0 1 1

1 1 0 1 0 1

1 1 1 0 1 0

1 1 1 1 0 0

11

10

00

01

∆

1

>

∆

2

∆

1

<

∆

2

11

10

00

01

∆

1

>

∆

2

∆

1

<

∆

2

∆

1

<

∆

2

11

10

00

01

∆

1

>

∆

2

11

10

00

01

∆

1

>

∆

2

∆

1

<

∆

2

stan następujący po

00

lub

11

nie jest

ściśle określony

nie wolno układu wprowadzać

w stany

y

1

y

2

= 00

i

y

1

y

2

= 11

nie wolno podawać na wejście

stanu

x

1

x

2

= 00

5

Dr inż.. Piotr Dębiec „Układy Logiczne” DM, sem. 3

Wstęp do układów sekwencyjnych

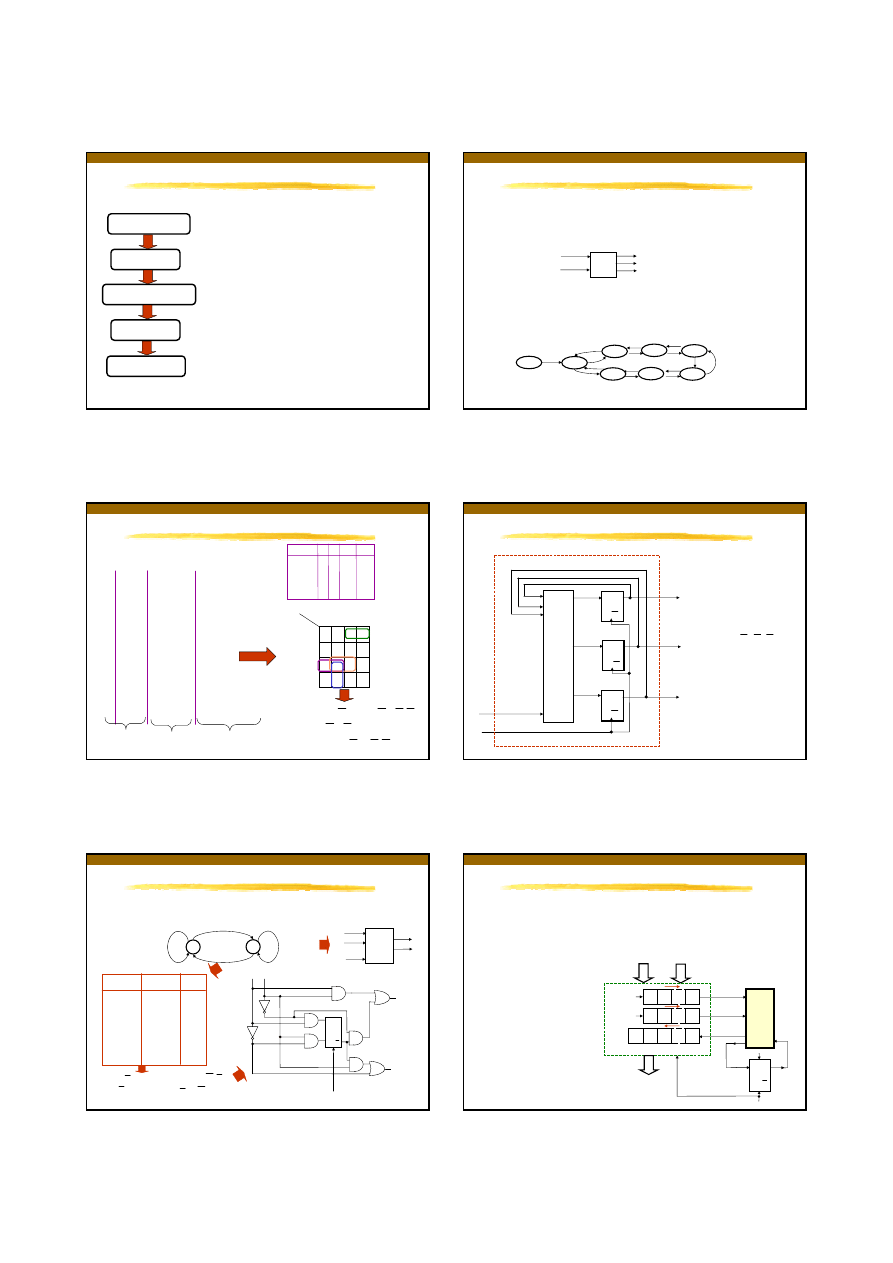

Przy tych założeniach ( ) funkcję układu można opisać przy

użyciu tablicy charakterystycznej:

1

2

y

y

=

t

x

1

t

x

2

1

1

+

t

y

t

y

1

0 0 0

?

0 0 1

?

0 1 0

1

0 1 1

1

1 0 0

0

1 0 1

0

1 1 0

0

1 1 1

1

stan niedozwolony

ustawianie

zerowanie

pamiętanie

1

+

t

t

Q

Q

R

S

skróconej tablicy charakterystycznej:

1

+

t

Q

R

S

0 0 ?

0 1 1

1 0 0

1 1 Q

t

lub równania stanu:

1

,

1

=

+

+

=

+

R

S

S

R

Q

Q

t

t

R

S Q

Q

asynchroniczny

przerzutnik SR (RS)

6

Dr inż.. Piotr Dębiec „Układy Logiczne” DM, sem. 3

Układy sekwencyjne synchroniczne

Wniosek:

nawet proste obwody asynchroniczne są trudne do analizy.

O wiele prościej analizuje się i projektuje układy synchroniczne, których stan

może zmieniać się tylko chwilach czasu, określonych przez tzw.

wejście zegarowe.

negacja powoduje zmianę

sygnału aktywnego na wejściach

z 0 na 1.

1

+

t

Q

R

S

0 0 Q

t

0 1 0

1 0 1

1 1 ?

Jest to synchroniczny przerzutnik RS wyzwalany poziomem wysokim

(„

zatrzask

”, ang.

latch

)

stan przerzutnika może się zmienić

tylko przy wysokim poziomie

logicznym na wejściu CK (CK = 1)

R

S

CK

Q

Q

Zmodyfikujmy układ przerzutnika RS:

2

7

Dr inż.. Piotr Dębiec „Układy Logiczne” DM, sem. 3

Układy sekwencyjne synchroniczne

Typy przerzutników:

D

Q

Q

CK

Przerzutnik typu D

1

+

t

Q

D

0 0

1 1

0

1

1

1

0

0

D

Q

t

=

+1

Przerzutnik typu T

T

Q

Q

CK

1

+

t

Q

T

0

1

t

Q

t

Q

0

1

0

1

1

0

T

Q

T

Q

T

Q

Q

t

t

t

t

⊕

=

+

=

+1

8

Dr inż.. Piotr Dębiec „Układy Logiczne” DM, sem. 3

Układy sekwencyjne synchroniczne

Przerzutnik typu JK

K

J

Q

Q

CK

1

+

t

Q

K

J

0 0

0 1 0

1 0 1

1 1

t

Q

t

Q

0

1

00,10

JK=10,11

01,11

01,00

J

Q

K

Q

Q

t

t

t

+

=

+1

Przerzutnik typu RS

R

S

Q

Q

CK

1

+

t

Q

R

S

0 0

0 1 0

1 0 1

1 1

?

t

Q

0

1

00,10

SR=10

01

01,00

0

,

1

=

+

=

+

RS

R

Q

S

Q

t

t

9

Dr inż.. Piotr Dębiec „Układy Logiczne” DM, sem. 3

Układy sekwencyjne synchroniczne

Każdy przerzutnik może dodatkowo posiadać

asynchroniczne wejścia ustawiające

przerzutnik w stan Q=1 (

PRESET

) oraz Q=0

(

CLEAR

), aktywne w stanie niskim lub

wysokim

Synchroniczne układy sekwencyjne są zbudowane wyłącznie

z

przerzutników

,

bramek

oraz

generatora sygnału zegarowego

.

Y=f(S,X)

→ automat Mealy’ego

Y=f(S)

→ automat Moore’a

D

Q

CK

CLEAR

PRESET

Q

UK- układ kombinacyjny

UK

Pamięć

Zegar

X

S

Z

Y

10

Dr inż.. Piotr Dębiec „Układy Logiczne” DM, sem. 3

Sposoby wyzwalania przerzutników:

Układy sekwencyjne synchroniczne

Sposobem wyzwalania nazywa się warunek, który musi wystąpić na linii CK, aby

przerzutnik mógł zmienić swój stan.

•

wyzwalane zboczem

(narastającym lub opadającym) - ang.

flip-flop

Przykład:

Przerzutnik RS typu „zatrzask” - slajd 6.

Wada:

zmiana stanu na wejściach RS lub wystąpienie zakłóceń przy CK=1 może

powodować asynchroniczną zmianę stanu przerzutnika.

2 podejścia:

1. Układy różniczkujące zbocze

2. Architektura Master-Slave

Jak zbudować przerzutniki, których stan może się zmieniać tylko na zboczu impulsu

zegarowego ?

•

wyzwalane poziomem

(niskim lub wysokim) - przerzutniki typu „zatrzask”, ang.

latch

11

Dr inż.. Piotr Dębiec „Układy Logiczne” DM, sem. 3

Układy sekwencyjne synchroniczne

)

(t

CK

dt

CK

d

)

(

Układy różniczkujące zbocze

CK

Q

Q

F

F

CK

Q

F

F

~10ns

D

Q

Q

CK

dt

d

12

Dr inż.. Piotr Dębiec „Układy Logiczne” DM, sem. 3

Układy sekwencyjne synchroniczne

Idea: 2 przerzutniki typu „zatrzask” tworzą przerzutnik wyzwalany zboczem

Architektura Master-Slave

M

1

Q

1

Q

S

2

Q

2

Q

CK

D

S

R

D

Q

Q

CK

D

1

Q

Q

t

M,S:

3

13

Dr inż.. Piotr Dębiec „Układy Logiczne” DM, sem. 3

Podział układów sekwencyjnych

(automatów)

Podział funkcjonalny:

•

liczniki

•

rejestry

•

sterowniki

•

generatory sekwencji

•

detektory sekwencji

•

układy arytmetyczno-logiczne

•

............................

Ze względu na architekturę:

•

automaty Moore’a

•

automaty Mealy’ego

→

Y=f(S)

→

Y=f(S,X)

Ze względu na sposób pracy:

•

iteracyjne

(iterowanie w czasie !)

•

standardowe (nie iteracyjne)

Formy opisu układów sekwencyjnych

•

graf

•

tablica przejść-wyjść (tablica charakterystyczna, tablica stanów)

•

równanie charakterystyczne (równanie stanu)

•

przebiegi czasowe

14

Dr inż.. Piotr Dębiec „Układy Logiczne” DM, sem. 3

Układy sekwencyjne - Liczniki

Licznik rewersyjny

może zliczać wprzód i wstecz, zależnie od stanu linii sterującej.

Najczęściej spotykane liczniki zliczają w NKB (również modulo n) i BCD.

S

0

/Y

0

. . . . . . .

S

1

/Y

1

S

2

/Y

2

S

3

/Y

3

S

k

/Y

k

S

4

/Y

4

1

1

S

0

/Y

0

. . . . . . .

S

1

/Y

1

S

2

/Y

2

S

3

/Y

3

S

k

/Y

k

S

4

/Y

4

1

1

1

1

1

0

0

0

0

0

0

0

jest to licznik NKB

asynchroniczny

zbudowany z przerzutników

synchronicznych

0

T

0

Q

0

Q

CK

1

T

1

Q

1

Q

CK

T

2

Q

2

Q

CK

1

1

1

we

Licznik:

automat typu Moore’a, który zmienia stan po każdym impulsie wejściowym.

Graf licznika stanowi zamknięty pierścień stanów, bez pętli własnych.

15

Dr inż.. Piotr Dębiec „Układy Logiczne” DM, sem. 3

Układy sekwencyjne - Rejestry

D

Q

Q

D

Q

Q

D

Q

Q

D

Q

Q

X

3

X

2

X

1

X

0

IR

SR

SL

LD

IL

CK

Y

2

Y

1

Y

3

Y

0

Rejestrem uniwersalnym

nazywamy rejestr, który oprócz operacji wpisywania

może wykonywać operacje przesuwania swojej zawartości w lewo i w prawo.

Tryby pracy

SR SL LD Operacja

0 0 1 wpis równoległy

0 1 0 przesuw w lewo

1 0 0 przesuw w prawo

0 0 0 ?

0 1 1 ?

1 1 0 ?

1 0 1 ?

1 1 1 ?

uzupełnić samodzielnie

Rejestrem

nazywamy grupę przerzutników służącą do przechowywania informacji.

16

Dr inż.. Piotr Dębiec „Układy Logiczne” DM, sem. 3

Układy sekwencyjne - Rejestry jako liczniki

0000

1010

0010

0101

0001

1111

1000

0100

1101

1110

0111

1011

1101

1010

1011

0101

0010

1001

0100

0110

Narysować brakujące podgrafy !

n n-1.... 0

UK

...

schemat ogólny

R

F

Narysować wszystkie

podgrafy, jeśli UK realizuje

następującą funkcję Y

wyjść komórek 4-bitowego

rejestru R:

3

2

1

0

R

R

R

R

F

⊕

⊕

⊕

=

3 2 1 0

licznik pierścieniowy

3 2 1 0

licznik pseudopierścieniowy

17

Dr inż.. Piotr Dębiec „Układy Logiczne” DM, sem. 3

Analiza układów sekwencyjnych synchronicznych

3-bitowy licznik synchroniczny NKB

Y=f(S)

→ automat Moore’a

t

t

t

t

t

t

t

t

t

t

t

t

Q

D

Q

Q

Q

D

Q

Q

Q

Q

D

Q

0

0

1

0

0

1

1

1

1

0

1

2

2

1

2

)

(

=

=

⊕

=

=

⊕

=

=

+

+

+

1

0

1

1

1

2

0

1

2

+

+

+

t

t

t

t

t

t

Q

Q

Q

Q

Q

Q

0 0 0 0 0 1

0 0 1 0 1 0

0 1 0 0 1 1

0 1 1 1 0 0

1 0 0 1 0 1

1 0 1 1 1 0

1 1 0 1 1 1

1 1 1 0 0 0

111

000

110

001

101

100

011

010

CK

t

Y

1

Y

0

Y

2

000 001 010 011 100 101 110 111

2

D

2

Q

2

Q

1

D

1

Q

1

Q

0

D

0

Q

0

Q

CK

Przykład 1

Y

2

Y

1

Y

0

18

Dr inż.. Piotr Dębiec „Układy Logiczne” DM, sem. 3

0

1

1

0

1

0

1

0

1

,

,

Q

x

Q

y

Q

x

K

Q

x

J

x

K

Q

x

J

+

=

+

=

+

=

=

⊕

=

y

Q

Q

K

J

K

J

Q

xQ

t

t

t

t

1

0

1

1

0

0

1

1

0

1

+

+

0 0 0 1 1 1 1 1 1 1

0 0 1 0 1 1 1 0 0 0

0 1 0 1 1 1 1 0 1 1

0 1 1 0 1 1 1 0 0 0

1 0 0 0 0 1 0 0 1 1

1 0 1 1 0 1 0 1 1 1

1 1 0 0 0 0 1 1 0 1

1 1 1 1 0 0 1 1 0 0

00

11

10

01

1/1

x/y=

0/1

0/0

1/1

0/0

0/1

1/1

1/0

Analiza układów sekwencyjnych synchronicznych

Y=f(X,S)

→ automat Mealy’ego

1

K

1

J

1

Q

1

Q

CK

0

K

0

J

0

Q

0

Q

x

y

Przykład 2

00

)

0

(

Q

Q

0

1

=

=

t

CK

t

x

y

00

11

10

01

Q

1

Q

0

4

19

Dr inż.. Piotr Dębiec „Układy Logiczne” DM, sem. 3

Synteza układów sekwencyjnych synchronicznych

Kolejne etapy projektowania:

Opis funkcjonalny

Graf układu

Tablica przejść-wyjść

Synteza UK

Schemat połączeń

zgodnie z ogólnym schematem układu sekwencyjnego

synchronicznego: UK i przerzutniki spięte pętlą sprzężenia

zwrotnego, wyraźne określenie wejść i wyjść układu,

włącznie z wejściem zegarowym

1

2

3

4

5

zrozumienie sposobu działania układu, określenie liczby

wejść, wyjść, stanów (przerzutników), schemat blokowy

określenie typu automatu (Moore, Mealy),rysunek grafu

z uwzględnieniem stanów niewykorzystywanych

wybór typu przerzutników, konstrukcja tablicy na

podstawie grafu i tablic wzbudzeń przerzutników

zgodnie z tablicą przejść-wyjść realizowane są funkcje

sterujące przerzutnikami i funkcje wyjściowe

20

Dr inż.. Piotr Dębiec „Układy Logiczne” DM, sem. 3

Synteza układów sekwencyjnych synchronicznych

Przykład 1

Zaprojektować rewersyjny licznik binarny modulo 7

Etap 1:

licznik modulo 7 zlicza:

0-1-2-3-4-5-6-0-1

.... Potrzebne są więc 3 linie wyjściowe. Liczba

wykorzystywanych stanów=7, więc potrzebne są 3 przerzutniki Q

2

Q

1

Q

0.

Potrzebne są 2 wejścia

zegarowe (CK)i trybu zliczania (MODE) - w przód (MODE=

0

) i wstecz (MODE=

1

).

MODE

CK

y

2

y

1

y

0

Etap 2:

automat typu Moore’a. Przy naturalnym zakodowaniu stanów, wyjścia

przerzutników mogą stanowić wyjścia układu:

0

→(000), 1 → (001), 2 → (010), 3 → (011), 4 → (100), 5 → (101), 6 → (110)

.

001

000

010

011

110

100

1

1

1

1

1

1

0

0

0

0

0

0

111

101

0,1

1

0

Stan niewykorzystywany:

7

→ (111)

należy włączyć do grafu, np. skierować

je do stanu

0

.

21

Dr inż.. Piotr Dębiec „Układy Logiczne” DM, sem. 3

Synteza układów sekwencyjnych synchronicznych

Wybieramy przerzutniki T

Etap 3:

Zbiorcza tablica wzbudzeń przerzutników:

Q

t

Q

t+1

D T RS JK

0 0 0 0 x0 0x

0 1 1 1 01 1x

1 0 0 1 10 x1

1 1 1 0 0x x0

0

1

2

1

0

1

1

1

2

0

1

2

T

T

T

Q

Q

Q

Q

Q

Q

M

t

t

t

t

t

t

+

+

+

0 0 0 0 0 0 1

0 0 1

0 0 0 1 0 1 0

0 1 1

0 0 1 0 0 1 1 0 0 1

0 0 1 1

1 0 0 1 1 1

0 1 0 0 1 0 1 0 0 1

0 1 0 1 1 1 0 0 1 1

0 1 1 0 0 0 0 1 1 0

0 1 1 1 0 0 0 1 1 1

1 0 0 0 1 1 0 1 1 0

1 0 0 1 0 0 0 0 0 1

1 0 1 0 0 0 1 0 1 1

1 0 1 1 0 1 0 0 0 1

1 1 0 0 0 1 1 1 1 1

1 1 0 1 1 0 0 0 0 1

1 1 1 0 1 0 1 0 1 1

1 1 1 1 0 0 0 1 1 1

wejścia UK

wyjścia UK

st. następne

M

Q

Q

M

Q

Q

M

Q

Q

Q

Q

Q

T

t

t

t

t

t

t

t

t

t

0

1

0

1

1

2

0

1

2

2

+

+

+

=

t

t

t

t

Q

Q

M

Q

M

Q

T

1

2

0

0

1

+

+

=

M

Q

M

Q

Q

Q

Q

T

t

t

t

t

t

1

2

1

2

0

0

+

+

+

=

0 0 1

0

1

0

0

00 01 11 10

0

00

01

11

10

1 1 1 0

0 1 0 0

T

2

:

t

t

t

Q

Q

MQ

0

1

2

Etap 4:

22

Dr inż.. Piotr Dębiec „Układy Logiczne” DM, sem. 3

Synteza układów sekwencyjnych synchronicznych

Etap 5:

Schemat układu

2

T

2

Q

1

T

1

Q

1

Q

0

T

0

Q

0

Q

2

Q

UK

M

CK

Y

2

Y

1

Y

0

w celu minimalizacji kosztu

układu do UK powinny być

doprowadzone sygnały

negacji stanów automatu

z przerzutników:

0

1

2

,

,

Q

Q

Q

Narysować przykładowe

przebiegi czasowe !

23

Dr inż.. Piotr Dębiec „Układy Logiczne” DM, sem. 3

Synteza układów sekwencyjnych synchronicznych

Przykład 2

Zaprojektować układ, którego graf przedstawiono na schemacie. (JK)

0

1

10/00

11/10

00/01

10/10

01/01

11/11

01/01

00/11

CK

x

1

x

0

y

1

y

0

2 stany

→ 1 przerzutnik (Q)

x

1

x

0

Q

t

Q

t+1

JK y

1

y

0

0 0 0 0 0 x 1 1

0 0 1

1 x 0 0 1

0 1 0

0 0 x 0 1

0 1 1

0 x 1 0 1

1 0 0

1 1 x 1 0

1 0 1

1 x 0 0 0

1 1 0

0 0 x 1 1

1 1 1 1 x 0 1 0

0

1

x

x

J

=

0

1

x

x

K

=

0

0

1

1

x

Q

x

x

y

t

+

=

0

1

0

x

Q

x

y

t

+

=

K

J Q

Q

CK

x

1

x

0

y

1

y

0

24

Dr inż.. Piotr Dębiec „Układy Logiczne” DM, sem. 3

Synteza układów sekwencyjnych synchronicznych

Przykład 3 (iterowanie w czasie)

Zaprojektować iteracyjny układ sekwencyjny sumatora n-bitowego

Ogólna idea:

•

pojedyncza komórka realizuje operacje dla n kolejnych bitów

a

n-1

a

n-2

.... a

0

b

n-1

b

n-2

.... b

0

s

0

s

1

s

2

.... s

n-1

∑

a

i

b

i

D

Q

Q

c

i

c

i+1

CLEAR

s

i

0

0

CK

CK

A

B

S

Algorytm pracy:

1

. A.load=

1

, B.load=

1,

CK

2.

A.sr=

1

, B.sr=

1

.

3.

S.sl=

1

4.

CLEAR =

1

-

0

5.

(n+1)

× CK

Samodzielnie zaprojektować komparator

2 liczb n-bitowych !

• obliczone w i -tej iteracji przeniesienie C

i+1

jest zapamiętywane

w przerzutniku i służy do obliczenia S

i+1

i C

i+2

.

5

25

Dr inż.. Piotr Dębiec „Układy Logiczne” DM, sem. 3

Przykład 4 (detektor sekwencji bitowej)

Zaprojektować układ wykrywający pojawienie się na wejściu w sekwencji 1-0-1

Synteza układów sekwencyjnych synchronicznych

CK

w

y

2. wykrywający także nakładające się sekwencje (ang.

overlapped

)

2 typy architektury układu:

2 typy funkcjonalne układu:

1. wykrywający tylko nie nakładające się sekwencje (ang.

nonoverlapped

)

•

automat Moore’a

•

automat Mealy’ego

CK

t

Y

1

w

Y

2

1

0

0

0

0

1

1

26

Dr inż.. Piotr Dębiec „Układy Logiczne” DM, sem. 3

Synteza układów sekwencyjnych synchronicznych

S

1

=00

S

2

=01

S

3

=10

S

4

=11

stan początkowy

S

1

/0

S

4

/1

S

3

/0

S

2

/0

0

1

0

1

1

0

0

1

Automat Moore’a (overlapped)

t

t

Q

Q

y

0

1

=

w

D

=

0

t

t

t

Q

wQ

Q

w

D

0

1

0

1

+

=

0 0 0 0 0 0

0 0 1 1 0 0

0 1 0 0 0 0

0 1 1 1 0 1

1 0 0 0 1 0

1 0 1 0 1 0

1 1 0 1 1 0

1 1 1 0 1 1

0

1

1

0

1

1

0

1

D

D

y

Q

Q

Q

wQ

t

t

t

t

+

+

0

D

0

Q

0

Q

CK

1

D

1

Q

1

Q

y

w

t

t

t

Q

wQ

Q

w

0

1

0

+

27

Dr inż.. Piotr Dębiec „Układy Logiczne” DM, sem. 3

S

1

/0

S

4

/1

S

3

/0

S

2

/0

0

1

0

1

1

0

0

1

stan początkowy

Automat Moore’a (nonoverlapped)

Automat Mealy’ego (overlapped) =

?

Automat Mealy’ego (nonoverlapped)

S

1

S

3

S

2

0/0

1/0

0/0

0/0

1/0

1/1

stan początkowy

S

4

x/0

Synteza układów sekwencyjnych synchronicznych

Wyszukiwarka

Podobne podstrony:

Abolicja podatkowa id 50334 Nieznany (2)

4 LIDER MENEDZER id 37733 Nieznany (2)

katechezy MB id 233498 Nieznany

metro sciaga id 296943 Nieznany

perf id 354744 Nieznany

interbase id 92028 Nieznany

Mbaku id 289860 Nieznany

Probiotyki antybiotyki id 66316 Nieznany

miedziowanie cz 2 id 113259 Nieznany

LTC1729 id 273494 Nieznany

D11B7AOver0400 id 130434 Nieznany

analiza ryzyka bio id 61320 Nieznany

pedagogika ogolna id 353595 Nieznany

Misc3 id 302777 Nieznany

cw med 5 id 122239 Nieznany

D20031152Lj id 130579 Nieznany

mechanika 3 id 290735 Nieznany

więcej podobnych podstron