Układy Cyfrowe – laboratorium

Przykład realizacji ćwiczenia nr 8.

Stanowisko laboratoryjne:

1.

Komputer PC i oprogramowanie

2.

2 x kabel TRS

3.

kabel USB

4.

Płyta Altera DE-2.

Opis stanowiska:

Komputer PC jest używany do syntezy struktury i konfiguracji układu FPGA, dodatkowo

jest używany jako generator i analizator sygnału audio. Generacja i analiza sygnału audio

jest wykonywana w darmowym oprogramowaniu Spectrum Lab.

Analogowy sygnał audio jest wysyłany z wyjścia liniowego karty dźwiękowej komputera

PC do płyty Altera DE-2 kablem TRS. Sygnał analogowy jest przetwarzany na cyfrowy w

zamontowanym na płycie przetworniku analogowo-cyfrowym. Dane w postaci cyfrowej

przechodzą przez układ FPGA na wejście przetwornika cyfrowo-analogowego. Następnie

w postaci analogowej są przesyłane do komputera PC kablem TRS na wejście liniowe

karty dźwiękowej komputera PC.

Kabel USB służy do wysyłania z komputera PC danych konfigurujących układ FPGA

przez urządzenie USB-Blaster za pomocą oprogramowania Altera Quartus II.

Zadania do wykonania :

Zadanie. 0 Konfiguracja przetwornika analogowo-cyfowego:

Celem tego zadania jest poprawne skonfigurowanie przetwornika analogowo-cyforwego

cyfrowo-analogowego Wolfson WM8731 zamontowanego na płycie DE-2.

Po włączeniu zasilania płyty DE-2 pobierana jest automatycznie z pamięci FLASH fabryczna

konfiguracja układu FPGA.

Przed rozpoczęciem zadań filtracji sygnału audio w układzie FPGA należy poprawnie

skonfigurować przetwornik analogowo-cyfrowy, cyfrowo-analogowy.

Należy wgrać do układu FPGA konfigurację z zaimplementowanym interfejsem I2C, przez

który zostaną wysłane dane ustawiające przetwornik w pożądany tryb pracy. Ustawienia

parametrów przetwornika mogą być zmienione przez wyłączenie zasilania lub ponowne

przesłanie danych. Przekonfigurowanie układu FPGA, nie zmienia wcześniej ustawionych

parametrów przetwornika.

W celu przesłania danych konfigurujących przetwornik ADC DAC należy:

1. Upewnić się czy poprawnie podłączony jest kabel USB do złącza USB-Blaster

2. Włączyć zasilanie płyty DE-2 czerwonym przyciskiem.

3. Uruchomić plik codec_config.bat w katalogu ./filter_lab/z0/

Zadanie. 1 Opis struktury filtru FIR w języku VHDL:

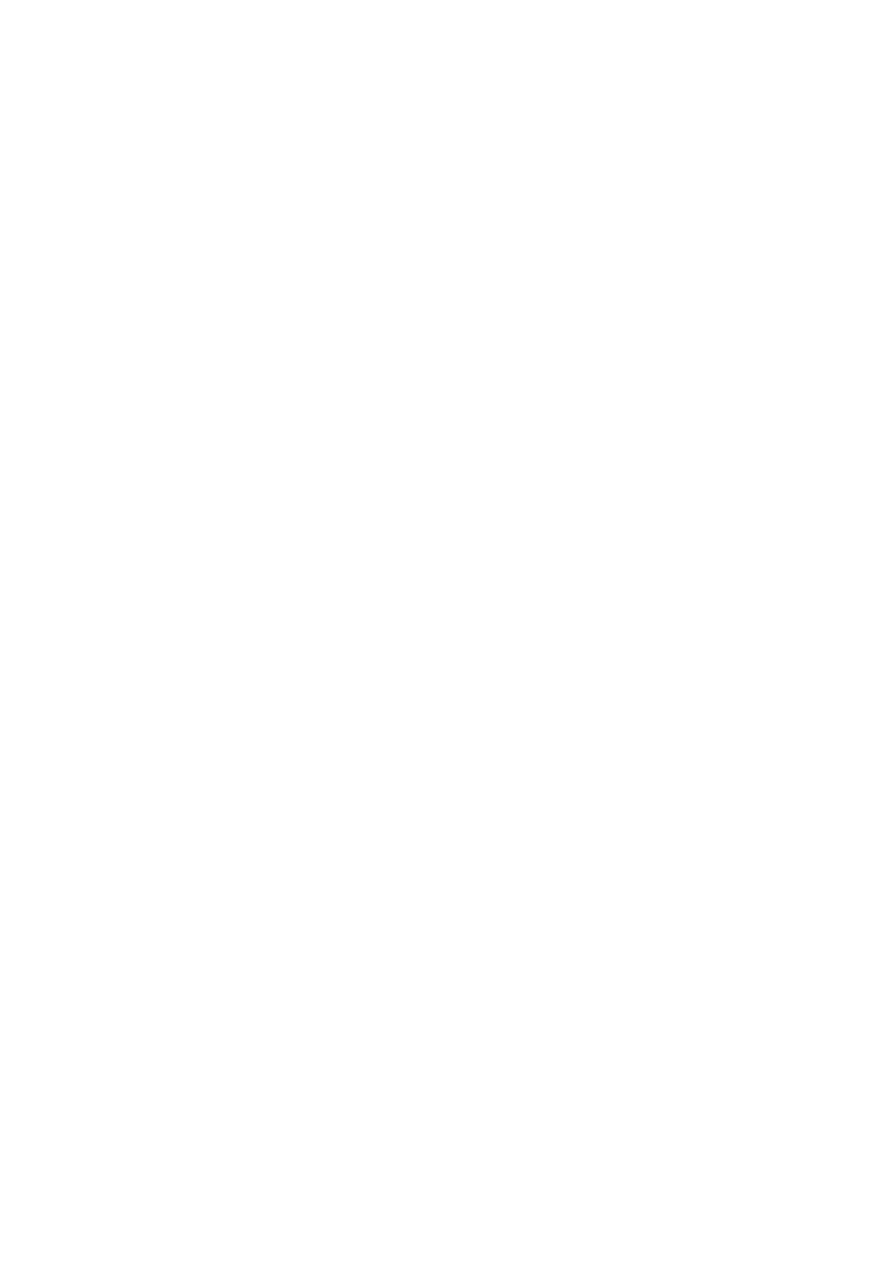

Struktura projektu fl_z1:

Protokół danych wychodzących i wchodzących do bloku audio_top

- próbki dźwięku wychodzące z modułu audio_top są w formacie U2 i mają zakres

wartości <-1, 1) zapisany na 8 bitach.

- próbki dźwięku wychodzące z modułu audio_top pojawiają się z częstotliwością

48 kHz, obecność nowej wartości na linii danych ADC_OUT jest sygnalizowana wysokim

stanem sygnałem ADC_OUT_EN.

- próbki dźwięku wchodzące do modułu audio_top są pobierane z częstotliwością

48 kHz, próbki są zatrzaskiwane w rejestrach modułu gdy sygnał ADC_OUT_EN jest w

stanie wysokim.

- próbki dźwięku wchodzące do modułu audio_top są w formacie U2 i mają zakres

wartości <-1, 1) zapisany na 16 bitach

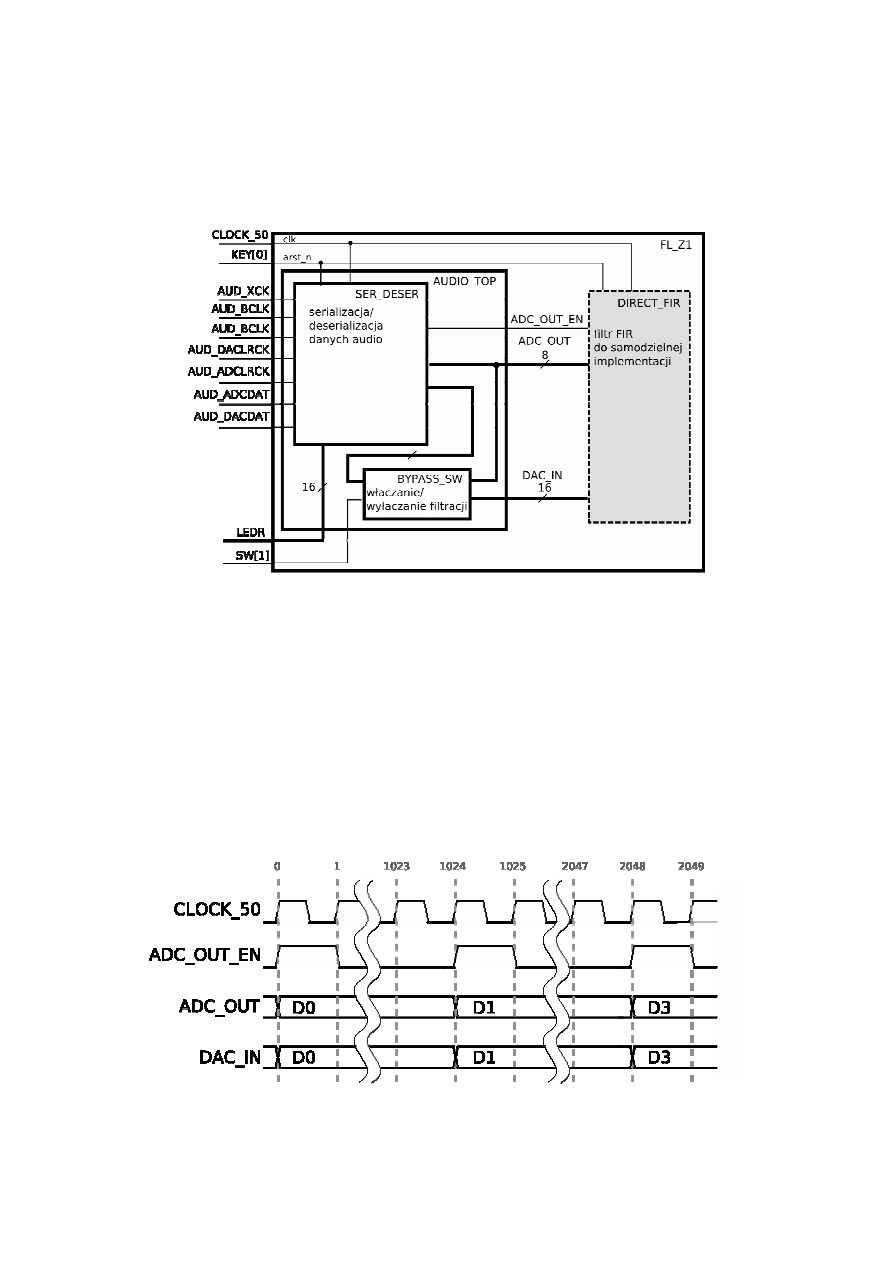

Struktura filtru FIR:

Filtr o transmitancji H(z) = -0.2 + 0.6 z

-1

– 0.2 z

-2

Opis struktury filtru w języku VHDL

plik direct_fir.vhd :

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_signed.all;

use IEEE.std_logic_arith.all;

entity direct_fir is

port(

clk : in STD_LOGIC; -- sygnal zegara

arst_n : in STD_LOGIC; -- asynchroniczny sygnal zerowania niskim poziomem

data_in : in STD_LOGIC_VECTOR(7 downto 0); -- dane wejsciowe

data_out : out STD_LOGIC_VECTOR(15 downto 0); -- dane wyjsciowe

data_in_en : in STD_LOGIC -- strob danych wejsciowych

);

end entity;

architecture RTL of direct_fir is

-- definicja typu rejestrow przchowujacych wartosci poprzednich probek

type DLY_TYPE is array(2 downto 0) of STD_LOGIC_VECTOR(7 downto 0);

-- deklaracja sygnalow przechowujacych wartosci poprzednich probek

signal taps_r : DLY_TYPE;

signal taps_nxt : DLY_TYPE;

signal data_sum : STD_LOGIC_VECTOR(16 downto 0);

begin

dly_synch_proc:

process(clk,arst_n)

begin

if arst_n = '0' then

for i in 0 to 2 loop

taps_r(i) <= (others => '0');

end loop;

elsif clk = '1' and clk'event then

if data_in_en = '1' then

for i in 1 to 2 loop

taps_r(i) <= taps_r(i-1);

end loop;

taps_r(0) <= data_in;

end if;

end if;

end process;

fir_sum: data_sum <= taps_r(0) * conv_std_logic_vector( 460,9) +

taps_r(1) * conv_std_logic_vector( 154,9) -

taps_r(2) * conv_std_logic_vector( 52,9);

fir_output: data_out <= data_sum(15 downto 0);

end architecture;

zalecenia projektowe:

- należy wystrzegać się przesterowania sygnału:

- zachować odpowiedni rozmiar sygnału przechowującego wynik operacji

arytmetycznych

- pamiętać o propagacji znaku

- należy poprawnie wysterować sygnał, tak aby nie usunąć istotnych informacji

przechowywanych na najmłodszych bitach

- przy mnożeniu liczb ułamkowych należy pamiętać o pozycji kropki dziesiętnej:

identycznie zachowuje się kropka dziesiętna w przypadku liczb binarnych przykład:

fix<8,7>*fix<8,7> = fix<16,14>

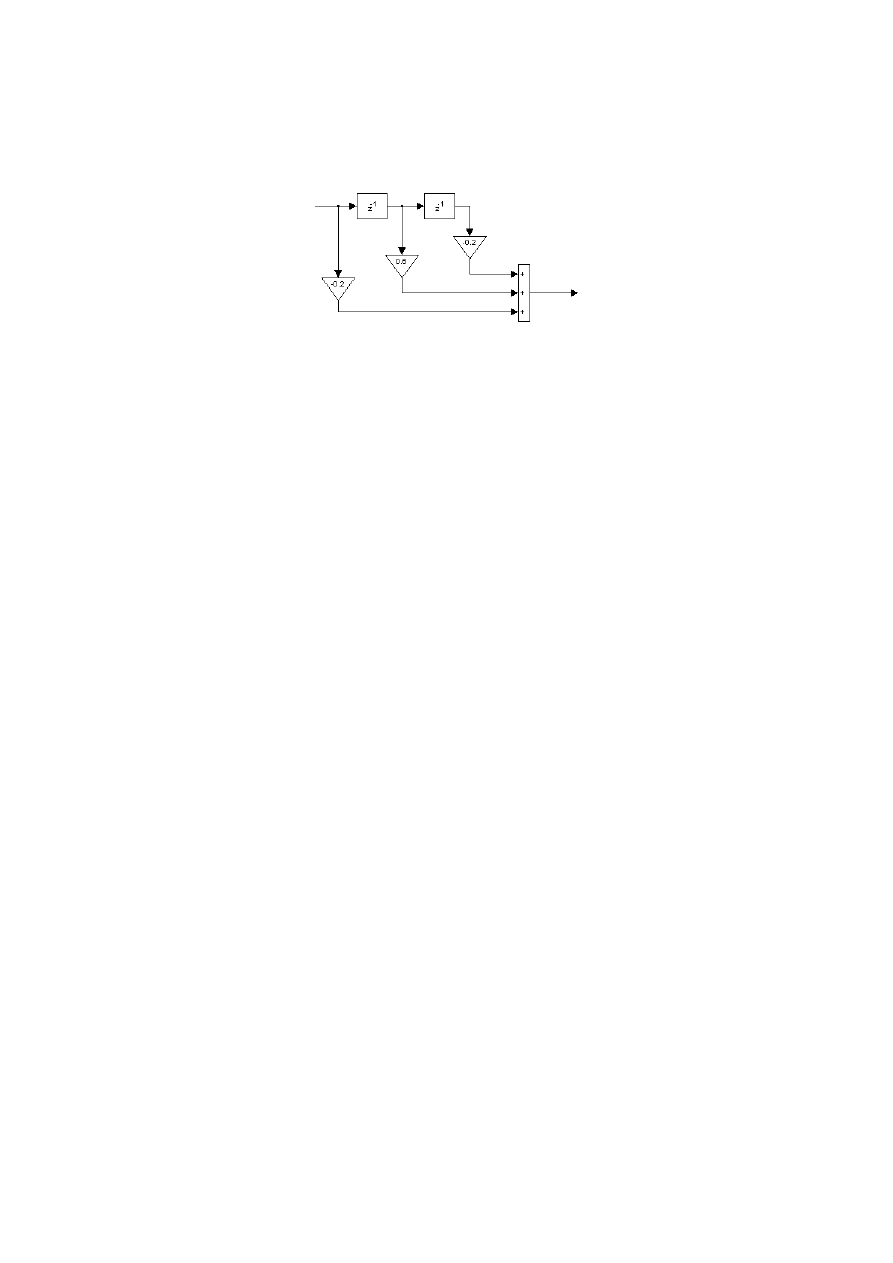

1. Umieścić plik direct_fir.vhd w projekcie fl_z1 znajdującym się w podkatalogu

./filter_lab/z1/fl_z1/

z menu głównego wybrać: Project -> Add/Remove Files in Project

nacisnąć przycisk … i wskazać plik direct_fir.vhd w oknie dialogowym, potwierdzić Open

nacisnąć przycisk Add,

zamknąć okno przyciskiem OK

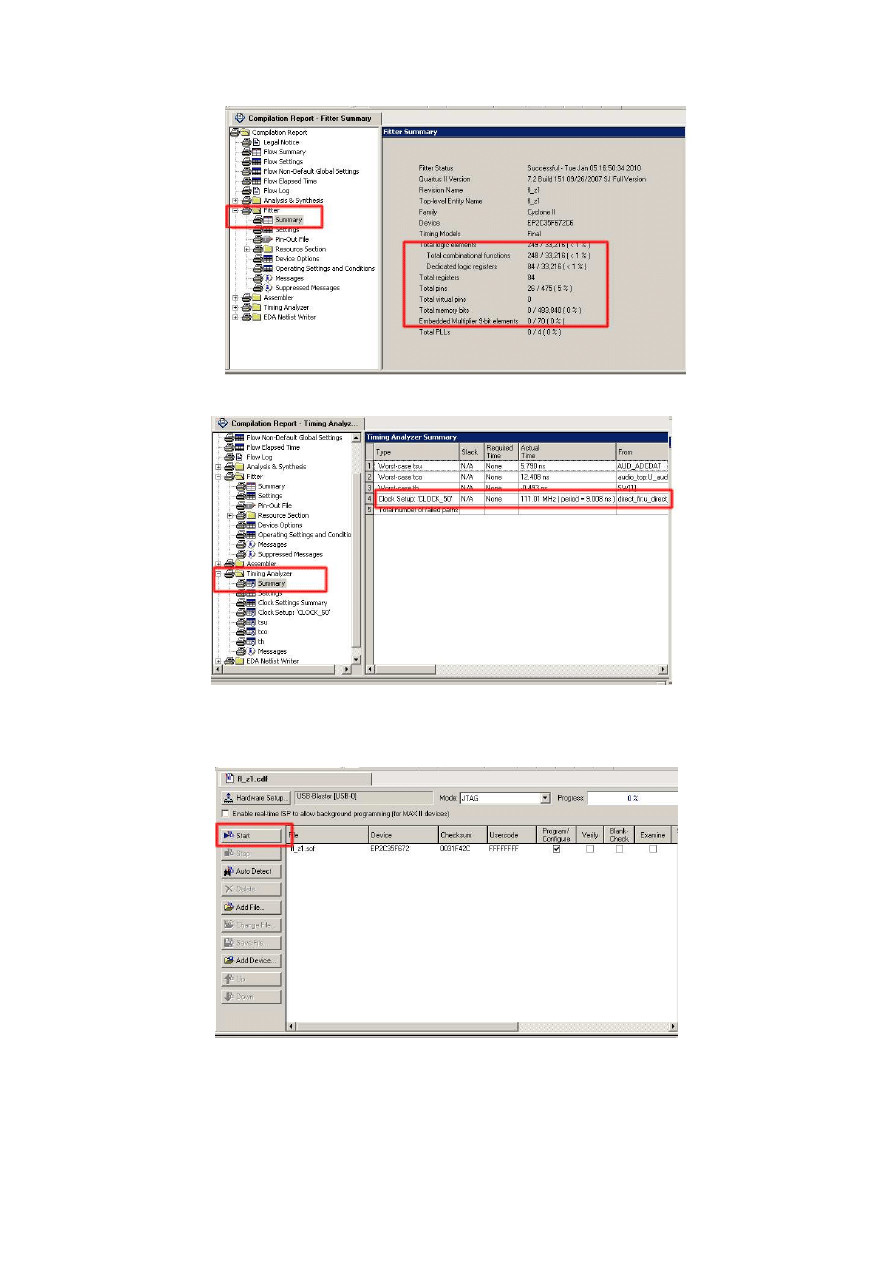

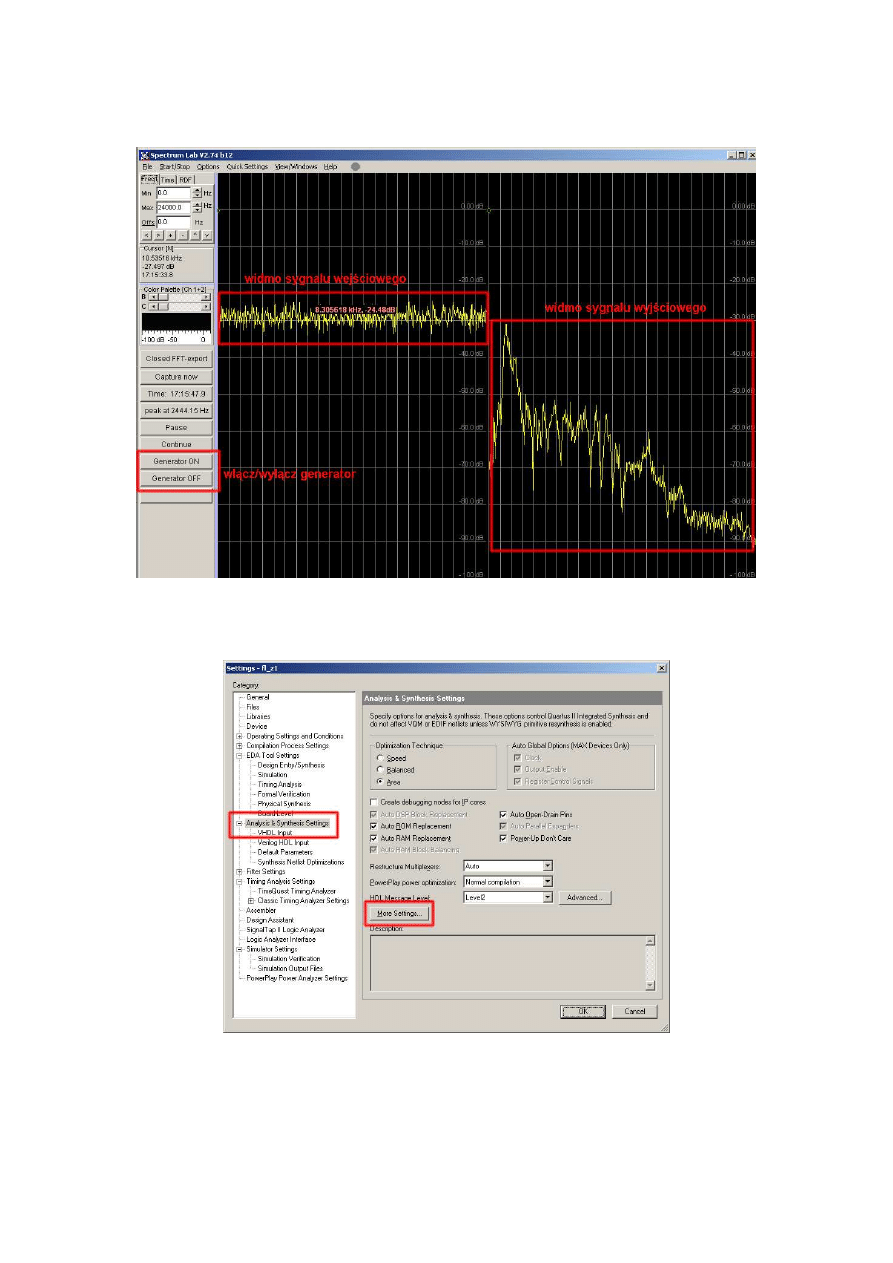

2. Synteza i implementacja

z menu głównego wybrać Processing -> Start Compilation

wyniki implementacji:

liczba elementów logicznych:

maksymalna częstotliwość pracy układu

3. Programowanie układu

Z menu głównego wybrać: Tools -> Programmer

Nacisnąć przycisk Start

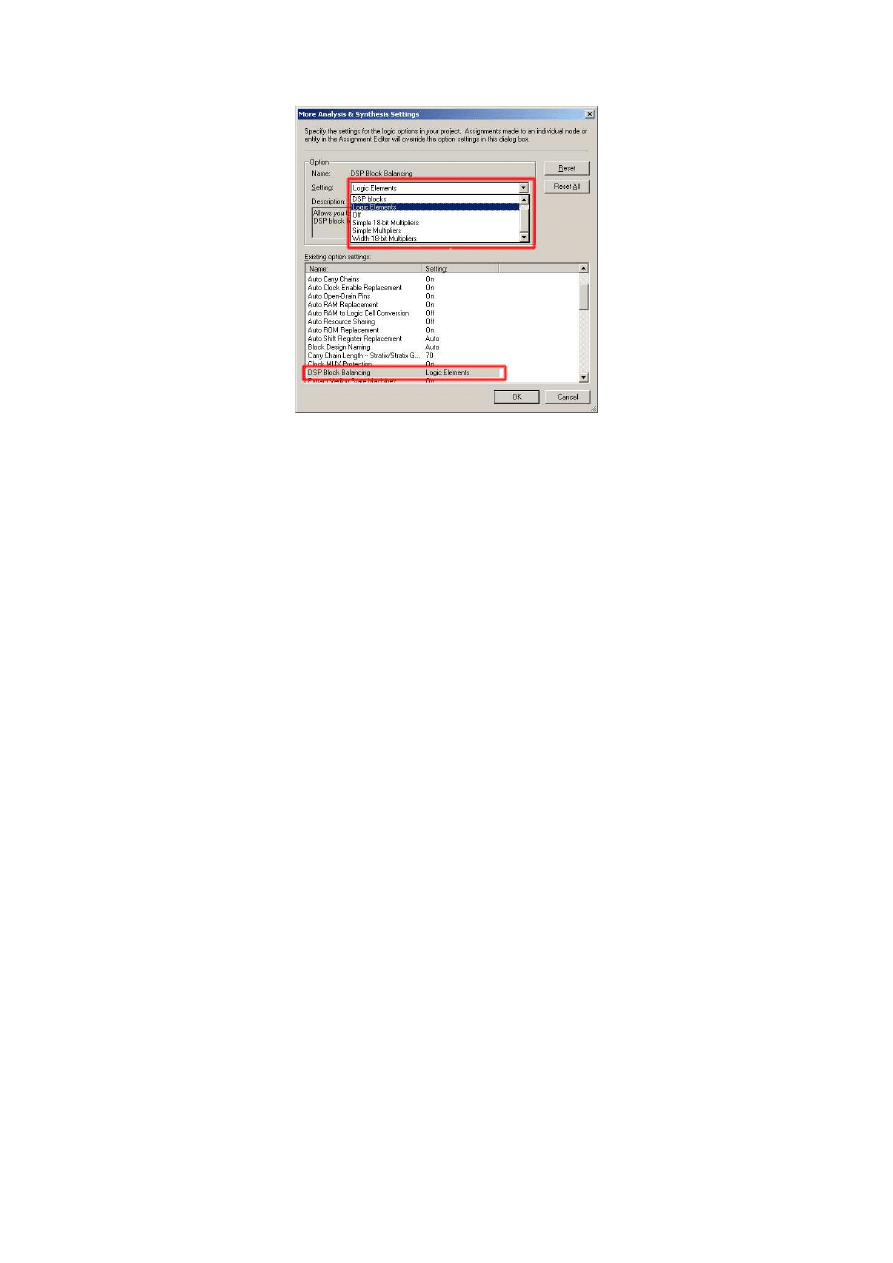

4. Analizator widma - program Spectrum LAB

uruchomić program: ./sw/spectrum/spec_lab.exe

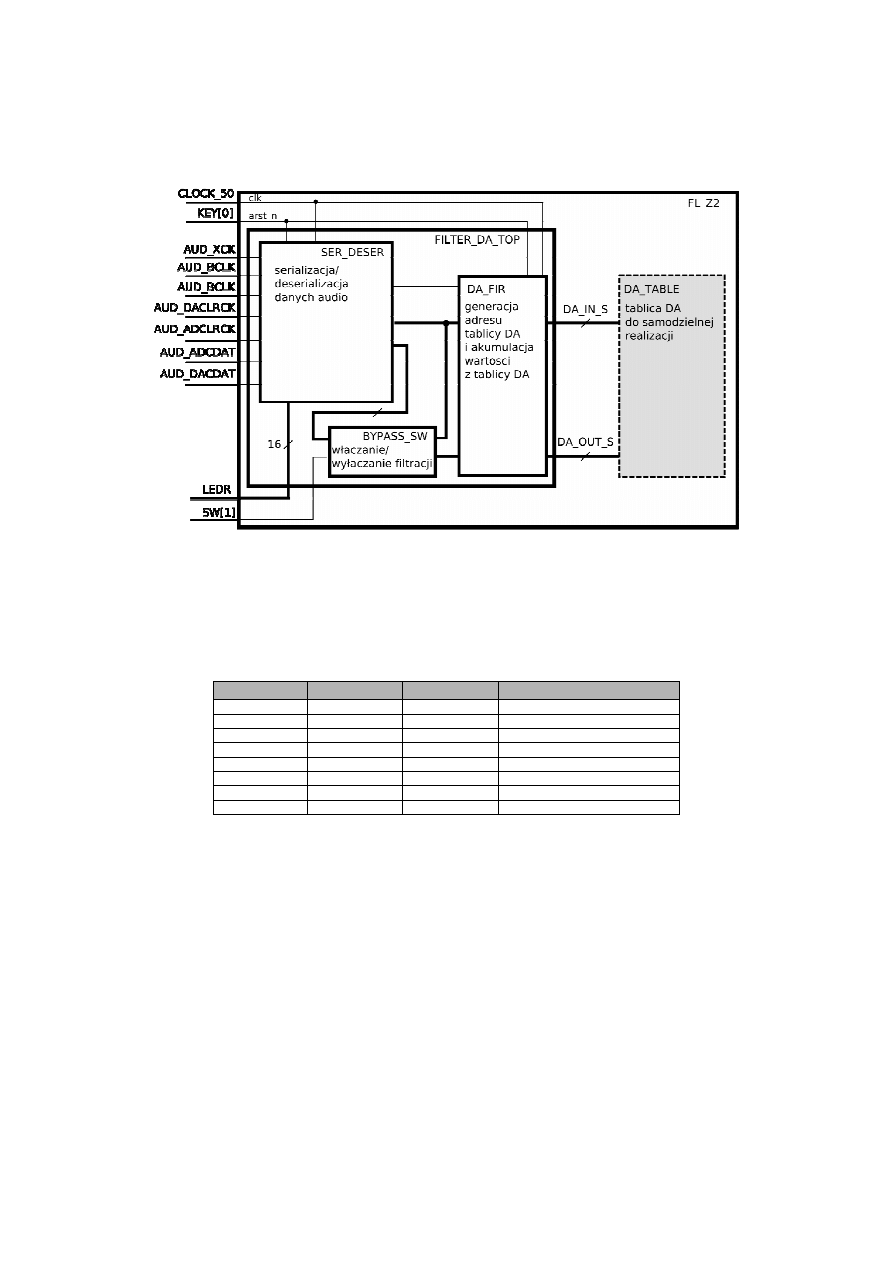

5. Włączenie użycia bloków DSP w implementacji filtru:

Z menu głównego wybrać Assignments -> Settings

Nacisnąć przycisk More Settings…

Wybrać w oknie Existing option settings : DSP Block Balancing

W rozwijanej liście Setting: wybrać DSP blocks

Zamknąć okna zatwierdzając wybór przyciskiem OK

6. Wykonanie syntezy i implementacji i programowania układu (powtórzyć kroki 2 i 3)

Zadanie 2. Implementacja filtru FIR w arytmetyce rozproszonej

Struktura projektu fl_z2:

1. Obliczenie współczynników filtru FIR realizowanego w arytmetyce rozproszonej

przykład:

filtr o współczynnikach [-0.2, 0.6 , -0.2]

– zapisując współczynniki na 8 bitach otrzymamy następującą dziesiętną reprezentację [ -26, 77 , -26 ]

liczb binarnych

xb[2]

xb[1]

xb[0]

f(c[n],x[n])

0

0

0

-26

·

0+77

·

0-26

·

0 = 0

0

0

1

-26

·

0+77

·

0-26

·

1 = -26

0

1

0

-26

·

0+77

·

1-26

·

0 = 77

0

1

1

-26

·

0+77

·

1-26

·

1 = 51

1

0

0

-26

·

1+77

·

0-26

·

0 = -26

1

0

1

-26

·

1+77

·

0-26

·

1 = -52

1

1

0

-26

·

1+77

·

1-26

·

0 = 51

1

1

1

-26

·

1+77

·

1-26

·

1 = 25

2. Wyznaczenie rozmiaru tablicy DA

2

3

·

(log

2

max {0,|-26|,77,51,|-26|,|-52|,25} +1)= 2

3

·

( log

2

77 +1) = 64 bity

3. Generacja tablicy prawdy przy pomocy oprogramowania filter.exe:

program filter.exe na podstawie podanych współczynników filtra zapisanych w pliku

tekstowym o dowolnej nazwie:

-generuje tablicę prawdy zapisaną w standardzie Berkeley’a i zapisuje ją do pliku o

podanej nazwie przez użytkownika,

-zapisuje wygenerowaną tablicę prawdy w języku VHDL i zapisuje ją w pliku

da_table.vhd.

Plik wejściowy współczynników filtra jest postaci np.: [-26,77,-26]. Pierwszy skrajny lewy

współczynnik jest „najmłodszym” współczynnikiem. Dla wygody i zgodności nazw z

projektem fl_z2 nazwa pliku dla generowanej tablicy prawdy powinna mieć nazwę

da_table.pla.

4. Umieszczenie tablicy DA zapisanej w języku VHDL w projekcie fl_z2 znajdującym się w

podkatalogu ./filter_lab/z2/fl_z2/vhdl

Należy dodać plik da_table.vhd do projektu (analogicznie jak w zad.1.1)

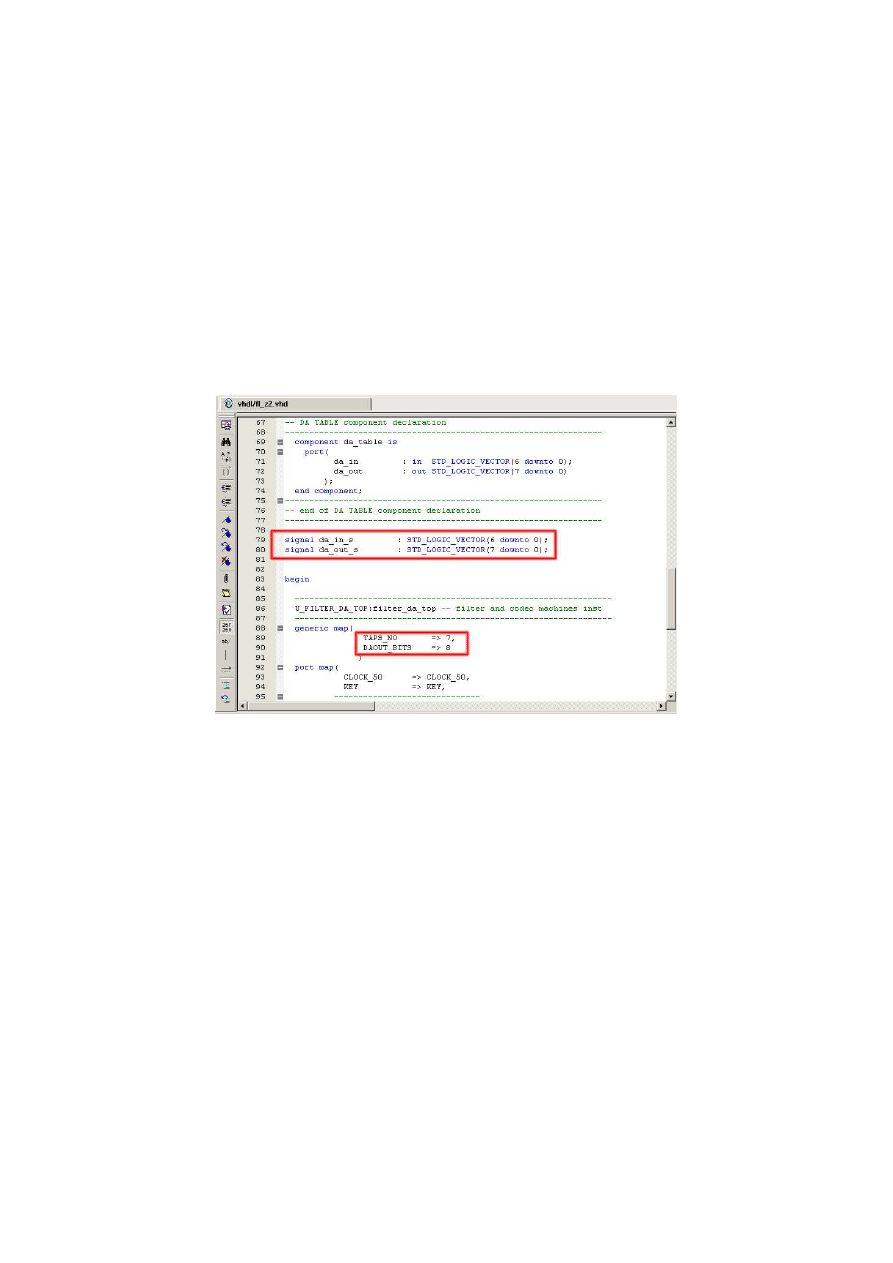

Należy zwrócić uwagę czy poprawnie są podane wartości GENERIC dla instancji

U_FILTER_DA_TOP

oraz rozmiary sygnałów łączących moduł U_FILTER_DA_TOP z U_DA_TABLE w pliku:

.filter_lab/z2/fl_z2/vhdl/fl_z2.vhd

5. Wykonanie syntezy i implementacji i programowania układ (analogicznie jak w zad. 1. 2,3)

6. Wykonanie dekompozycji tablicy DA programem GUIDEC i/lub DEMAIN:

6.1 Program Demain ( umieszczony na<http:://www.zpt.tele.pw.edu.pl/projekty.htm>). Do

uruchomienia wymagana biblioteka cw3220.dll w tym samym katalogu co program. Program

Demain.exe i cw3220.dll znajdują się również w podkatalogu lut_da.

6.1.1 dekompozycja tablicy programem DEMAIN. W podkatalogu <lut_DA\pdf

>umieszczone są:

opis.pdf – instrukcja obsługi

strategie.pdf – prosty szkic strategii prowadzących do w miarę optymalnego

rozwiązania.

przykład.pdf – dekompozycja funkcji bin2bcd.pla

Plikiem wejściowym dla programu Demain jest plik z tablicą prawdy (u nas: da_table.pla )

W wyniku dekompozycji otrzymujemy plik da_table_out z komórkami rozkładu zapisanymi

w standardzie Berkeley’a

6.1.2 Konwersja pliku da_table.out na plik da_table.vhd za pomocą programu

demain_VHD_vec.exe<katalog lut_DA> Do uruchomienia programu wymagane jest aby

pliki nazwa.pla oraz nazwa.out znajdowały się w tym samym katalogu co program.

6.2 Program GUIDEC(umieszczony na<http:://www.zpt.tele.pw.edu.pl/projekty.htm>

Plikiem wejściowym dla programu GUIDEC jest plik z tablicą prawdy ( u nas: da_table.pla)

Uwaga: przed uruchomieniem programu należy w tablicy doknać następujących zmian w

dwóch wierszach tablicy prawdy: .ilb oraz .ib. Wszystkie numery występujące po nazwach

zmiennych muszą być ujęte w nawiasy. Np.

.ilb da_i4 da_i3 da_i2 da_i1 da_i0 zamieniamy na: .ilb da_i(4) da_i(3) da_i(2) da_i(1) da_i(0)

i podobnie np.:

.ob da_o3 da_o2 da_o1 da_o0 zamieniamy na: .ob da_o(3) da_o(2) da_o(1) da_o(0)

Obsługa programu: File->Open-> [wybór nazwy z katalogu],

Project ->Set Project to Current File (ustawia nazwę projektu na nazwę otwartego pliku),

Option -> Select architecture( ustawamy na FLEX/APEX)

Option->Process control ( ustawiamy w Output formats opcję VHDL )

Decompose-> Start process.

Program zapisuje wynik dekompozycji w języku VHDL(opcja process control->VHDL) w

pliku o takiej nazwie jak tablica prawdy i rozszerzeniu .vhd. Przed umieszczeniem pliku

da_table.vhd w projekcie należy dokonać następującej zmiany. Usunąć lub zakomentować

sygnały wejściowe i wyjściowe i zapisać je w postaci logicznych wektorów o odpowiedniej

długości.

ENTITY

da_table

IS

PORT

(

-- da_i(0), da_i(1), da_i(3), da_i(4)

: IN STD_LOGIC;

-- da_i(6), da_i(2), da_i(8)

: IN STD_LOGIC;

-- da_o(12), da_o(13), da_o(14), da_o(9)

: OUT STD_LOGIC;

-- da_o(11), da_o(6), da_o(10), da_o(7)

: OUT STD_LOGIC;

-- da_o(8), da_o(2), da_o(5), da_o(3)

: OUT STD_LOGIC;

-- da_o(0), da_o(1), da_o(4)

: OUT STD_LOGIC

da_i :

IN STD_LOGIC_VECTOR

(9

downto

0);

da_o :

OUT STD_LOGIC_VECTOR

(14

downto

0)

);

END

da_table;

6.3 Umieścić tablicę DA ( otrzymaną w punkcie 3.1 lub 3.2) zapisaną w języku VHDL w

projekcie fl_z2 znajdującym się w podkatalogu ./filter_lab/z2/fl_z2/. Zaimplementować,

wykonać oraz zanotować na karcie odpowiedzi liczbę zużytych elementów logicznych i

maksymalną częstotliwość pracy układu.

Wyszukiwarka

Podobne podstrony:

Asembler ARM przyklady II

Sily przyklady

Przykłady roli biologicznej białek

style poznawcze jako przykład preferencji poznawczych

pytania przykladowe exam zaoczne(1)

przykładowa prezentacja przygotowana na zajęcia z dr inż R Siwiło oceniona

17 Metodologia dyscyplin praktycznych na przykładzie teorii wychowania fizycznego

Organizacja stanowiska pracy przykładowa prezentacja słuchaczy

Inicjacja seksualna młodzieży gimnazjalnej na przykładzie szkoły wiejskiej

Algorytmy z przykladami tp 7 0

21 Fundamnety przyklady z praktyki

Edukacja na Kaszubach; przykłady edukacji regionalnej i regionalizacji nauczania

Metoda Bukowskiego przykład

Kordecki W, Jasiulewicz H Rachunek prawdopodobieństwa i statystyka matematyczna Przykłady i zadania

więcej podobnych podstron