Architektura Systemów Komputerowych

Laboratorium

Nr ćwiczenia: 3

Temat ćwiczenia: Hazard statyczny.

Imię i nazwisko prowadzącego kurs: Maciej Huk

Wykonawca:

Jakub Bartusiak

Imię i Nazwisko

nr Indeksu, wydział

Jakub Bartusiak

197914, SKP

Termin zajęć: dzień tygodnia, godzina

Wtorek, 15

15

Data oddania sprawozdania:

Ocena końcowa

Ewentualne adnotacje dotyczące wymaganych poprawek oraz daty otrzymania

poprawionego sprawozdania:

1 |

S t r o n a

S

PIS TREŚCI

2 |

S t r o n a

1.

C

EL ĆWICZENIA

Celem ćwiczenia jest wyjaśnienie zjawiska hazardu statycznego. Należy też podać różnice

pomiędzy hazardem statycznym i dynamicznym.

Na przykładzie zaproponowanej funkcji czterech zmiennych , wyjaśnić sposoby

eleminacji hazardu z układu.

2.

C

ZYM JEST HAZARD

?

W dotyczhczasowych rozważaniach, przyjmowaliśmy, że zmiany stanów układów logicznych

są natychmiastowe, wolne od opóźnień (z powodu braku parametru czasu w algebrze

Boola). Okazuje się, że w rzeczywistych warunkach, nie możemy uzyskać tego rodzaju zmian.

Przyjmijmy więc, że wprowadzanie jakichkolwiek zmian w stanie układu logicznego trwa

pewien czas. W takim razie, występuje krótki okres, w którym układ ma wartość

nieokreśloną, lub pomimo właściwego jego zaprojektowania, występuję nieodpowiednie

wartości na wyjściu. Jeżeli na wyjściu pojawia się krótkotrwały i nieodpowiedni impuls,

będący wynikiem opóźnień działania układu, to zjawisko takie nazywamy hazardem

statycznym (ponieważ sygnał wejściowy zmienił się parzystą ilość razy).

Hazard może (ale nie musi) wystąpić w układach, w którym na różnych drogach od wejścia

do wyjścia występuje jednakowa ilość bramek tego samego rodzaju.

Hazardem dynamicznym nazywamy taki układ, w którym występują wielokrotne zmiany

stanów na wyjściach.

3.

S

POSOBY USUWANIA HAZARDU

Istnieje kilka sposobów usuwania ryzyka wystąpienia hazardu w układach:

Dopasowanie elementów ze względu na ich opóźnienia,

Wprowadzenie do układu elementów opóźniających,

(z praktycznego punktu widzenia, rozwiązania takie są jednek niezadowalające. Dużo

bardziej sensownym rozwiązaniem jest następne),

Wprowadzenie do układu elementów nadmiarowych, które nie zmieniają realizowanej

przez układ funkcji, a jedynie usuwają zjawisko hazardu.

(takie rozwiązanie nie wymusza na konstruktorze brania pod uwagę indywidualnych

opóźnień elementów układu).

3 |

S t r o n a

4.

A

NALIZA FUNKCJI Z HAZARDEM

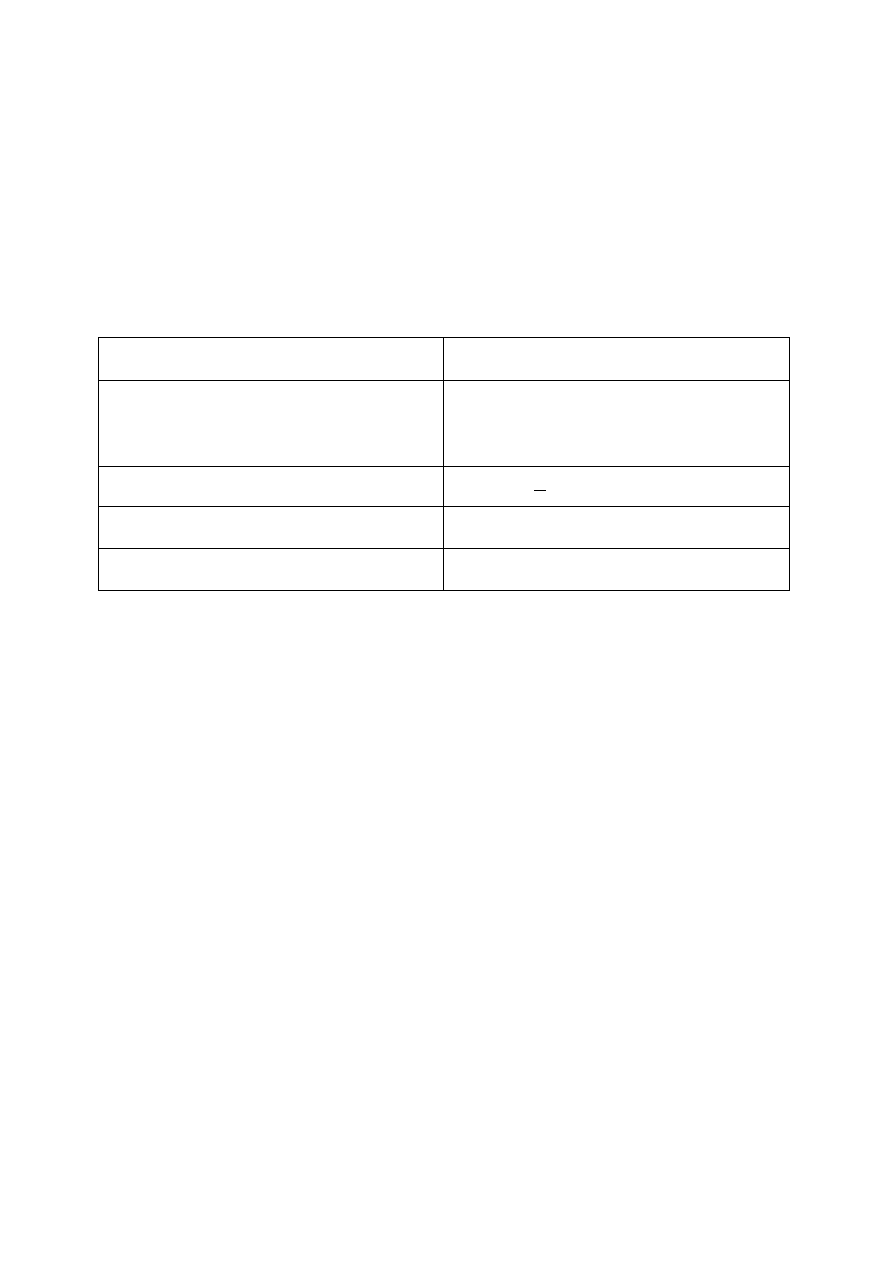

Na potrzeby zadania, proponuję funkcję czterech zmiennych , której tabela prawdy i

siatka Karnougha wygląda następująco:

0 0 0 0

1

0 0 0 1

1

0 0 1 0

0

0 0 1 1

0

0 1 0 0

0

0 1 0 1

1

0 1 1 0

0

0 1 1 1

1

1 0 0 0

0

1 0 0 1

0

1 0 1 0

0

1 0 1 1

0

1 1 0 0

0

1 1 0 1

1

1 1 1 0

0

1 1 1 1

1

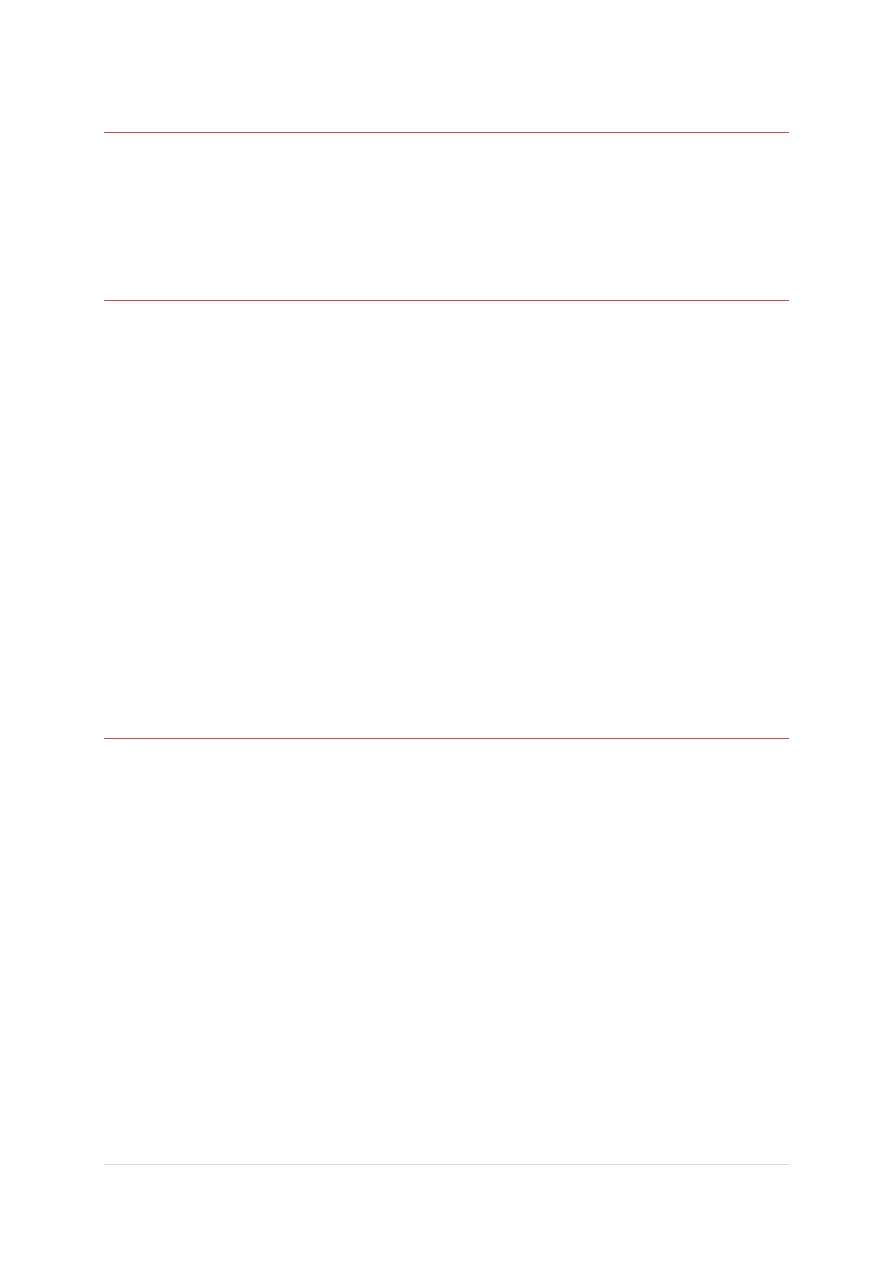

ab↓ cd→ 00 01 11 10

00

1 1 0 0

01

0 1 1 0

11

0 1 1 0

10

0 0 0 0

Taka funkcja wygląda następująco:

̅ ̅ ̅

Korzystając z praw deMorgana, przekształcam funkcję następująco:

̅ ̅ ̅

̅̅̅̅̅

̅̅̅̅

̅̅̅̅̅̅̅̅̅̅̅

4 |

S t r o n a

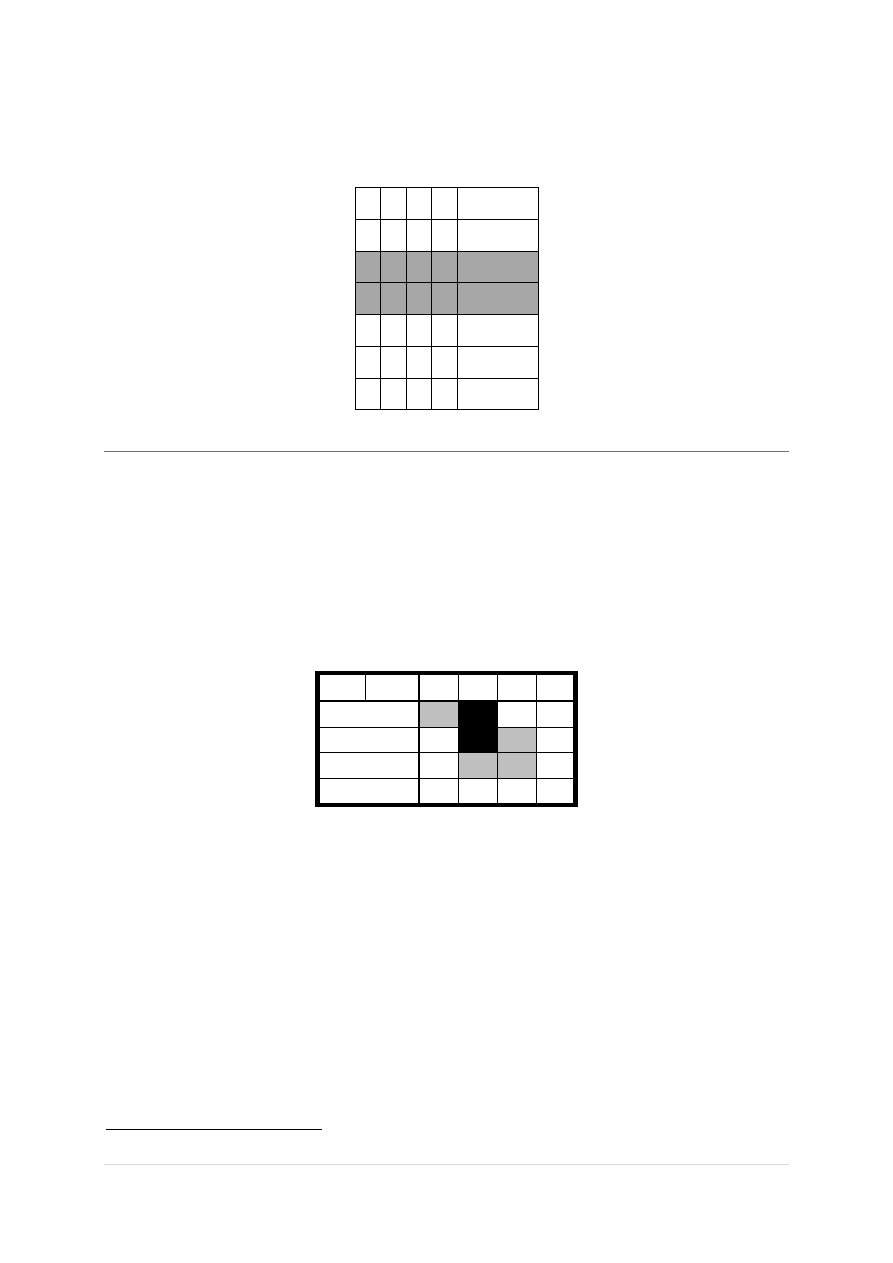

Hazard w mojej funkcji wystąpi, gdy wejście zmieni się z 0001 na 0101, czyli gdy wejście b

zmieni stan na stan a, podczas gdy wyjście powinno zostać takie samo. Jest to konsekwencją

dłuższego czasu propagacji w porównaniu do reszty ścieżek w układzie.

a b c d

0 0 0 0 1

0 0 0 1 1

0 1 0 1 1

0 1 1 1 1

1 1 0 1 1

1 1 1 1 1

5.

E

LIMINACJA HAZARDU Z UKŁADU

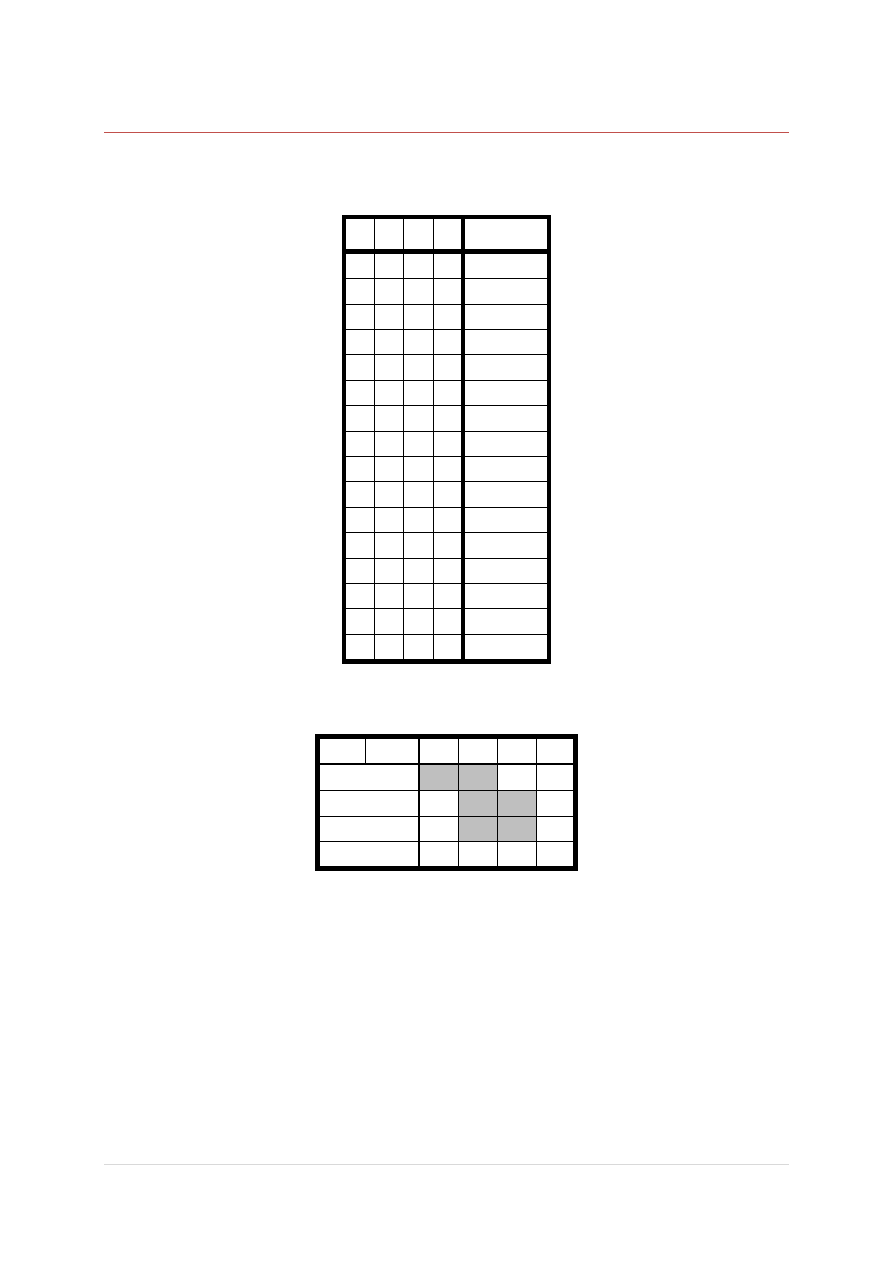

Powodem ryzyka wystąpienia hazardu jest zbytnie zminimalizowanie funkcji. Aby

wyeliminować to ryzyko, należy połączyć w pary wszystkie implikanty proste, zgodnie z

twierdzeniem:

Dwupoziomowa realizacja układowa AND-OR funkcji przełączającej jest wolna od

zjawiska hazardu statycznego, jeżeli zawieta realizację wszystkich implikantów prostych

danej funkcji

1

Tak więc, należy zrealizować wszystkie implkanty proste, w taki sposób:

ab↓ cd→ 00 01 11 10

00

1

1

0 0

01

0

1

1 0

11

0 1 1 0

10

0 0 0 0

Wynikowa funkcja przyjmie postać:

̅ ̅ ̅ ̅ ̅ ̅ ̅ ̅

̅̅̅̅̅

̅̅̅̅ ̅ ̅

̅̅̅̅̅

̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅

Tak zrealizowana nadmiarowa funkcja eliminuje ryzyko wystąpienia hazardu statycznego.

1

Pomoc dydaktyczna do wykładu teorii układów scalonych, twierdzenie 14.6.1

5 |

S t r o n a

6.

P

RZERZUTNIK TYPU D JAKO

„

OSCYLOSKOP

”

Do realizacji zadania wykorzystujemy układu UCY 7474, który jest przerzutnikiem typu D, w

zastępstwie oscyloskopu. Układ ten powinien wychwycić zmiany na wyjściu układu

realizującego moją funkcję.

Wadą zastosowania przerzutnika jest to, że przy zbyt krótkim hazardzie, przerzutnik nie

zdąży zareagować (należy wtedy zastosować elementy opóźniające- bramki NOT). Kolejnym

minusem użycia UCY7474, jest to, że nie pokaże nam on dokładnych danych dotyczących

hazardu układu. Oscyloskop umożliwiłby analizę tablicy stanów.

Przy narastającym zboczu sygnału zegarowego, układ 7474 będzie przełączał wartości jego

wyjść- spowoduje to miganie diod LED.

7.

O

DRĘCZNE RYSUNKI

a) układ z ryzykiem wystąpienia hazardu

b) układ z wyeliminowanym hazardem

Wyszukiwarka

Podobne podstrony:

09 Architektura systemow rozproszonychid 8084 ppt

Wstęp do informatyki z architekturą systemów kompuerowych, Wstęp

Architekrura Systemów Lab1

Architekrura SystemAlw Lab5 (1) Nieznany

66 251103 projektant architekt systemow teleinformatycznych

tranzystory mosfet(1), Architektura systemów komputerowych, Sentenza, Sentenza

sciaga-skrocona, Informatyka Stosowana, Architektura systemów komputerowych, ASK

ukl 74xx, Informatyka PWr, Algorytmy i Struktury Danych, Architektura Systemów Komputerowych, Archit

Architektura systemów komputerowych przeliczanie systemów, Notatki

kol x86 IID GAK, studia wsiz, semestr 5, Architektora systemow lab

Architekrura Systemów Lab2

T 3 Architektura systemow komputerowych wytyczne

Architektura systemu

ASK, Informatyka Stosowana, Architektura systemów komputerowych, ASK

R5 Budowa mikroprocesora, Architektura Systemów Komputerowych

więcej podobnych podstron