1

Elementy cyfrowe i układy

logiczne

Wykład

2

2

2

2

Legenda

Zezwolenie

Dekoder, koder

Demultiplekser, multiplekser

2

3

3

3

3

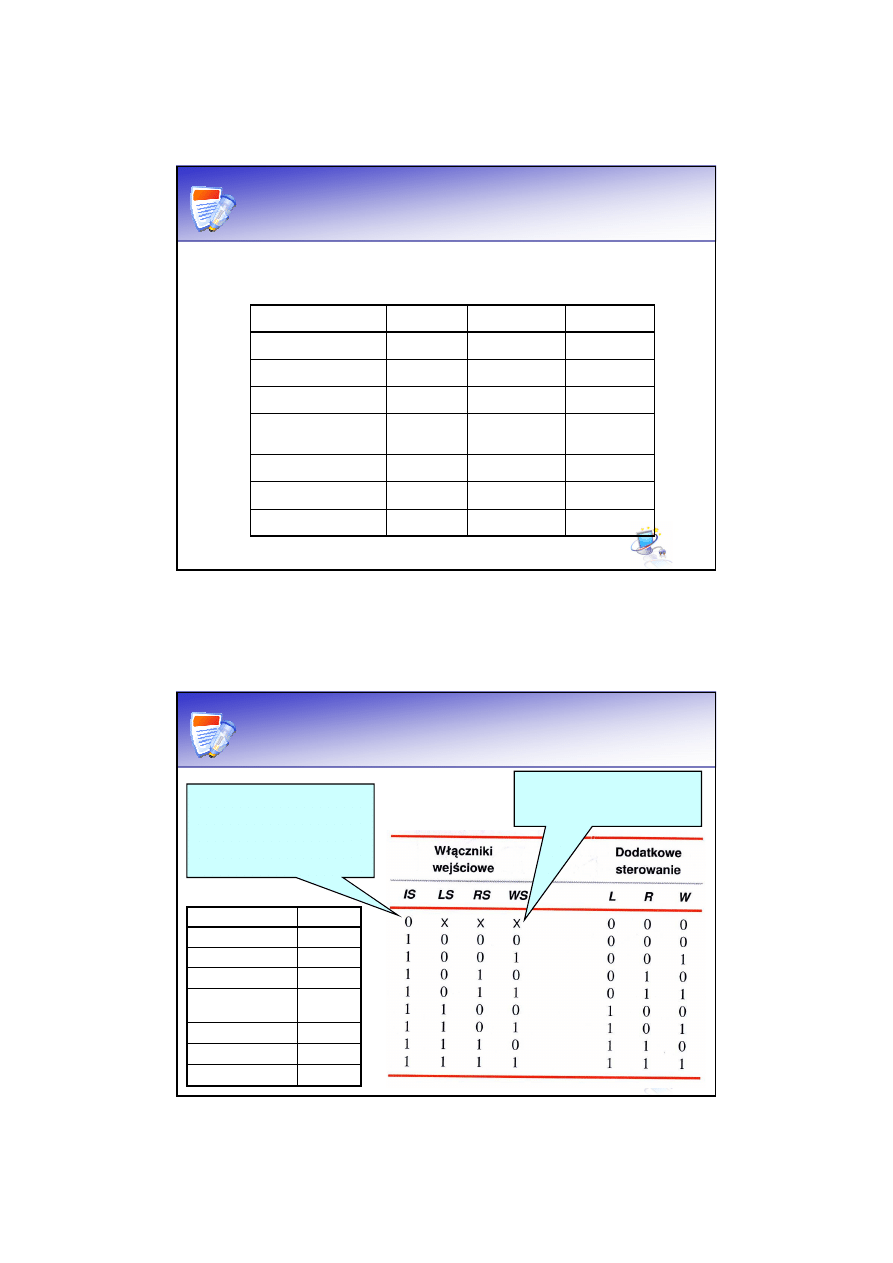

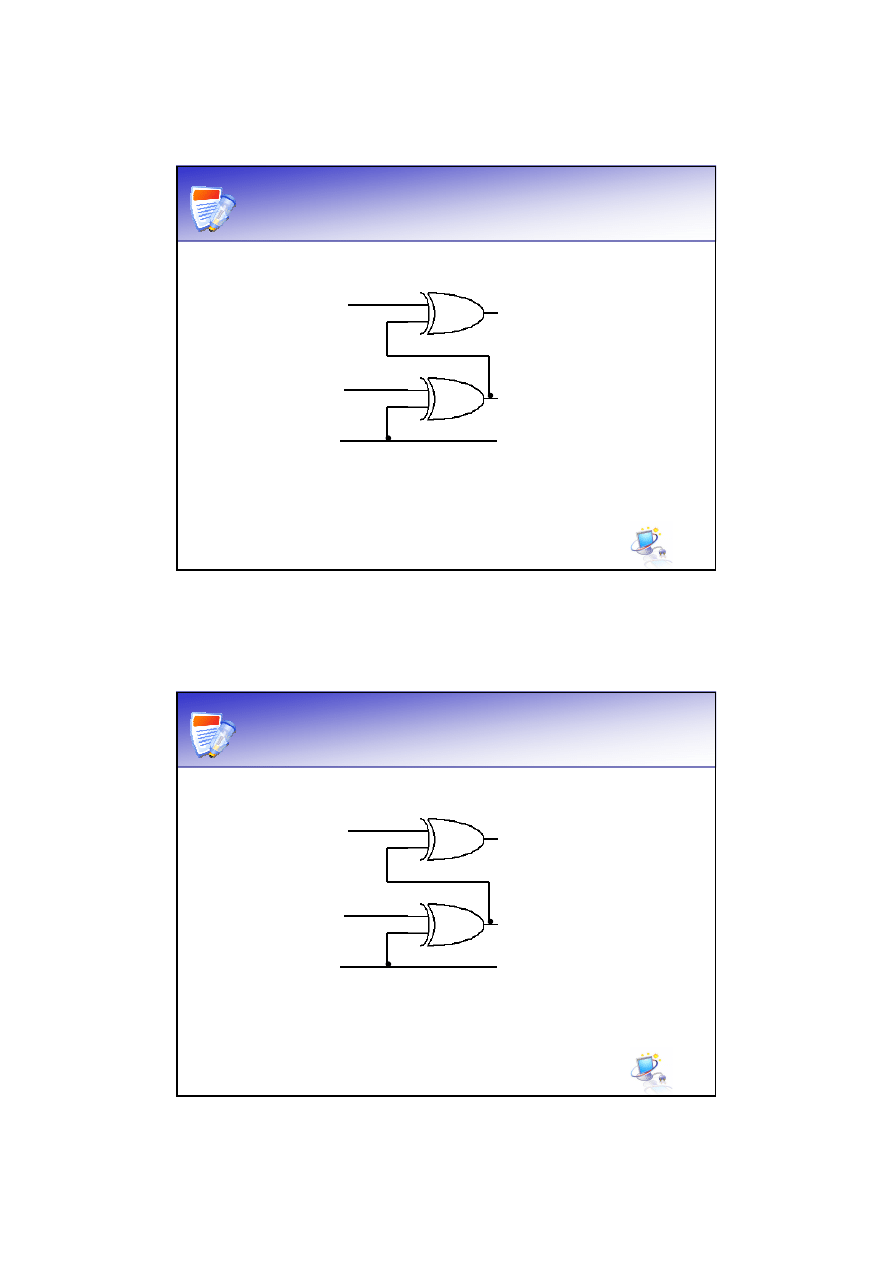

Operacja zezwolenia

Przykład:

zamodelować

podsystem

elektroniczny

samochodu do sterowania urządzeniami:

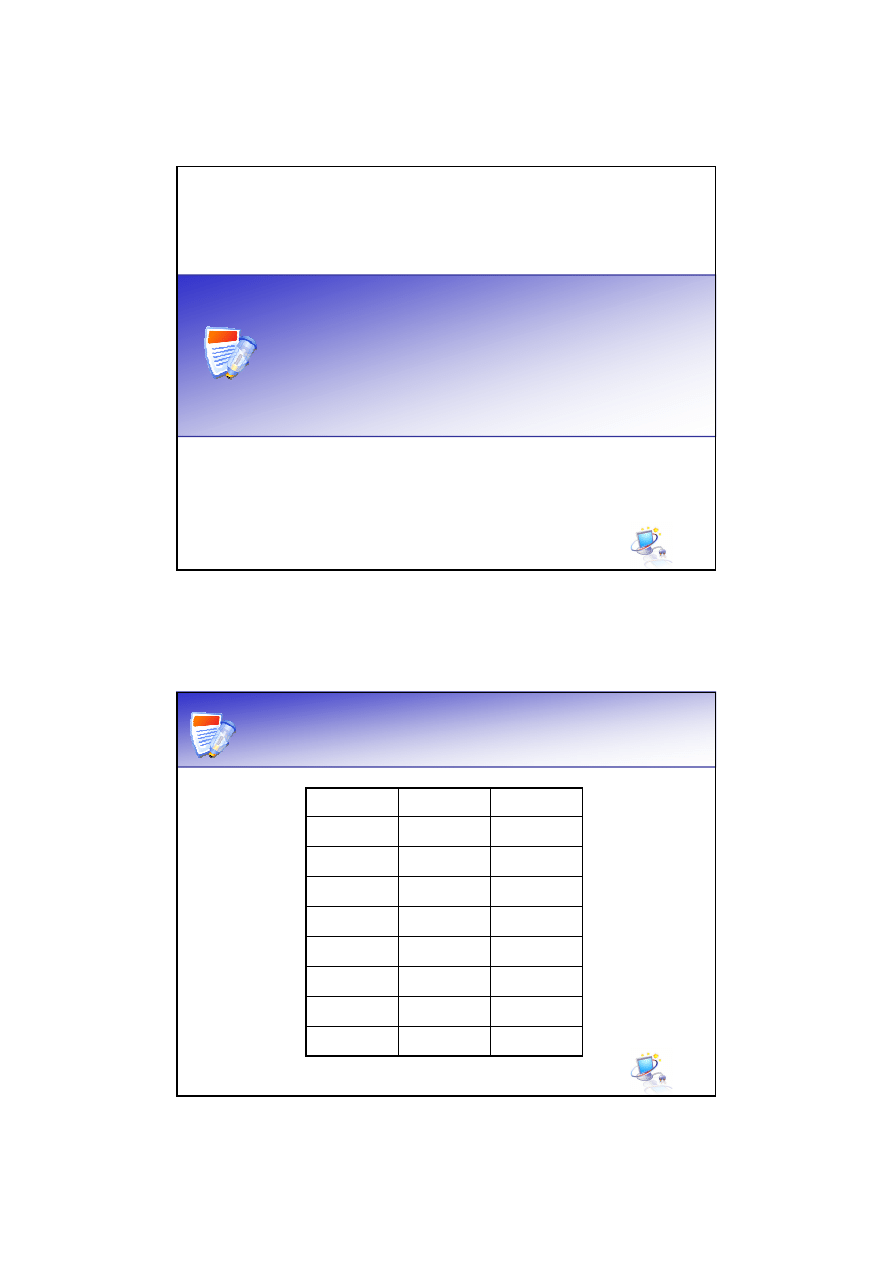

Nazwa

Zmienna Wyłączone Włączone

Wyłącznik zapłonu

IS

0

1

Wyłącznik świateł

LS

0

1

Wyłącznik radia

RS

0

1

Wyłącznik

ogrzewania szyb

WS

0

1

Światła

L

0

1

Radio

R

0

1

Ogrzewanie szyb

W

0

1

4

4

4

4

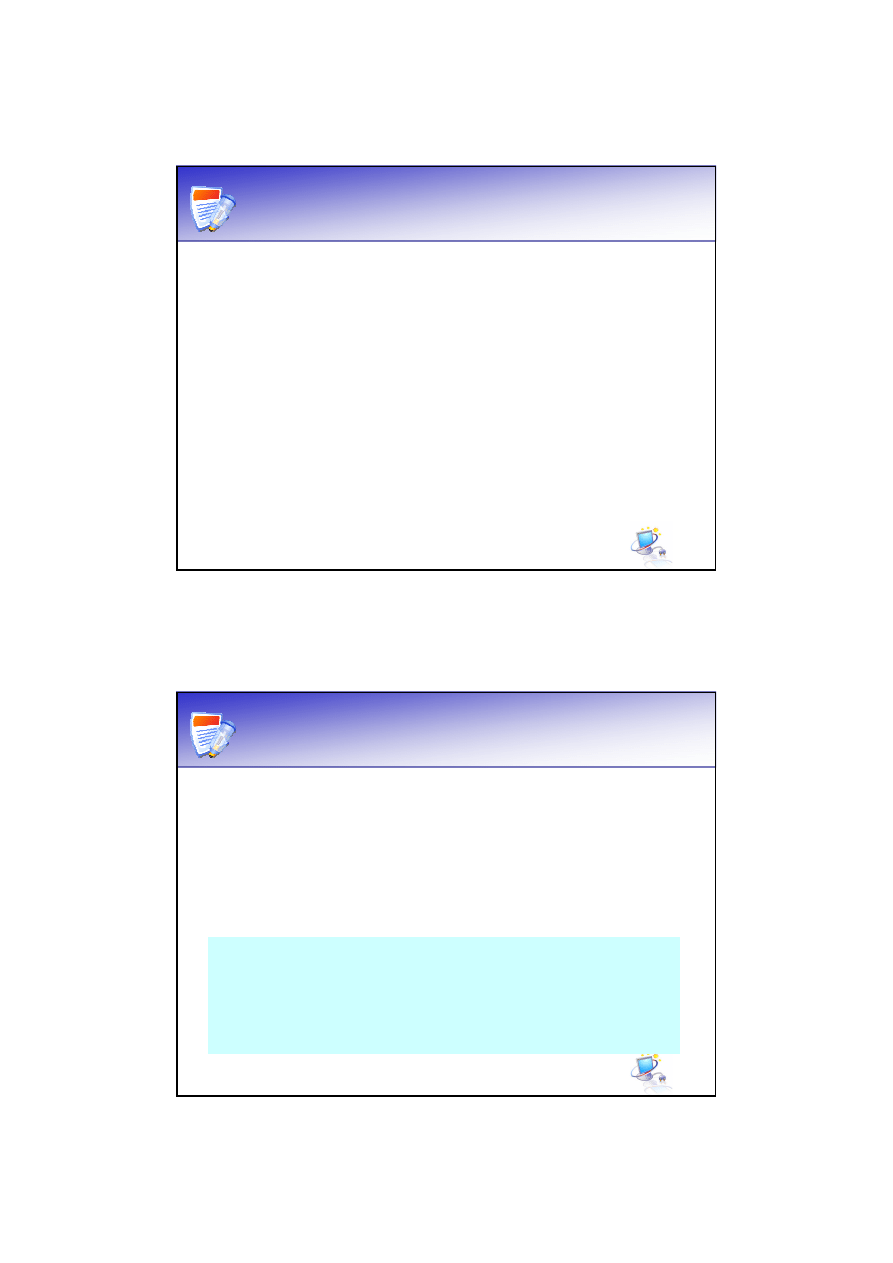

Operacja zezwolenia

x na wyjściu – don’t care

x na wejściu – zmienna nie

występuje w iloczynie

Enable

(0 – blokuje wszystko)

1 – „dopuszcza” akcję

Nazwa

Zmienna

Wyłącznik zapłonu

IS

Wyłącznik świateł

LS

Wyłącznik radia

RS

Wyłącznik

ogrzewania szyb

WS

Światła

L

Radio

R

Ogrzewanie szyb

W

3

5

5

5

5

Dekodowanie

• Dekodowanie

– konwersja n-bitowego kodu

wejściowego na m-bitowy kod wyjściowy, gdzie

n ≤ m ≤

2

n

, w taki sposób, że każde ważne słowo

kodowe tworzy niepowtarzalny kod wyjściowy.

6

6

6

6

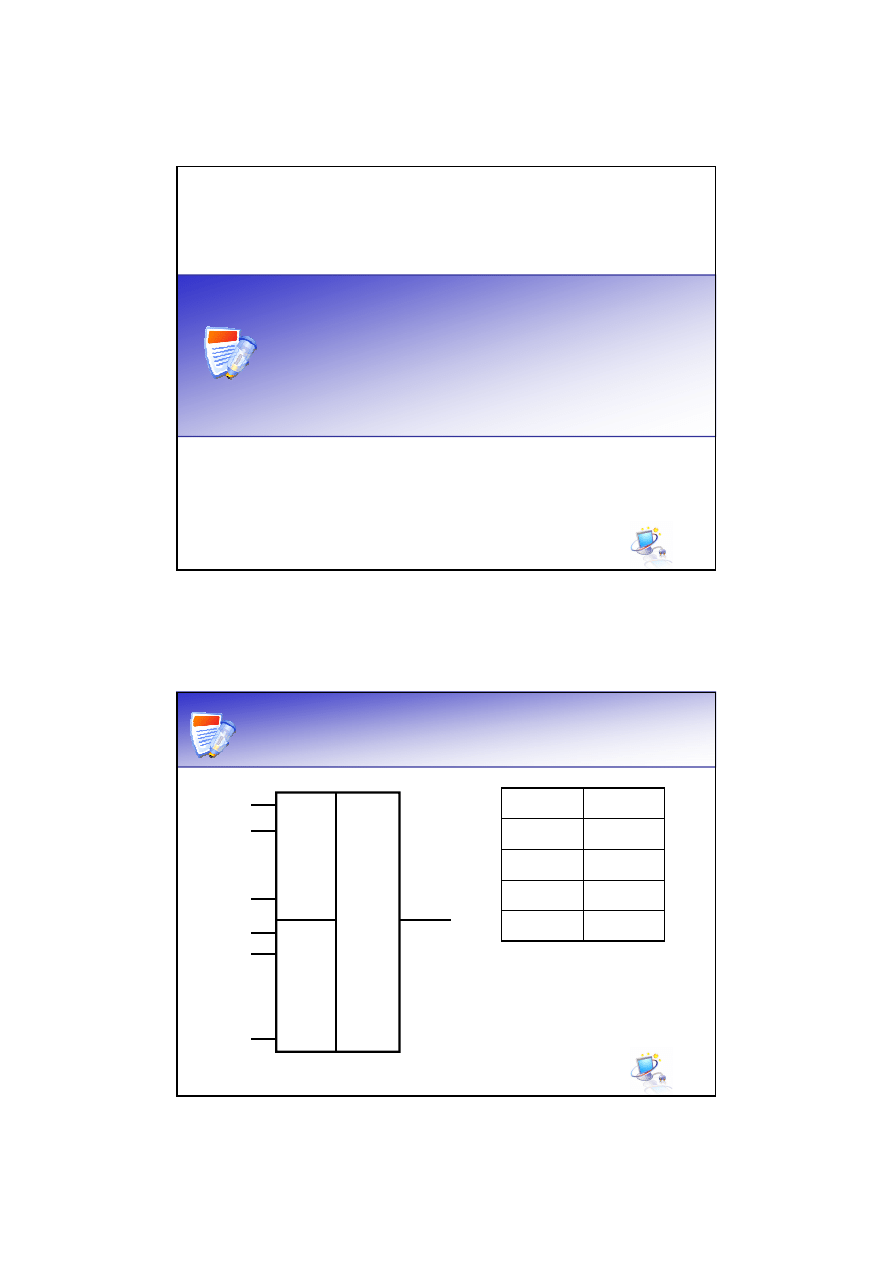

Dekoder

• Dekoder

należy

do

klasy

układów

kombinacyjnych.

• Układ posiadający n wejść oraz k wyjść (k=2^n).

Jego działanie polega na zamianie naturalnego

kodu binarnego (o długości n), lub każdego

innego kodu, na kod "1 z k" (o długości k). Działa

odwrotnie do kodera, tzn. zamienia kod binarny

na jego reprezentację w postaci tylko jednego

wybranego wyjścia. W zależności od ilości wyjść

nazywa się go dekoderem 1zN.

4

7

7

7

7

Dekoder

• Dekoder „n na m linii”, m ≤ 2

n

– generuje 2

n

lub

mniej mintermów z n zmiennych wejściowych.

8

8

8

8

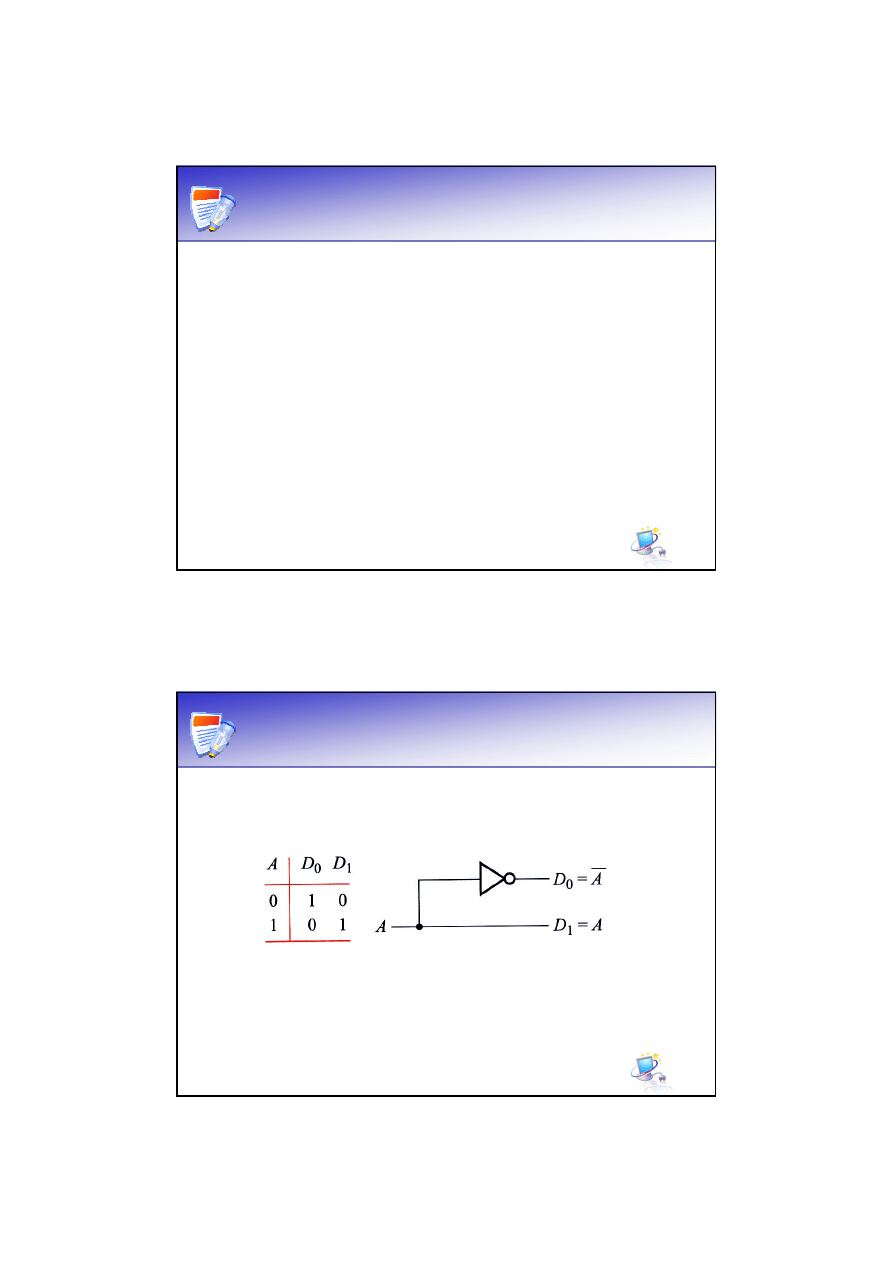

Dekoder „1 na 2 linie”

5

9

9

9

9

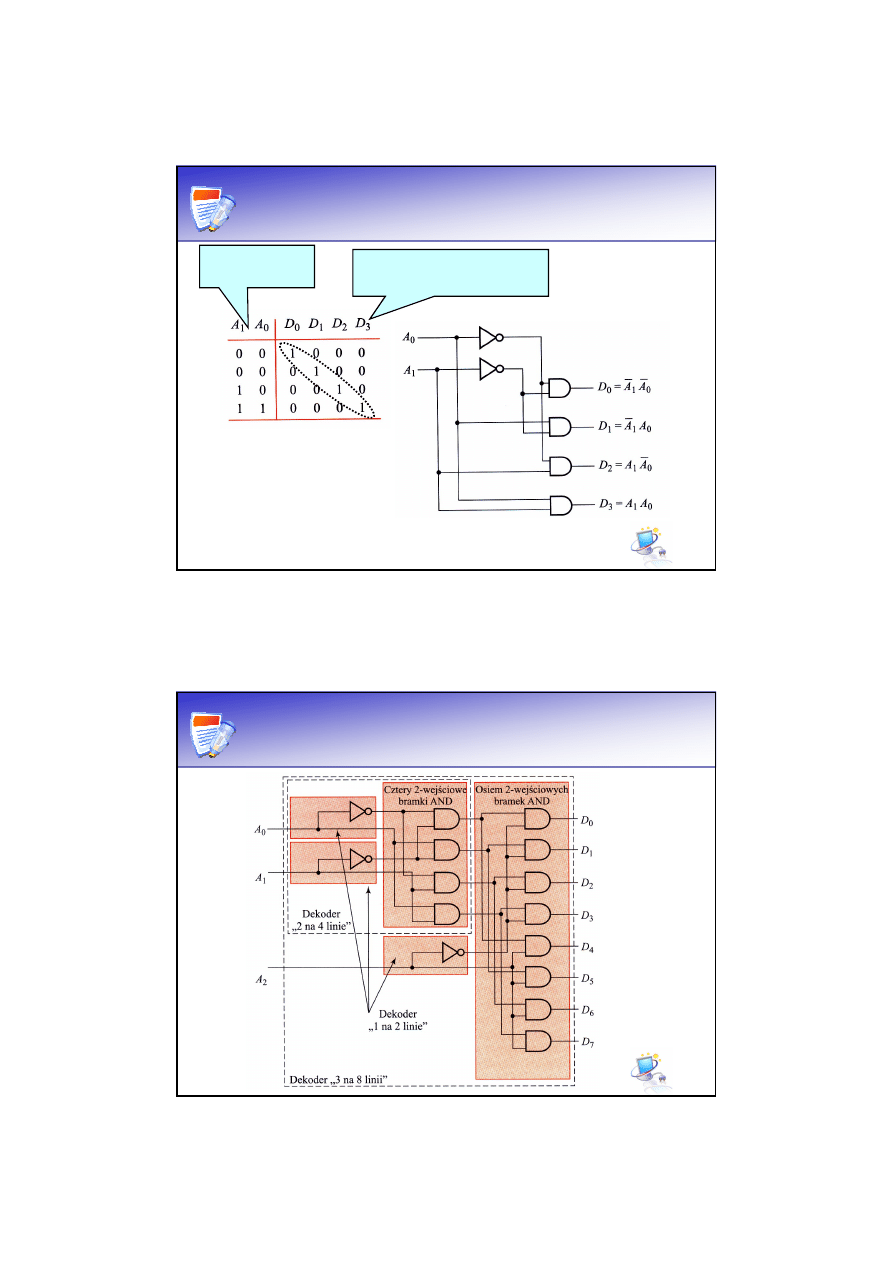

Dekoder „2 na 4 linie”

kod binarny

liczby i

D

i

– odpowiedź na

zadany kod wejściowy

10

10

10

10

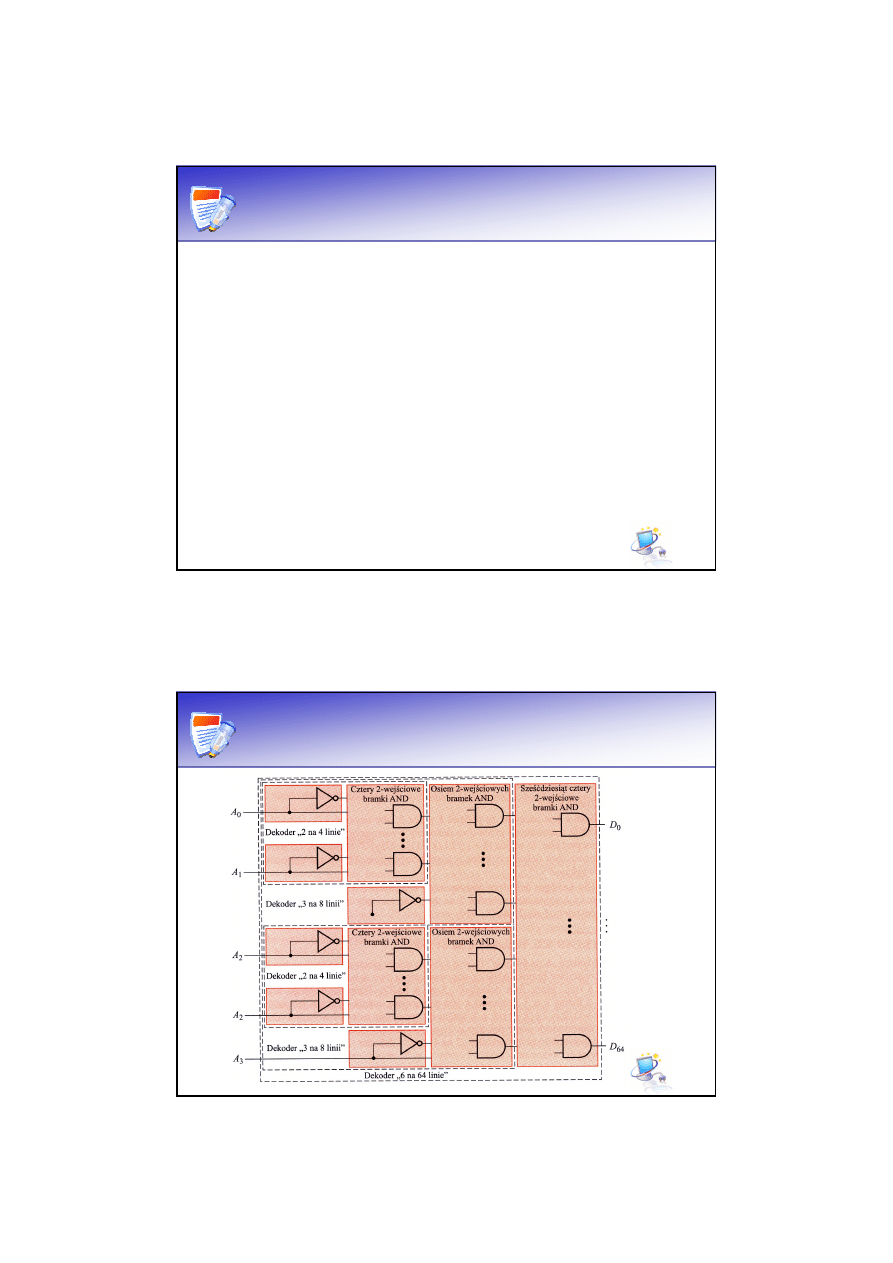

Dekoder „3 na 8 linii”

6

11

11

11

11

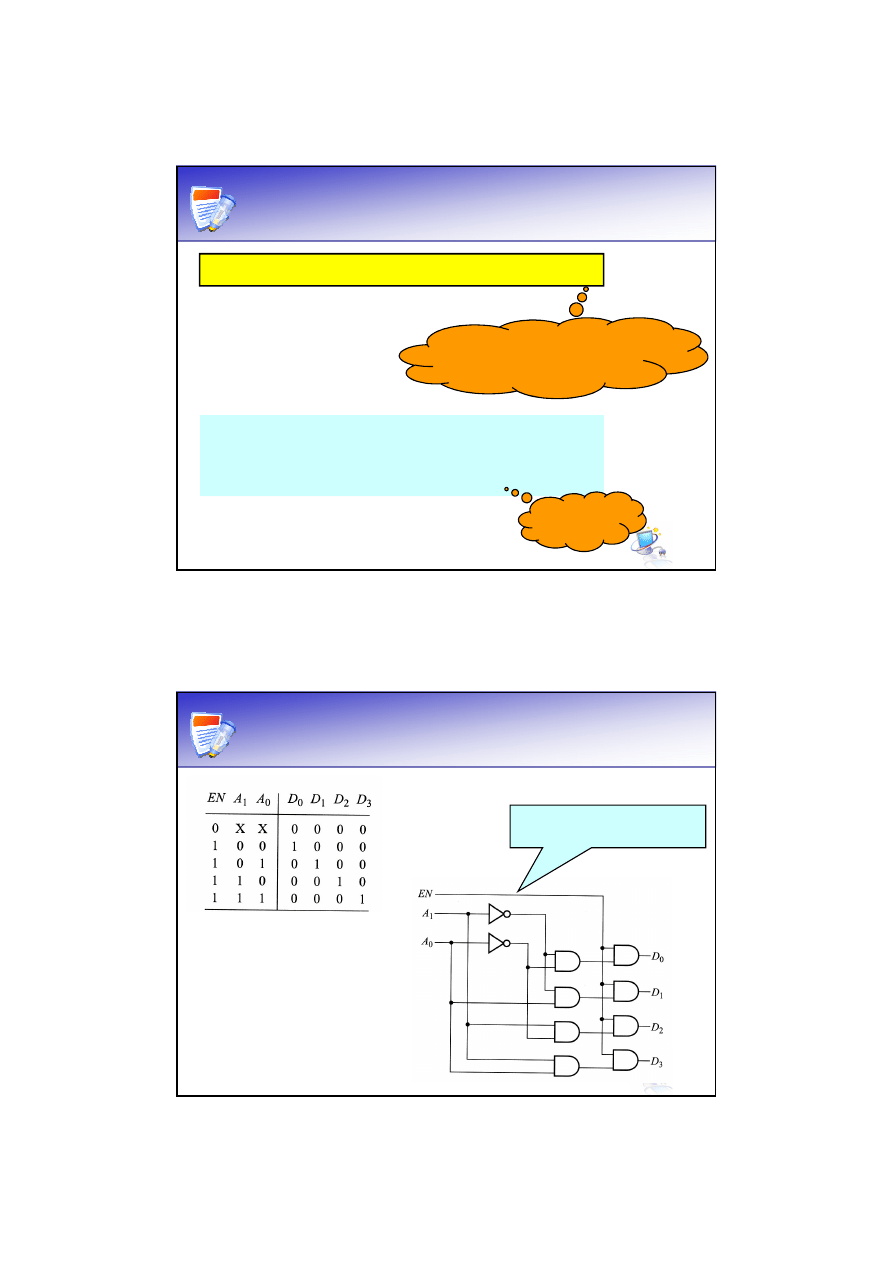

Rozbudowa dekoderów -

procedura

Krok 1:

Niech k = n.

Krok 2:

Jeśli k jest parzyste, to podziel k przez 2, aby

uzyskać k/2. Użyj 2

k

bramek AND sterowanych przez dwa

dekodery o rozmiarze wyjścia 2

k/2

. Jeśli k jest nieparzyste,

to oblicz (k +1)/2 i (k - 1)/2. Użyj 2

k

bramek AND

sterowanych przez dwa dekodery: jeden o rozmiarze

wyjścia 2

(k+1)/2

i drugi o rozmiarze wyjścia 2

(k-1)/2

.

Krok 3:

Dla każdego dekodera otrzymanego w punkcie 2

powtarzaj krok 2 dla wartości k uzyskanej w kroku 2 aż do

momentu, gdy k = 1 . Dla k = 1 zastosuj dekoder „1 na 2

linie”.

12

12

12

12

Dekoder „6 na 64 linie”

7

13

13

13

13

Rozbudowa dekodera

Liczba wejść bramkowych układu: K

b

= 182

Liczba wejść bramkowych układu przy użyciu

pojedynczych bramek AND dla każdego

mintermu: K

b

= 390

6+2(2*4)+2(2*8)+(2*64)

6+(6*64)

14

14

14

14

Demultiplekser

sygnał zezwolenia

8

15

15

15

15

Demultiplekser

Demultiplekser

umożliwia przesłanie do jednego z

wyjść układu sygnału doprowadzonego do jego wejścia.

Demultiplekser

jest

układem posiadającym jedno

wejście x, n wejść adresowych, oraz k wyjść (zazwyczaj

k=2

n

).

Numer wyjścia, do którego dołączone jest wejście,

określany jest przez podanie numeru na linie adresowe

a

0

... a

n-1

. Na pozostałych wyjściach panuje stan zera

logicznego.

16

16

16

16

Demultiplekser

Jeśli na wejście strobujące (blokujące) S (ang. strobe)

podane zostanie logiczne zero, to wyjścia y

i

przyjmują

określony stan logiczny (zazwyczaj zero), niezależny ani

od stanu wejścia x, ani wejść adresowych.

W praktyce spotykane są jedynie demultipleksery w

wyjściach zanegowanych, czyli na wybranym wyjściu

jest stan ~x a na wszystkich pozostałych 1. (jedynka)

logiczna.

9

17

17

17

17

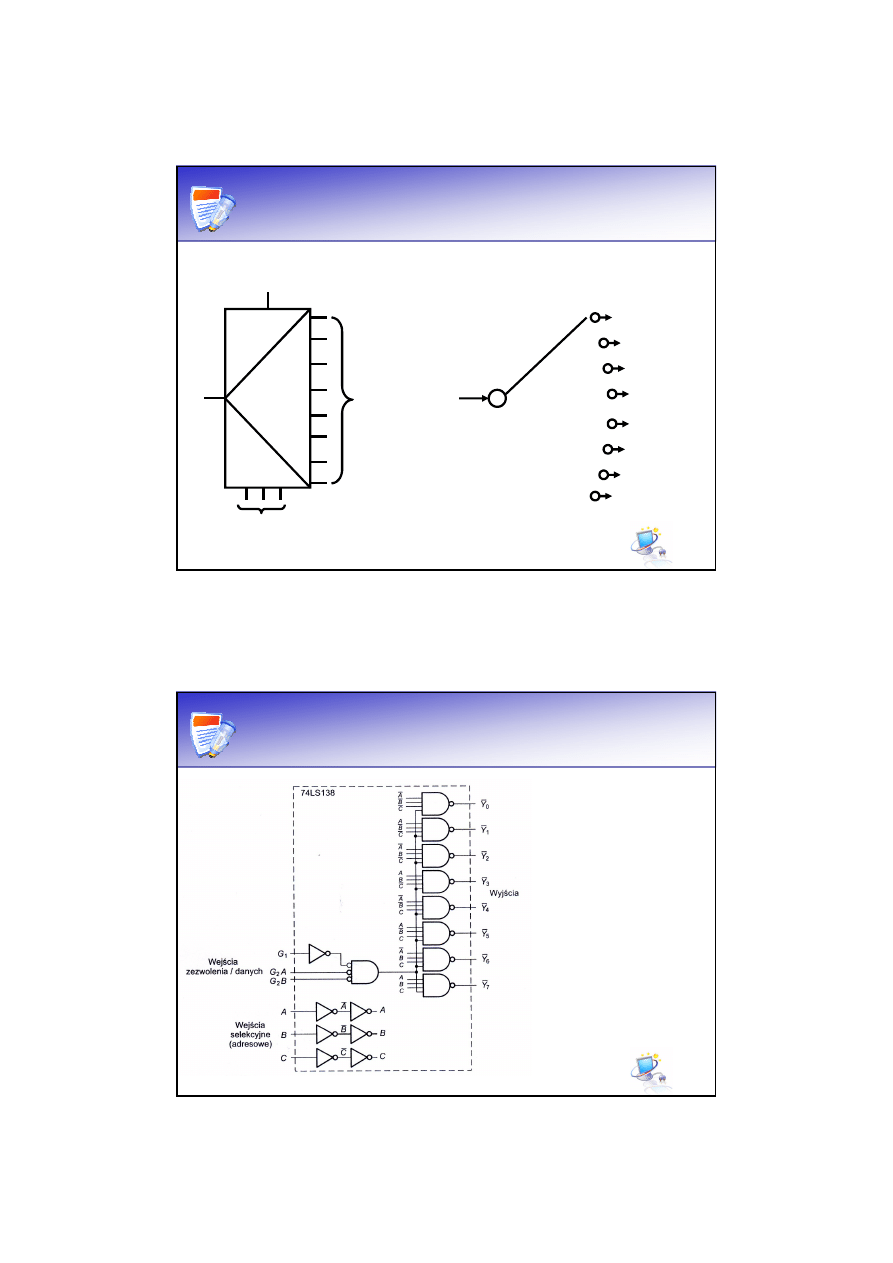

Demultiplekser

Wyjścia

danych

Wejścia

adresowe

Wejście strobujące

Model

mechaniczny

0

1

2

3

4

5

6

7

18

18

18

18

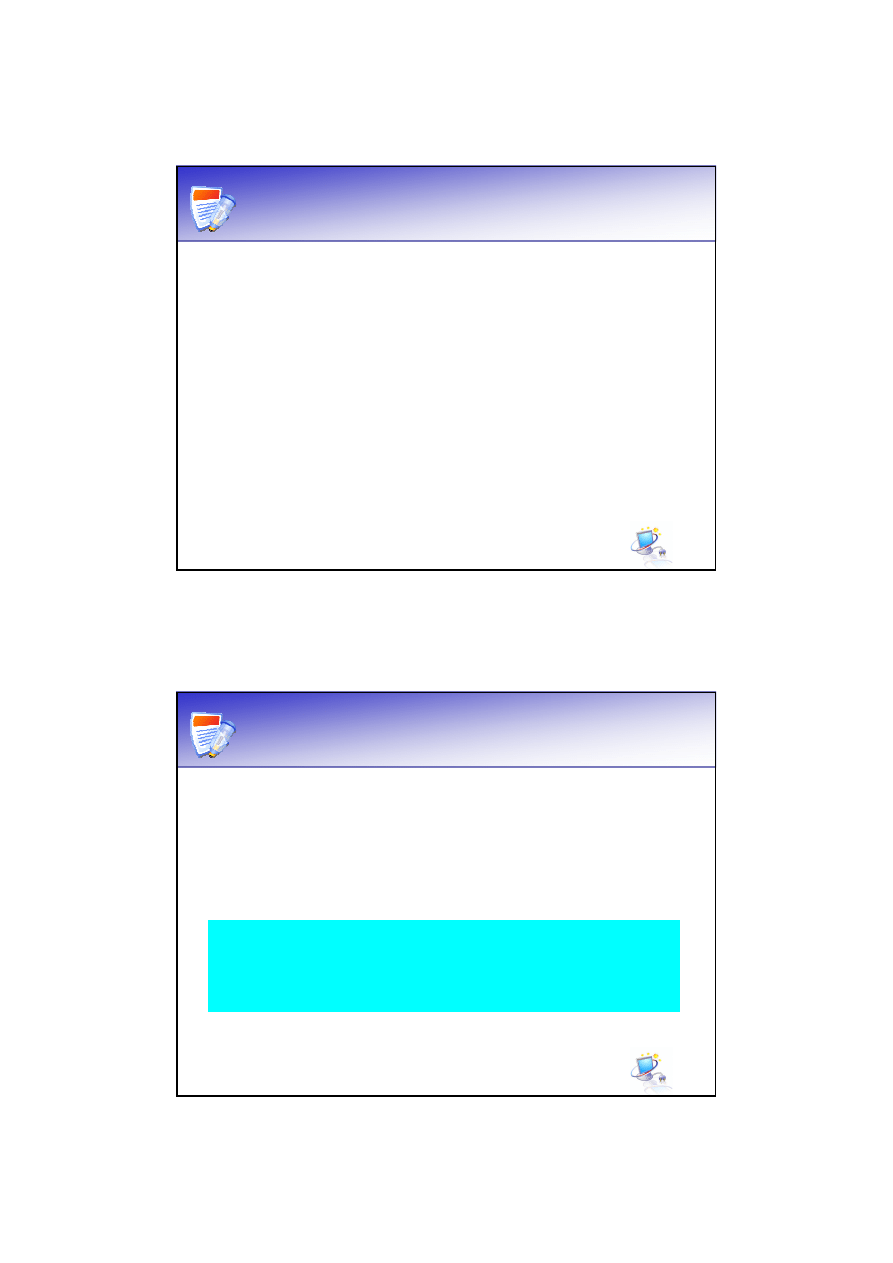

Demultiplekser

Demultiplekser (TTL,

74LS138

).

Wyjścia są

„inwersyjne” –

wybrane wyjście

zmienia stan z 1 (stan

nieaktywny) na 0,

pozostałe wyjścia

pozostają w stanie 1.

10

19

19

19

19

Koder

• Koder (enkoder)

– realizuje funkcję odwrotną do

operacji wykonywanej przez dekoder.

• Koder ma 2

n

(lub mniej) linii wejściowych i n

linii wyjściowych.

20

20

20

20

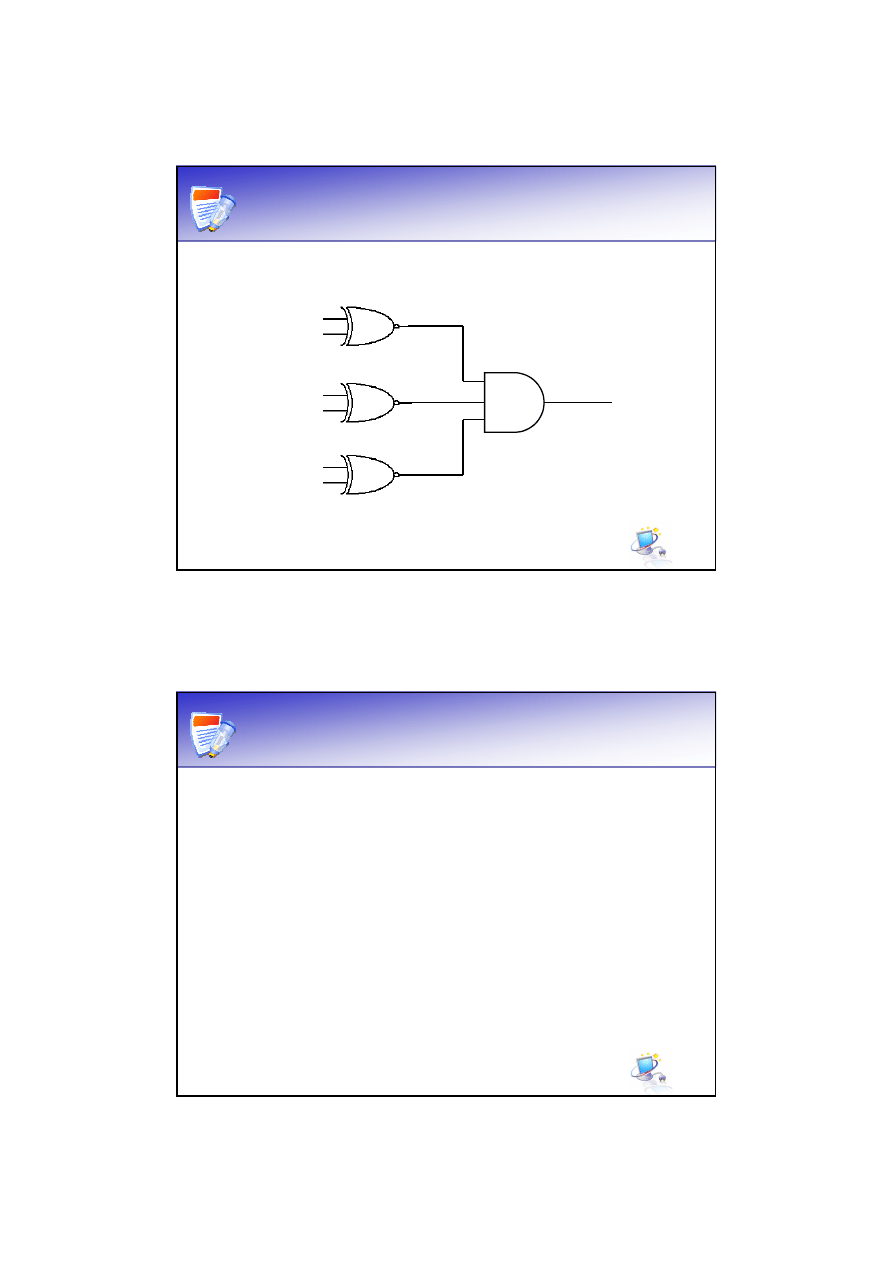

Koder priorytetowy

• Koder priorytetowy

(ang. priority enkoder) –

realizuje funkcję rozstrzygającą priorytet, czyli

pierwszeństwo sygnałów.

Jeśli dwa lub więcej wejść ma wartość równą 1

w tym samym czasie, to wejście mające

najwyższy priorytet ma pierwszeństwo.

11

21

21

21

21

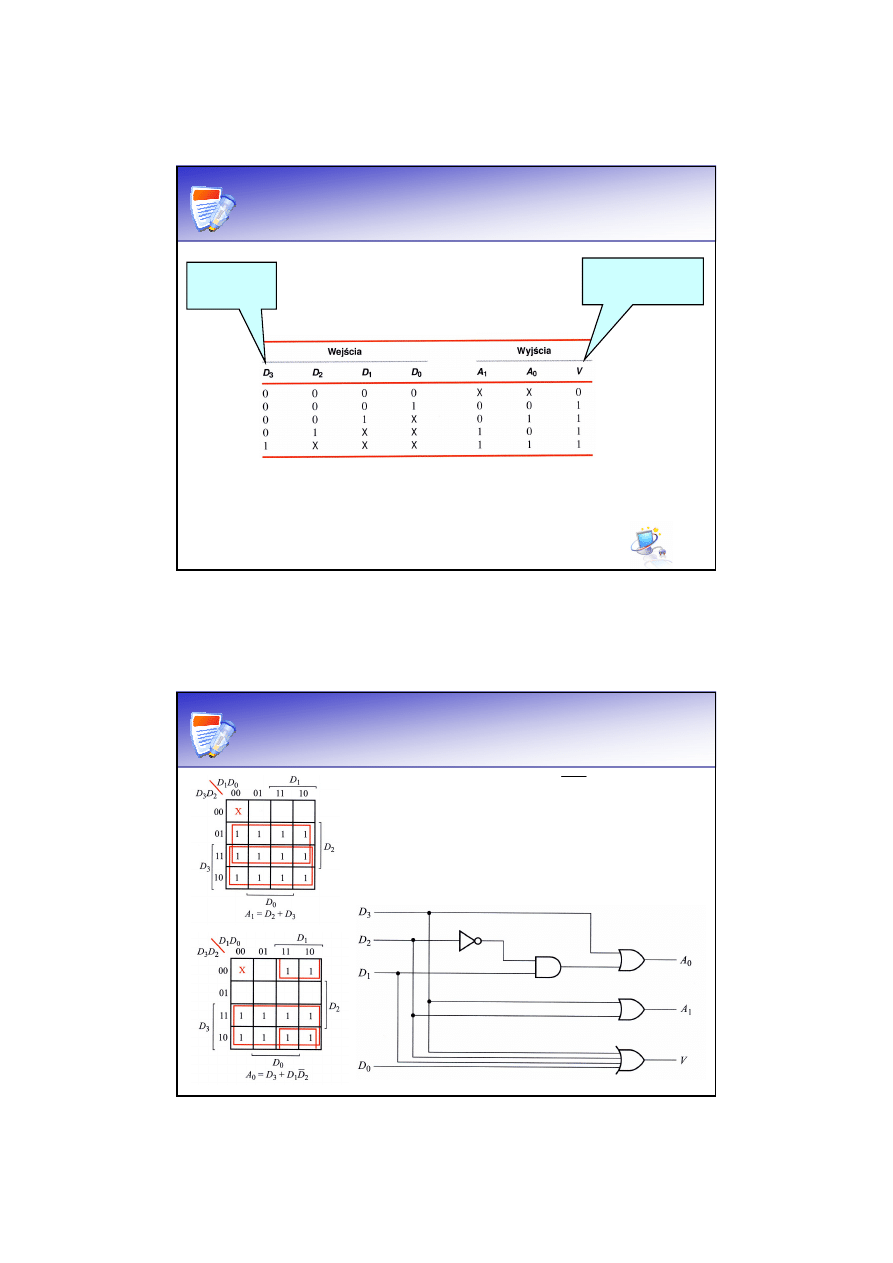

Koder priorytetowy

najwyższy

priorytet

wyjście

ważności kodu

22

22

22

22

4-wejściowy koder priorytetowy

2

1

3

0

D

D

D

A

+

=

3

2

1

D

D

A

+

=

3

2

1

0

D

D

D

D

V

+

+

+

=

12

23

23

23

23

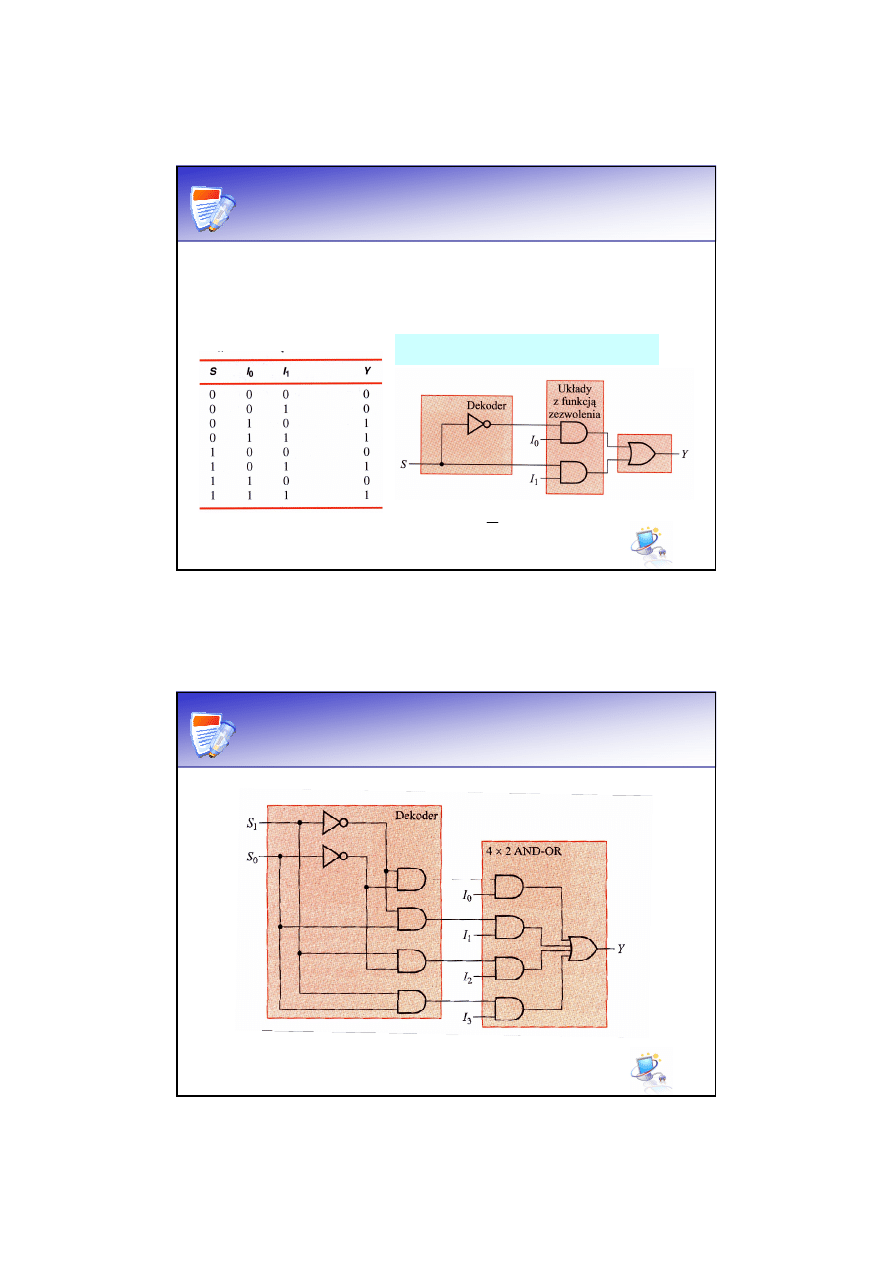

Multiplekser

Multiplekser

(MUX, selektor danych) – służy do

wyboru jednego z sygnałów wejściowych i przekazanie

go na wyjście układu.

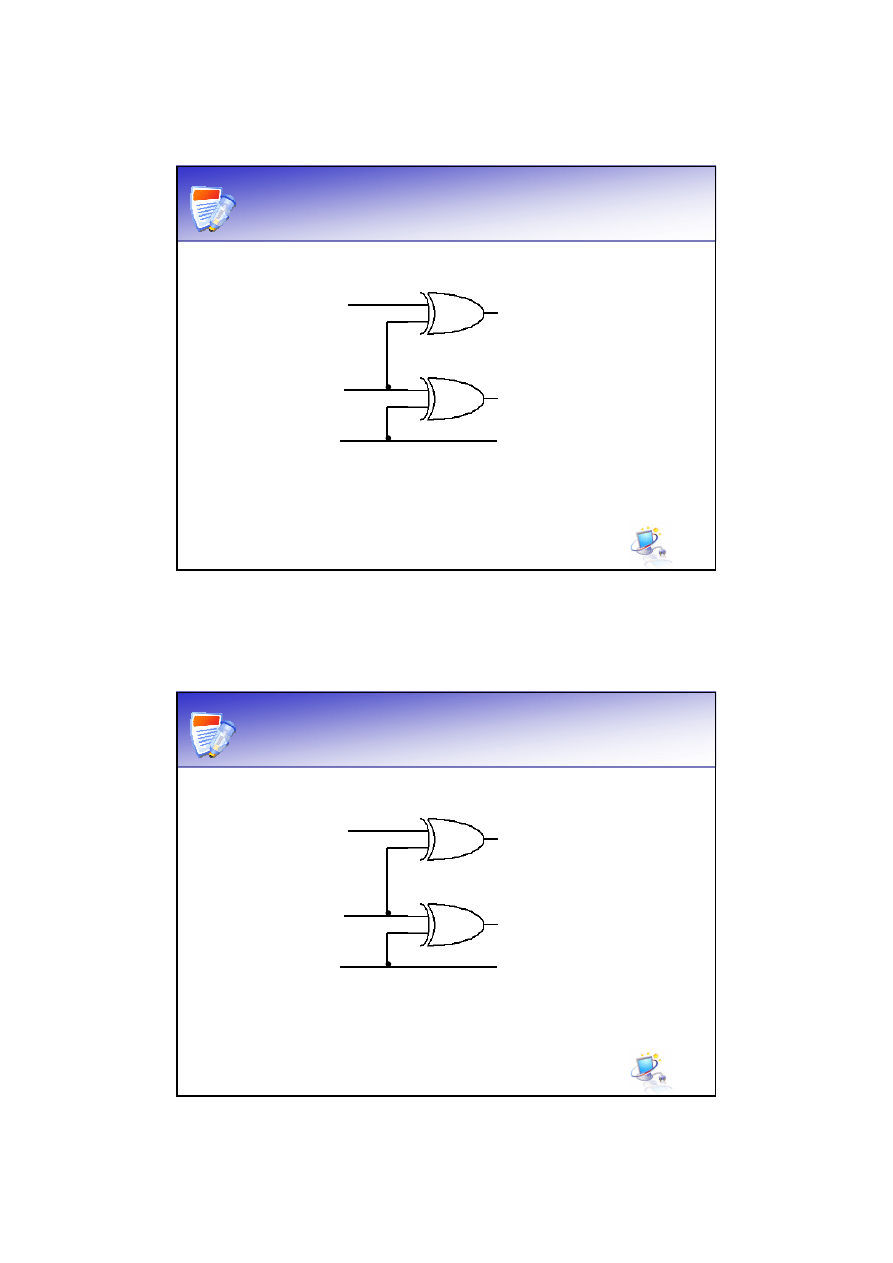

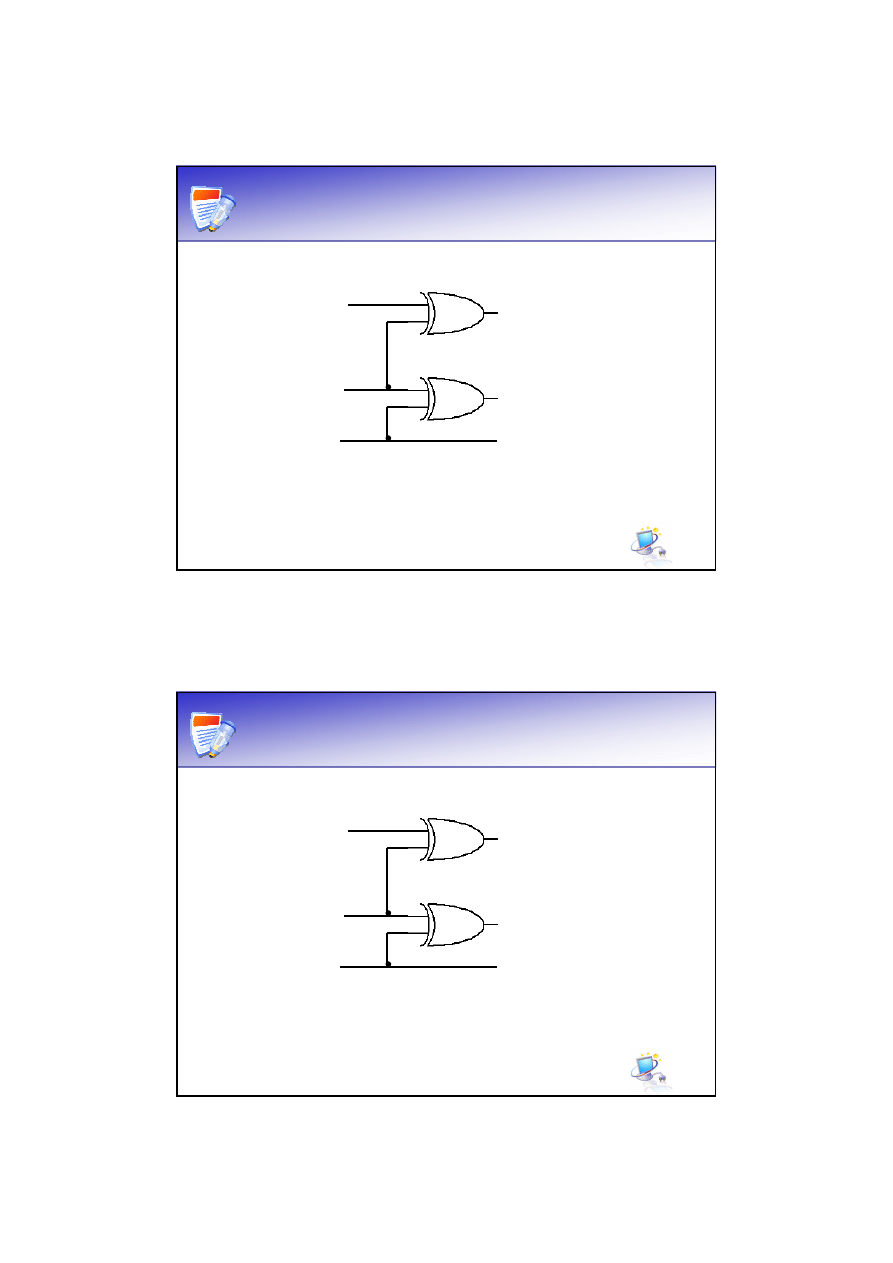

Multiplekser „2 na 1 linię”

1

0

SI

I

S

Y

+

=

24

24

24

24

Multiplekser „4 na 1 linię”

13

25

25

25

25

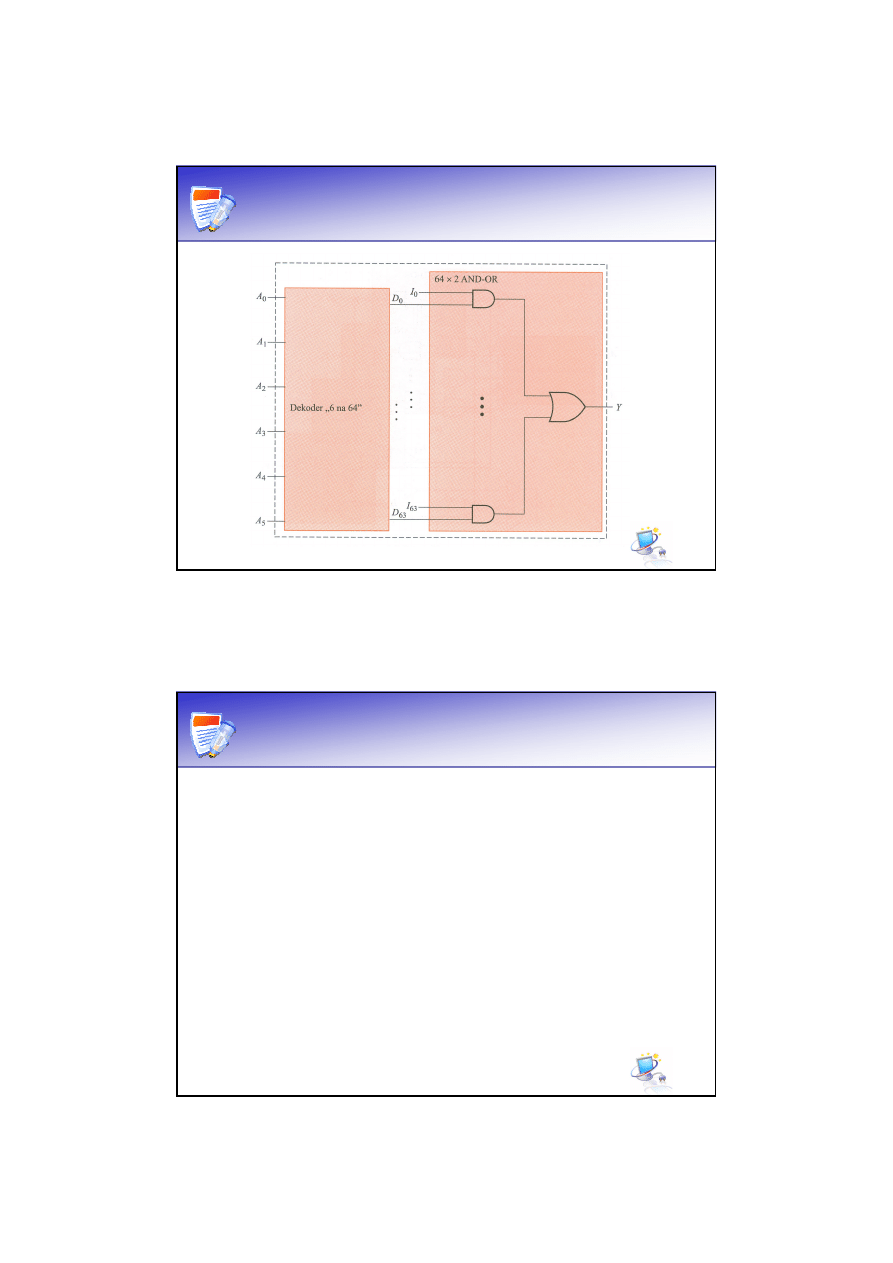

Multiplekser „64 na 1 linię”

26

26

26

26

Multiplekser

Multiplekser

jest układem posiadającym k wejść, n

wejść adresowych (zazwyczaj k=2

n

) i jedno wyjście y.

Jego działanie polega na połączeniu jednego z wejść x

i

z

wyjściem y. Numer wejścia jest określany przez

podanie jego numeru na linie adresowe A.

Jeśli na wejście strobujące (blokujące) S (ang. strobe)

podane zostanie logiczne zero, to wyjście y przyjmuje

określony stan logiczny (zazwyczaj zero), niezależny od

stanu wejść X i A.

14

27

27

27

27

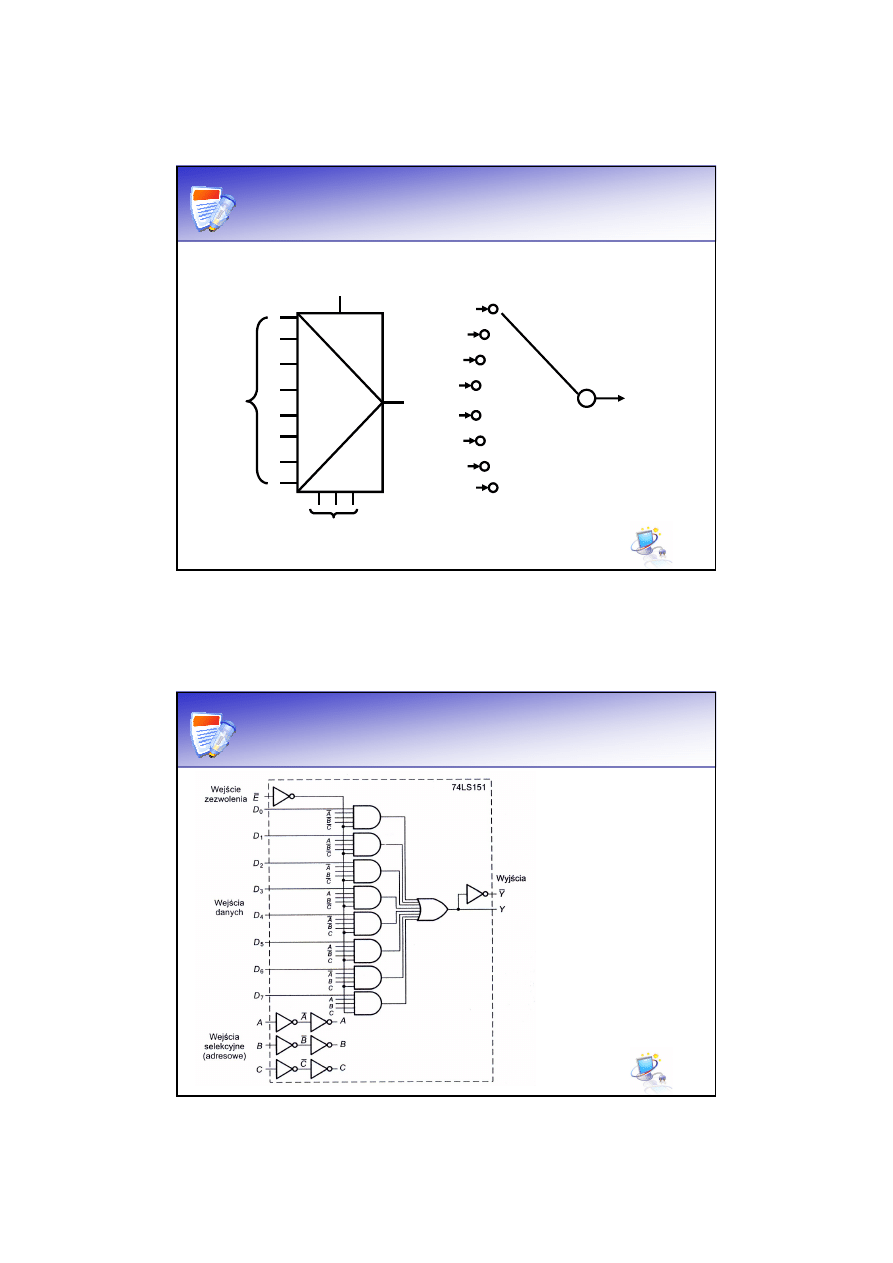

Multiplekser

Wejścia

danych

X

Wejścia

adresowe A

Wejście strobujące S

0

1

2

3

4

5

6

7

Model

mechaniczny

28

28

28

28

Multiplekser

8-bitowy multiplekser

(

74LS151

z rodziny

TTL) umieszczony w

obudowach

dwurzędowych 16-

wyprowadzeniowych,

posiada 2 wyjścia:

proste i zanegowane)

15

29

29

29

29

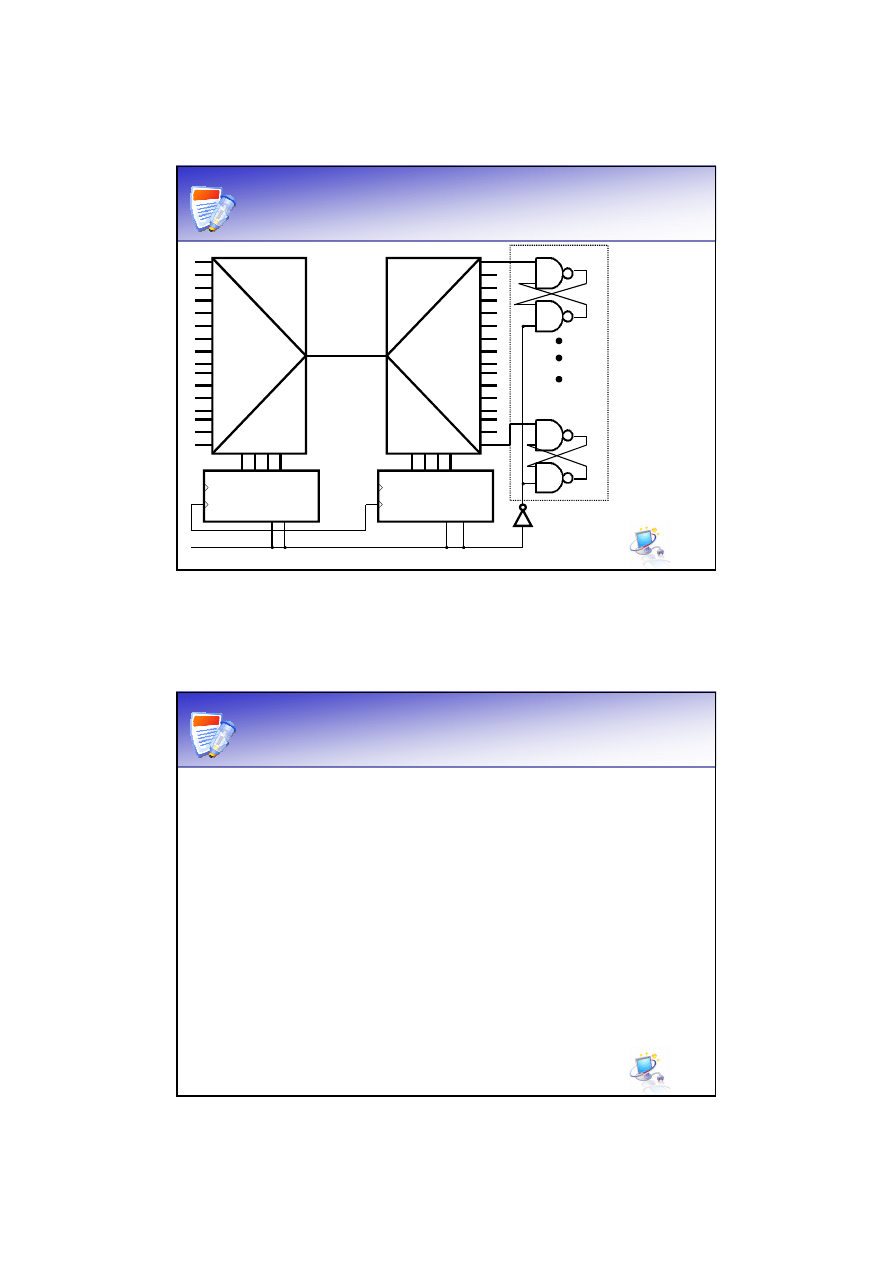

Multipleksowy sys. przesyłania danych

`150 Y

`154

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

Q

d

Q

c

Q

b

Q

a

R

01

R

02

Q

d

Q

c

Q

b

Q

a

R

01

R

02

B

we

A

we

B

we

A

we

Rejestr

D C B A

D C B A

Zegar

30

30

30

30

Cykl pracy układu

1. Wyzerowanie układu (przerzutniki wyjściowe, z których

składa się rejestr, ustawione w stan 1, liczniki w stan 0).

2. Ustawienie

na

wejściu

informacji

przeznaczonej

do

transmisji.

3. Podanie 16 impulsów na wejścia zliczające liczników

binarnych (mod 16) – z każdym kolejnym impulsem sygnał

z jednego z wejść jest przenoszony na odpowiednie wyjście

i jeśli jest to 1, to przerzutnik nie zmienia swego stanu, a

jeśli 0, to jest ustawiany w stan niski.

4. Informacja z wejścia znajduje się na wyjściu układu i

można przejść do następnego cyklu układu (punkt 1).

16

31

31

31

31

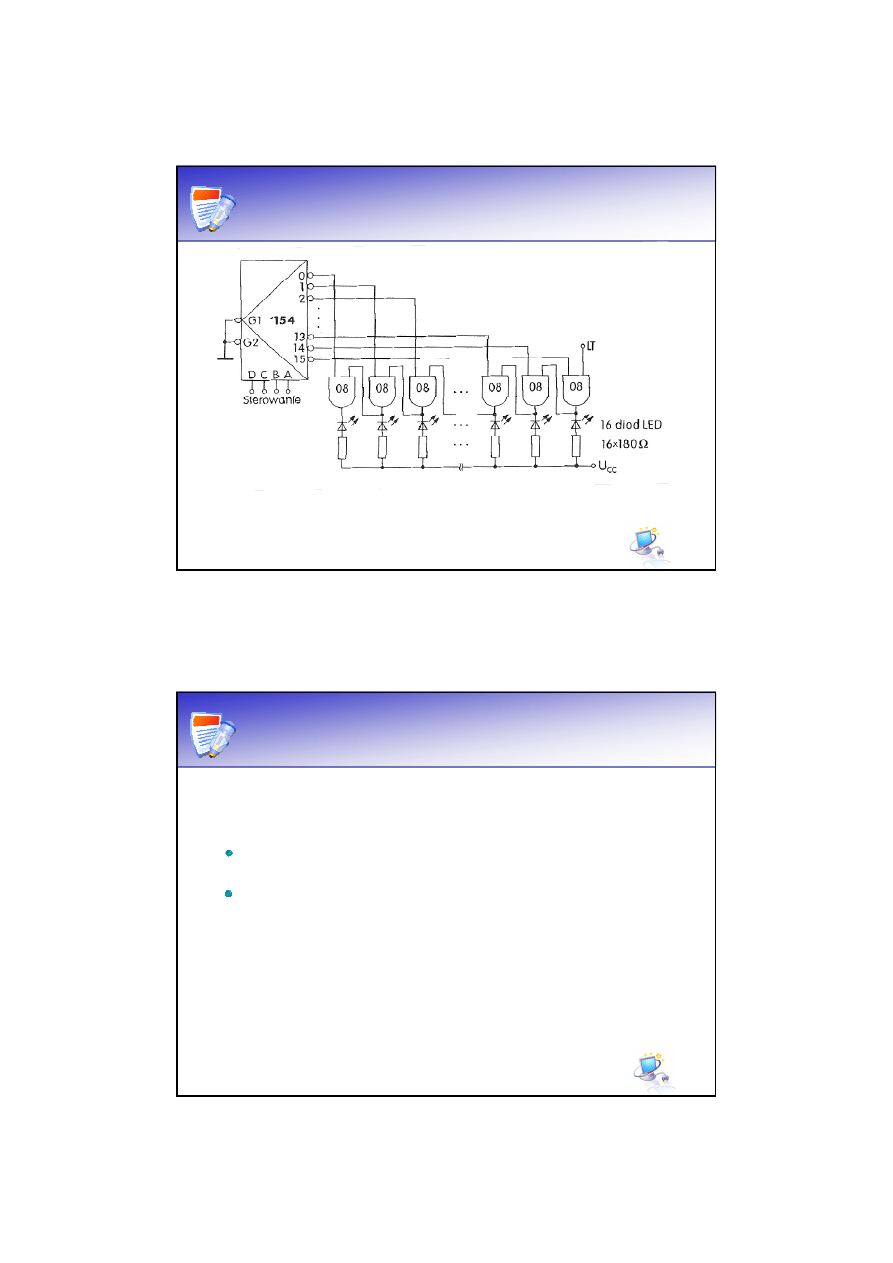

Linijka świetlna

Wybranie dowolnego wyjścia (słowem adresowym) powoduje świecenia sterowanej

przez to wyjście (za pośrednictwem bramki AND) diody oraz wszystkich diod

przyłączonych do wyjść o numerach mniejszych od wybranego. Wejście LT pozwala

skontrolować świecenie diod. Doprowadzenie do niego poziomu logicznego 0

powoduje świecenie wszystkich diod, niezależnie od stanu wejść adresowych.

32

32

32

32

Część 2:

Komparator

Zamiana kodu binarnego na kod Gray’a

17

33

33

33

33

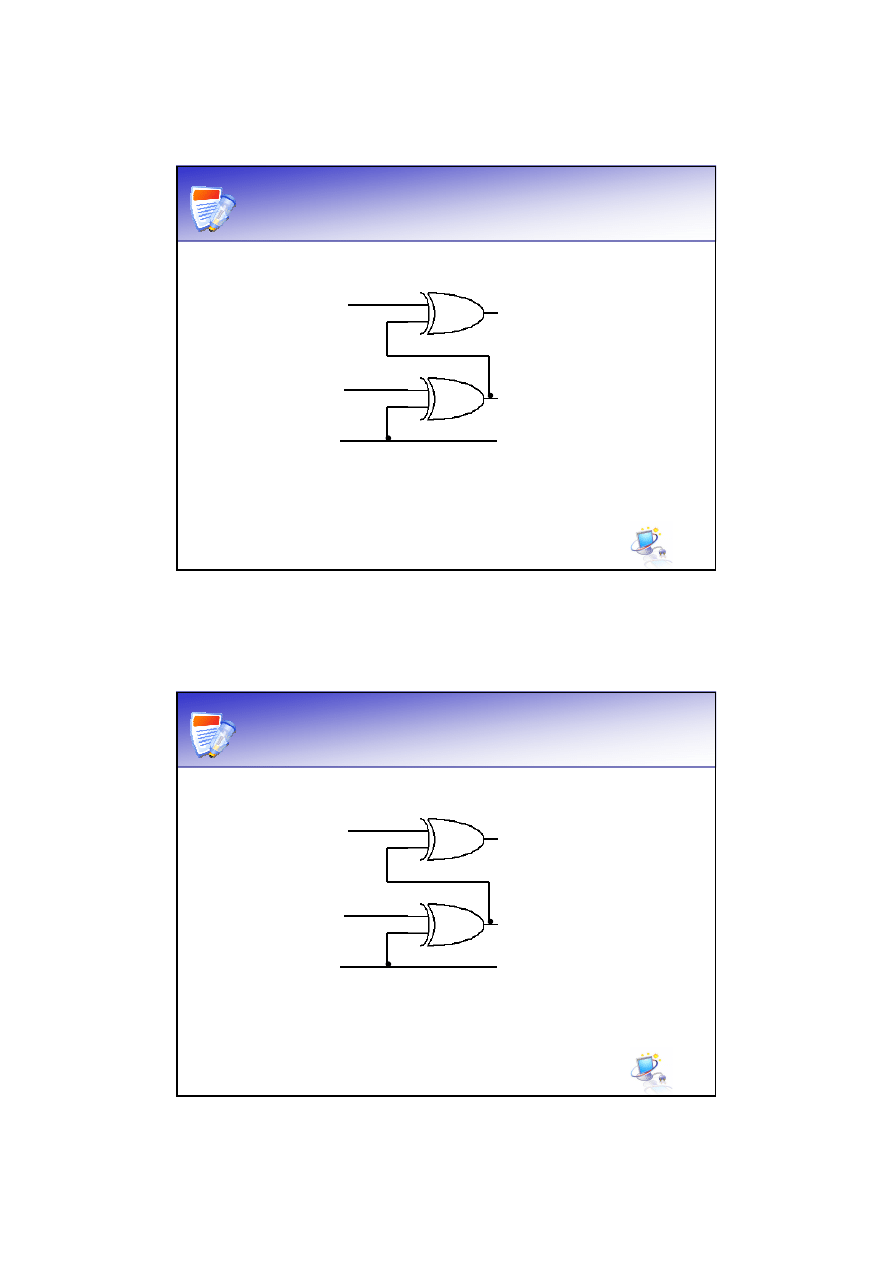

Zamiana kodu binarnego na

kod Gray’a

34

34

34

34

Zamiana c.d.

Dziesiętnie

Binarnie

Gray

0

000

000

1

001

001

2

010

011

3

011

010

4

100

110

5

101

111

6

110

101

7

111

100

18

35

35

35

35

Zamiana Bin-> Gray

x

0

x

1

x

2

g

0

g

1

g

2

36

36

36

36

Zamiana Bin-> Gray

0

0

0

0

0

0

Przykład 1/3

19

37

37

37

37

Zamiana Bin-> Gray

0

1

0

1

1

0

Przykład 2/3

38

38

38

38

Zamiana Bin-> Gray

1

1

0

0

1

0

Przykład 3/3

20

39

39

39

39

Zamiana Gray-> Bin

g

0

g

1

g

2

x

0

x

1

x

2

40

40

40

40

Zamiana Gray-> Bin

1

1

0

0

1

0

Przykład 1/3

21

41

41

41

41

Zamiana Gray-> Bin

1

0

0

1

0

0

Przykład 2/3

42

42

42

42

Zamiana Gray-> Bin

0

1

0

1

1

0

Przykład 3/3

22

43

43

43

43

Układ porównujący

44

44

44

44

Komparator

a0

a1

.

.

an

b0

b1

.

.

.

bn

= =

A= =B

?

a

i

b

i

A= =B

0 0

1

0 1

0

1

0

0

1

1

1

23

45

45

45

45

Komparator

Komparator to układ porównujący.

a

0

a

1

a

2

b

0

b

1

b

2

46

46

46

46

Koniec

Dziękuję za uwagę

Wyszukiwarka

Podobne podstrony:

ECiUL wyklad 1

ECiUL wyklad 6

ECiUL wyklad 3

ECiUL wyklad 8 testowanie

ECiUL wyklad 4

ECiUL wyklad 5

ECiUL wyklad 9 PLC

Napęd Elektryczny wykład

wykład5

Psychologia wykład 1 Stres i radzenie sobie z nim zjazd B

Wykład 04

geriatria p pokarmowy wyklad materialy

ostre stany w alergologii wyklad 2003

WYKŁAD VII

Wykład 1, WPŁYW ŻYWIENIA NA ZDROWIE W RÓŻNYCH ETAPACH ŻYCIA CZŁOWIEKA

Zaburzenia nerwicowe wyklad

więcej podobnych podstron