1

1

Architektura listy instrukcji – ISA

2

Zbiór poleceń (instrukcji) zrozumiałych dla CPU

–

lista instrukcji powinna być

funkcjonalnie pełna

, tzn.

umożliwiać zapis dowolnego algorytmu

Instrukcje są zapisywane w postaci binarnej

–

każda instrukcja ma swój unikatowy kod binarny (kod

operacji)

W programach źródłowych zapisanych w języku

asemblera zamiast kodów binarnych stosuje się

zapis symboliczny operacji

–

np. add, mov

Program źródłowy jest tworzony przy użyciu

edytora tekstu jako plik ASCII

Lista instrukcji

2

3

1.

Kod operacji (op code), określa czynność wykonywaną

przez instrukcję

2.

Wskazanie na argument źródłowy (source operand)

3.

Wskazanie na argument docelowy (destination operand)

4.

Wskazanie na kolejną instrukcję programu, która ma być

wykonana jako następna

Przykład: mov a,r0 ;prześlij r0 do a

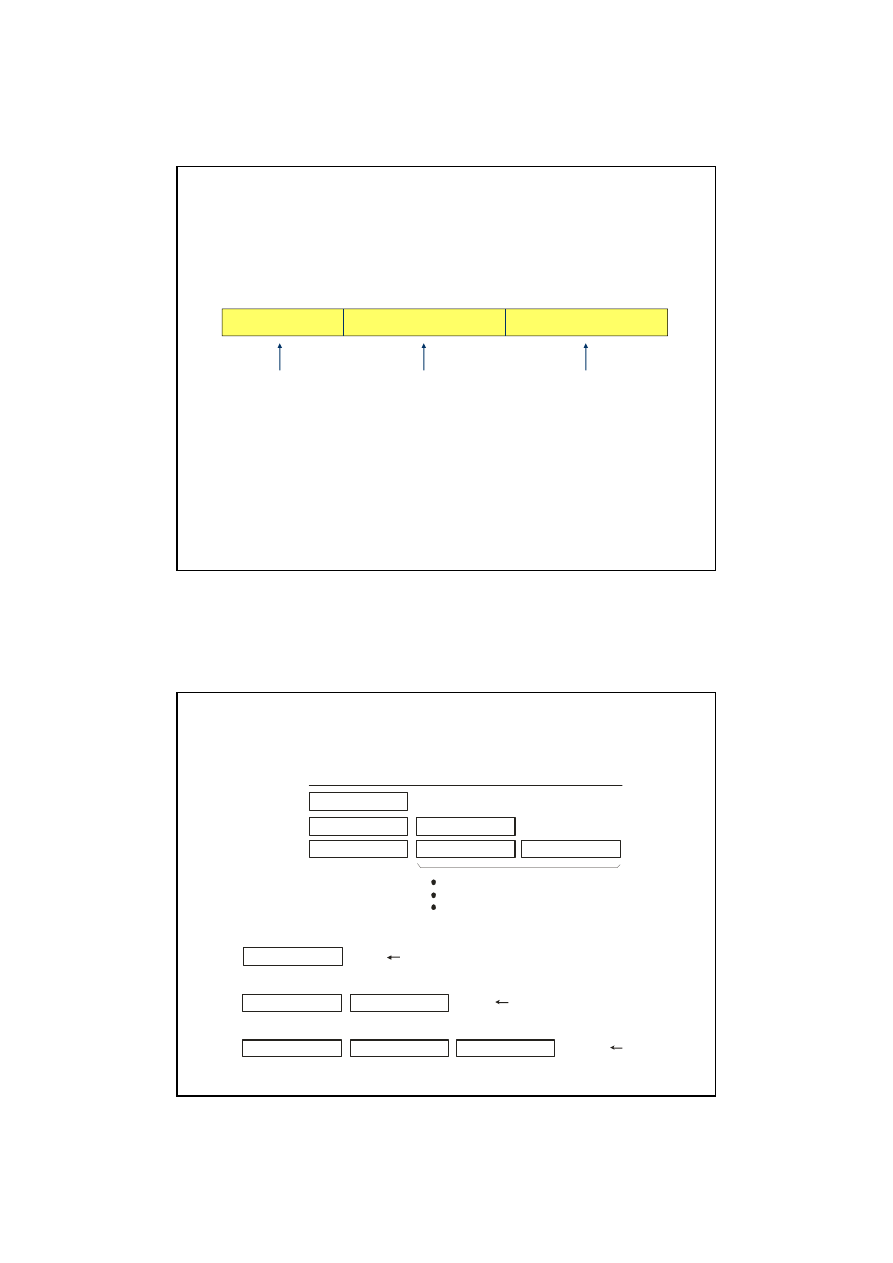

Elementy instrukcji

Mnemonik

(rodzaj operacji)

Argument źródłowy

Argument

docelowy

Element 1) jest obligatoryjny, elementy 2) – 4) są opcjonalne

4

Reprezentacja instrukcji

Postać symboliczna (język asemblera)

mov a,r0

Zapis funkcjonalny

a r0

Postać binarna w pamięci programu (x51)

11101000

w postaci binarnej kod operacji jest zapisywany jako

pierwszy, dalej następują argumenty (w tym przypadku

informacja o argumentach jest zawarta w kodzie

operacji)

3

5

Reprezentacja instrukcji

cd.

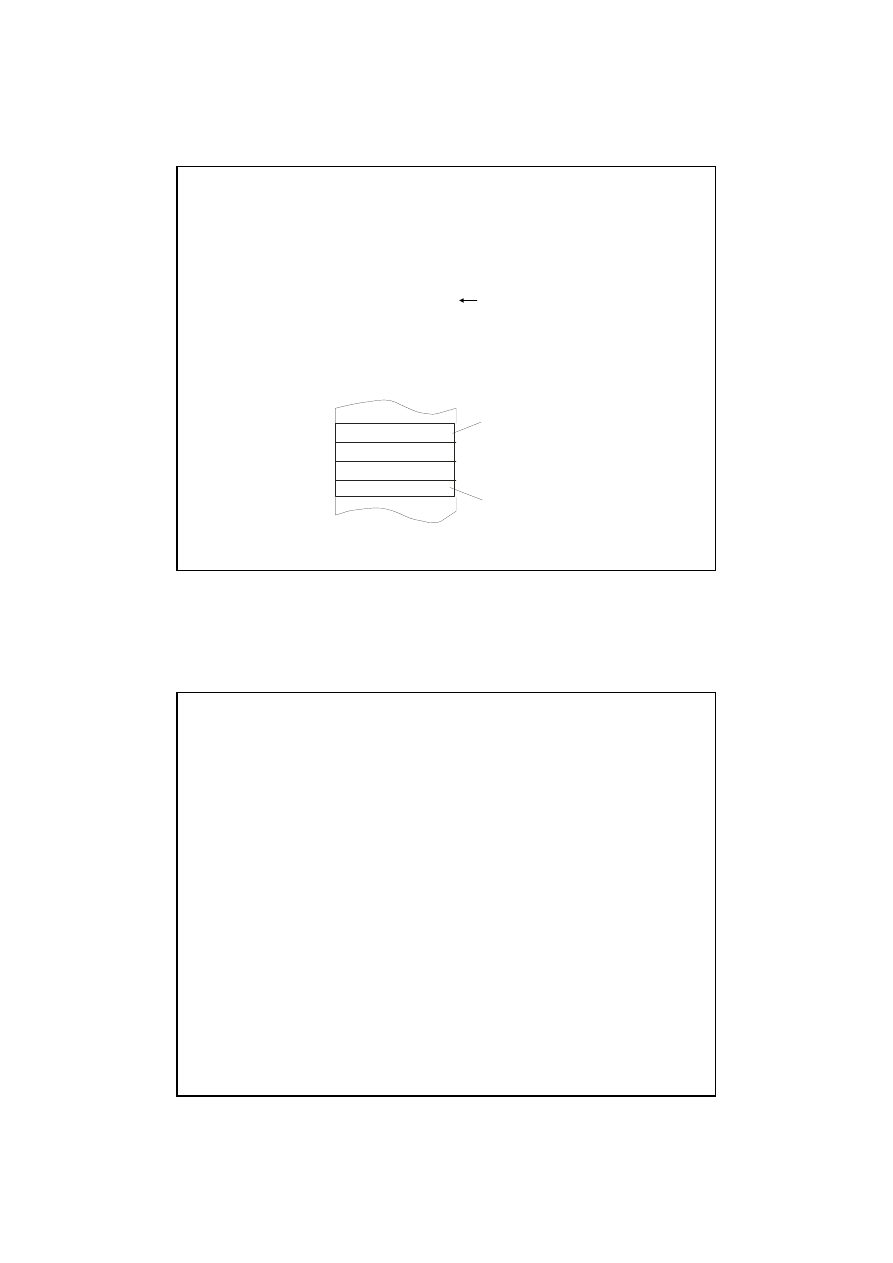

Przykład (x51)

–

Zapis symboliczny

add a,#3ch

–

Zapis funkcjonalny

(a) (a)+#3ch

–

Opis słowny: dodaj liczbę 3c w kodzie szesnastkowym do

zawartości akumulatora

–

Postać instrukcji w pamięci:

Kod operacji ADD

Dodajnik 3CH

Adres x

Adres x+1

Następna instrukcja

P oprzednia instrukcja

0 0 1 0 0 1 0 0

0 0 1 1 1 1 0 0

. . .

. . .

6

Istotnym czynnikiem przy projektowaniu ISA jest liczba

argumentów (lub odniesień do argumentów) zawartych w

instrukcji

–

wpływ na długość słowa instrukcji oraz złożoność CPU

–

duża liczba argumentów wymaga długiego słowa instrukcji

Rozważmy, ile argumentów wymaga instrukcja

dodawania ADD

–

jeśli chcemy dodać do siebie zawartość dwóch komórek pamięci

potrzebujemy

dwóch

adresów

–

gdzie umieścić wynik dodawania? Potrzebny jest

trzeci

adres

–

która instrukcja w programie ma być wykonana jako następna?

zwykle domyślnie przyjmuje się, że będzie to kolejna instrukcja w

programie, ale czasem chcemy wykonać skok w inne miejsce

programu

do wskazania miejsca skoku potrzebny jest

czwarty

adres

Liczba argumentów

4

7

Liczba argumentów

cd.

W praktyce procesory czteroadresowe nie są

stosowane

–

zbyt skomplikowana budowa CPU

–

długie słowo instrukcji

–

nie zawsze instrukcja wymaga aż czterech adresów

Większość instrukcji wymaga jednego, dwóch

lub najwyżej trzech adresów

–

adres kolejnej instrukcji w programie jest określany

przez inkrementację licznika rozkazów (z wyjątkiem

instrukcji skoków)

8

Więcej adresów

–

bardziej skomplikowane, ale też wygodne w użyciu

instrukcje

–

dłuższe słowo instrukcji

–

większa liczba rejestrów

operacje na rejestrach są szybsze niż operacje na zawartości

pamięci

–

krótsze programy (w sensie liczby instrukcji)

Mniej adresów

–

mniej skomplikowane instrukcje

–

dłuższe programy (w sensie liczby instrukcji)

–

krótszy cykl pobrania instrukcji

Większość współczesnych procesorów stosuje

architekturę

–

2-adresową (x51, x86)

–

3-adresową (MIPS)

Liczba adresów – wnioski

5

9

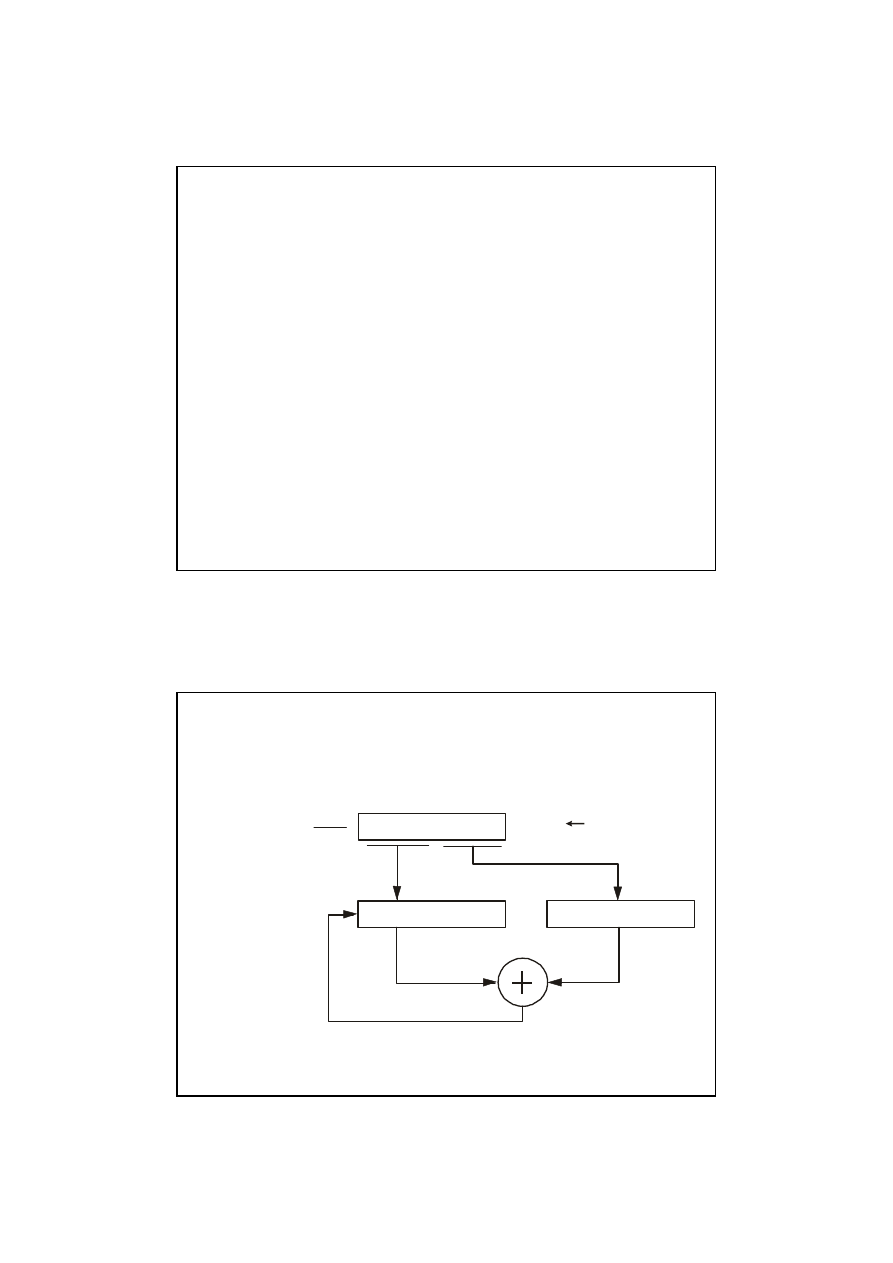

Reprezentacja instrukcji

cd.

Typowy format instrukcji z odniesieniami do dwóch

argumentów (architektura dwuadresowa)

Kod operacji

Argument 1

Argument 2

Binarny kod

operacji określający

jednoznacznie

rodzaj rozkazu;

zdeterminowany

przez mnemonik

instrukcji (np. MOV,

ADD itp.)

Odniesienie do

argumentu nr. 1

• jawnie (wprost)

podana wartość

argumentu lub

• adres lub

• inne wskazanie na

argument

Odniesienie do

argumentu nr. 2

• jawnie (wprost)

podana wartość

argumentu lub

• adres lub

• inne wskazanie na

argument

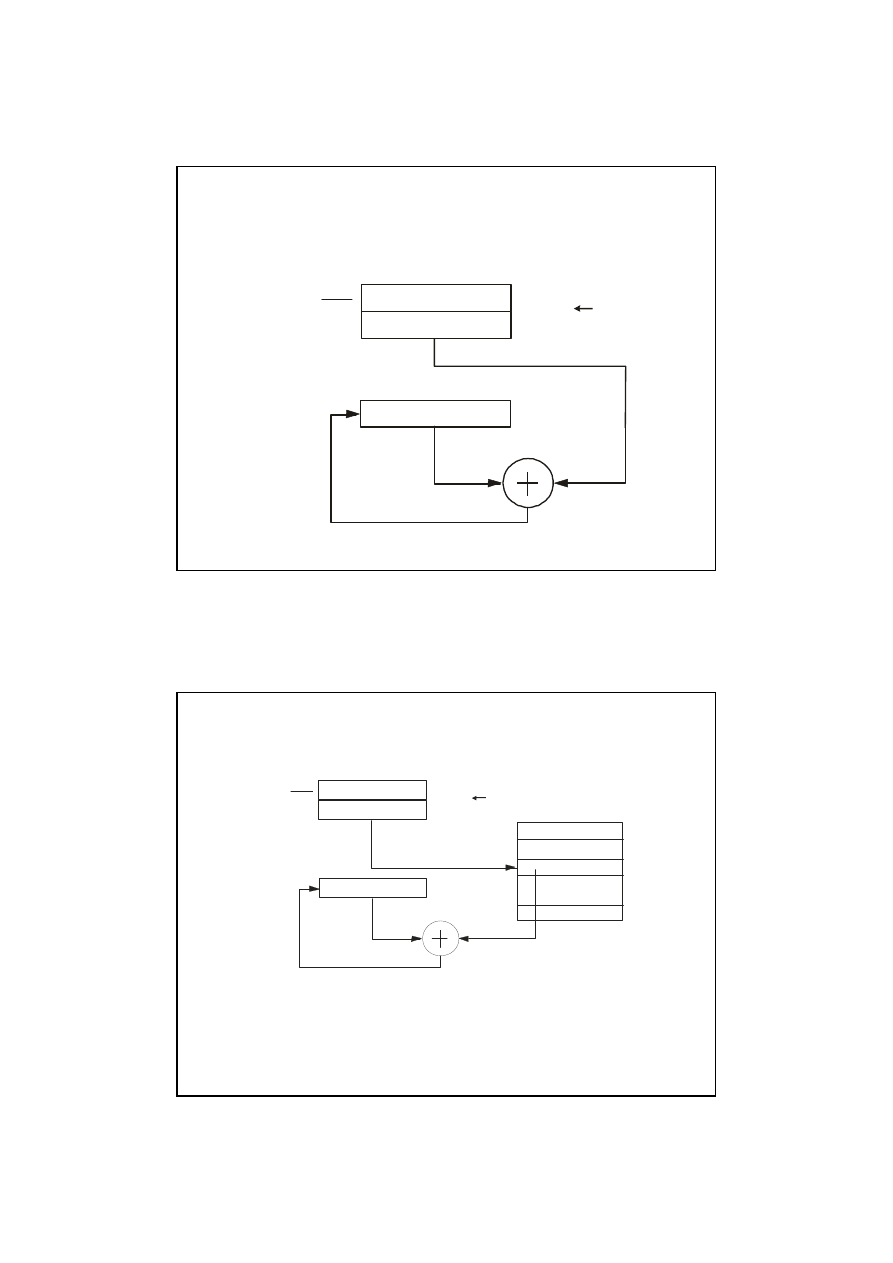

10

Formaty instrukcji

(x51)

a)

b)

Format 1 -bajtowy

16-b itowy operand

16-b itowy adres argumentu

8-bitowy adres i 8-bit owy operand

bajt B0

bajt B1

bajt B2

Kod oper acji

0 1 0 0 1 0 0 1

ORL A,R1

(A) (A) v (R1)

(A) (A) v #0FH

(3FH) (3FH) v #0FH

ORL A,#0FH

ORL 3FH,#0FH

Kod oper acji

0 1 0 0 0 1 0 0

Kod oper acji

0 1 0 0 0 0 1 1

0 0 1 1 1 1 1 1

Operand lub adres

0 0 0 0 1 1 1 1

0 0 0 0 1 1 1 1

Format 2 -bajtowy

Format 3 -bajtowy

6

11

Tryby adresowania argumentów

Tryb adresowania – sposób wskazania na

argumenty instrukcji

Liczba i rodzaje trybów adresowania są różne

dla różnych typów mikroprocesorów

Najważniejsze tryby adresowania

–

rejestrowe, zwane też implikowanym lub

wewnętrznym (ang. register, implied, inherent)

–

natychmiastowe (ang. immediate)

–

bezpośrednie (ang. direct)

–

pośrednie (ang. indirect)

–

indeksowe (ang. indexed)

–

względne (ang. relative)

12

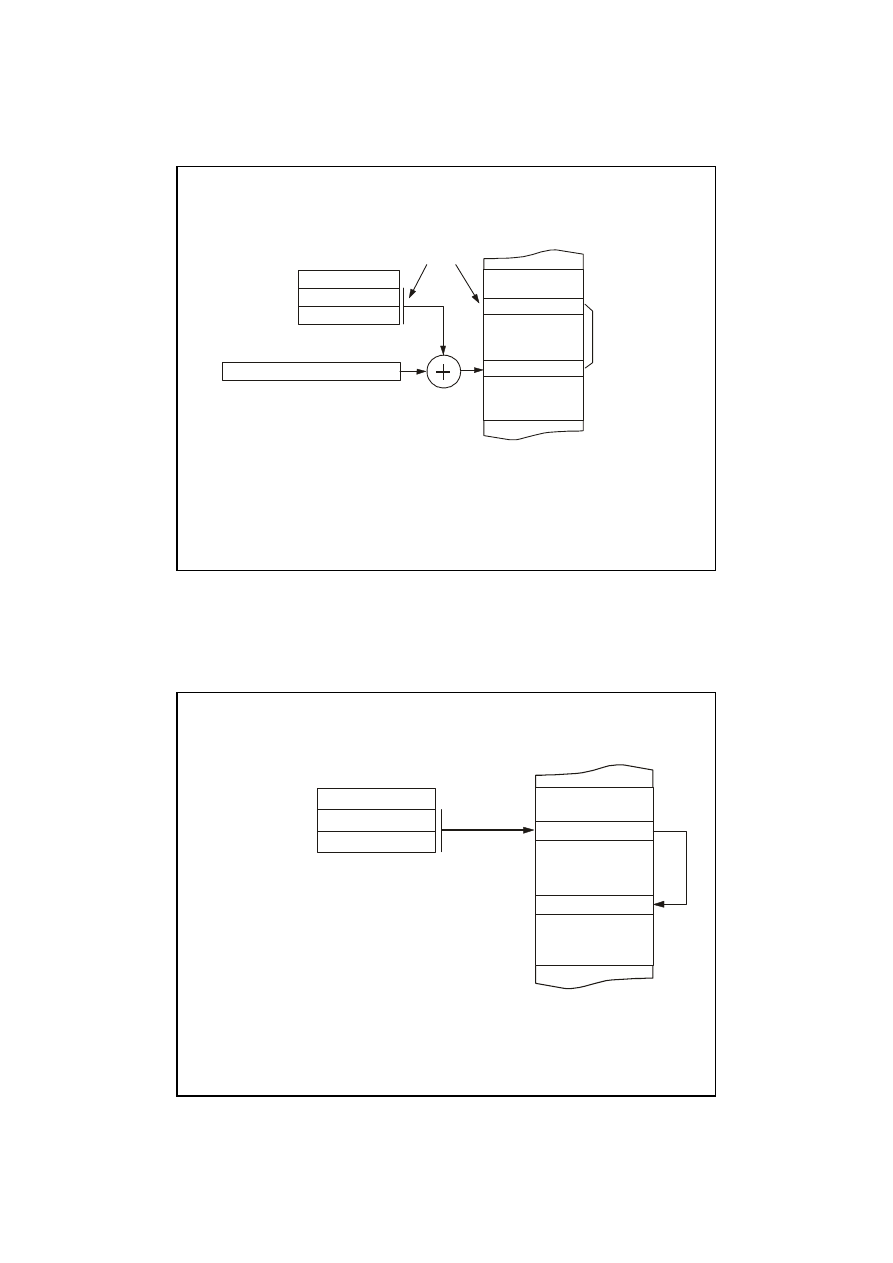

Adresowanie rejestrowe

0 0 1 0 1 0 0 1

Akumulator

Rejestr R1

ADD A,R1

(A) (A) + (R1)

Kod rozkazu

7

13

Adresowanie natychmiastowe

0 0 1 0 0 1 0 0

dana

Akumulator

ADD A,#dana

Kod rozkazu

(A) (A) + #dana

14

Adresowanie bezpośrednie

0 0 1 0 0 1 0 0

a dres 8-bitowy

Operand

00

FF

256 bajtó w

RAM

. . .

. . .

Akumula tor

Wewnętrzna p amięć

danych

ADD A,adre s

Kod rozkazu

(A) (A) + (direct)

Długość adresu bezpośredniego może być różna.

• Zależy to od typu procesora i rodzaju instrukcji

• Niektóre instrukcje mogą dopuszczać warianty instrukcji z

adresem 8-, 16-, 32 – itd.. bitowym

8

15

Adresowanie indeksowe

Operand

Przesunięcie

Przesunięcie

. . .

. . .

Rejestr indeksowy

Pamięć danych

Kod rozkazu

Adres

bazowy

B0

B1

B2

Uwaga: niektóre typy mikroprocesorów (np. x51) nie mogą

realizować tego trybu adresowania

16

Adresowanie pośrednie

Operand

. . .

. . .

Pamięć

Kod rozkazu

Adres

pośredni

Adres efektywny

B0

B1

B2

Uwaga: odmianą adresowania pośredniego

jest adresowanie zawartością rejestru lub

rejestrów (pointer addressing)

9

17

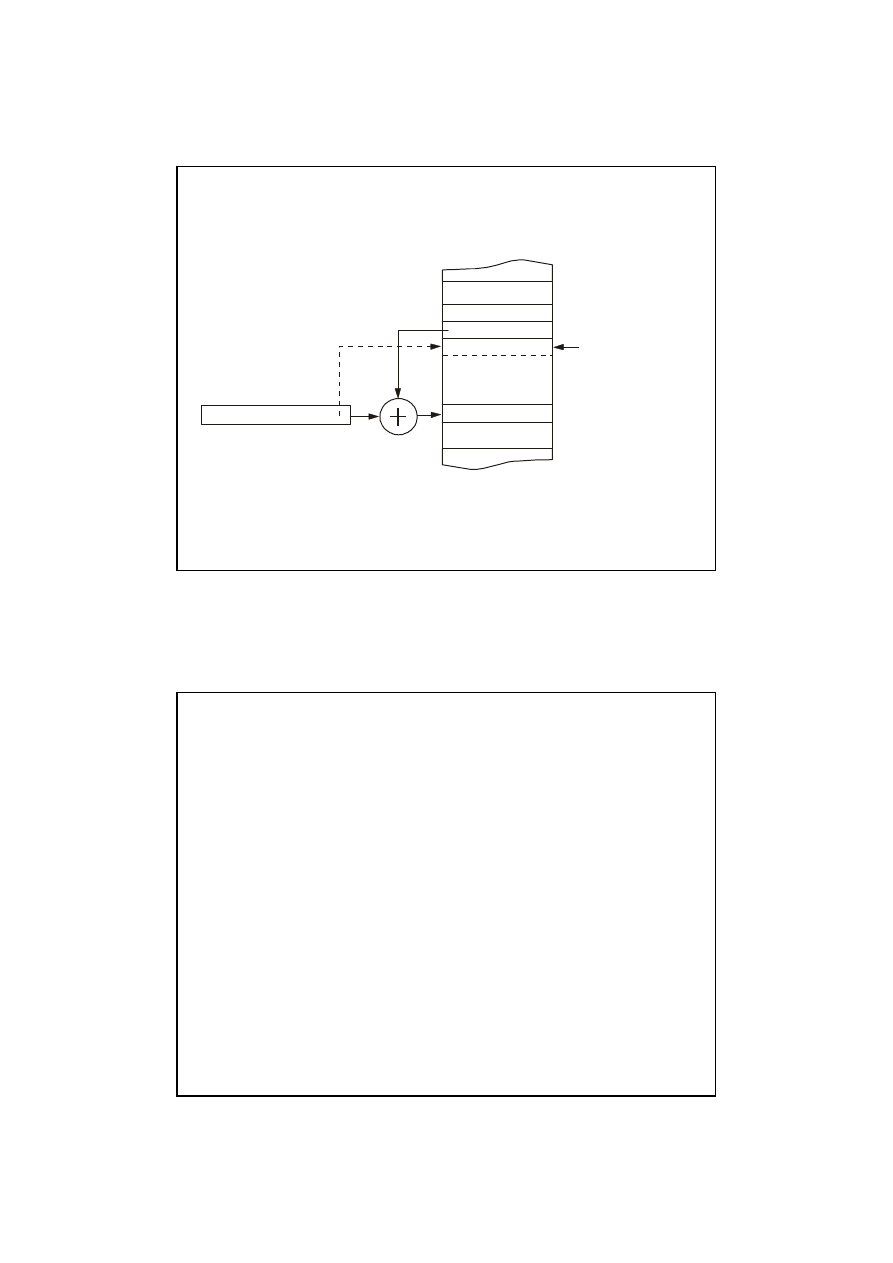

Adresowanie względne

Operand

. . .

. . .

. . .

Licznik programu

Pamięć programu

Kod rozkazu

Następny rozkaz

Przesunięcie

18

Jest używane przy dostępie do stosu

Przykłady

pop psw

;pobierz słowo wskaźników

(flagi) ze stosu

push psw

;wyślij słowo wskaźników na

stos

Adres szczytu stosu znajduje się w rejestrze

wskaźnika stosu SP

Adresowanie stosu

10

19

Data Transfer – przesyłanie danych (np. MOV)

Arithmetic – operacje arytmetyczne (np. ADD)

Logical – operacje logiczne (np. OR)

Conversion – konwersja danych, np. liczb binarnych na

BCD

I/O – operacje wejścia/wyjścia

System Control

–

specjalne operacje systemowe, np. sterowanie stanem

procesora, zarządzanie protekcją itp.

Transfer of Control (np. JMP)

–

skoki, wywołanie podprogramów itp..

Rodzaje instrukcji

20

Lista instrukcji

Każdy mikroprocesor ma własną, ustaloną przez

producenta listę instrukcji

Liczba instrukcji zależy od architektury i stopnia

złożoności procesora

–

Procesory RISC (np. PowerPC) realizują zwykle

kilkadziesiąt instrukcji

–

Procesory CISC (np. Pentium) mają znacznie

bogatszą listę instrukcji (kilkaset)

Najprostsze procesory CISC (np. x51) mogą realizować

mniej rozkazów

Architektura listy rozkazów ma wpływ na

budowę kompilatorów języków wysokiego

poziomu

Wyszukiwarka

Podobne podstrony:

AKiSO SS wykład 8 I2C SPI 1W CAN

AKiSO SS wykład 9 syst operacyjne

AKiSO SS wykład 1

AKiSO SS wykład 2 CPU

AKiSO SS wykład 6 ZL27ARM

AKiSO SS wykład 5 cache

AKiSO SS wykład 4 potok sscalar

AKiSO SS wykład 6 CortexM3

AKiSO SS wykład 2

AKiSO SS wykład 7 RS LPT FW USB

AKiSO SS wykład 0 E4x CYW wprowadzenie

AKiSO SS wykład 6 ARM wprowadzenie

więcej podobnych podstron