1

Podstawy techniki

mikroprocesorowej

ETEW006

Architektura

wybranych

mikrokontrolerów

Andrzej Stępień

Katedra Metrologii Elektronicznej i Fotonicznej

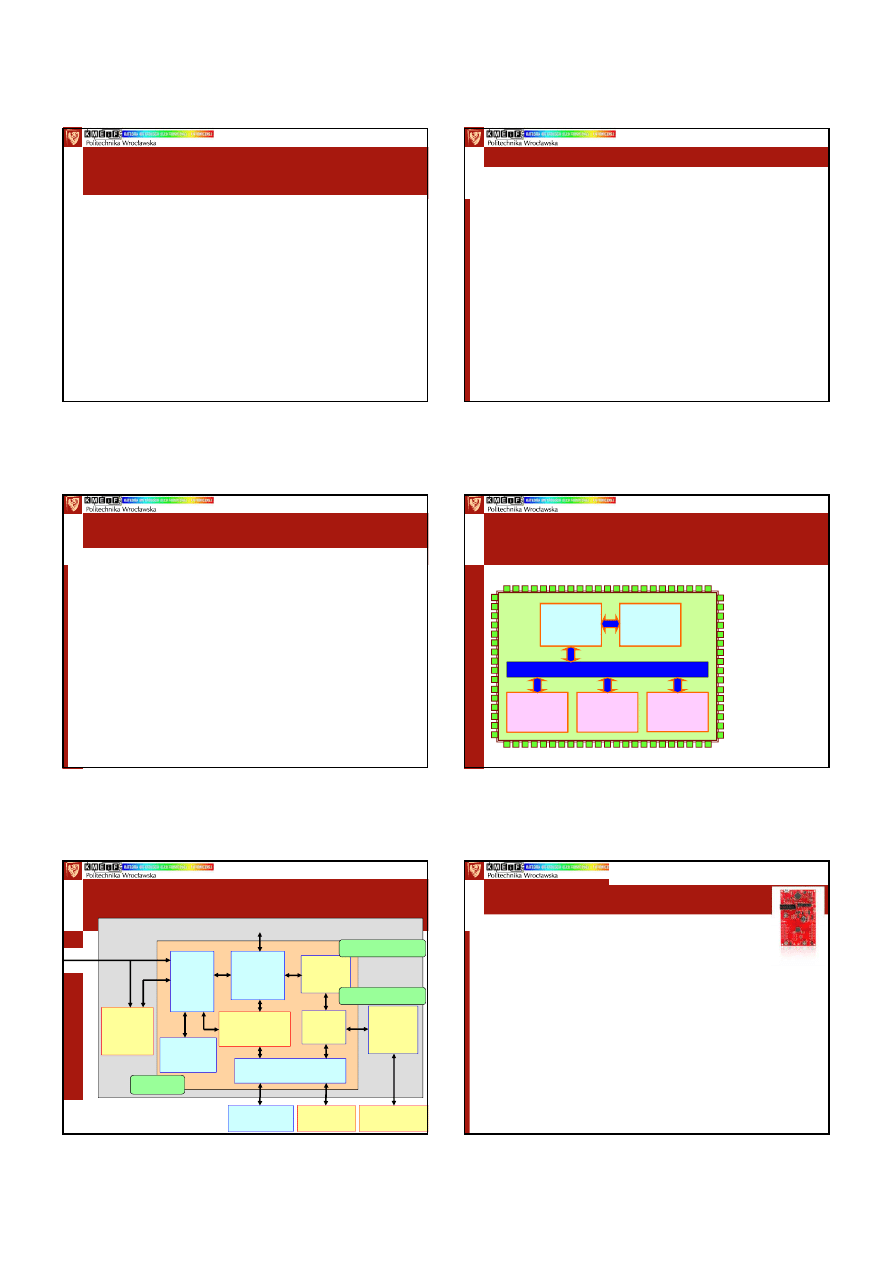

Assembler

[1#2]

Assembler

source file

∗

.asm

∗

.s

Assembler

listing file

∗

.lst

Assembler

object file

∗

.obj

Absolute / Relocatable

object file

Assembler

Compiler

Compiler

source file

∗

.c

∗

.c51

Compiler

listing file

∗

.lst

Compiler

object file

∗

.obj

Absolute / Relocatable

object file

Compiler

Source file

∗

.asm

∗

.s

∗

.src

on

some

compilers

Linker

Compiler

object file

∗

.obj

Absolute / Relocatable object file

Assembler

object file

∗

.obj

Assembler

object file

∗

.obj

Assembler

object file

∗

.obj

Compiler

object file

∗

.obj

Compiler

object file

∗

.obj

Linker

[Converter]

Map file

∗

.map

∗

. m51

Library file

∗

.lib

Absolute file

∗

.

∗

.abs

∗

.hex

Symbol file

∗

.sym

IDE

(Integrated Development Environment)

http://en.wikipedia.org/wiki/Integrated_development_environment

http://pl.wikipedia.org/wiki/Zintegrowane_

ś

rodowisko_programistyczne

zintegrowane

ś

rodowisko programistyczne (IDE) lub interaktywne

ś

rodowisko programistyczne to aplikacja, zapewniaj

ą

ca kompleksowe

wsparcie dla programisty przy tworzeniu oprogramowania

zazwyczaj zło

ż

one z: edytora kodu

ź

ródłowego, asemblera, kompilatora,

linkera, debugger’a, bibliotek (np. dla zapisu stało- i zmienno-

przecinkowego, funkcji trygonometrycznych itp.), formatek / ekranów / okien

dialogowych, menu, raportów, elementów graficznych (ikony, obrazy itp.),

tworzenie baz danych (np. struktura projektu), ...

zaprojektowane do optymalizacji procesu tworzenia, modyfikowania

oprogramowania, programowania urz

ą

dzenia docelowego (mikrokontrolera)

rozwi

ą

zania komercyjne (np. MDK-ARM) lub otwarte (np. GCC / GNU

system developed to be 100% free software)

Zestaw uruchomieniowy

(Development Board = Kit)

http://en.wikipedia.org/wiki/Microprocessor_development_board

znany jako

Microcontroller Development Board

lub

Development Kit

lub

Evaluation Board / Kit

lub

Reference Design Board / Kit

Kit = zestaw

to

płytka drukowana

zawieraj

ą

ca mikrokontroler i minimaln

ą

liczb

ę

układów

logicznych umo

ż

liwiaj

ą

cych nauk

ę

działania i programowania

mikrokontrolera

stosowany

jako

prototypowy zestaw mikroprocesorowy

posiada

minimaln

ą

liczb

ę

wyprowadze

ń

/ interfejsów lub ich brak

umo

ż

liwia zaprogramowanie

i

testowanie

mikrokontrolera za

po

ś

rednictwem

specjalizowanego portu szeregowego

(

Single/Serial Wire

Debug

)

2

Embedded system

System wbudowany

to

system komputerowy

(mikroprocesorowy) z

dedykowanymi funkcjami

,

cz

ęść

wi

ę

kszego systemu mechanicznego lub elektrycznego,

zaprogramowany do wykonywania ograniczonej ilo

ś

ci zada

ń

lub tylko jednego

zadania

zawiera oprogramowanie dedykowane

jednemu zadaniu lub (cz

ę

sto

uproszczony) system operacyjny ze specjalizowanymi funkcjami

zaletami

s

ą

: niski pobór mocy, małe rozmiary, niskie koszty jednostkowe,

odporno

ść

na zakłócenia, znaczna liczba sprz

ę

towych kontrolerów interfejsów

komunikacyjnych, łatwa współpraca z ró

ż

norodnymi czujnikami (sensorami)

wad

ą

jest znacznie wy

ż

szy koszt opracowania, napisania i przetestowania

oprogramowania steruj

ą

cego systemem

przykłady

: urz

ą

dzenia przeno

ś

ne (zegarki, odtwarzacze MP3, automaty do

gier, telewizory, ..), pogodowe sterowniki ogrzewania, pralki, lodówki, kuchenki,

sterowniki pojazdów hybrydowych, sygnalizacja

ś

wietlna, avionika, ..

http://en.wikipedia.org/wiki/Embedded_system

http://pl.wikipedia.org/wiki/System_wbudowany

Dobry mikrokontroler to ...

[1#2]

Jakie znam j

ę

zyki programowania

, jakie mam do

ś

wiadczenia i jaki j

ę

zyk

chciałbym stosowa

ć

przy programowaniu systemów embedded ?

Najcz

ęś

ciej wybór pada na j

ę

zyk C

Które

procesory

s

ą

najłatwiejsze

do poznania ?

Najcz

ęś

ciej wymienia si

ę

: C51, PIC, AVR itp.

Które istniej

ą

ce

zestawy

mikroprocesorowe s

ą

najkorzystniejsze

?

Arduino + Arduino IDE / Atmel AVR + AVR Studio 4 / Freescale HCS12 or

Coldfire + CodeWarrior / Microchip PIC+ MPLAB / ARM Cortex-M3 + ARM

RealView / ??????????

Jakie jest

wsparcie programistyczne

(IDE) i ewaluacyjne,

biblioteki

programów oraz

literatura

?

Jaka jest

stabilno

ść

produkcji

, liczba producentów rodziny procesorów,

poziom kosztów ?

Które

rozwi

ą

zania

(architektury) s

ą

najbardziej

perspektywiczne

?

Cortex-Mx.

Dobry mikrokontroler to ...

[2#2]

Równie wa

ż

ne

cechy

:

–

szeroka gama układów peryferyjnych

,

‘

Crossbar- Peripherals Architecture

’

–

nietypowe rozwi

ą

zania, np. zwi

ę

kszona wydajno

ść

portów do sterowania

wska

ź

ników 7-segmentowych, krótki czas dost

ę

pu do tych układów

–

wysoka cz

ę

stotliwo

ść

taktowania, niski pobór energii, tryby redukcji mocy

–

szeroki zakres napi

ęć

zasilania i temperatur pracy

–

ró

ż

norodno

ść

obudów, w zale

ż

no

ś

ci od stopnia komplikacji układów

peryferyjnych,

–

wła

ś

ciwa długo

ść

słowa (zapis całkowitoliczbowy / zmiennoprzecinkowy)

–

typy wykonywanych operacji: bajtowe, słowowe, bitowe

–

efektywno

ść

, wydajno

ść

pracy, przetwarzanie potokowe, struktura RISC

–

wsparcie dla wyj

ą

tków, wielow

ą

tkowo

ś

ci, bankowanie rejestrów

–

wsparcie do aplikacji systemu operacyjnego, współpraca z zewn

ę

trznymi

pami

ę

ciami ...

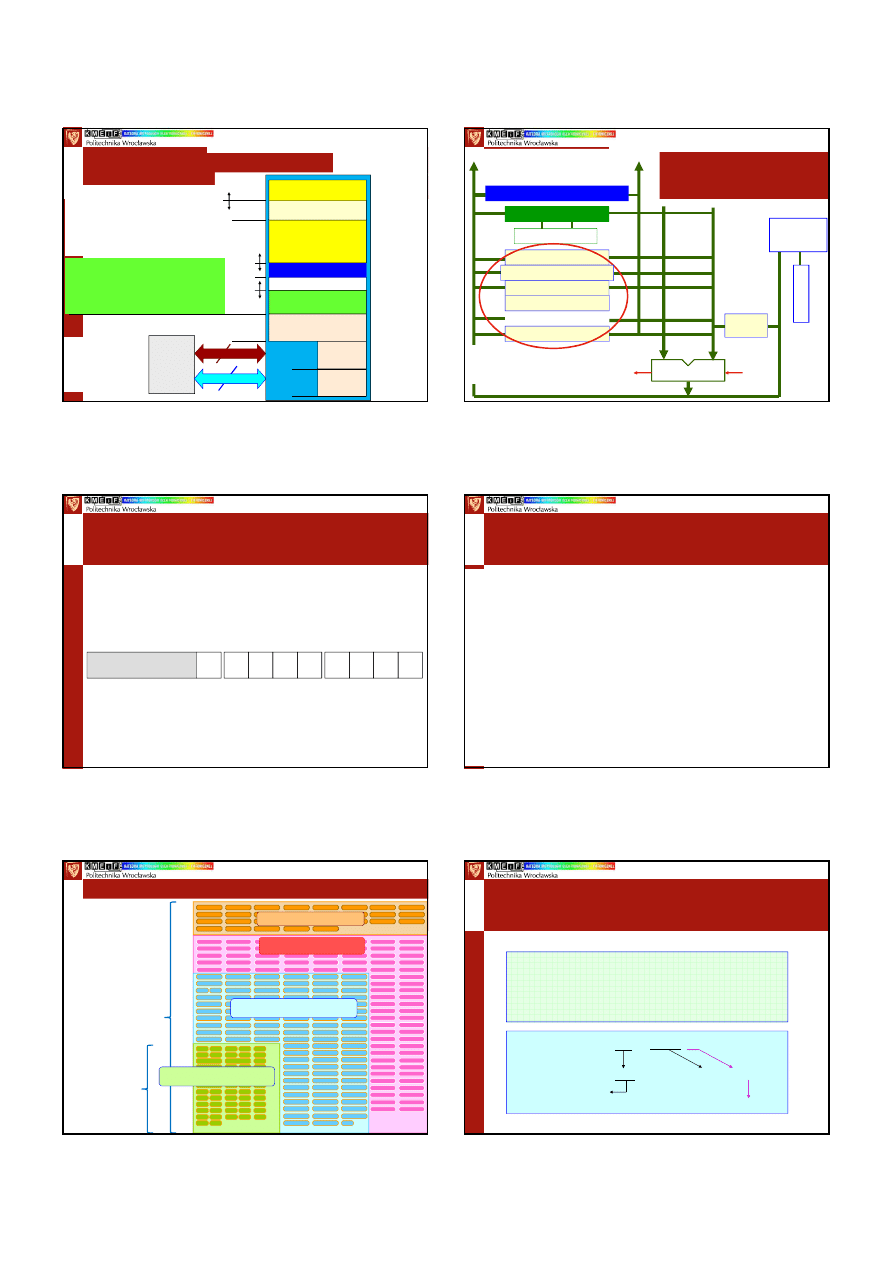

Procesor vs Rdzeń (Core)

Rdze

ń

(Core)

System

System

testuj

ą

cy

(Debug

System)

Wewn

ę

trzna magistrala (Internal Bus)

Peripherals

&

I/O

System

Pami

ęć

(Memory)

Rozwijane przez

producentów

układów scalonych

(chipów)

Rozwijane przez

producenta rdzenia

(licencjonodawc

ę

)

Procesor vs Rdzeń (Core)

Cortex-M0/M0+

Cortex™-M0 Technical Reference Manual.

Rev. r0p0. ARM DDI 0432C, p.2-2

Cortex™-M0+ Technical Reference Manual.

Rev. r0p1. ARM DDI 0484C, p.2-2

Optional

Wakeup

Interrupt

Controller

(WIC)

Optional

Memory

Protection Unit

(MPU)

Cortex-M0

Cortex-M0+

processor

core

Nested

Vectored

Interrupt

Controller

(NVIC)

4 priority

levels

Breakpoint

&

Watchpoint

Units

Optional

Debug

Access

Port

(DAP)

Debugger

interface

Bus matrix

Cortex-M0/

M0+

Components

Cortex-M0/

M0+

Core

Interrupts (NMI)

1 .. 32 ext. inputs

Optional

single cycle

I/O port

Optional

Serial-Wire or

JTAG debug port

Execution Trace Interface

System timer

(24-bit

SysTick Timer)

AHB-Lite

interface

to system

Fast or small

Multiplier

Number of breakpoint

comparators: 0 .. 4

Number of watchpoint

comparators: 0 .. 2

MSP430FRxxxx

Features

MSP430FR57xx, MSP430FR58xx, MSP430FR59xx,

MSP430FR68xx, and MSP430FR69xx Bootstrap Loader.

User's Guide. TI, SLAU550C–December 2013–Revised January 2015

16-Bit RISC Architecture

up to 16-MHz Clock

Wide Supply Voltage Range (1.8 V to 3.6 V)

Optimized Ultra-Low-Power Modes

:

Active Mode: Approximately 100

µ

A/MHz .. Shutdown: 0.02

µ

A

(Typical)

Real-Time Clock (RTC): 0.35

µ

A (Typical)

Ultra-Low-Power Ferroelectric RAM

(FRAM):

Fast Write at 125 ns per Word (64KB in 4 ms)

Unified Memory = Program + Data + Storage in One Single Space

10

15

Write Cycle Endurance

Radiation Resistant and Nonmagnetic

32-Bit Hardware Multiplier (MPY)

RTC

With Calendar and Alarm Functions

Five 16-Bit Timers With up to Seven Capture/Compare Registers Each

16-Channel Analog Comparator

12-Bit Analog-to-Digital Converter

(ADC) With Internal Reference and

Sample-and-Hold and up to 16 External Input Channels

Integrated LCD Driver

With Contrast Control for up to 320 Segments

3

MSP430FR57xx, MSP430FR58xx, MSP430FR59xx,

MSP430FR68xx, and MSP430FR69xx Bootstrap Loader.

User's Guide. TI, SLAU550C–December 2013–Revised January 2015

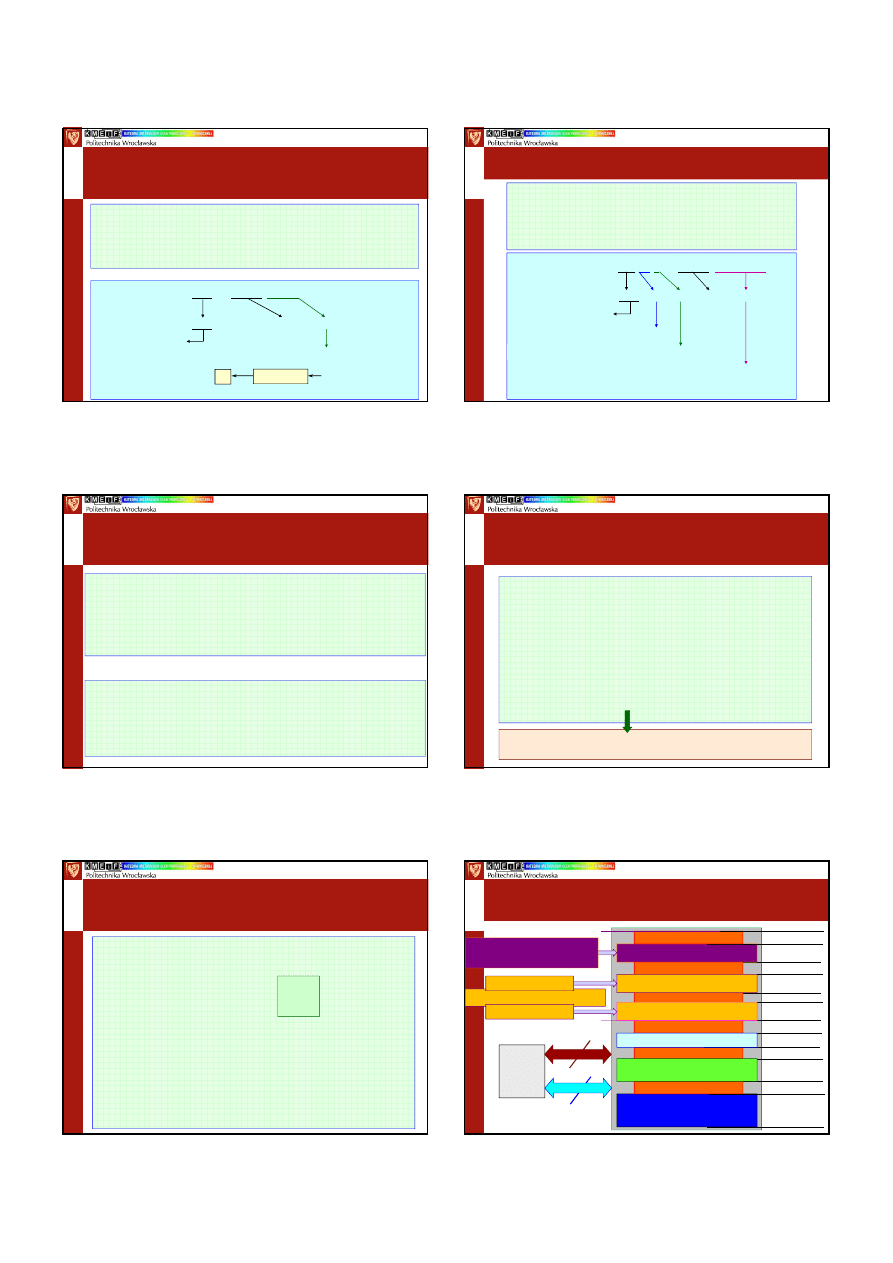

von-NEUMANN Architecture

only

Byte

only

Byte

only

Word

Word/Byte

200h

100h

The end address of RAM

depends on the amount of RAM

present and varies by device.

RAM can be used for both code

and data.

Bytes are located at even or odd

addresses

Words are only located at even

addresses

Low byte of a word is always an

even address

0C00h

Word/Byte

Word/Byte

0FFE0h

10000h

Word/Byte

Access

only

Word for CODE

Word/Byte for Data

CPU

Data

Addr

16-bit

16-bit

Special

Function

Registers

8-Bit

Peripheral

Modules

16-Bit

Peripheral Modules

RAM

Reserved

0

10h

BootLoader

Flash/ROM

Interrupt

Vector Table

Flash/ROM

the same

program and data

bus for code

memory, data

memory and SFR

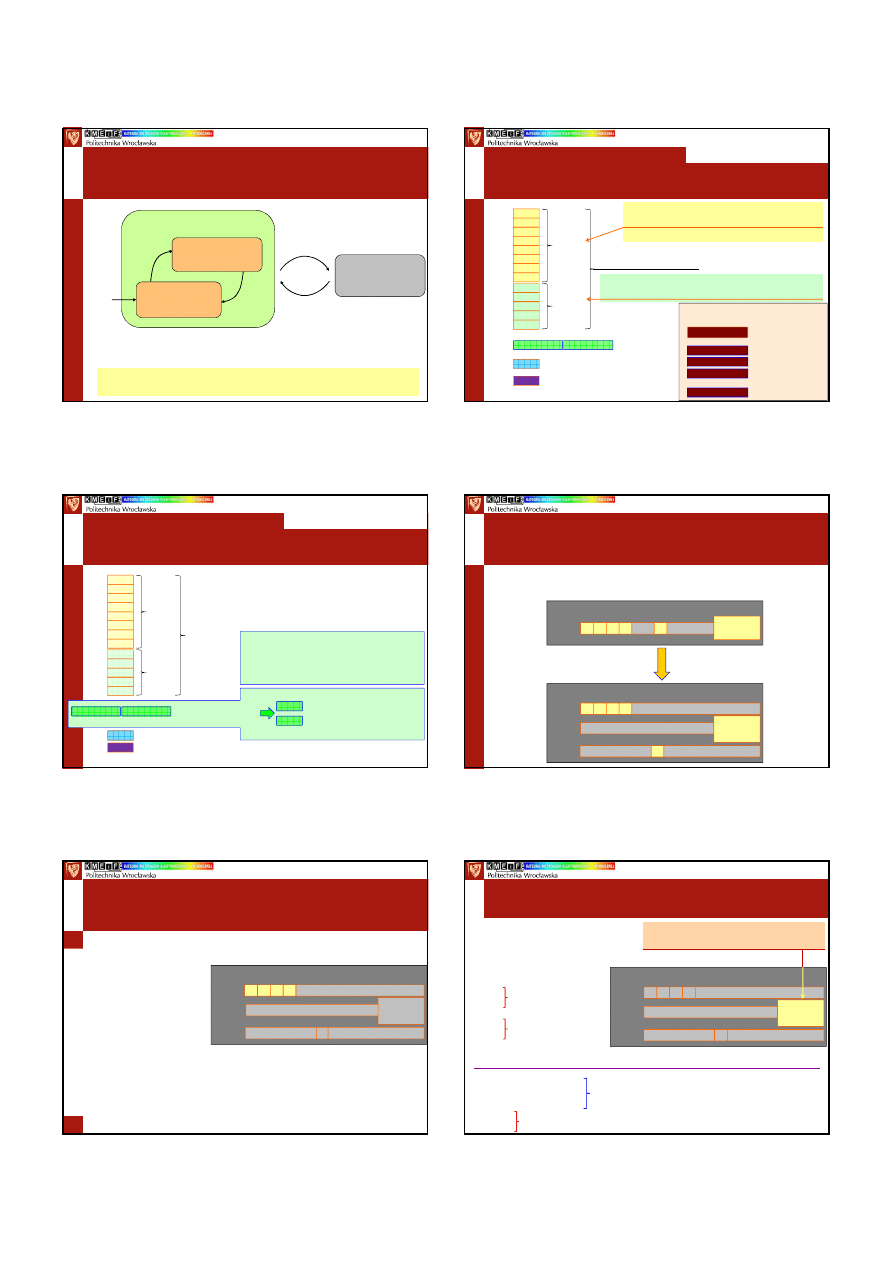

Register R1 (SP)

Register R4

Register R15

Register R3 (CG2)

ALU + Shifter

Cin

C (Carry)

Z (Zero)

N (Negative)

V (oVerflow)

Temp

Register

Increment logic

Register R0 (PC)

Memory Data

Bus (MDB)

Memory Address

Bus (MAB)

Memory Address Register (MA)

Instruction

Fetch

Register

S

e

q

u

e

n

ce

r

...........

Register R2 (SR/CG1)

MSP430

CPU Architecture

MSP430FR57xx, MSP430FR58xx, MSP430FR59xx,

MSP430FR68xx, and MSP430FR69xx Bootstrap Loader.

User's Guide. TI, SLAU550C–December 2013–Revised January 2015

NOT

memory

access

MSP430

Status Register

SCG

1

SCG

0

OSC

Off

CPU

Off

GIE

N

Z

C

V

RESERVED

+2

+4

+8

+1

most used constant:

R0 - Program Counter PC

R1 - Stack Pointer SP

R2

-

Status Register SR

/ Constant Generator CG1

(+4, +8

)

R3 - Constant Generator CG2 (

0, +1, +2,

−−−−

1

)

R4 .. R15 - User working Registers

MSP430x4xx Family User’s Guide.

Texas Instruments, SLAU056G, 2007, p.4-9

MSP430

Constant Generator

R2

-

Status Register SR

/

Constant Generator CG1

(

+4, +8

)

R3 - Constant Generator CG2

(

0, +1, +2, –1

≡≡≡≡

FFh, FFFFh

):

CLR

*

Clear destination:

MOV

#

0

, dst

; 0

→

dst

*

):

MOV #

0

, dst

CLRC

*

Clear Carry bit:

BIC

#

1

, SR

;

0

→

C

*

):

BIC

#

1

, SR

CLRZ

*

Clear Zero bit:

BIC

#

2

, SR

;

0

→

Z

*

):

BIC

#

2

, SR

SETN

*

Clear Negative bit:

BIS

#

4

, SR

; 1

→

N

*

):

BIS

#

4

, SR

EINT

*

Disable general

BIS

#

8

, SR

; 1 → GIE

*

):

BIS

#

8

, SR

interrupts:

INV

*

Invert destination:

INV.W dst

;

*

):

XOR #

0FFFFh

, dst

*

) Emulation

MSP430x4xx Family User’s Guide.

Texas Instruments, SLAU056G, 2007, p.4-61 ...

Cortex-M Instruction Set

PKH

QADD

QADD16

QSUB

QSUB16

QSUB8

SHADD8

SHASX

SHSAX

SMLATT

SMLAD

SMLALBB

SMLAWT

SMLSD

SMLSLD

QADD8

QASX

QDADD

SADD16

SADD8

SASX

SHSUB16

SHSUB8

SMLABB

SMLALBT

SMLALTB

SMLALTT

SMMLA

SMMLS

SMMUL

Cortex-M4

QDSUB

QSAX

SEL

SHADD16

SMLABT

SMLATB

SMLALD

SMLAWB

SMUAD

SMULBB

SMULBT

SMULWT

SMULTB

SMULWT

SMULWB

SMUSD

SSAT16

SSAX

SSUB16

SSUB8

SXTAB

SXTAB16

SXTAH

SXTB16

UADD16

UADD8

UASX

UHADD16

UHADD8

UHASX

UHSAX

UHSUB16

UHSUB8

UMAAL

UQADD16

UQADD8

UQASX

UQSAX

UQSUB16

UQSUB8

USAD8

USADA8

USAT16

USAX

USUB16

USUB8

UXTAB

UXTAB16

UXTAH

UXTB16

ADC

CBNZ

CBZ

Cortex-M3

ADD

ADR

CLZ

BFC

BFI

CMN

CMP

LDMIA

LDMDB

LDR

LDREX

LDREXB

LDREXH

LDRSBT

LDRSHT

LDRSH

LSR

MCRR

MLS

MRC

MRRC

MUL

ORR

PLD

PLDW

RBIT

REV

REV16

AND

ASR

B

BIC

CDP

CLREX

EOR

LDC

LDRB

LDRBT

LDRD

LDRH

LDRHT

LDRSB

LDRT

MCR

LSL

MLA

MOV

MOVT

MVN

NOP

ORN

PLI

POP

PUSH

REVSH

ROR

RRX

DBG

RSB

SBC

BSBFX

SDIV

SEV

SMLAL

SSAT

STC

STMIA

STMDB

STR

STRB

STRBT

STRD

STREX

STREXB

STREXH

STRH

STRHT

STRT

TBB

TBH

TEQ

TST

UBFX

UDIV

UMLAL

UMULL

USAT

SMULL

UXTB

UXTH

WFE

WFI

YIELD

IT

VABS

VADD

VCMP

VLDR

VMLA

VMLS

VNMLA

VMMLS

VNMUL

VSUB

VFMA

VFMS

VCMPE

VCVT

VCVTR

VMOV

VMRS

VMSR

VPOP

VPUSH

VSQRT

VFNMA

VFNMS

Cortex-M4 FPU

VDIV

VLDM

VMUL

VNEG

VSTM

VSTR

BKPT

BX

BLX

CPS

DMB

DSB

ISB

MRS

MSR

ADC

AND

ADD

ASR

BL

CMN

LDR

CMP

LDRB

LDRH

LSL

LDRSB

LSR

NOP

REV16

REV

REVSH

MUL

POP

MOVN

PUSH

SEV

SXTH

SXTB

UXTB

RSB

STR

SBC

STRB

UXTH

WFI

WFE

YIELD

SUB

SVC

ADR

B

EOR

LDM

LDRSH

MOV

ORR

ROR

STM

STRH

TST

BIC

Cortex-M0/M0+/M1

Floating Point

DSP (SIMD, fast MAC)

Advanced data processing

Bit field manipulations

Architecture

ARMv7-M

Architecture

ARMv6-M

General data processing

I/O control tasks

Joseph Yiu (Senior Embedded Technology Specialist, ARM):

Which Cortex-M ? A Selection Guide.

C or ASM

(1/6)

C

instruction:

a = b + c ;

Compiled

ARM

instruction:

ADD

R1, R2, R3

ADD

R1, R2,

R3

ADD

{cond}

{S}

Rd, Rn

,

<Oprnd2>

R1 = R2 + R3

R3

4

C or ASM

(2/6)

C

instruction:

a = 8

∗

b

Destination

CF

0

Multiplication

by a power of 2

MOV

R1, R0,

LSL #3

MOV

{cond}

{S}

Rd, Rn

,

<Oprnd2>

R1 = R0

∗∗∗∗

8

Logical Left Shift

Compiled

ARM

instruction:

MOV

R1, R0, LSL #3

; R1

←

R0

∗

8

C or ASM

(3/6)

C

instruction:

if (Z == 1) R1 = R2 + ( R3

∗

4)

Compiled

ARM

instruction:

ADDEQS

R1, R2, R3, LSL #2

ADD

EQ

S

R1, R2,

R3, LSL #2

Z=1

↔

(Equal) EQ

ADD

{cond}

{S}

Rd, Rn

, <Oprnd2>

Logical Shift Left

Rm LSL #5bit_Imm

↔

<Oprnd2>

sets condition flags after instruction

↔

S

R1 = R2 + R3 SHL 2

C or ASM

(4/6)

C

instruction:

a = a

∗

(2

n

+ 1)

Compiled

ARM

instruction:

ADD

R0, R0, R0, LSL #n

; R0

←

R0 + (R0 << n)

C

instruction:

a = a

∗

(2

n

– 1)

Compiled

ARM

instruction:

RSB

R0, R0, LSL #n

; R0

←

(R0 << n) – R0

C or ASM

(5/6)

C

instruction:

a = 100

∗

a + b

Compiled

ARM

instruction:

ADD

R0, R0, R0, LSL #2

; R0 = R0

∗

5

ADD

R0, R0, R0, LSL #2

; R0 = R0

∗

5

; R0 = R0

∗

25

ADD

R0, R1, R0, LSL #2

; R0 = R1 + R0

∗

4

; R0 = R1 + (R0

∗

25)

∗

4

MLA (Multiply Accumulate):

MLA

R0, R2, R1, R0

; R0

←

R2

∗

R1 + R0

C or ASM

(6/6)

C

instruction:

if (a == 0) {

b = 23 ;

} else {

b = 42 ;

c = a ;

}

Compiled

ARM

instruction:

TEQ

R0, #0

; compare, set or reset Z flag

MOVEQ

R1, #23

; if Z=1 then R1

←

23

MOVNE

R1, #42

; if Z=0 then R1

←

42

MOVNE

R2, R0

; if Z=0 then R2

←

R0

a in R0

b in R1

c in R2

Architektura von-NEUMANN’a

Cortex-M0

[NXP LPC1114]

CPU

Data

Addr

Pami

ęć

programu

(Program Memory

32KB

MAX

on-chip Flash)

0x1000 0000

0x0000 0000

Zarezerwowane (Reserved)

32-bity

32-bity

Zarezerwowane (Reserved)

0x4000 0000

0x5000 0000

0xE000 0000

UM10398. LPC111x/LPC11Cxx User manual.

NXP, Rev. 12.3 — 10 June 2014, fig. 7

0x0001 0000

0x1000 2000

Zarezerwowane (Reserved)

1 GB

0x4008 0000

Zarezerwowane (Reserved)

0x5020 0000

Zarezerwowane (Reserved)

Własna magistrala peryferii

(PPB Private Peripheral Bus)

0xE010 0000

Zarezerwowane (Reserved)

0xFFFF FFFF

Pami

ęć

danych

(Data Memory – 8KB

MAX

SRAM)

Peryferia typu APB

(APB Peripherals)

Peryferia typu AHB

(AHB Peripherals)

4 GB

Rdze

ń

(core): NVIC, SysTick,

System Control Block;

(only word)

AHB – Advanced High-performance Bus

APB – Advanced Peripheral Bus

pozostałe peryferia

GPIO PIO3..PIO0

0x1FFF 0000

0x1FFF 4000

16KB BootLoader

5

Cortex

–

M0 / Cortex-M0+

(ARMv6M)

tryby i stany procesora

(Processor Modes and States)

J. Yiu: The Definitive Guide to the ARM Cortex-M0.

Elsevier Inc. 2011, Fig. 3.1

Thread Mode

Executing normal

code

Thumb State

Exception

Request

Exception

return

praca standardowa (normal operation)

procesor wykonuje instrukcje Thumb

Handler Mode

Executing exception

handler

Debug State

(wstrzymanie

wykonywania

instrukcji)

stan Debug mo

ż

liwy po

uruchomieniu debuggera

Debug

activities

Procesor

Cortex-M0/M0+

pracuje w:

2 trybach (modes)

i 2 stanach (states)

Start

(reset)

Procesory z architektur

ą

ARMv6-M pracuj

ą

wył

ą

cznie w trybie

uprzywilejowanym

(only privileged operation)

[DDI0419C, A2.1.1]

Cortex

–

M

Rejestry ogólnego przeznaczenia

rejestry ogólnego

przeznaczenia

Link Register (LR)

Program Counter (PC)

Stack

Pointer (SP)

ARMv6-M Architecture Reference Manual.

ARM DDI 0419C, September 2010

ARMv7-M Architecture Reference Manual.

ARM DDI 0403D, Errata 2010_Q3

Low

Register

High

Register

R0

R1

R2

R3

R4

R5

R6

R7

R8

R9

R10

R11

R12

R13 (PSP)

R14

PC

R13 (MSP)

dost

ę

pne przez

wszystkie 16-bitowe

instrukcje

Thumb

i

wszystkie 32-bitowe

instrukcje

Thumb-2

dost

ę

pne przez

wszystkie

instrukcje

Thumb-2

ale

nie wszystkie 16-bitowe

instrukcje

Thumb

n

ie

o

k

re

ś

lo

n

y

s

ta

n

re

je

s

tr

ó

w

p

o

r

e

s

e

c

ie

xPSR

PRIMASK

FAULTMASK

BASEPRI

CONTROL

Program status

register

Interrupt

mask

registers

Control register

Rejestry specjalne

Cortex

–

M0 / M0+ / M3

Wskaźniki stosu

(Stack Pointer Registers)

(General

Purpose

ARM Core

Register)

MSP

PSP

Main Stack Register

(SP_main after Reset)

Process Stack Register

(SP_process)

Link Register (LR)

Program Counter (PC)

Stack Pointer (SP)

ARMv6-M Architecture Reference Manual.

ARM DDI 0419C, September 2010

ARMv7-M Architecture Reference Manual.

ARM DDI 0403D, Errata 2010_Q3

Low

Register

High

Register

R0

R1

R2

R3

R4

R5

R6

R7

R8

R9

R10

R11

R12

R14

PC

2 najmniej znacz

ą

ce bity wska

ź

ników

stosu (

stack pointers)

maj

ą

zawsze

warto

ść

0 – wyrównanie słowowe

(

always word aligned

)

R13 (PSP)

R13 (MSP)

rejestry ogólnego

przeznaczenia

Cortex

–

M0 / Cortex

–

M0+

Rejestry statusowe

(Program Status Registers)

ARMv6-M Architecture Reference Manual.

ARM DDI 0419C, September 2010, B1.4

N Z C V

31

28

Reserved

24

APSR

T

Reserved

IPSR

Reserved

EPSR

Reserved

5

0

0 or

Exception

Number

N Z C V

31

28

Reserved

24

T

5

0

Exception

Number

Program Status Registers

(xPSR)

Res

xPSR

Cortex

–

M0 / Cortex

–

M0+

Rejestr aplikacji

(Application Program Status Register)

ARMv6-M Architecture Reference Manual.

ARM DDI 0419C, September 2010, B1.4

Application

Program Status Register

(APSR):

zawiera znaczniki (flags)

(

N

egative,

Z

ero,

C

arry/borrow, o

V

erflow)

rejestr APSR

dost

ę

pny

przez instrukcje

MSR

lub

MRS

(tak

ż

e w trybie nieuprzywilejowanym)

:

MSR

(

MSR{cond} spec_reg, Rn)

; APSR

←

Rn

MRS

(

MRS{cond} Rd, spec_reg)

; Rn

←

APSR

Niekre

ś

lony stan znaczników po resecie

N Z C V

31

28

Reserved

24

APSR

T

Reserved

IPSR

Reserved

EPSR

Reserved

5

0

0 or

Exception

Number

Program Status Registers

(xPSR)

Exception mumber

:

0

= Initial SP value

1

= Reset

2

= NMI

3

= HardFault

4...

...10

11

= SVCall

11...

...13

14

= PendSV

15

= SysTick (

zarezerwowane je

ś

li brak SysTick Timer’a

)

16

= IRQ0

...

n+15

= IRQ(n-1)

n+16...

...63

Cortex

–

M0 / Cortex

–

M0+

Rejestr przerwań

(Interrupt Program Status Register)

Cortex™-M0 Devices. Generic User Guide

ARM DUI0497A, October 2009

N Z C V

31

28

Reserved

24

APSR

T

Reserved

IPSR

Reserved

EPSR

Reserved

5

0

0 or

Exception

Number

Program Status Registers

(xPSR)

max 32 przerwania (Interrupts)

= zarezerwowane

kontroler przerwa

ń

(ARMv6-M

NVIC

)

obsługuje do

16

ź

ródeł przerwa

ń

= zarezerwowane

= zarezerwowane

6

Cortex

–

M0 / Cortex

–

M0+

Rejestr wykonania

(Execution Program Status Register)

ARMv6-M Architecture Reference Manual.

ARM DDI 0419C, September 2010, B1.4

Program Status Registers

(xPSR)

Execution Program Status Register

(EPSR):

bit-T

(bit stanu)

identyfikuje

stan Thumb procesora:

–

bit-T

nie

mo

ż

e by

ć

odczytywany przez

oprogramowania;

–

bit-T dost

ę

pny w trybie debug)

Bit-T = 1

; procesor Cortex-M0/M0+ (architektura ARMv6-M)

pracuje

wył

ą

cznie z instrukcjami Thumb

Bit-T = 0 generuje HardFault

; (wskazanie na prób

ę

wykonania instrukcji

innej ni

ż

typu THUMB

Pozostałe bity s

ą

zarezerwowane

.

N Z C V

31

28

Reserved

24

APSR

T

Reserved

IPSR

Reserved

EPSR

Reserved

5

0

0 or

Exception

Number

Pętla FOR

deklaracja zmiennej k

[1#2]

Keil

µµµµ

Vision IDE

void

Opoznienie

(unsigned int czas_ms) {

unsigned int k;

// deklaracja 32-bitowej zmiennej

for (k = 0; k < czas_ms

∗

6000; k++);

// pojedynczy obieg p

ę

tli trwa 1

ms

}

; r0

←

czas_ms

0x00000278 2100

MOVS r1, #0x00

; r1

←

k = 0

0x0000027A E000

B

0x0000027E

; skok do 0x027E

0x0000027C 1C49

ADDS

r1, r1, #1

; r1

←

r1 + 1 (k++)

0x0000027E 4A10

LDR

r2, [pc, #64]

; r2

←

6000 = 0x1770

0x00000280 4342

MULS

r2, r0, r2

; r2

←

czas_ms

∗

6000

0x00000282 428A

CMP

r2, r1

; porównanie r2 oraz r1

0x00000284 D8FA BHI

0x0000027C

; je

ś

li r1 < r2 to skok do 0x027C

Pętla FOR

deklaracja zmiennej k

[2#2]

unsigned int k;

// deklaracja 32-bitowej zmiennej

void

Opoznienie

(unsigned int czas_ms) {

for (k = 0; k < czas_ms

∗

6000; k++);

// pojedynczy obieg p

ę

tli trwa 1 ms

}

; r0

←

czas_ms

0x00000278 2100

MOVS r1, #0x00

; r1

←

0

0x0000027A 4A15

LDR

r2, [pc, #84]

;

r2

←

0x1000000C

(

adres w zmiennej k w RAM

)

0x0000027C 6011

STR

r1, [r2, #0x00]

; (r2)

←

r1 (zapis k do RAM)

0x0000027E E004

B

0x0000028A

; skok do 0x028A

0x00000280 4913

LDR

r1, [pc, #76]

;

r1

←

0x1000000C

0x00000282 6809

LDR

r1, [r1, #0x00]

; r1

←

(r1) czyli warto

ść

k

0x00000284 1C49

ADDS

r1, r1, #1

; r1

←

r1 + 1 (k++)

0x00000286 4A12

LDR

r2, [pc, #72]

;

r2

←

0x1000000C

0x00000288 6011

STR

r1, [r2, #0x00]

; (r2)

←

r1

0x0000028A 4912

LDR

r1, [pc, #72]

; r1

←

6000 = 0x1770

0x0000028C 4341

MULS r1, r0, r1

; r1

←

czas_ms

∗

6000

0x0000028E 4A10

LDR

r2, [pc, #64]

;

r2

←

0x1000000C

0x00000290 6812

LDR

r2, [r2, #0x00]

; r2

←

(r2) czyli warto

ść

k

0x00000292 4291

CMP

r1, r2

; porównanie r2 oraz r1

0x00000294 D8F4

BHI

0x00000280

; je

ś

li r1 < r2 to skok do 0x0280

Problemy i pytania

1. Co to jest mapa pami

ę

ci (memory map) ?

2. Jakie elementy tworz

ą

map

ę

pami

ę

ci ?

3. Jak

ą

funkcj

ę

pełni

ą

rejestry R0 i R1 w procesorze MSP430 ?

4. Jak

ą

funkcj

ę

pełni

ą

rejestry R2 i R3 w procesorze MSP430 ?

5. Poda

ć

przykłady instrukcji emulowanych w procesorze MSP430.

6. Jaki obszar pami

ę

ci przyporz

ą

dkowano układom peryferyjnym w LPC1114 ?

7. Jak

ą

rol

ę

pełni

ą

rejestry R0 .. R12 w procesorach ARM Cortex-M0/M0+ ?

8. Jak

ą

rol

ę

pełni

ą

rejestry R13 i R14 w procesorach Cortex-M0/M0+ ?

9. Jak

ą

rol

ę

pełni rejestr R15 w procesorach Cortex-M0/M0+ ?

10. Jak

ą

rol

ę

pełni rejestr xPSR w procesorach Cortex-M0/M0+ ?

11. Jakie jest przeznaczenie ’Development Kit’ ?

Wyszukiwarka

Podobne podstrony:

2 Architektura 2015 www

9 Liczniki 2015 www

10 Serial Interface 2015 www

13 Power 2015 www

ARCHITEKTURA Bazodanowych aplikacji WWW, edukacja i nauka, Informatyka

4 Typy instrukcji Tryby adresowania 2015 www (1)

5 Architektura MCU 2010 id 4004 Nieznany (2)

3 Przetw danych Typy proces 2015 www (1)

7 Stos 2015 www

12 DMA 2015 www

Lokalny program rewitalizacji osiedla „Stara Kolonia” w Brzeszczach 2005 2015 www old brzeszcze pl

6 Pamieci ROM RAM 2015 www

11 Przetworniki 2015 www

8 Przerwania 2015 www

9 Liczniki 2015 www

10 Serial Interface 2015 www

więcej podobnych podstron