F2-28

Układy CMOS - 7

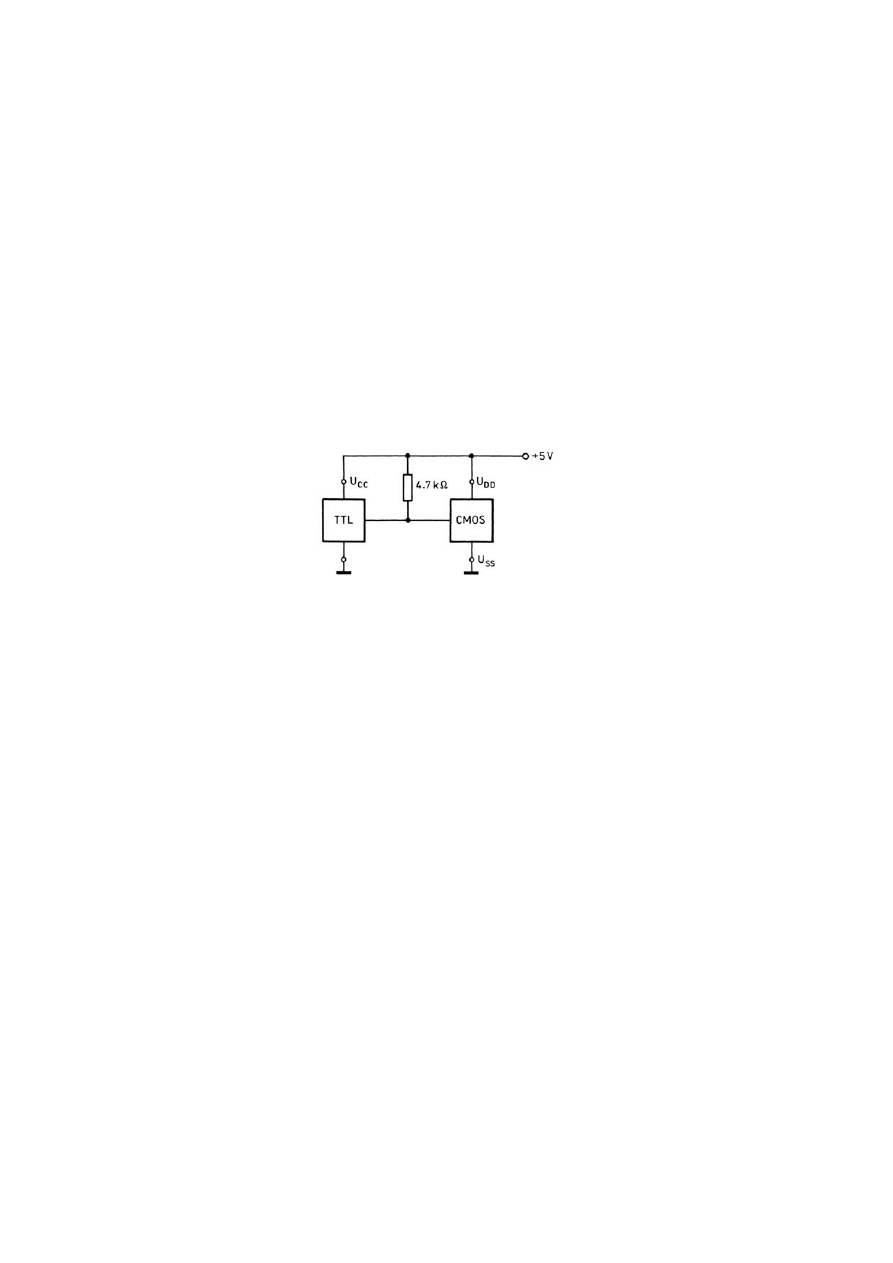

Struktury wejść CMOS z TTL-owskim napięciem progowym stosuje

się aby umożliwić

niezawodne połączenie TTL → CMOS

(I TYLKO DO TEGO CELU!)

Np. dla TTL LS jest U

OH

min

= 2.4 V,

a napięcie progowe CMOS na wejściu standardowym

U

T

= U

DD

/2 = 2.5 V

Margines zakłóceń: M

H

min

= 2.4 – 2.5

< 0!

Można zastosować rezystor podciągający:

UWAGA!

Rezystancja wejściowa układu CMOS wynosi ok. 10

12

Ω.

Grozi nieodwracalne

przebicie dielektryka bramkowego

w wyniku gromadzenia ładunku elektrostatycznego na wejściu!

REGUŁA:

należy zachować ostrożność przy transporcie,

magazynowaniu i montażu układów CMOS!

REGUŁA:

opakowania antystatyczne, uziemione stoły

i urządzenia laboratoryjne!

REGUŁA:

nieużywane wejścia układów CMOS nie powinny

pozostawać swobodne!

© J. Kalisz, WAT, 2005

Wyszukiwarka

Podobne podstrony:

F2 17 Układy CMOS 1 Inwerter

F2 19 Układy CMOS 3 Parametry

F2 35A Układy CMOS 11 Przerzutniki

F2 34 Układy CMOS 13 Bramki transmisyjne

F2 18 Układy CMOS 2 Struktury

F2 31 Układy CMOS 10 Margines zakłóceń

F2 30 Układy CMOS 9 Szybkość działania

F2 29 Układy CMOS 8 Charakterystyki

F2 36 Układy CMOS 15 Wyjście trójstanowe

F2 33 Układy CMOS 12 Bramki transmisyjne

F2 27 Układy CMOS 6 Bramki

F2 26 Układy CMOS 5 Bramki

więcej podobnych podstron