2009-03-01

1

2009-03-01

Procesory sygnałowe I / III

1

Procesory sygnałowe

Materiały ilustracyjne do wykładu.

Część III

Lista rozkazów DSP ‘C5400

Przygotowane z wykorzystaniem materiałów

firmy Texas Instruments

Dr Krzysztof Kardach

(ver. 5.0 luty 2009)

2009-03-01

Procesory sygnałowe I / III

2

Wykaz wykorzystanych materiałów

Bruno Pillard „An Introduction To Digital Signal Processors”;

Uniwersytetu Sherbrooke

TMS320C54x DSP Functional Overview [CD-ROM, materiały

podstawowe = C54xx_OV_spru307a.pdf ]

TMS320C54x DSP Reference Set - CPU and Peripherals [CD-ROM,

materiały podstawowe = C54x_CPU_&_Priph_spru131g.pdf]

TMS320C54x DSP Reference Set - Mnemonic Instruction Set [CD-

ROM, materiały podstawowe = C54x_Mnem_Instr_Set_spru172c.pdf]

Peter Robinson TMS320 Algorithm Debugging Techniques; SPRA084

TLC320ADC50 Data Manual; SLAS131E

TMS320C54x Design Workshop – materiały firmy Texas Instruments

2009-03-01

2

2009-03-01

Procesory sygnałowe I / III

3

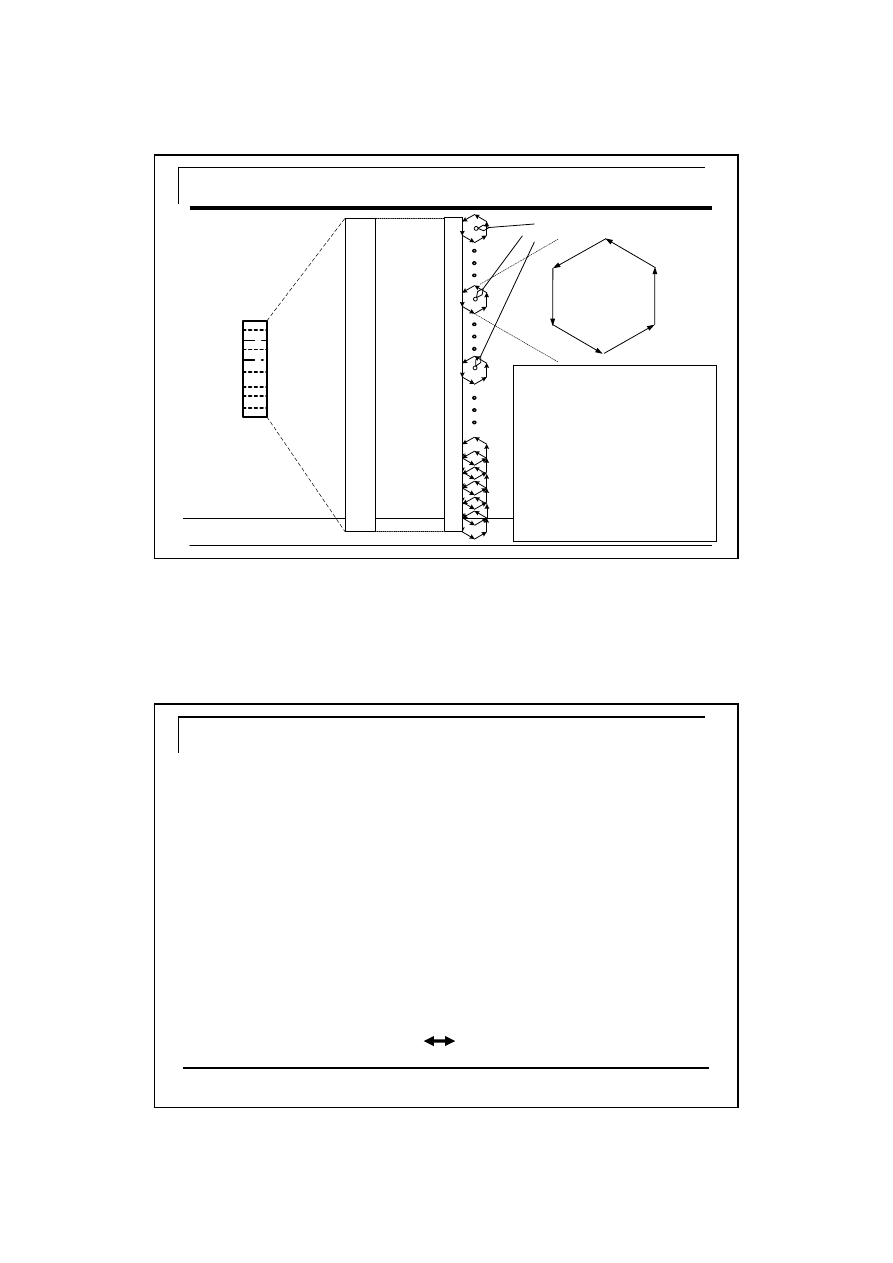

Od programu do pracy procesora

Tek

s

t

Program

w jez. C

Program w

Asemblerze

while

.....

.......

.=.=..

a.=2

=......

.......-

-----

for....

.....

Indywidualne rozkazy

wykonywane przez procesor

K

o

d

binar

n

y

Tekst

Program w

kodzie proc.

przygot.adr.rozkazu

odczyt rozkazu

analiza rozkazu

przygot.adr.operand.

pobranie.operand.

wykonanie operacji

• Rozkazy w trakcie

wykonania zachodzą na siebie

ich czasy wykonania

nakładają się na siebie

• Każdy rozkaz wykonywany

jest w 6-ciu fazach

• Każda faza wykonywania

rozkazu trwa jeden cykl

procesora, tj. 4 cykle

zegarowe

2009-03-01

Procesory sygnałowe I / III

4

Asembler - program

Strona Asemblera

Zapis kolejnych linii programu

Rozkazy zapisane skrót.

mnemotechnicznymi

Operują na nazwach,

etykietach, zmiennych

formalnych i wartościach

Programista rozpisuje rozkazy

w ustalonym układzie –

organizacji linii poleceń

Jeden rozkaz asemblera

Strona procesora

Zawartość kolejnych komórek

pamięci programu

Binarne kody rozkazów w

kolejnych komórkach

Operuje tylko na adresach i

zawartościach komórek pamięci /

rejestrów

Procesor analizując kod

kolejnego rozkazu ustala jego

rozmiar sposób działania

Jeden rozkaz w kodzie bin.

2009-03-01

3

2009-03-01

Procesory sygnałowe I / III

5

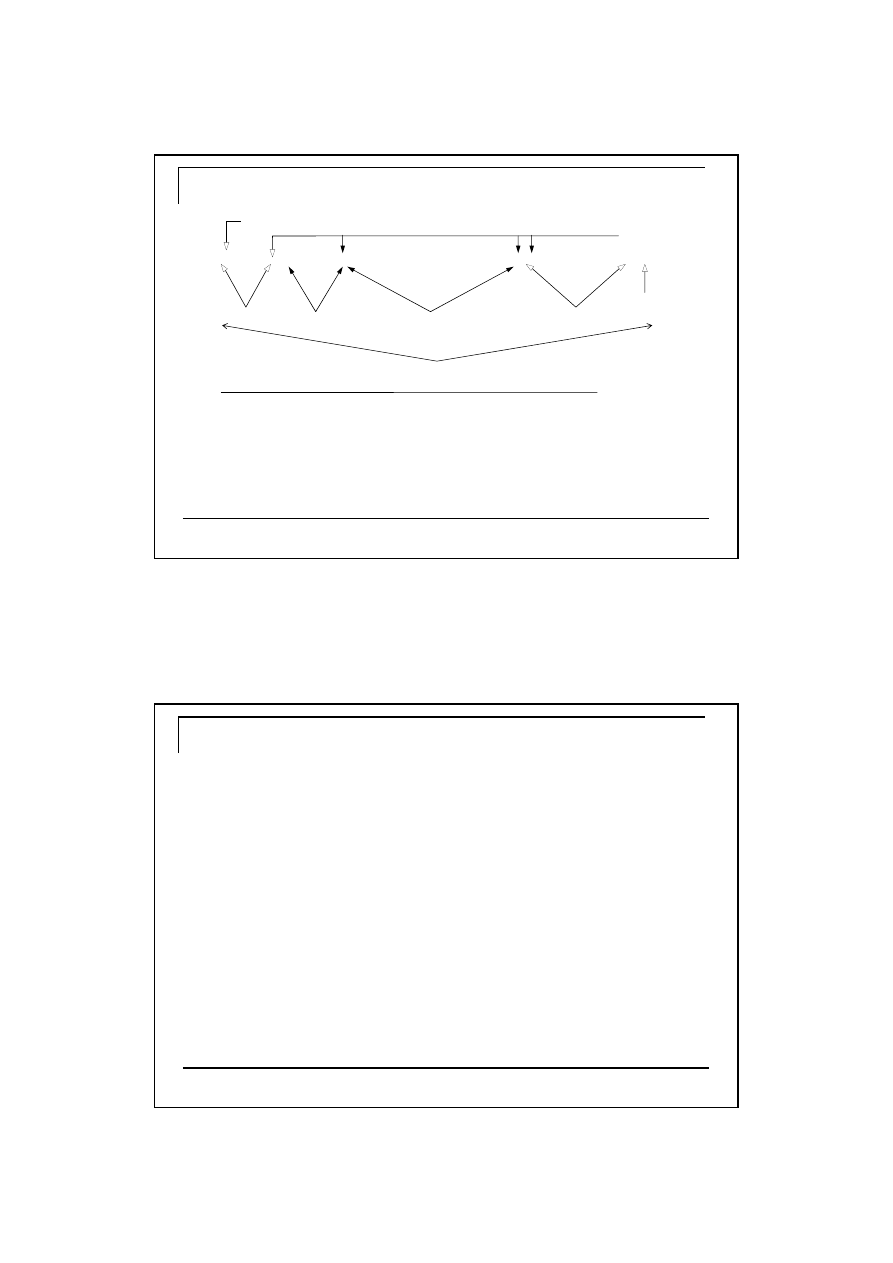

Składnia linii programu

[Etykieta]

Mnemonik Operand[[,Operand2],Operand3] [; text objasnienia] CR/LF

kolumna 0

pole etykiety

pole mnemonika

pole operandów

pole komentarza

koniec linii

separatory

rozkaz

tutaj: BR tutaj: ;pętla bez końca, „skok na siebie” np. czkanie na ...

;PC Å wartość "tutaj" (wartosc "tutaj" to adres tego rozkazu)

MAC *AR1+,*AR2+,B ;oblicza jedno ogniwo filtru

;PC = PC + 1

przygotowanie adresu kolejnego rozkazu

;B = B + (AR1) * (AR2)

wykonanie operacji rozkazu

;AR1 = AR1 + 1, AR2 = AR2 + 1

Í

postmodyfikacja

Przyklady:

;PC = tutaj

2009-03-01

Procesory sygnałowe I / III

6

Rodzaje rozkazów procesora DSP

• Rozkazy operacji arytmetycznych

• Rozkazy operacji logicznych

• Rozkazy sterujące przebiegiem programu

• Rozkazy sterujące przesłaniami

• Rozkazy specjalizowane

2009-03-01

4

2009-03-01

Procesory sygnałowe I / III

7

Asembler - składnia rozkazu

MNEMONIK

Smem, src

MNEMONIK

Smem, TS , src

MNEMONIK

Smem, 16, src [, dst]

MNEMONIK

Smem [, SHIFT] , src [ , dst]

Smem

:

Single data-memory operand

src, dst:

A (accumulator A)

B (accumulator B)

–16

≤ SHIFT ≤ 15

Xmem, Ymem:

Dual data-memory operands

Operandy -

2009-03-01

Procesory sygnałowe I / III

8

Lista rozkazów (1) procesora DSP

• Rozkazy operacji arytmetycznych

(przykłady)

Składnia

operacja

słów

cykli

ADD Smem, src

src = src + Smem

1 1

ADD Smem [, SHIFT], src [, dst]

dst = src + Smem << SHIFT

2 2

MAC Xmem, Ymem, src [, dst]

dst = src + Xmem * Ymem,

1 1

T = Xmem

MACAR T, src [, dst]

dst = rnd(src + T * A(32–16))

1 1

SQURA Smem, src

src = src + Smem * Smem,

T = Smem

1 1

DADD Lmem, src [, dst]

If C16 = 0

1 1

dst = Lmem + src

If C16 = 1

dst(39–16) = Lmem(31–16) + src(31–16)

dst(15–0) = Lmem(15–0) + src(15–0)

2009-03-01

5

2009-03-01

Procesory sygnałowe I / III

9

Lista rozkazów (2) procesora DSP

•Rozkazy operacji logicznych

(przykłady)

Składnia

operacja

słów

cykli

AND Smem, src

src = src & Smem

1 1

AND # lk [, SHFT], src [, dst]

dst = src & #lk << SHFT

2 2

SFTA src, SHIFT [, dst]

dst = src << SHIFT {arithmetic shift} 1 1

BIT Xmem, BITC

TC = Xmem(15 – BITC)

1 1

BITT Smem

TC = Smem(15 – T(3–0))

1 1

BITF Smem, # lk

TC = (Smem && #lk)

2 2

CMPM Smem, # lk

TC = (Smem == #lk)

2 2

CMPR CC, ARx

Compare ARx with AR0

1 1

CC

00

EQ

01

LT

10

GT

11

NEQ

2009-03-01

Procesory sygnałowe I / III

10

Lista rozkazów (3) procesora DSP

• Rozkazy sterujące przebiegiem programu

(przykłady)

Składnia

operacja

słów

cykli

B[D] pmad

PC = pmad(15–0)

2 4/[2¶]

BACC[D] src

PC = src(15–0)

1 6/[4¶]

BANZ[D] pmad, Sind

if (Sind <>0) then PC = pmad(15–0)

2

4‡/2§/

Sind – adres pośredni (ARx)

[2¶ ]

BC[D] pmad, cond [, cond [, cond] ]

if (cond(s)) then PC = pmad(15–0)

2 5‡/3§/

[3¶]

FB[D] extpmad

PC = pmad(15–0), XPC = pmad(22–16)

2 4/[2¶ ]

† liczba słów i cykli przy założeniu pracy z danymi w DARAM

‡ warunek prawdziwy

§ warunek fałszywy

¶ Instrukcja z opóźnieniem (Delayed instruction)

2009-03-01

6

2009-03-01

Procesory sygnałowe I / III

11

Lista rozkazów (3a) procesora DSP

• Rozkazy sterujące przebiegiem programu

(przykłady)

Składnia

operacja

słów

cykli

CALL[D] pmad

– –SP, PC + 2[4 ¶ ] = TOS,

PC = pmad(15–0)

2 4/[2§]

CALA[D] src

– –SP, PC + 1[3 ¶ ] = TOS,

PC = src(15–0)

1 6/[4¶]

CC[D] pmad, cond [, cond [, cond]]

if (cond(s)) then – –SP,

PC + 2[4 ¶ ] = TOS,

PC = pmad(15–0)

2 5‡/3§/

[3 ¶ ]

RET[D]

PC = TOS, ++SP

1 5/[3¶]

RETE[D]

PC = TOS, ++SP, INTM = 0

1 5/[3¶]

† liczba słów i cykli przy założeniu pracy z danymi w DARAM

‡ warunek prawdziwy

§ warunek fałszywy

¶ Instrukcja z opóźnieniem (Delayed instruction)

2009-03-01

Procesory sygnałowe I / III

12

Lista rozkazów (3b) procesora DSP

• Rozkazy sterujące przebiegiem programu

(przykłady)

Składnia

operacja

słów

cykli

RPT Smem

Repeat single, RC = Smem

1 3

RPT # K

Repeat single, RC = #K

1 1

RPT # lk

Repeat single, RC = #lk

2 2

RPTB[D] pmad

Repeat block, RSA = PC + 2[4 ¶ ],

2 4/[2¶ ]

REA = pmad, BRAF = 1

RPTZ dst, # lk

Repeat single, RC = #lk, dst = 0

2 2

FRAME K

SP = SP + K

1 1

XC n , cond [, cond[, cond]]

If (cond(s)) then execute the next n

instructions;

1 1

n = 1 or 2

† / ‡ / § / ¶ - patrz uwagi na poprzednim slajdzie

2009-03-01

7

2009-03-01

Procesory sygnałowe I / III

13

Składnia

operacja

słów

cykli

LD Smem, dst

dst = Smem

1 1

LD Xmem, SHFT, dst

dst = Xmem << SHFT

1 1

LD # lk [, SHFT], dst

dst = #lk << SHFT

2 2

SACCD src, Xmem, cond

If (cond) Xmem = src << (ASM – 16) 1 1

MVPD pmad, Smem

Smem = pmad

2 3

MVDD Xmem, Ymem

Ymem = Xmem

1

1

PORTR PA, Smem

Smem = PA

2 2

READA Smem

Smem = A

1 5

ST src, Ymem

Ymem = src << (ASM – 16)

|| MAC Xmem, dst

|| dst = dst + T * Xmem

1 1

Lista rozkazów (4) procesora DSP

• Rozkazy sterujące przesłaniami

(przykłady)

2009-03-01

Procesory sygnałowe I / III

14

Lista rozkazów (5) procesora DSP

• Rozkazy specjalizowane

(przykłady)

Składnia

operacja

słów

cykli

MACD Smem, pmad, src

src = src + Smem * pmad,

2 3

T = Smem, (Smem + 1) = Smem

FIRS Xmem, Ymem, pmad

B = B + A * pmad

A = (Xmem + Ymem) << 16

2 3

LMS Xmem, Ymem

B = B + Xmem * Ymem

A = A + Xmem << 16 + 2^15

1 1

MAX dst

dst = max(A, B)

1 1

MIN dst

dst = min(A, B)

1 1

ABDST Xmem, Ymem

B = B + |A(32–16)|

A = (Xmem – Ymem) << 16

1 1

SQDST Xmem, Ymem

B = B + A(32–16) * A(32–16)

A = (Xmem – Ymem) << 16

1 1

2009-03-01

8

2009-03-01

Procesory sygnałowe I / III

15

Istotne pojęcia do przyswojenia

• Mapa pamięci

• Adres

• Przestrzeń

Programu

• Przestrzeń

Danych

• DARAM

• SARAM

• Blok pamięci

• bit OVLY

• bit MP/MC

• Bit DROM

• MMR

• ...

• McBSP

• HPI

• GPIO

• DMA

• Boot-loader

• PLL

• Power Down

• Idle Mode

• Repetycja rozk.

• Repetycja bloku

• Mnemonik.

• Operand

• Rozkazy

arytmetyczne,

logiczne,

sterowania programem,

przesłań,

specjalizowane

• Rozkazy z opóźnieniem

• ...

Wyszukiwarka

Podobne podstrony:

2009 wykl04 BW 2fsid 26852 Nieznany

2009 03 26 prezentacja pochodne Nieznany

INF2 2009 Wykl 04 Zaoczne 4na1 Nieznany

2009 test lo[1]pgiid 26764 Nieznany

2009 czerwiec zad 3 Egzamin pra Nieznany (2)

2009 02 17 test egzaminacyjny n Nieznany (2)

2009 10 05 praid 26669 Nieznany

mje 2009 matematyka 5SP e2 test Nieznany

2009 czerwiec zad 2 Egzamin pra Nieznany

fizyka 2009 styczen podst id 17 Nieznany

Logistyka 2009 s287 292 id 2726 Nieznany

fizyka 2009 maj podst id 175998 Nieznany

2009 styczen zad 1 Egzamin prak Nieznany (2)

2009 EGZ WSTEPNY NA AM Nieznany (2)

Codex Alimentarius od 31 grudnia 2009 r NIE POZWÓLMY NA TO, NIEZNANE i CIEKAWE, Codex Alimentarius

2009 czerwiec zad 5 Egzamin pra Nieznany (2)

matura 2009 roz a2 styczen id 6 Nieznany

więcej podobnych podstron