Przerzutnik

Przerzutnik

Przerzutnik

Przerzutnik

Przerzutnik

Przerzutnik

Przerzutnik

Przerzutnik

Schmitt

Schmitta

a

Schmitt

Schmitta

a

Schmitt

Schmitta

a

Schmitt

Schmitta

a

6 marca 2011

Wojciech Kucewicz

2

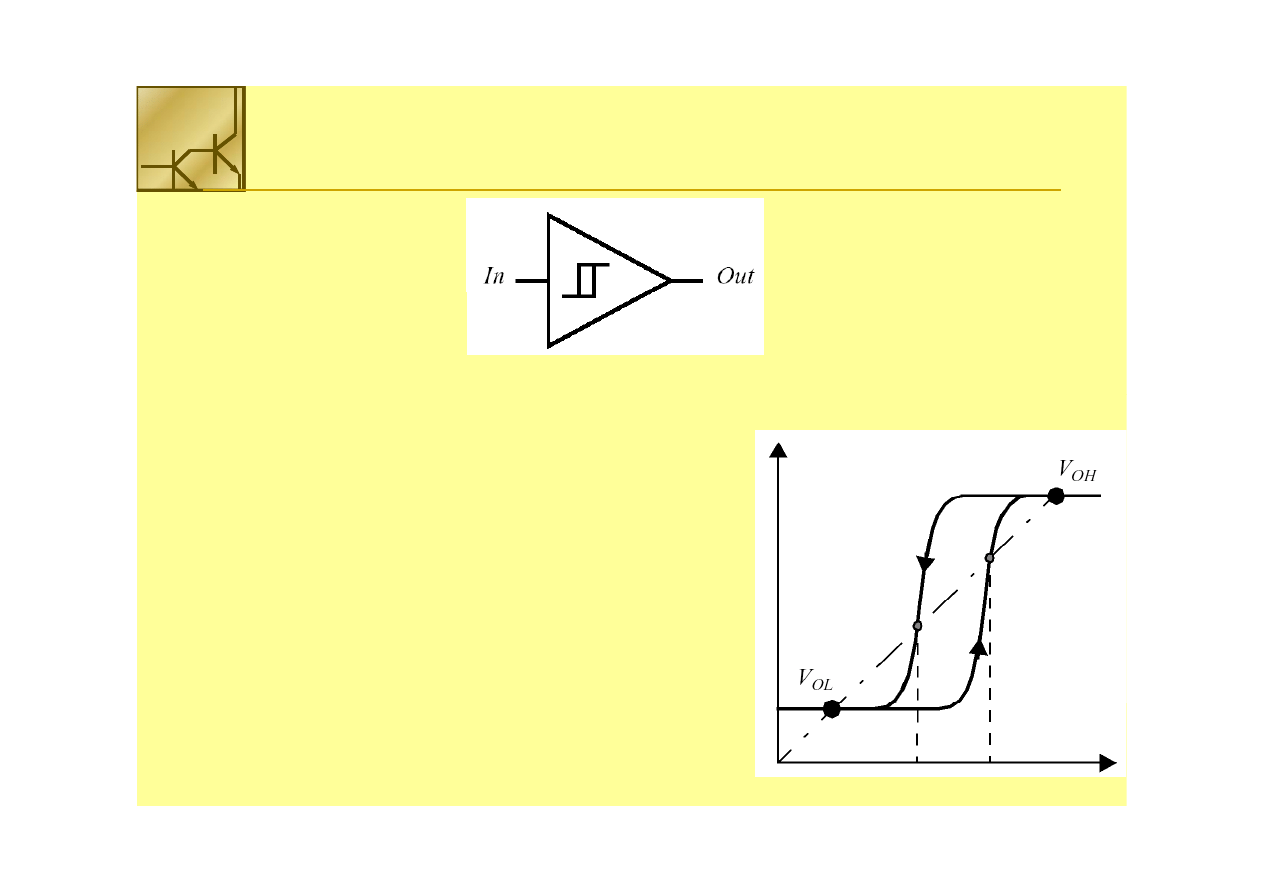

The Schmitt Trigger

The Schmitt Trigger

The Schmitt Trigger

The Schmitt Trigger

A Schmitt trigger is a device with two important properties:

A Schmitt trigger is a device with two important properties:

1. The voltage-transfer characteristic

VV

in

in

VV

Out

Out

1. The voltage transfer characteristic

of the device displays

different

different

switching thresholds for positive

switching thresholds for positive--

nd n

tiv

nd n

tiv

in input si n ls

in input si n ls

in

in

and negative

and negative--going input signals.

going input signals.

6 marca 2011

Wojciech Kucewicz

3

VV

in

in

VV

M

M--

VV

M+

M+

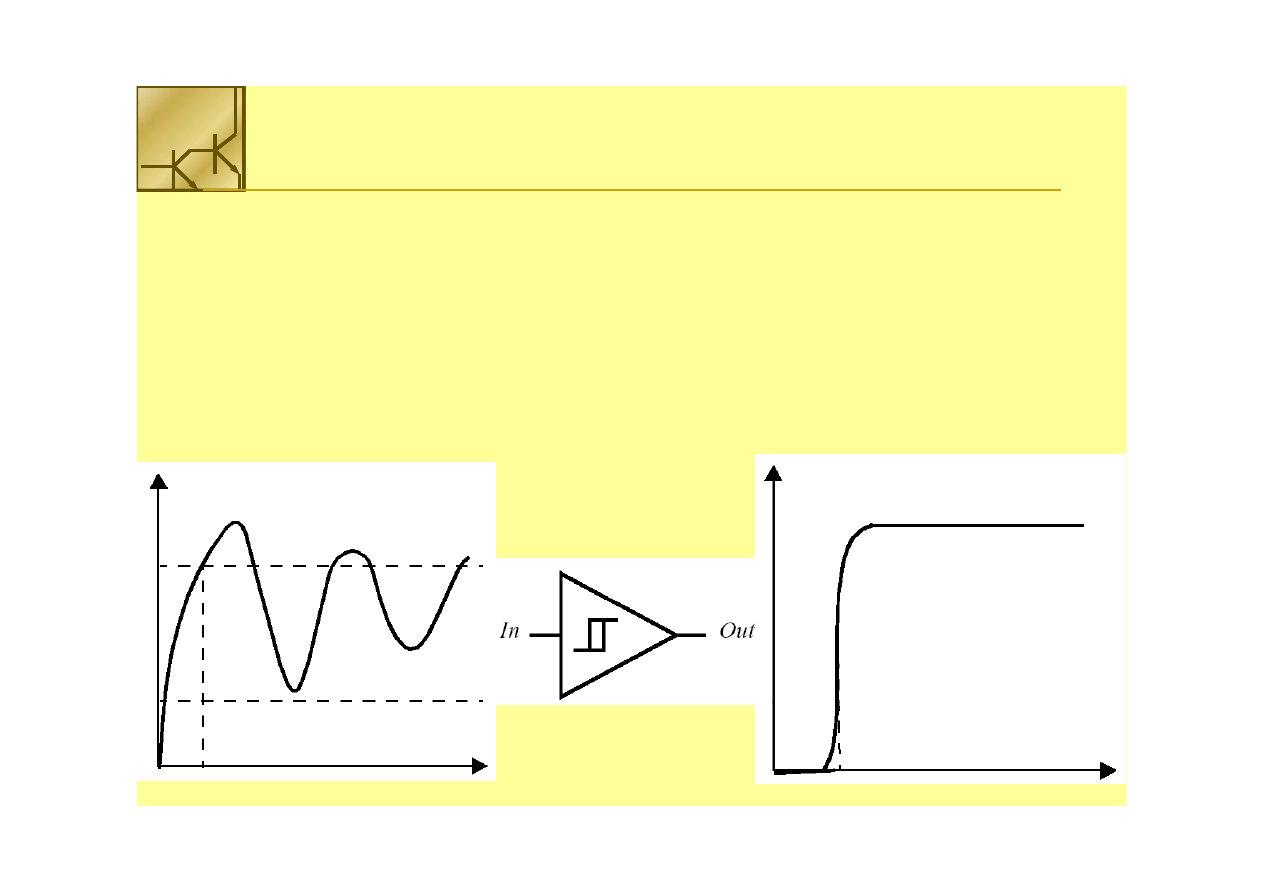

The Schmitt Trigger

The Schmitt Trigger

The Schmitt Trigger

The Schmitt Trigger

2. It responds to a slowly changing input waveform with a

fast

transition time at the output.

transition time at the output.

m

p

m

p

VV

in

in

VV

Out

Out

in

in

VV

M+

M+

6 marca 2011

Wojciech Kucewicz

4

VV

M

M--

tt

tt

tt

oo

tt

oo

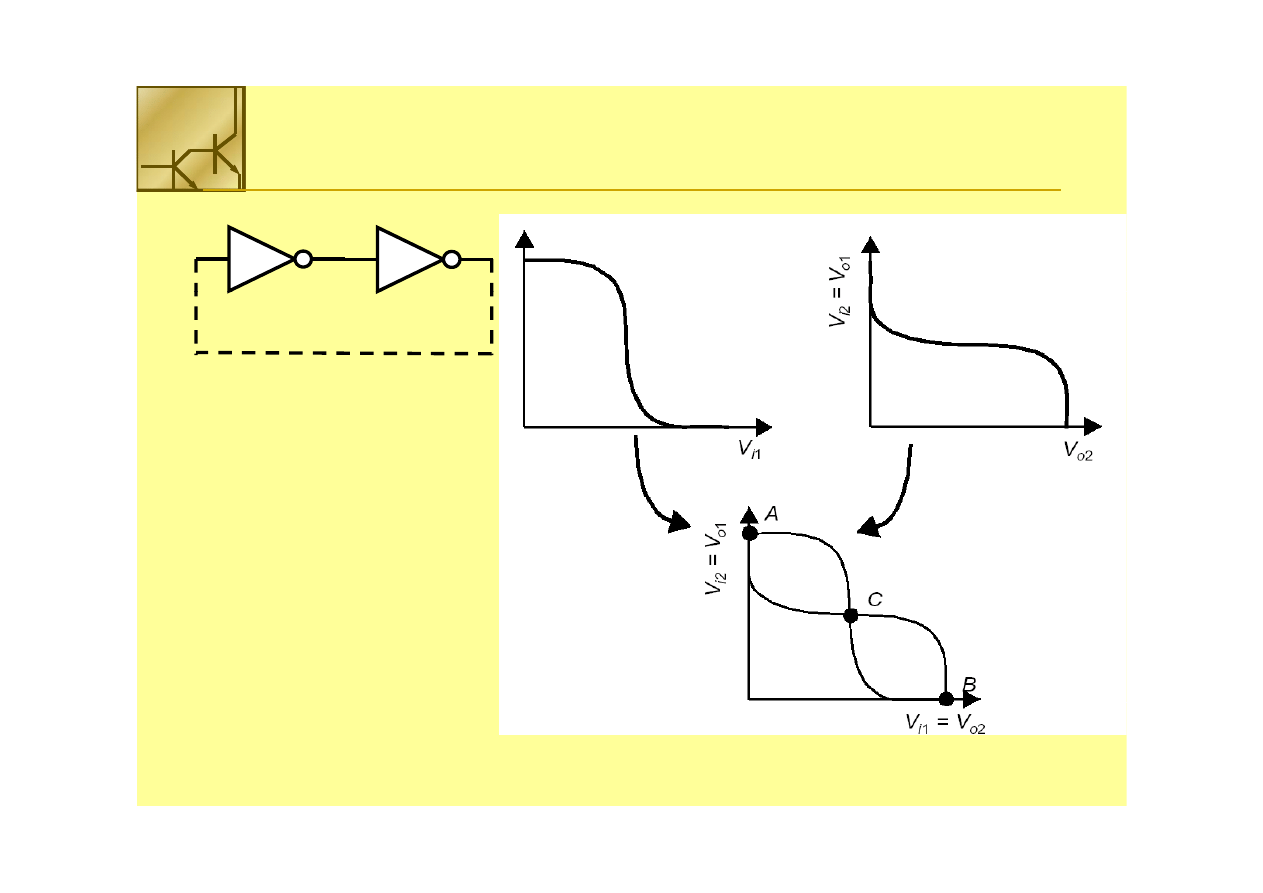

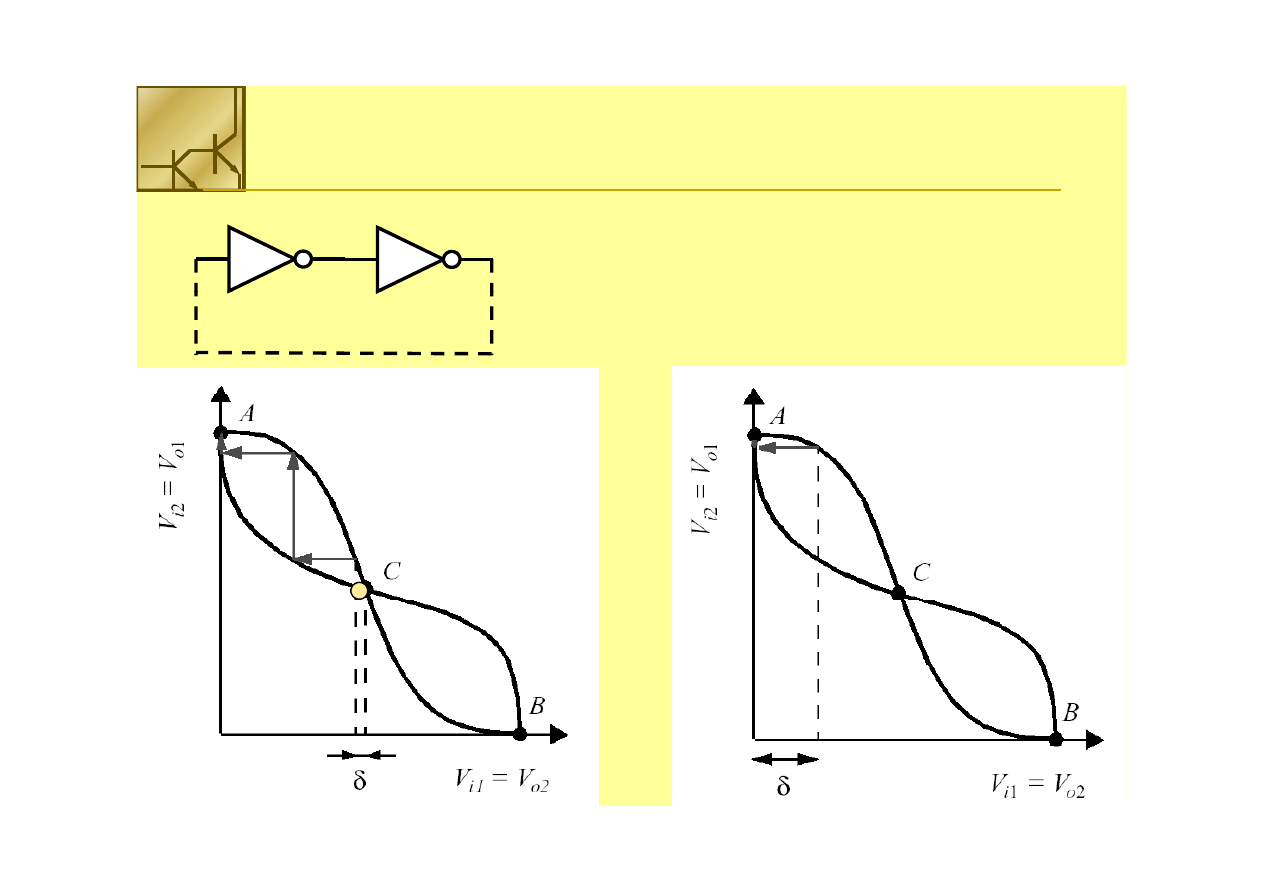

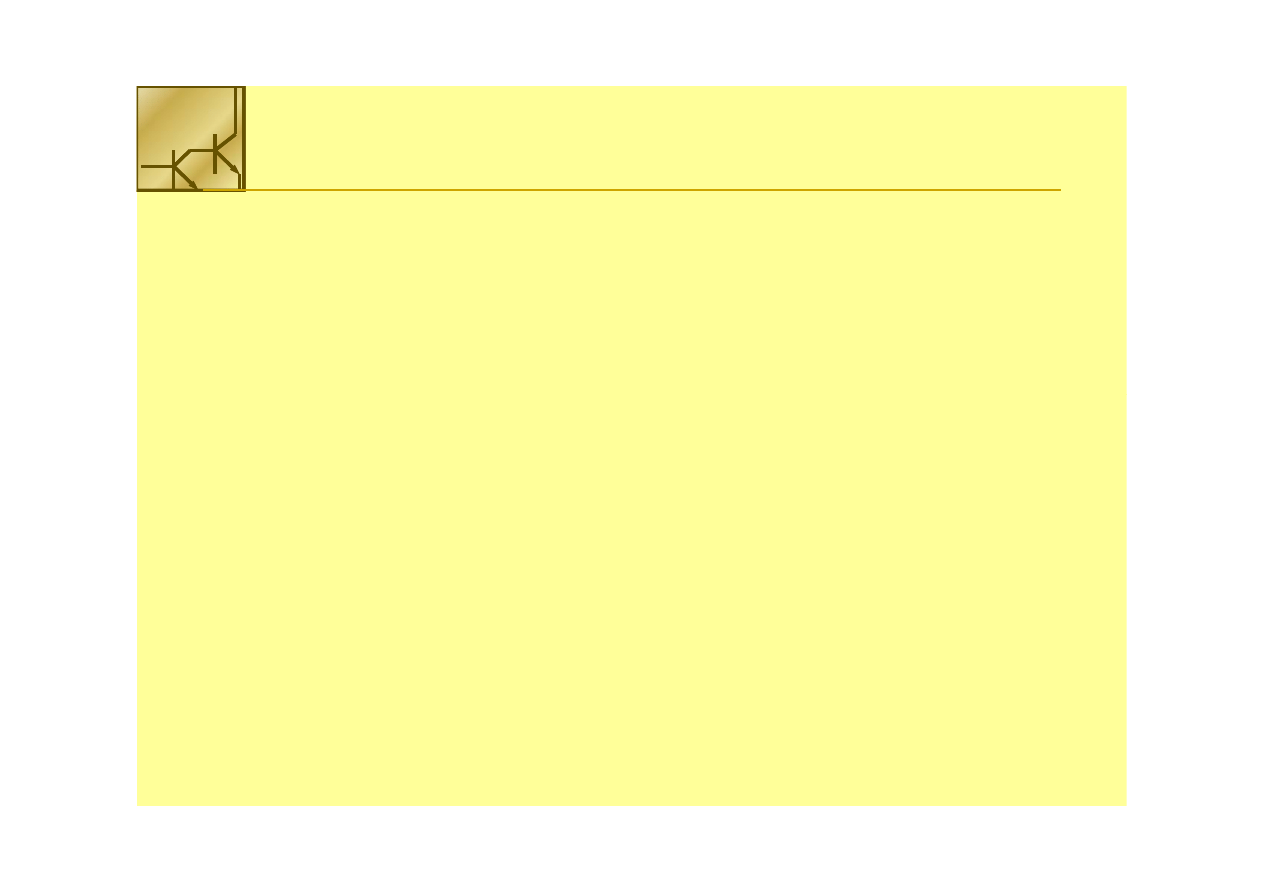

Positive Feedback in Bistable Circuits

Positive Feedback in Bistable Circuits

Positive Feedback in Bistable Circuits

Positive Feedback in Bistable Circuits

VV

i1

i1

VV

o1

o1

VV

i2

i2

VV

o2

o2

VV

o1o1

6 marca 2011

Wojciech Kucewicz

5

Positive

Positive FFee

eeddback in

back in BBistable

istable CCircuits

ircuits

Positive

Positive FFee

eeddback in

back in BBistable

istable CCircuits

ircuits

VV

i1

i1

VV

o1

o1

VV

i2

i2

VV

o2

o2

6 marca 2011

Wojciech Kucewicz

6

8ram

The Schmitt Trigger

The Schmitt Trigger

The Schmitt Trigger

The Schmitt Trigger

VV

In

In

VV

Out

Out

High switch threshold for the low

High switch threshold for the low--to

to--high

high

Low switch threshold for the high

Low switch threshold for the high--to

to--low

low

Low switch threshold for the high

Low switch threshold for the high--to

to--low

low

VV

M+

M+

VV

M

M--

6 marca 2011

Wojciech Kucewicz

7

Fast transition time

Fast transition time

PPPPPamięci

Pamięci

Pamięci

Pamięci

m ę

m ę

m ę

m ę

6 marca 2011

Wojciech Kucewicz

8

Pamięci

Pamięci

Pamięci

Pamięci

Najprostszymi układami mającymi własności pamiętania są

Najprostszymi układami mającymi własności pamiętania są

jp

y

j y

p

jp

y

j y

p

przerzutniki.

przerzutniki.

Funkcję prostych pamięci mogą spełniać również rejestry i liczniki.

Funkcję prostych pamięci mogą spełniać również rejestry i liczniki.

ję p

y

p

ę

gą p

j

y

ję p

y

p

ę

gą p

j

y

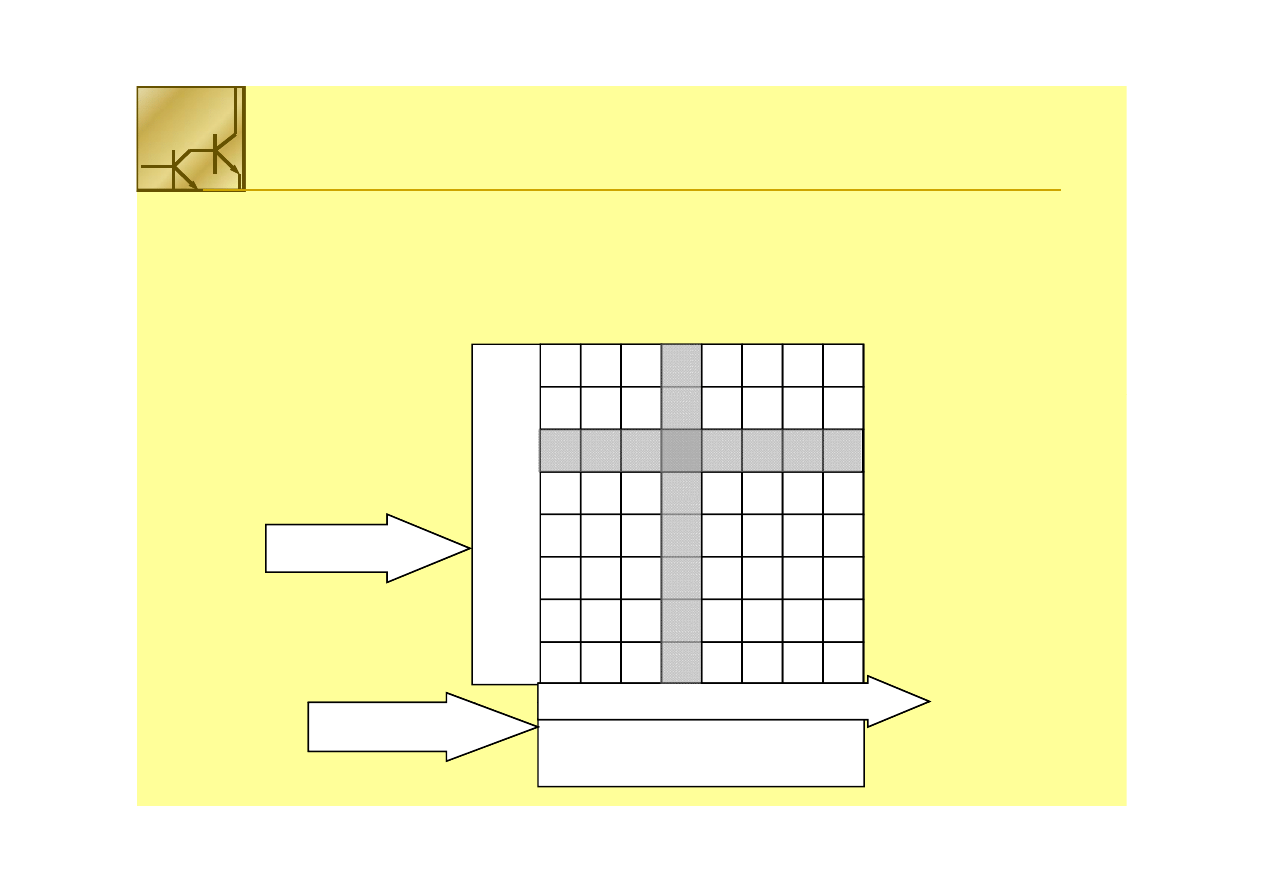

Pamięci są to specjalne układy komórek pozwalające na pamiętanie

Pamięci są to specjalne układy komórek pozwalające na pamiętanie kk--

słów

słów o długości

o długości nn--bitów

bitów (Pamięć o pojemności k x n)

(Pamięć o pojemności k x n)

słów

słów o długości

o długości nn bitów

bitów. (Pamięć o pojemności k x n)

. (Pamięć o pojemności k x n)

Zespół wszystkich komórek pamięciowych danego układu tworzy

Zespół wszystkich komórek pamięciowych danego układu tworzy

matrycę pamięciową

matrycę pamięciową

matrycę pamięciową

matrycę pamięciową

..

Poziome paski matrycy nazywamy

Poziome paski matrycy nazywamy

wierszami (liniami słowa),

wierszami (liniami słowa),

a pionowe

a pionowe

kolumnami (liniami bitu)

kolumnami (liniami bitu)

6 marca 2011

Wojciech Kucewicz

9

––

kolumnami (liniami bitu).

kolumnami (liniami bitu).

Pamięci

Pamięci

Pamięci

Pamięci

Każde przecięcie wiersza z kolumną wyznacza jedną komórkę

Każde przecięcie wiersza z kolumną wyznacza jedną komórkę

pamięciową matrycy. Aby umożliwić zapis i odczyt stanu określonej

pamięciową matrycy. Aby umożliwić zapis i odczyt stanu określonej

k ó k l

d

ć d

d l

ł

l

b

k ó k l

d

ć d

d l

ł

l

b

komórki, należy zaadresować odpowiednią linię słowa i linię bitu.

komórki, należy zaadresować odpowiednią linię słowa i linię bitu.

L i n i a s ł o w a

Dekoder a

d

Dekoder a

d

Linia

dresowy wier

s

dresowy wier

s

Adres wiersza

Adres wiersza

bit

szyszy

Linia danych

Linia danych

u

6 marca 2011

Wojciech Kucewicz

10

Dekoder adresowy kolumn

Dekoder adresowy kolumn

Adres kolumny

Adres kolumny

Linia danych

Linia danych

Pamięci

Pamięci

Pamięci

Pamięci

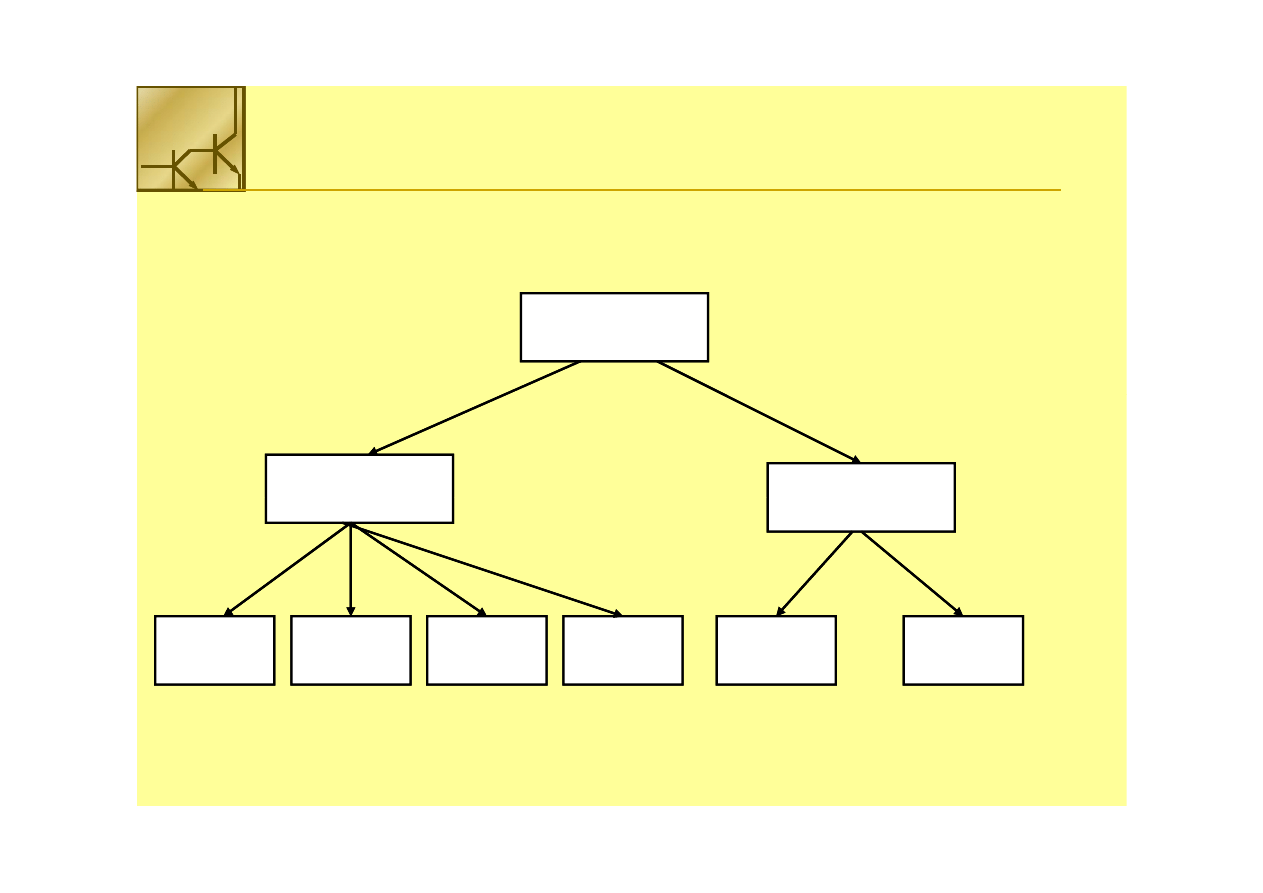

Rodzaje pamięci:

Rodzaje pamięci:

j p

j p

Pamięci

Pamięci

RAM

RAM

ROM

ROM

RAM

RAM

DRAM

DRAM

SRAM

SRAM

PROM

PROM

EPROM

EPROM

EEPROM

EEPROM

Flash

Flash

EEPROM

EEPROM

6 marca 2011

Wojciech Kucewicz

11

RAM

RAM

RAM

RAM

RAM

RAM

RAM

RAM

6 marca 2011

Wojciech Kucewicz

12

RAM

RAM

RAM

RAM

Pamięci RAM (Random Access

Pamięci RAM (Random Access Memory

Memory) ) –– pamięci o swobodnym

pamięci o swobodnym

d t i )

żli i j ó

bki i

j k

i bki

d

t

d t i )

żli i j ó

bki i

j k

i bki

d

t

dostępie) umożliwiają zarówno szybki zapis jak i szybki odczyt

dostępie) umożliwiają zarówno szybki zapis jak i szybki odczyt

danych do/z

danych do/z pamięci.

pamięci.

Wyróżnia się pamięci statyczne SRAM, w których komórki pamięci są

Wyróżnia się pamięci statyczne SRAM, w których komórki pamięci są

układy

układy wielotranzystorowe

wielotranzystorowe oraz pamięci dynamiczne DRAM, w

oraz pamięci dynamiczne DRAM, w

których komórki pamięci są

których komórki pamięci są jednotranzystorowe

jednotranzystorowe..

y

p

ę

y

p

ę

j

y

j

y

6 marca 2011

Wojciech Kucewicz

13

S

SRAM

RAM

S

SRAM

RAM

S

SRAM

RAM

S

SRAM

RAM

6 marca 2011

Wojciech Kucewicz

14

SRAM

SRAM

SRAM

SRAM

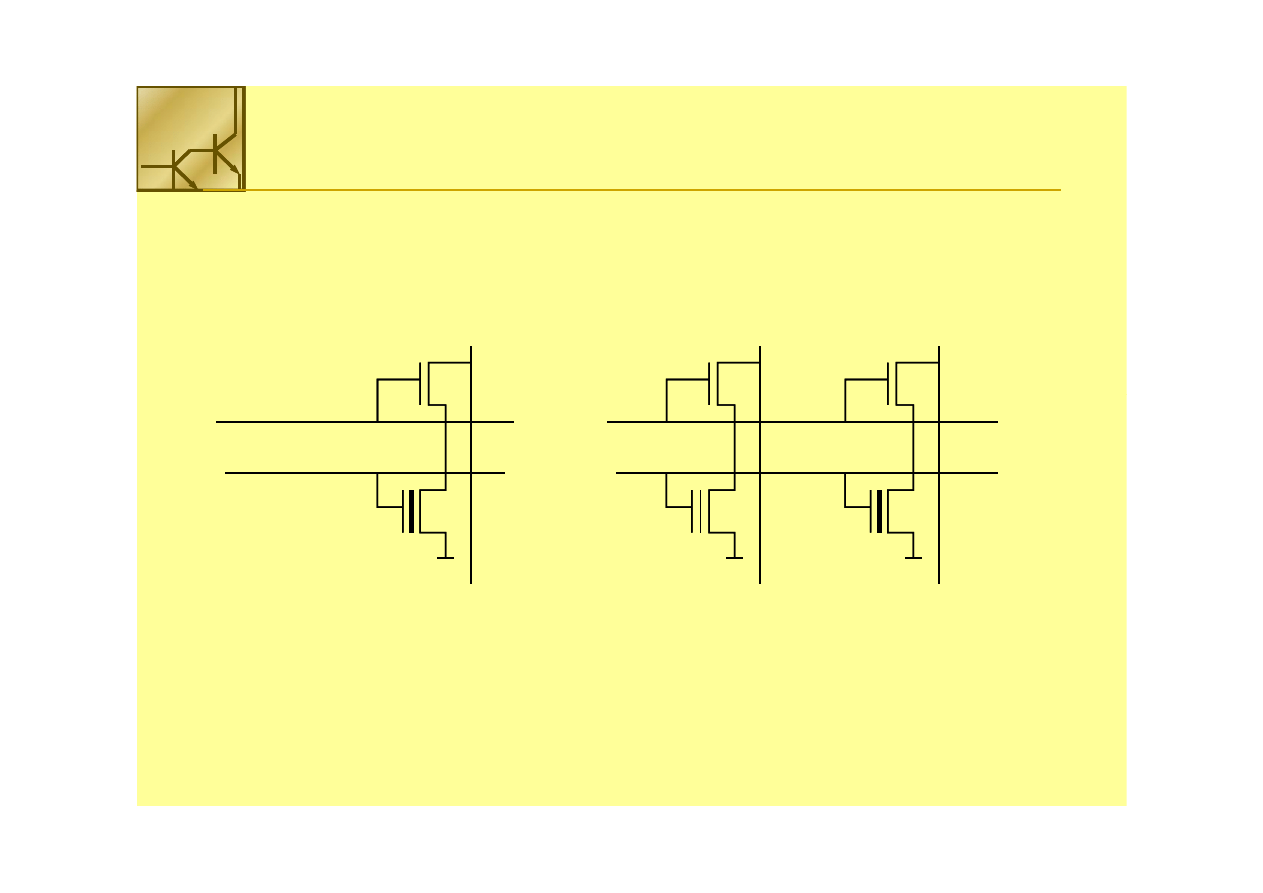

Pamięci statyczne mogą być synchronizowane zegarem (pamięci

synchroniczne) lub nie (pamięci asynchroniczne).

Szybsze pamięci synchroniczne (DDR- Double Data Rate) wykorzystują

do przesyłania słów obydwa zbocza sygnału zegarowego.

W ciągu jednego okresu zegara przesyłane są dwa słowa.

6 marca 2011

Wojciech Kucewicz

15

SRAM

SRAM

SRAM

SRAM

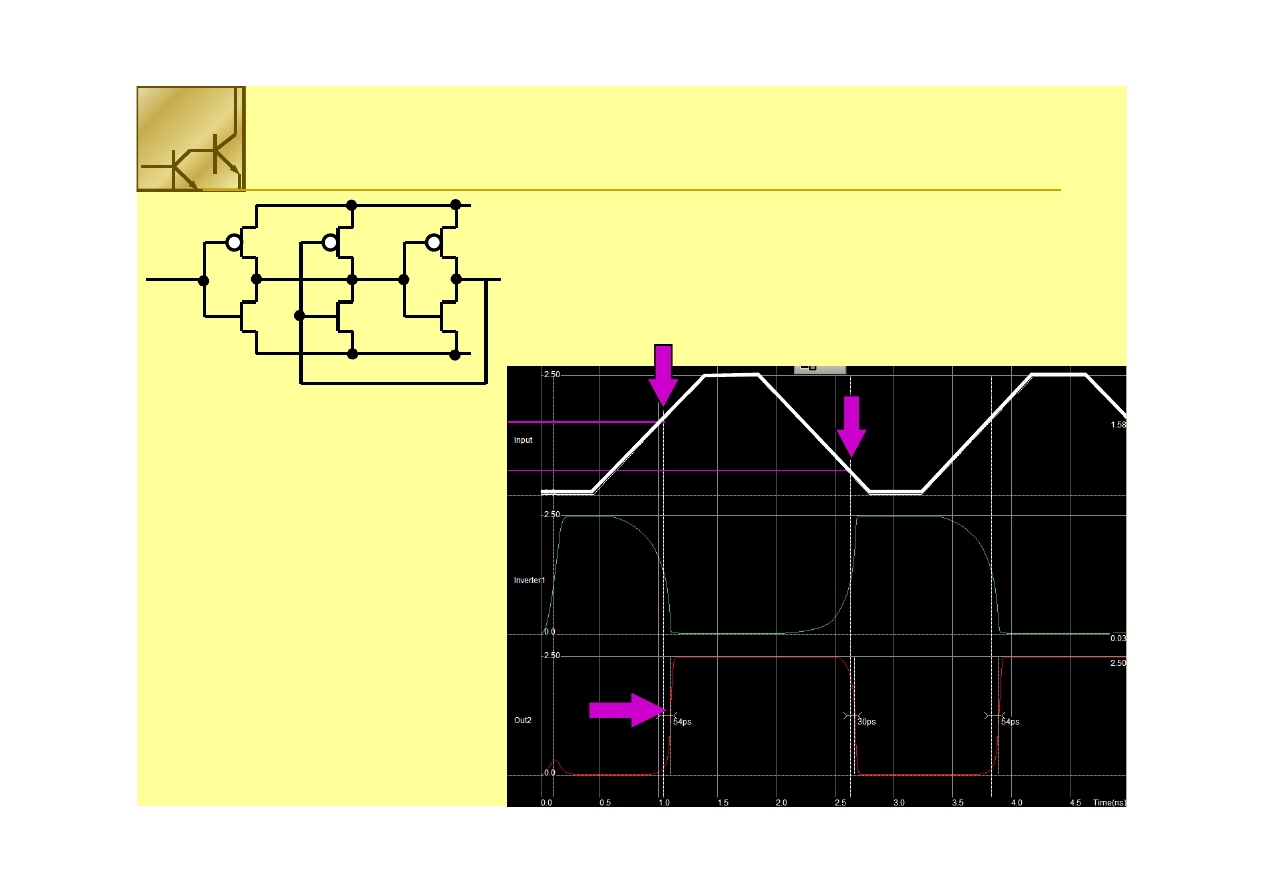

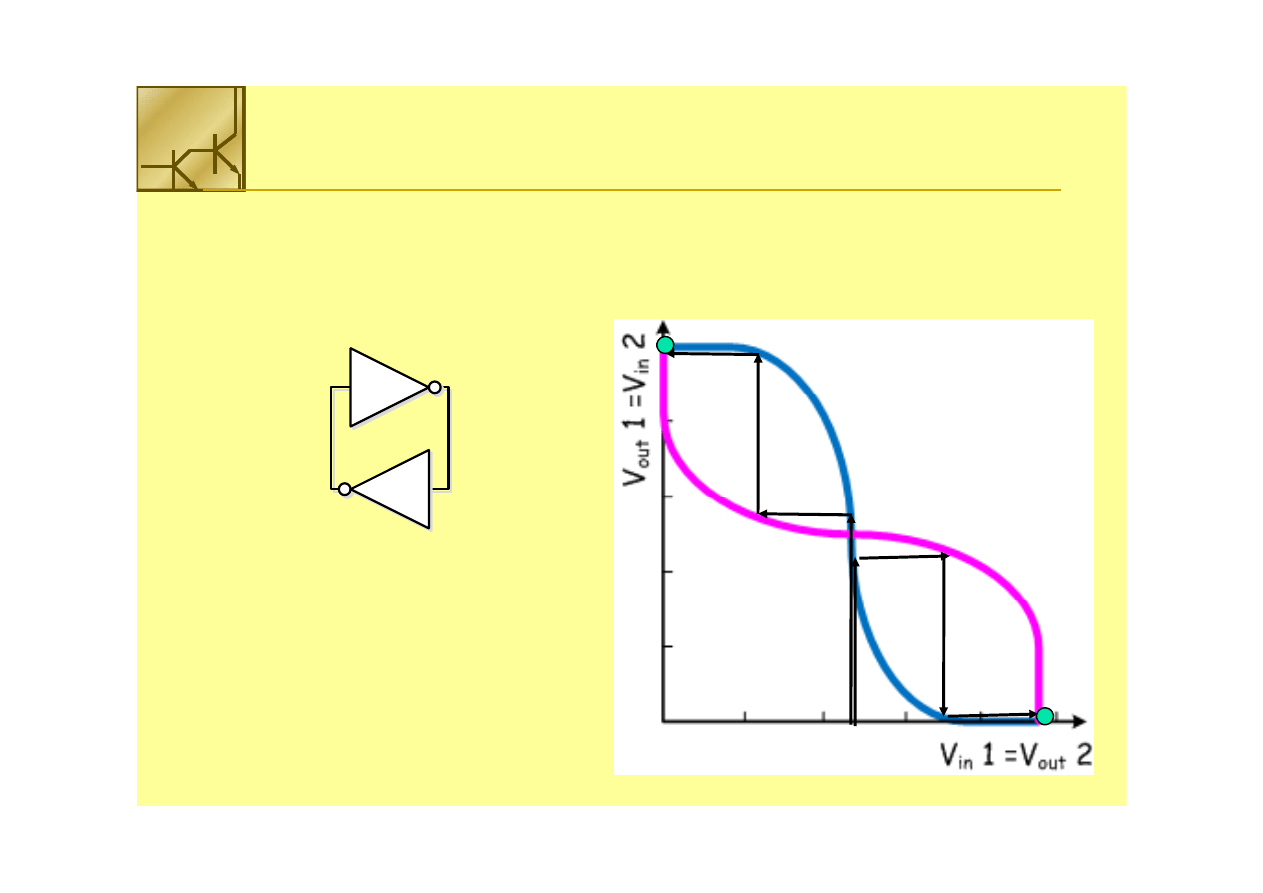

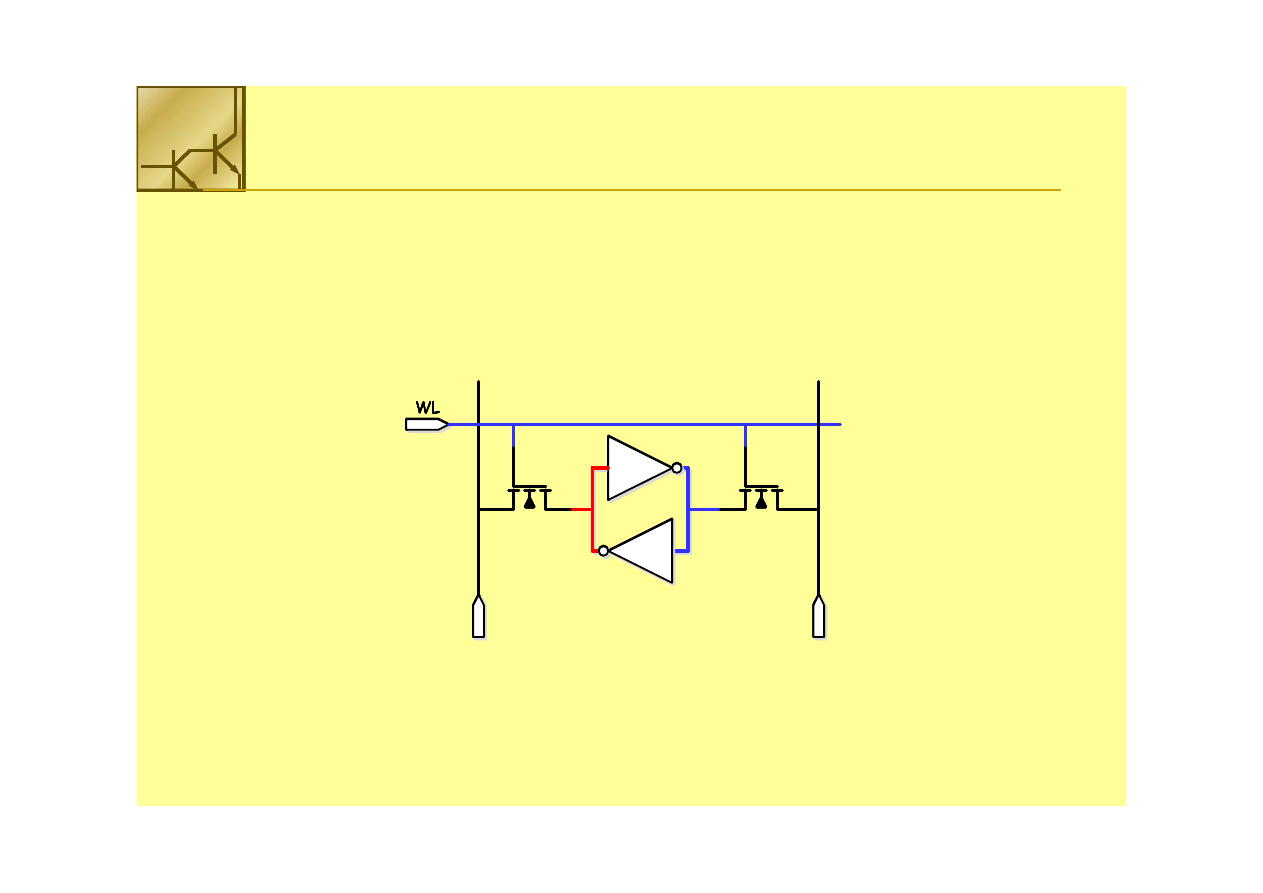

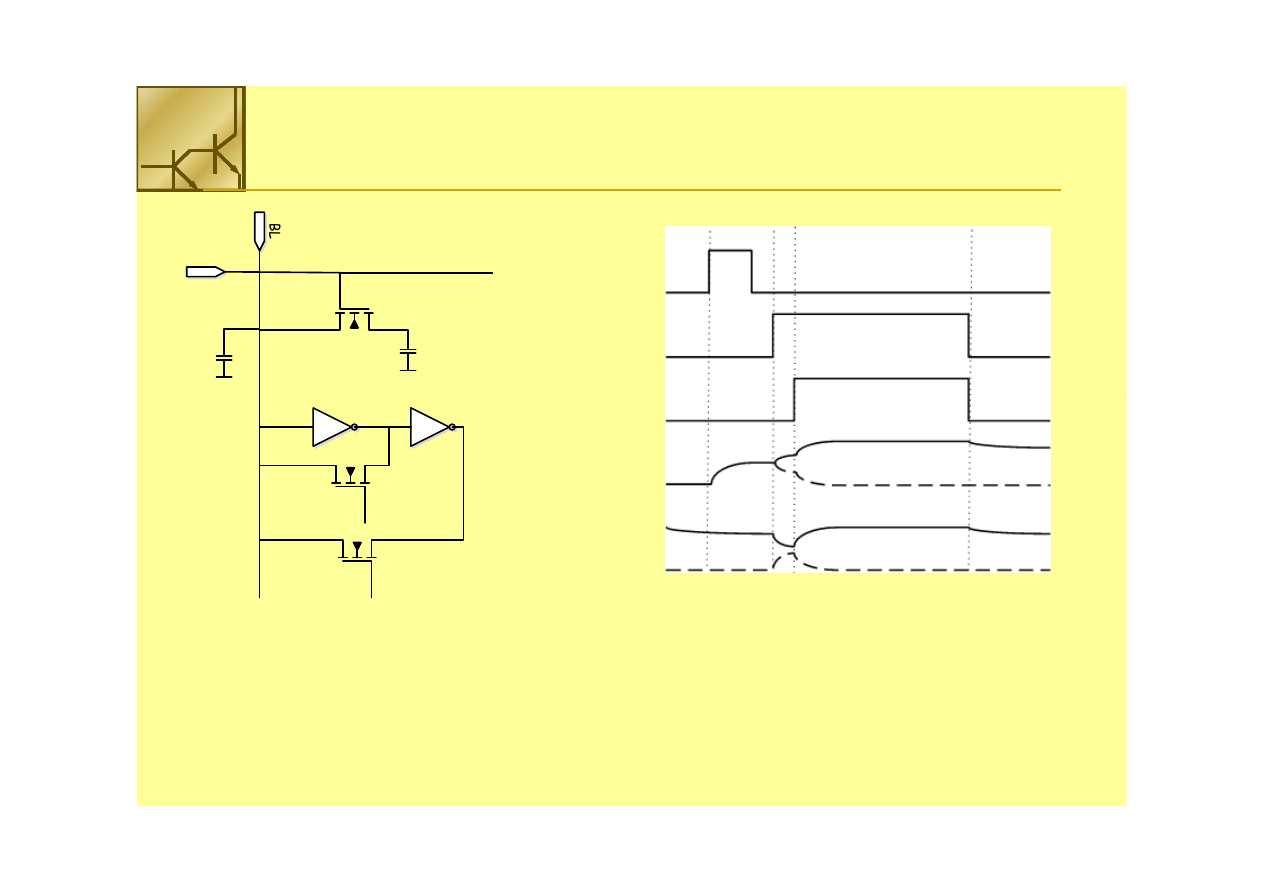

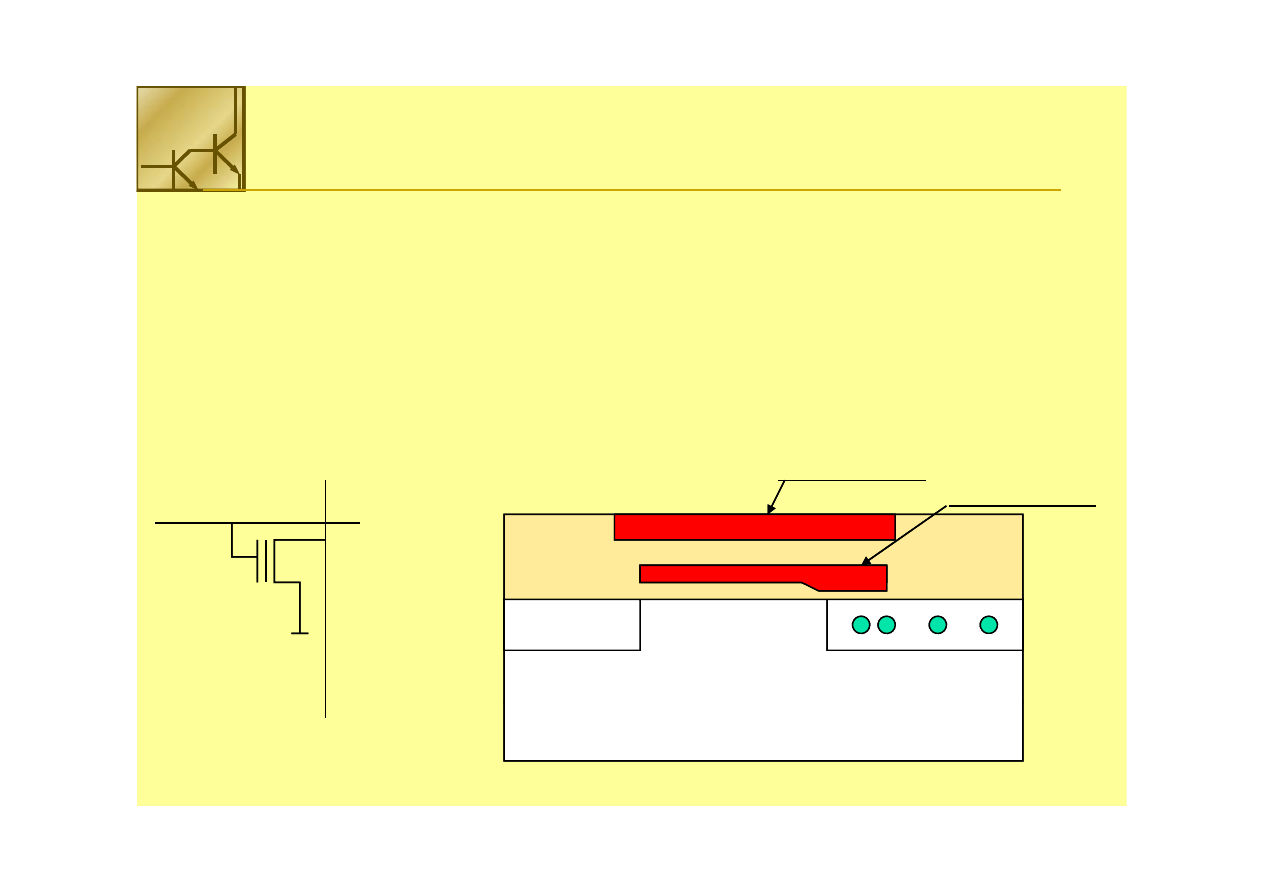

Komórka pamięci statycznej wykorzystuje układ bistabilny złożony z

dwóch inwerterów.

A

V

in

1 = V

out

2

V

out

1 = V

in

2

Układ ma dwa stany stabilne w

punktach A i B

B

6 marca 2011

Wojciech Kucewicz

16

B

SRAM

SRAM

SRAM

SRAM

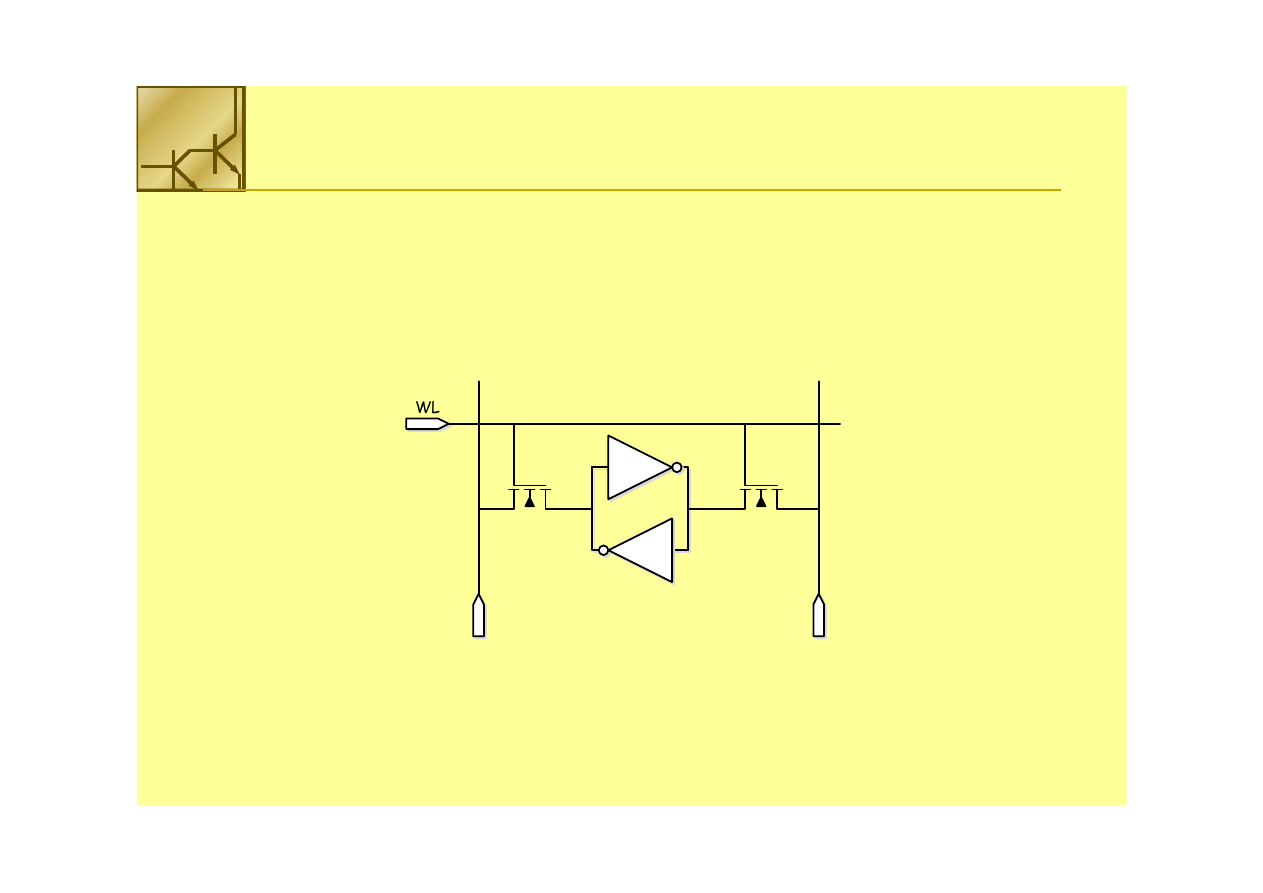

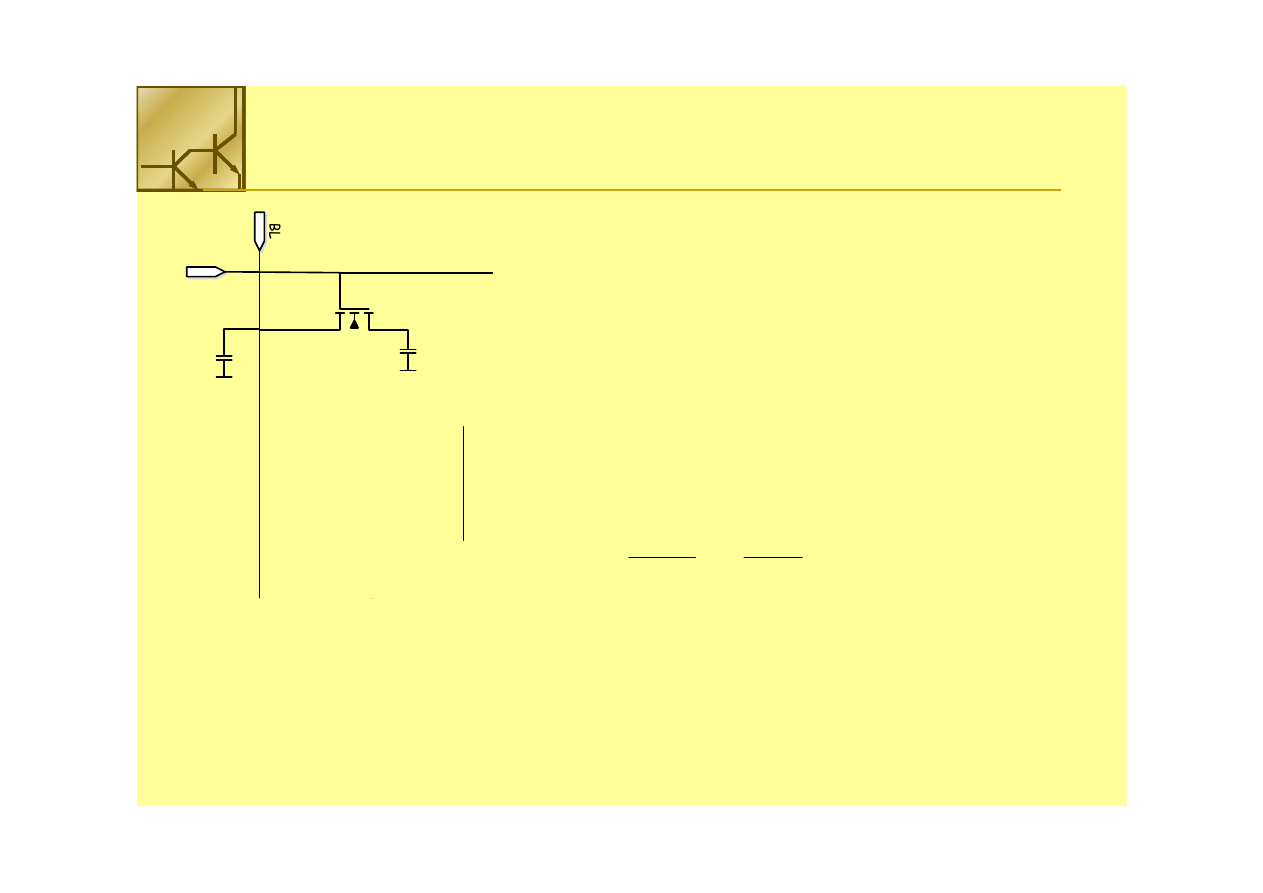

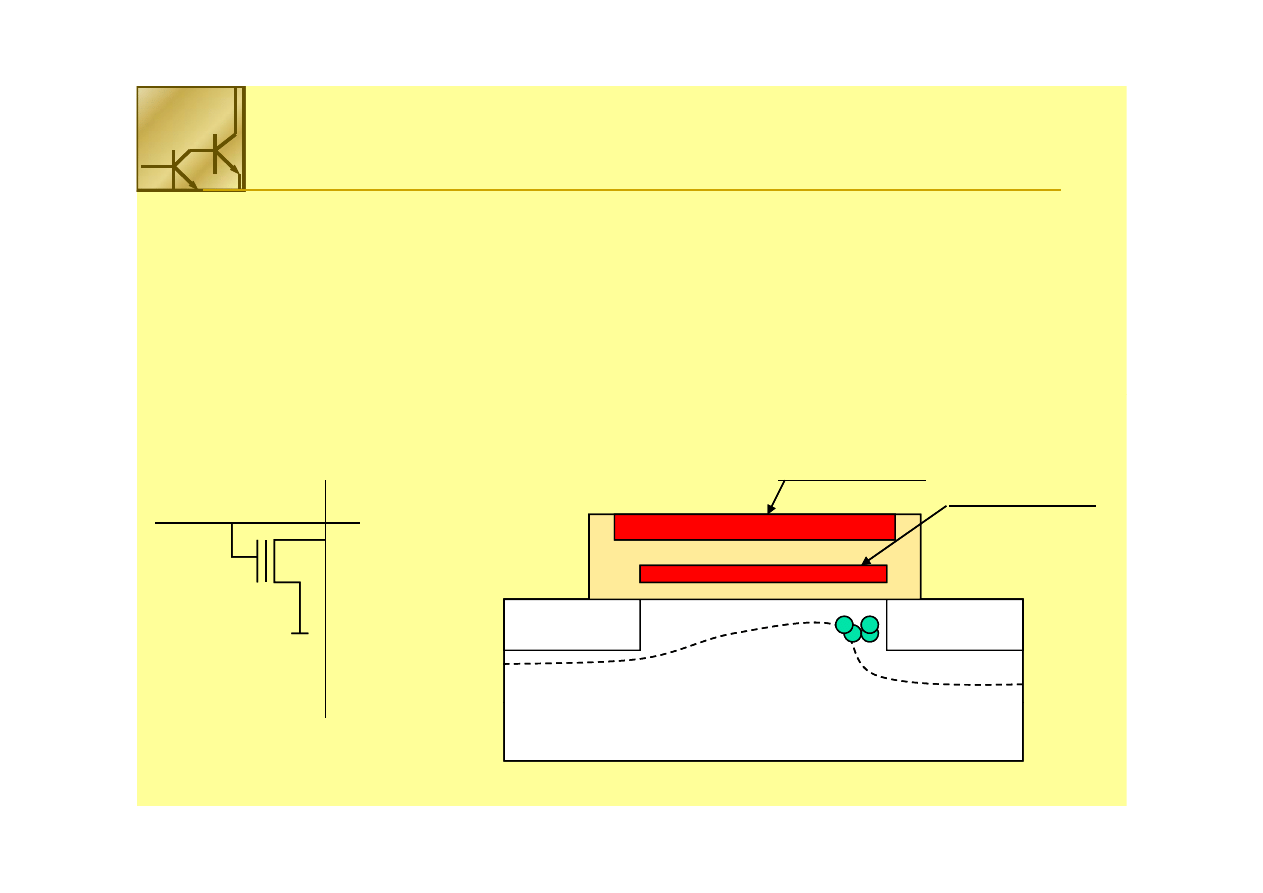

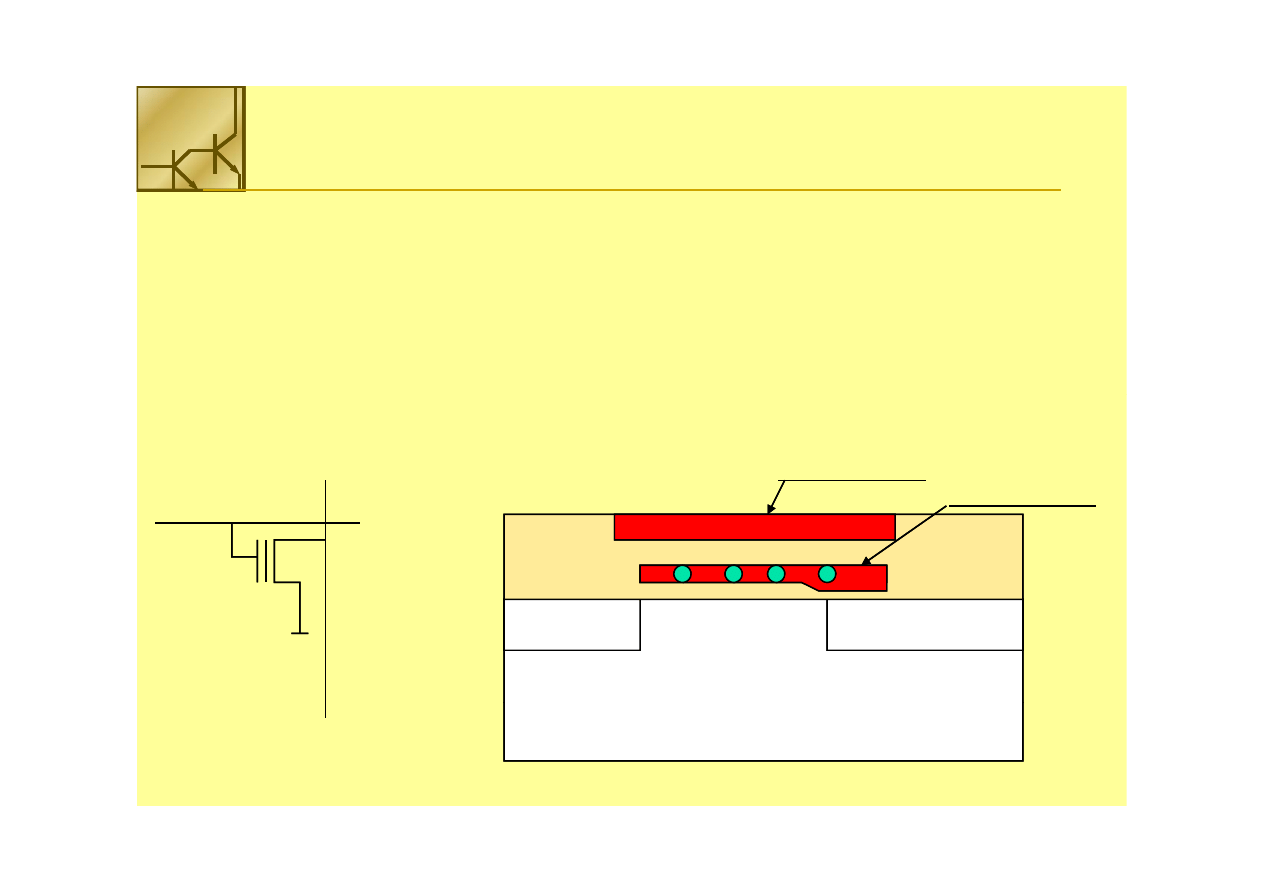

Komórka pamięci statycznej zawiera dwa inwertery oraz dwa

tranzystory dostępowe NMOS. Łącznie komórka SRAM zbudowana

y

y

ęp

ą

m

jest z 6 tranzystorów i nosi nazwę komórki „6T”.

BL

BL’

6 marca 2011

Wojciech Kucewicz

17

SRAM

SRAM -- zapis

zapis

SRAM

SRAM -- zapis

zapis

Dane wystawione na liniach bitu są zapamiętane w układzie bistabilnym.

BL

BL’

BL

BL’

BL

BL’

BL

BL’

BL

BL’

6 marca 2011

Wojciech Kucewicz

18

SRAM

SRAM -- odczyt

odczyt

SRAM

SRAM -- odczyt

odczyt

Stan układu bistabilnego ładuje (rozładowuje) linie bitu przy wysokim

napięciu na linii słowa..

p ę

BL

BL’

BL

BL’

BL

BL’

6 marca 2011

Wojciech Kucewicz

19

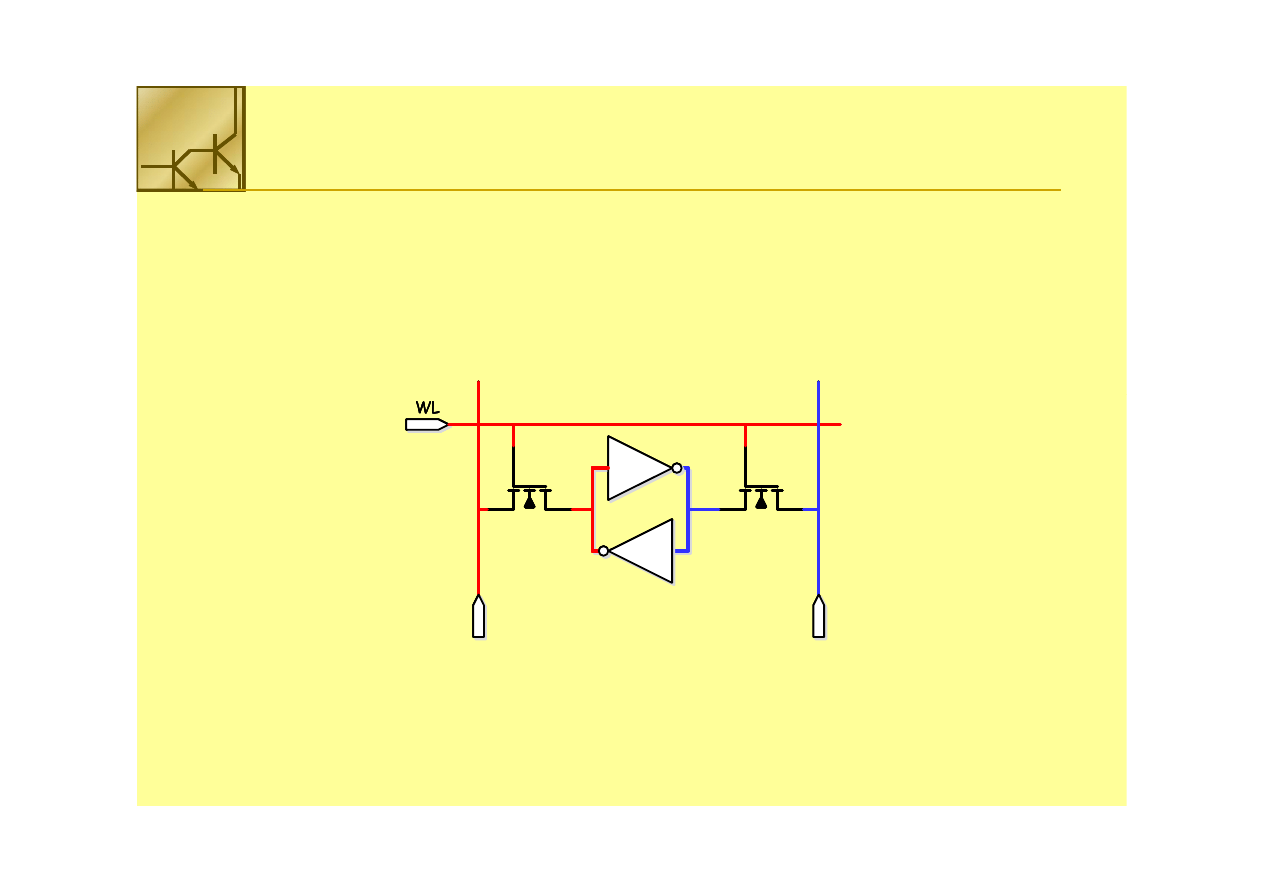

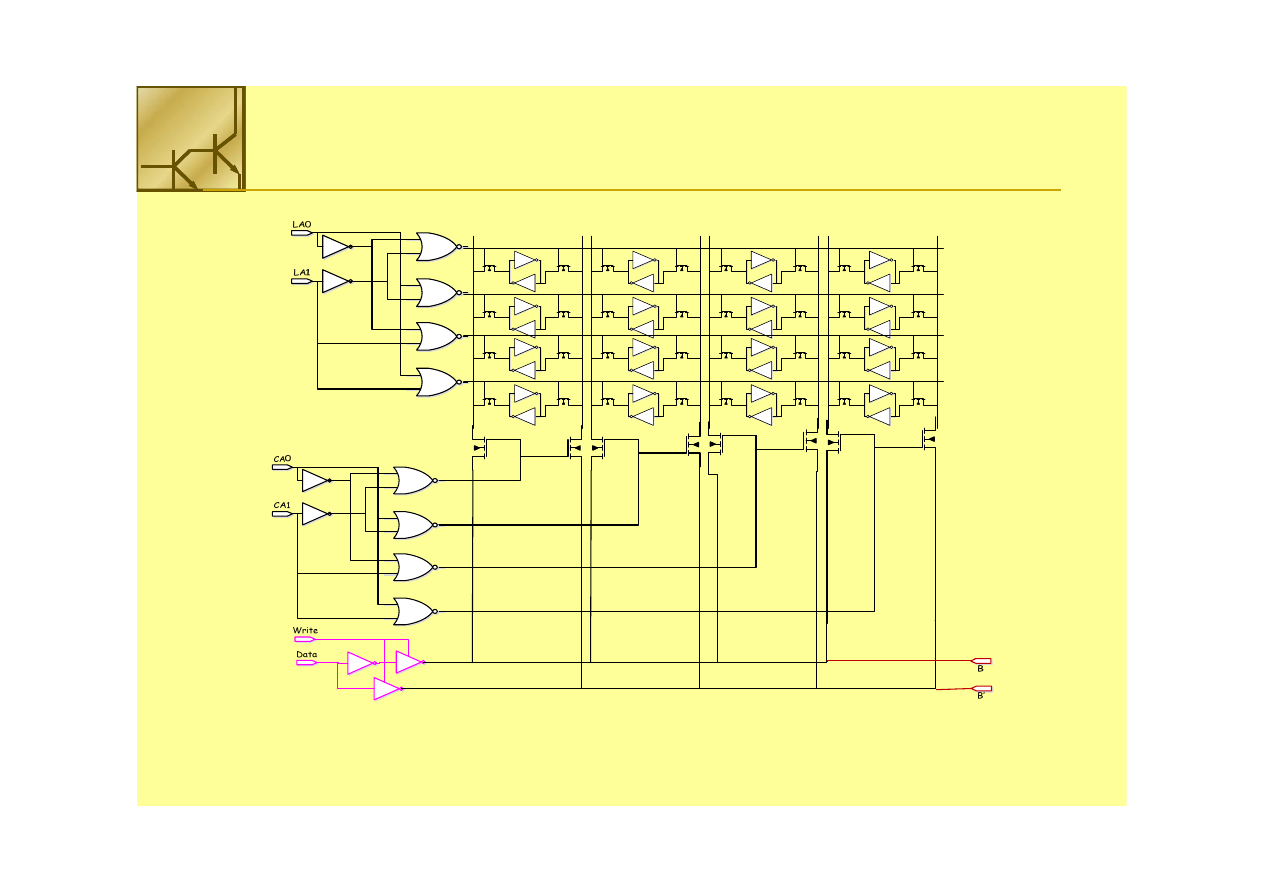

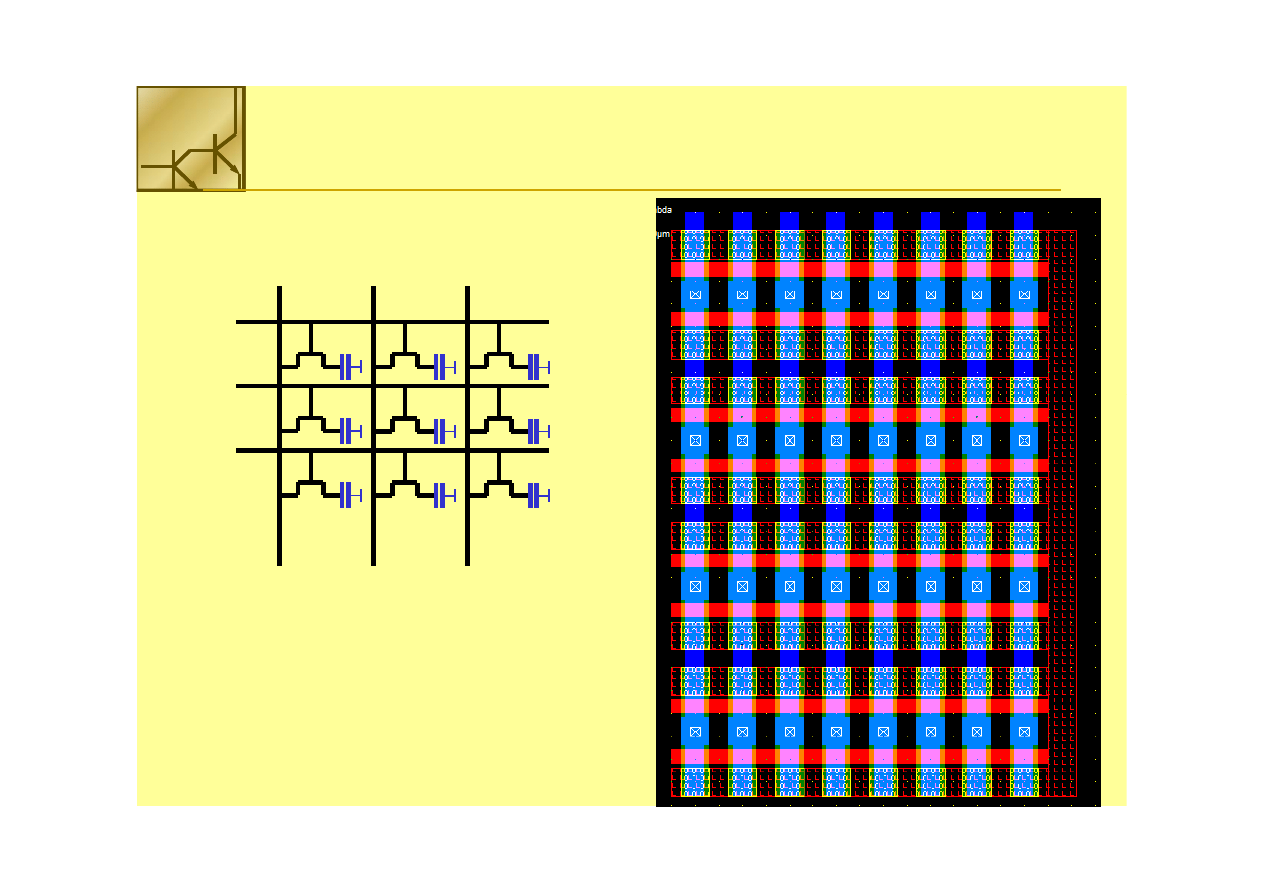

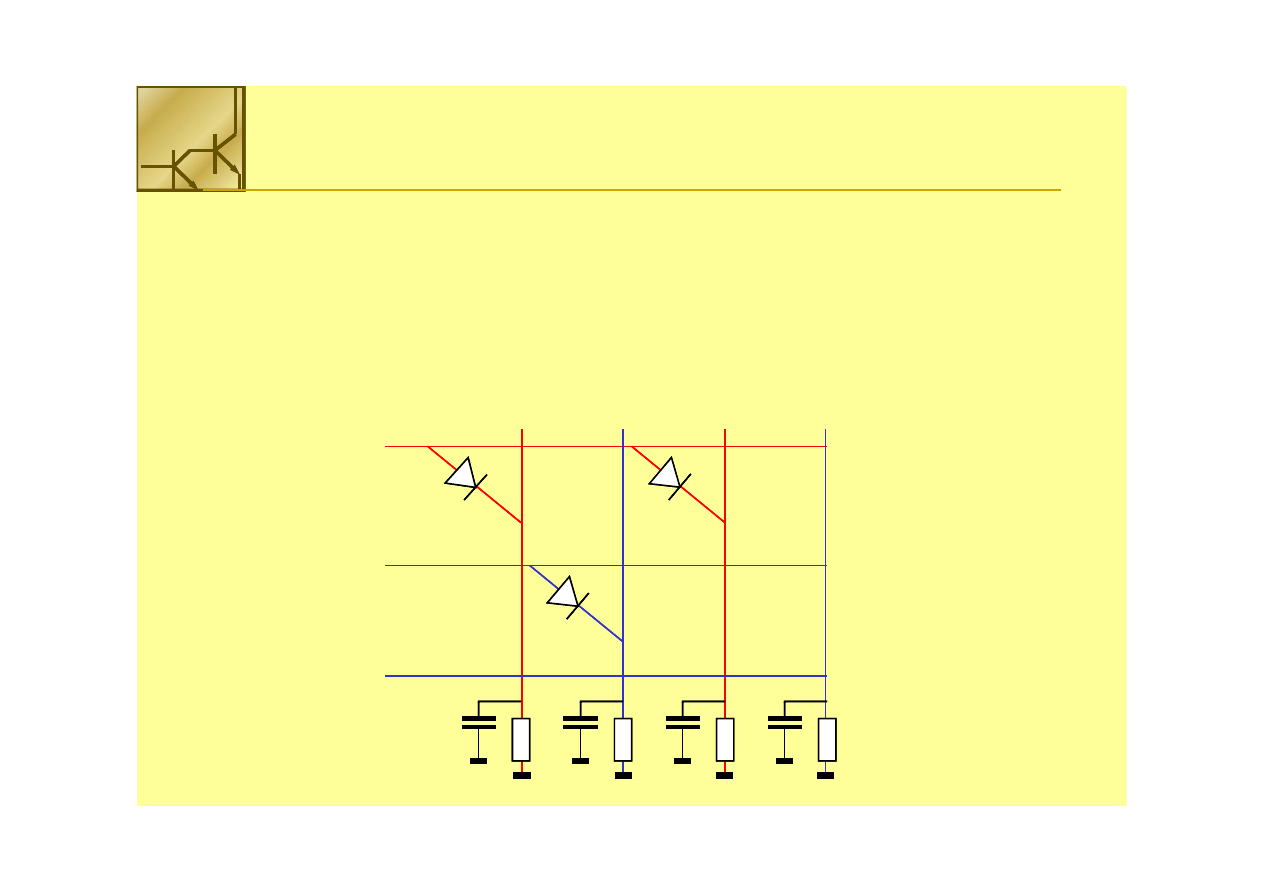

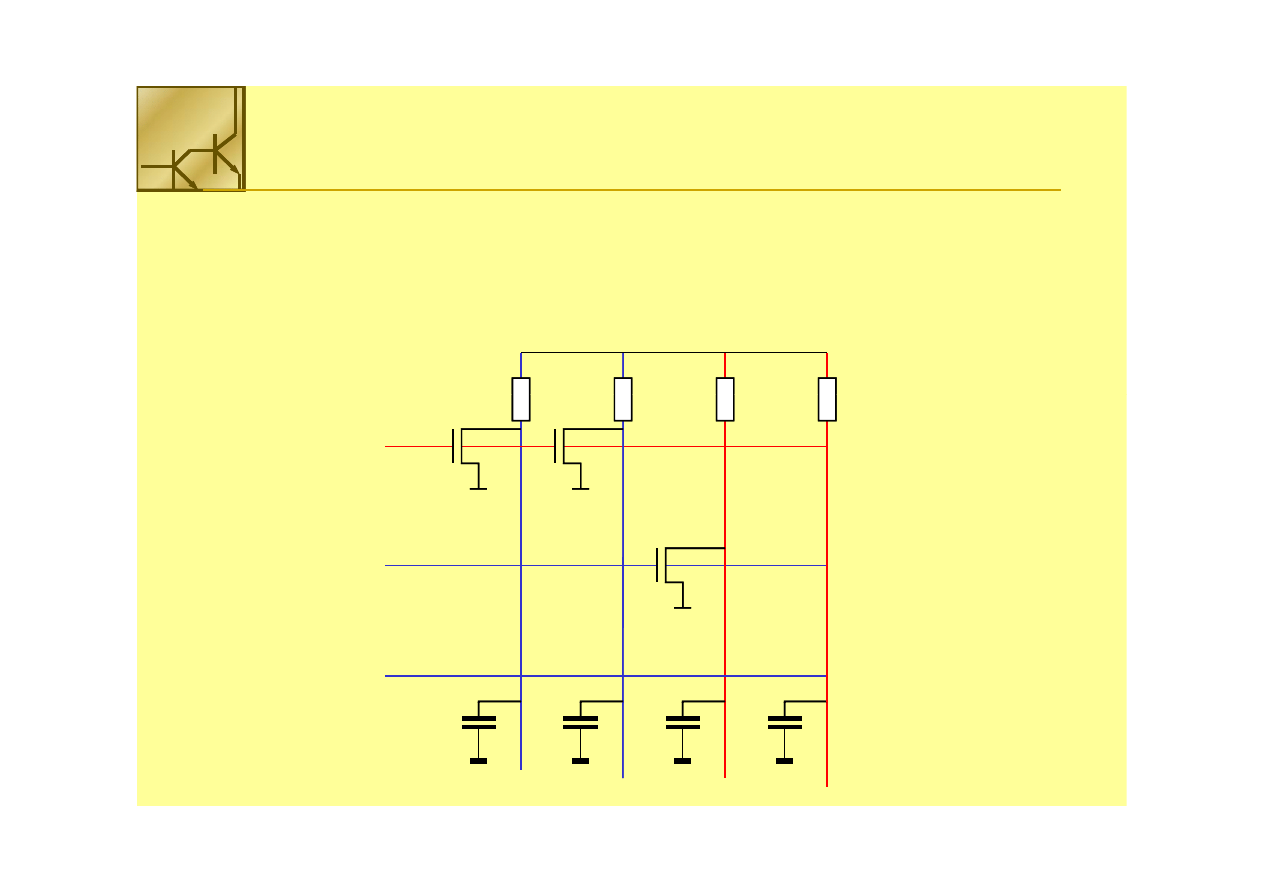

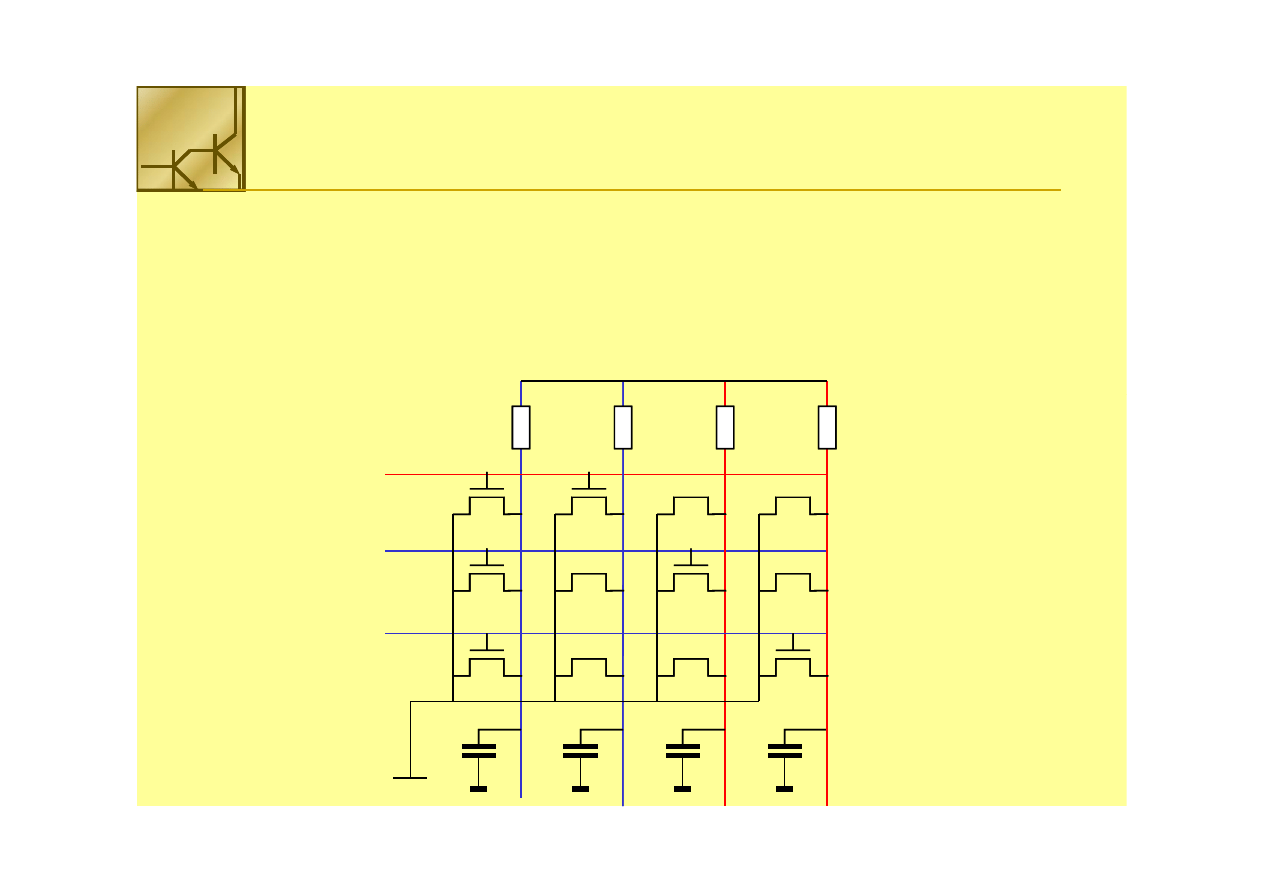

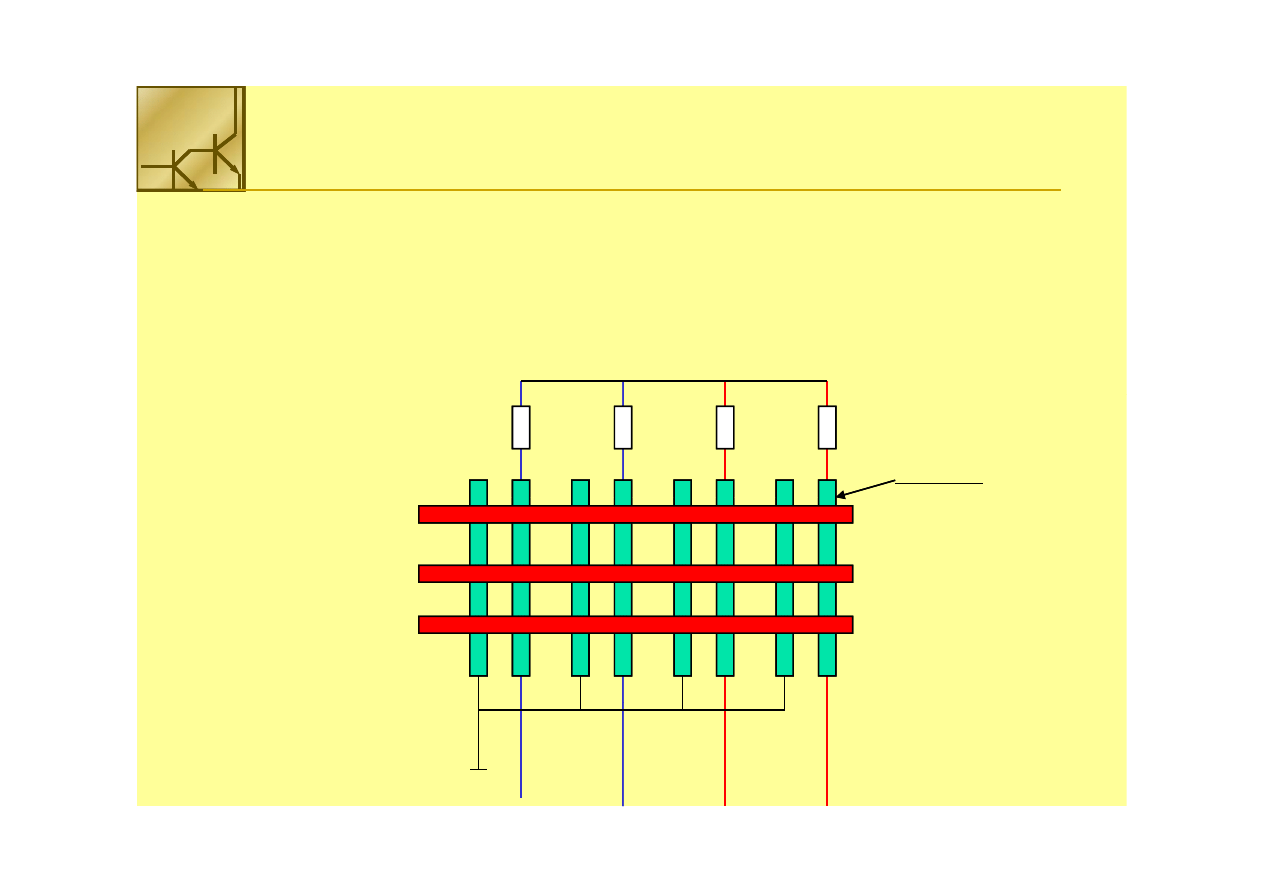

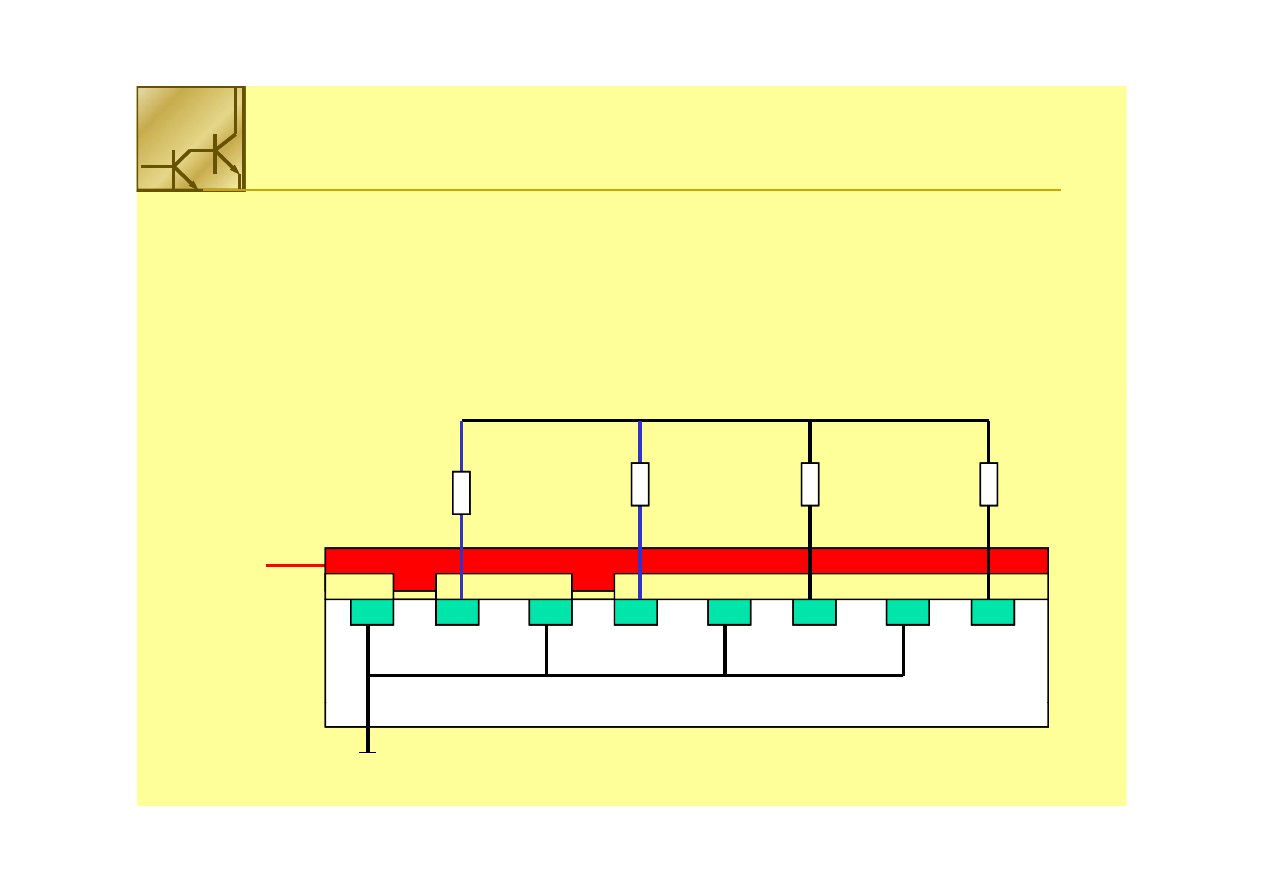

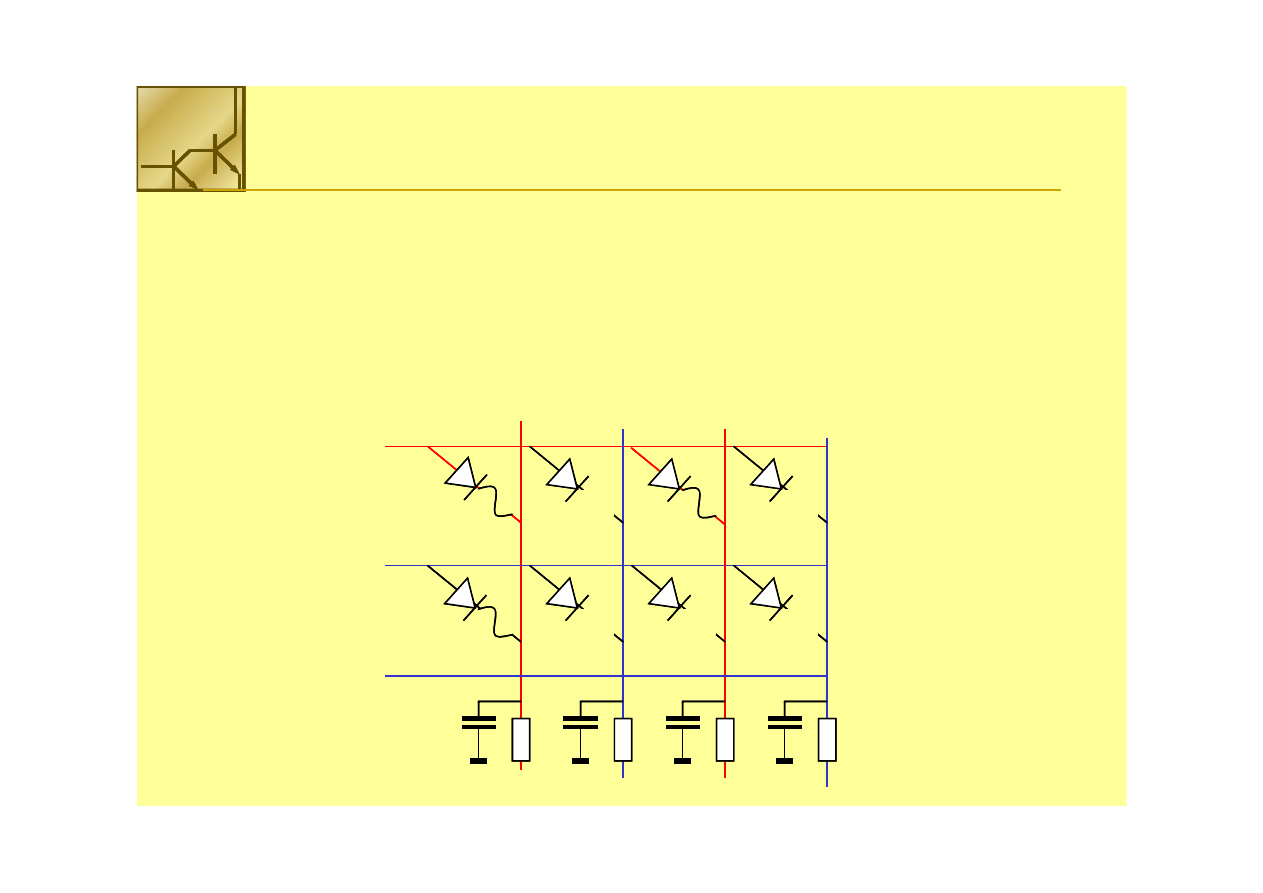

Matryca pamięci SRAM

Matryca pamięci SRAM

Matryca pamięci SRAM

Matryca pamięci SRAM

Line n

Line n

Line n+1

Line n+1

Line n+2

Line n+2

Line n+3

Line n+3

BL

BL’

BL

BL’

BL

BL’

BL

BL’

6 marca 2011

Wojciech Kucewicz

20

Kolumn

Kolumn kk

Kolumn

Kolumn kk+1

+1 Kolumn

Kolumn kk+2

+2

Kolumn

Kolumn kk++33

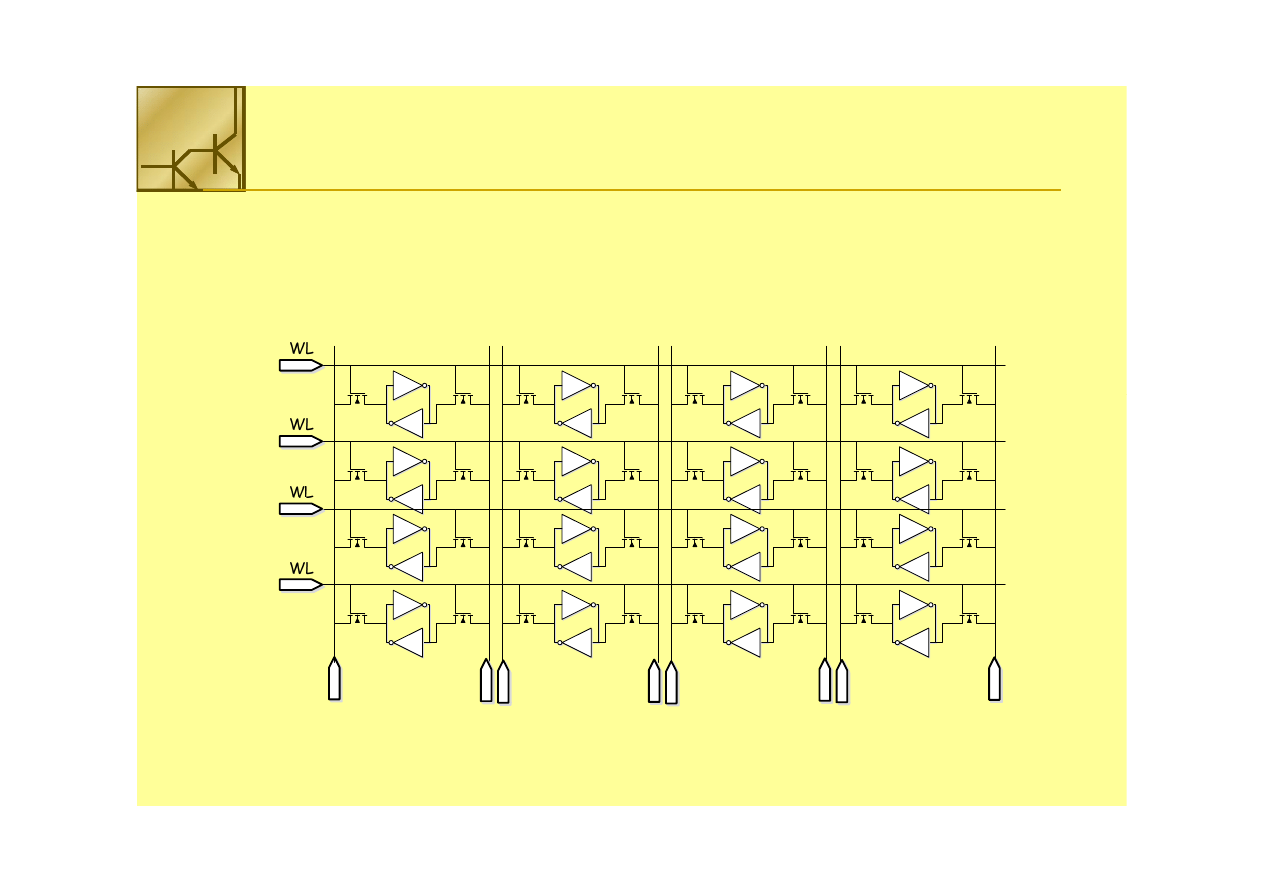

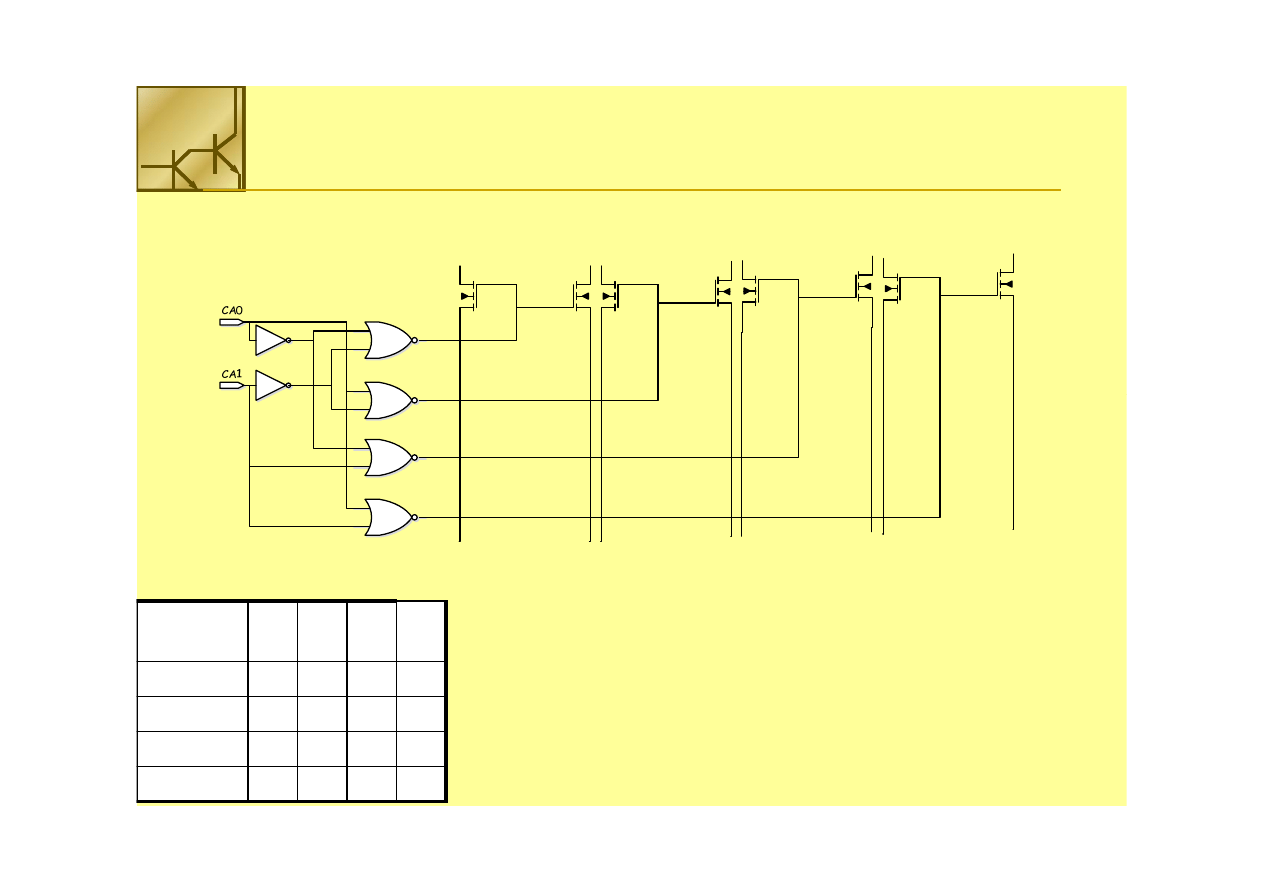

Adresowanie linii słowa

Adresowanie linii słowa

Adresowanie linii słowa

Adresowanie linii słowa

Adresowanie linii słowa realizuje się przy pomocy dekodera słowa.

LA

LA L0

L0 L1

L1 L2

L2 L3

L3

00

00

11

00

00

00

01

01

00

11

00

00

6 marca 2011

Wojciech Kucewicz

21

01

01

00

11

00

00

10

10

00

00

11

00

11

11

00

00

00

11

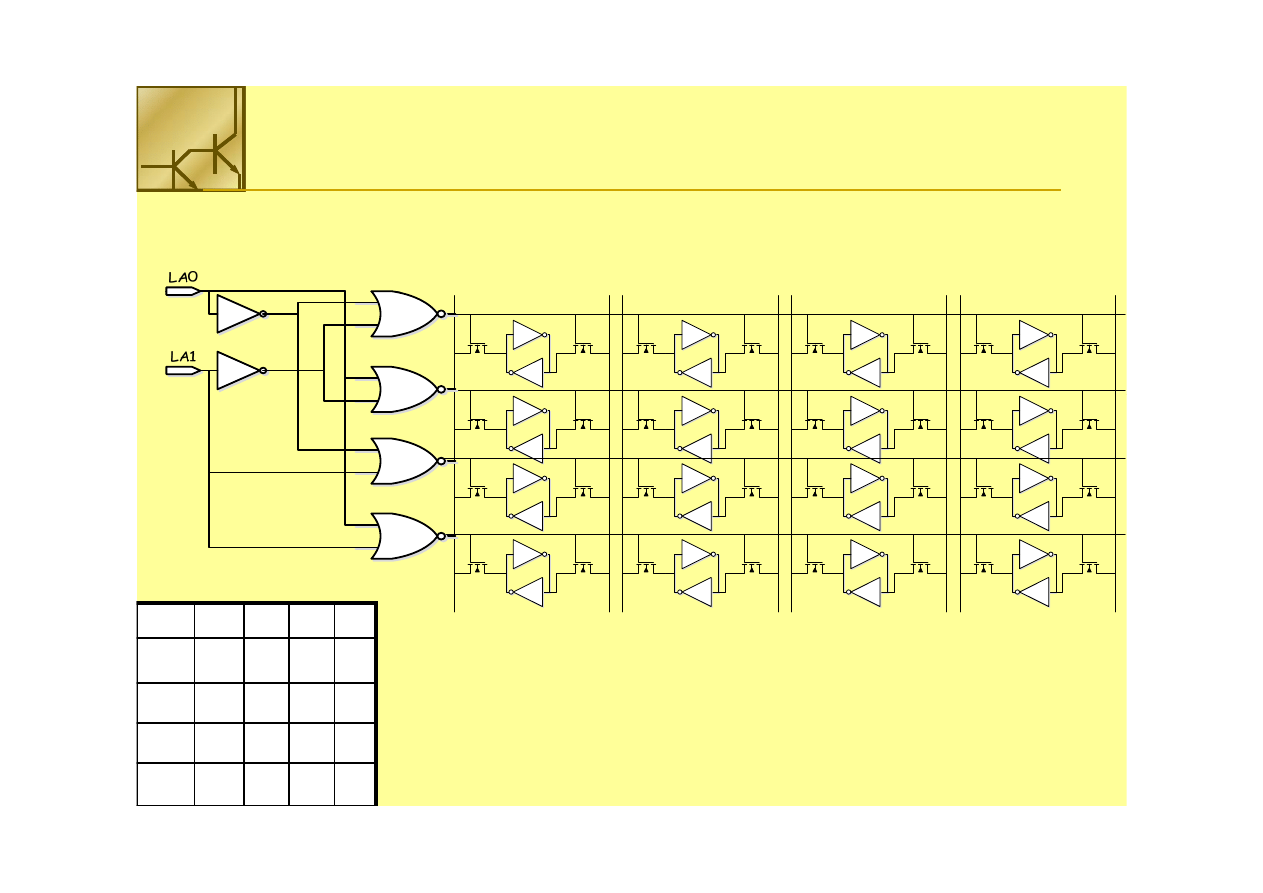

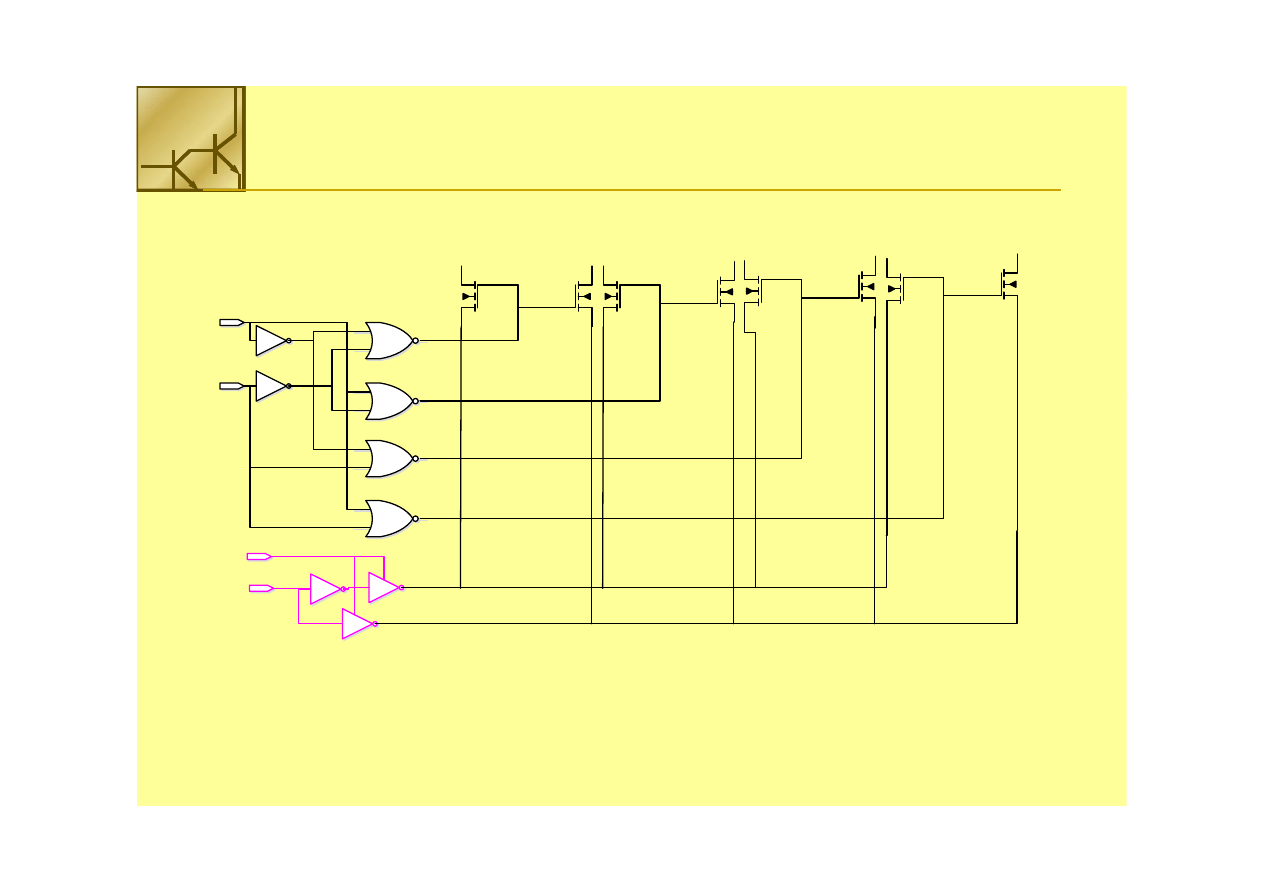

Adresowanie linii bitu

Adresowanie linii bitu

Adresowanie linii bitu

Adresowanie linii bitu

Col

Col 0

0 Col

Col 1

1 Col

Col 2

2 Col

Col 33

ColAdrr

ColAdrr Col

Col

00

Col

Col

11

Col

Col

22

Col

Col

33

0 0

0 0

11

00

00

00

6 marca 2011

Wojciech Kucewicz

22

0 1

0 1

00

11

00

00

1 0

1 0

00

00

11

00

1 1

1 1

00

00

00

11

Adresowanie linii bitu

Adresowanie linii bitu

Adresowanie linii bitu

Adresowanie linii bitu

CA0

CA1

Col

Col 0

0 Col

Col 1

1 Col

Col 2

2 Col

Col 33

Data

Write

6 marca 2011

Wojciech Kucewicz

23

Matryca pamięci SRAM

Matryca pamięci SRAM

Matryca pamięci SRAM

Matryca pamięci SRAM

6 marca 2011

Wojciech Kucewicz

24

D

DRAM

RAM

D

DRAM

RAM

D

DRAM

RAM

D

DRAM

RAM

6 marca 2011

Wojciech Kucewicz

25

Pamięć DRAM

Pamięć DRAM

Pamięć DRAM

Pamięć DRAM

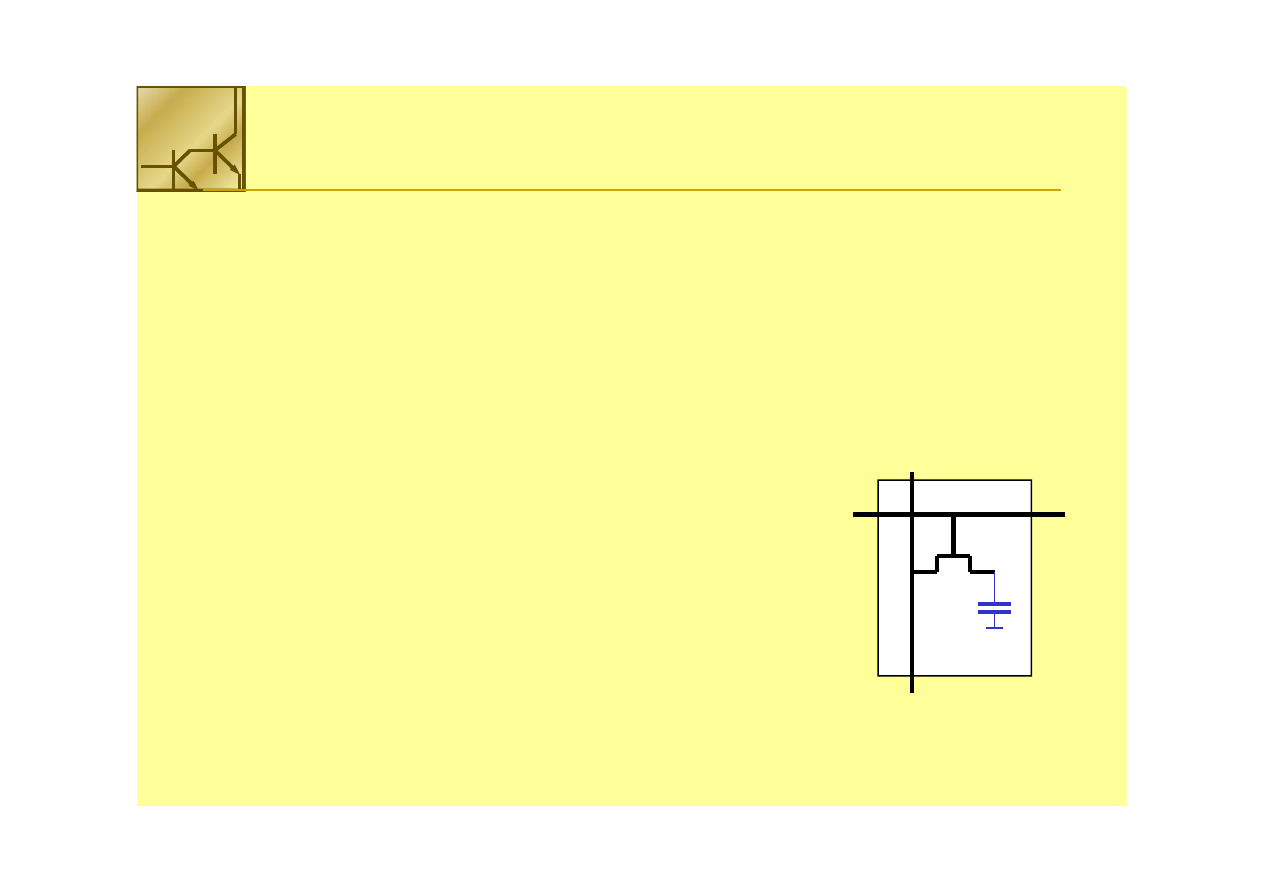

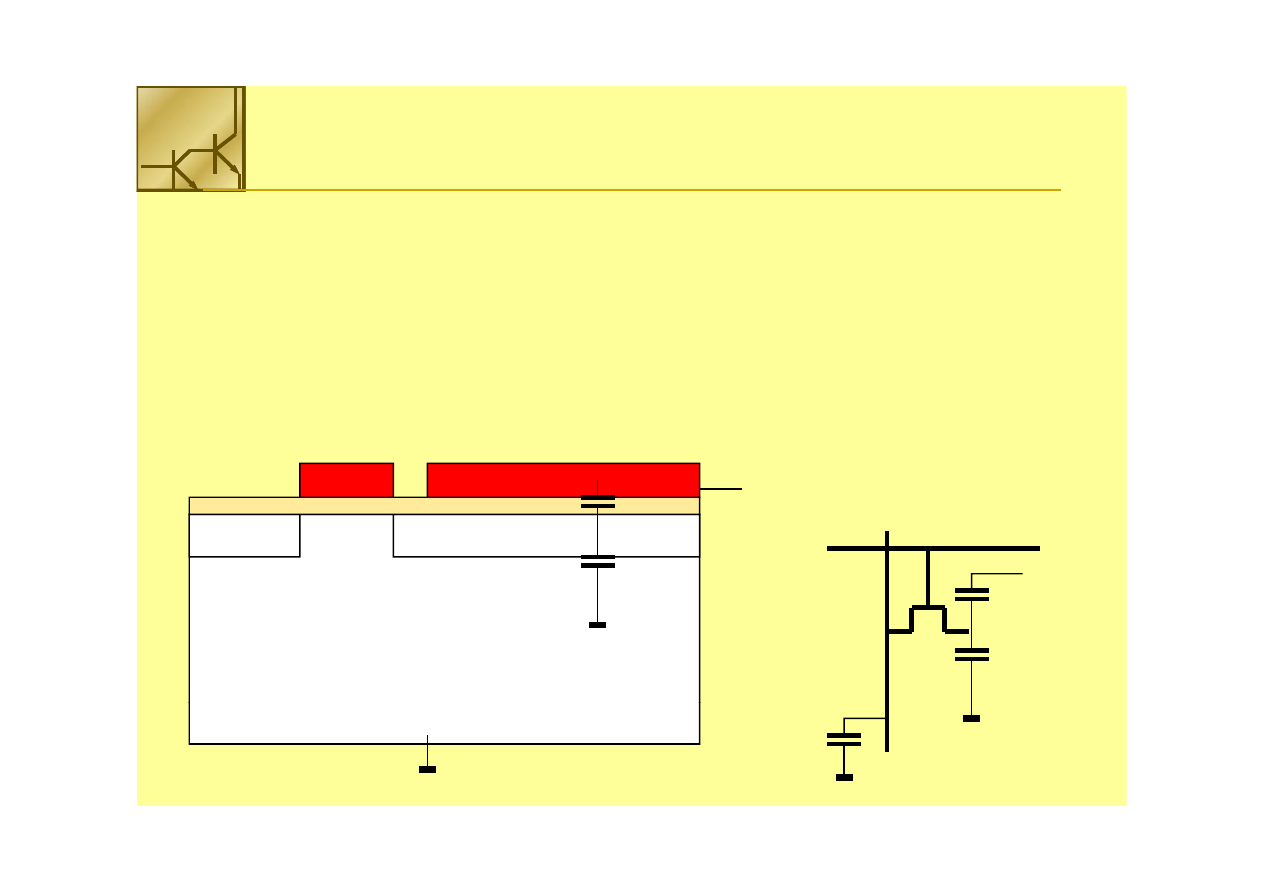

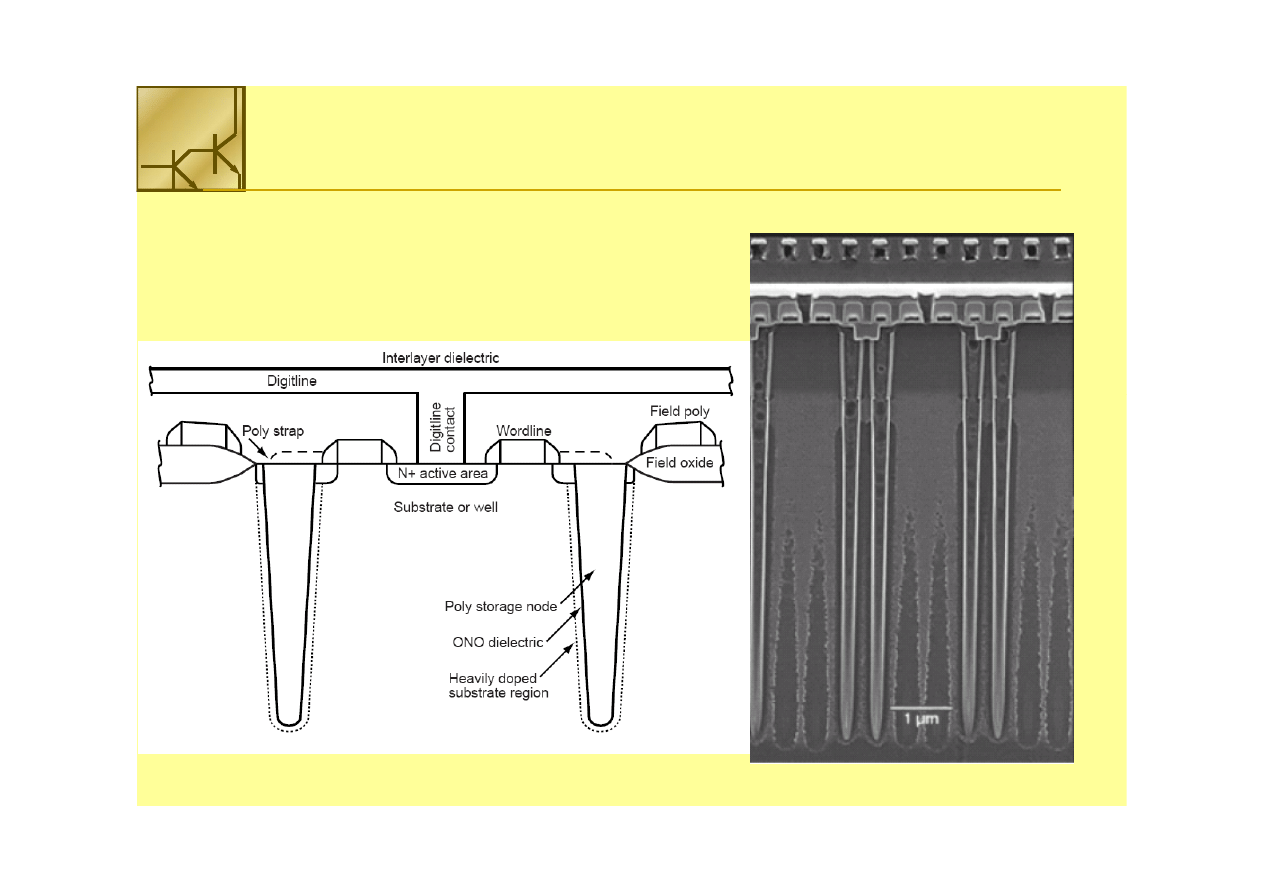

Komórka pamięci DRAM zbudowana jest z jednego tranzystora i

Komórka pamięci DRAM zbudowana jest z jednego tranzystora i

pojemności

pojemności

pojemności.

pojemności.

Dlatego pamięć DRAM charakteryzuje się:

Dlatego pamięć DRAM charakteryzuje się:

••

najmniejszą

najmniejszą powierzchnią komórki

powierzchnią komórki

n jmni jsz

n jmni jsz str t m c

str t m c

Linia słowa

Linia słowa

••

najmniejszą

najmniejszą stratą mocy

stratą mocy

••

najmniejszym

najmniejszym kosztem

kosztem

Lini

a

Lini

a

Linia słowa

Linia słowa

CC

a bitua bitu

CC

cell

cell

K mó k p mi i DRAM

K mó k p mi i DRAM

6 marca 2011

Wojciech Kucewicz

26

Komórka pamięci DRAM

Komórka pamięci DRAM

Pamięć DRAM

Pamięć DRAM

Pamięć DRAM

Pamięć DRAM

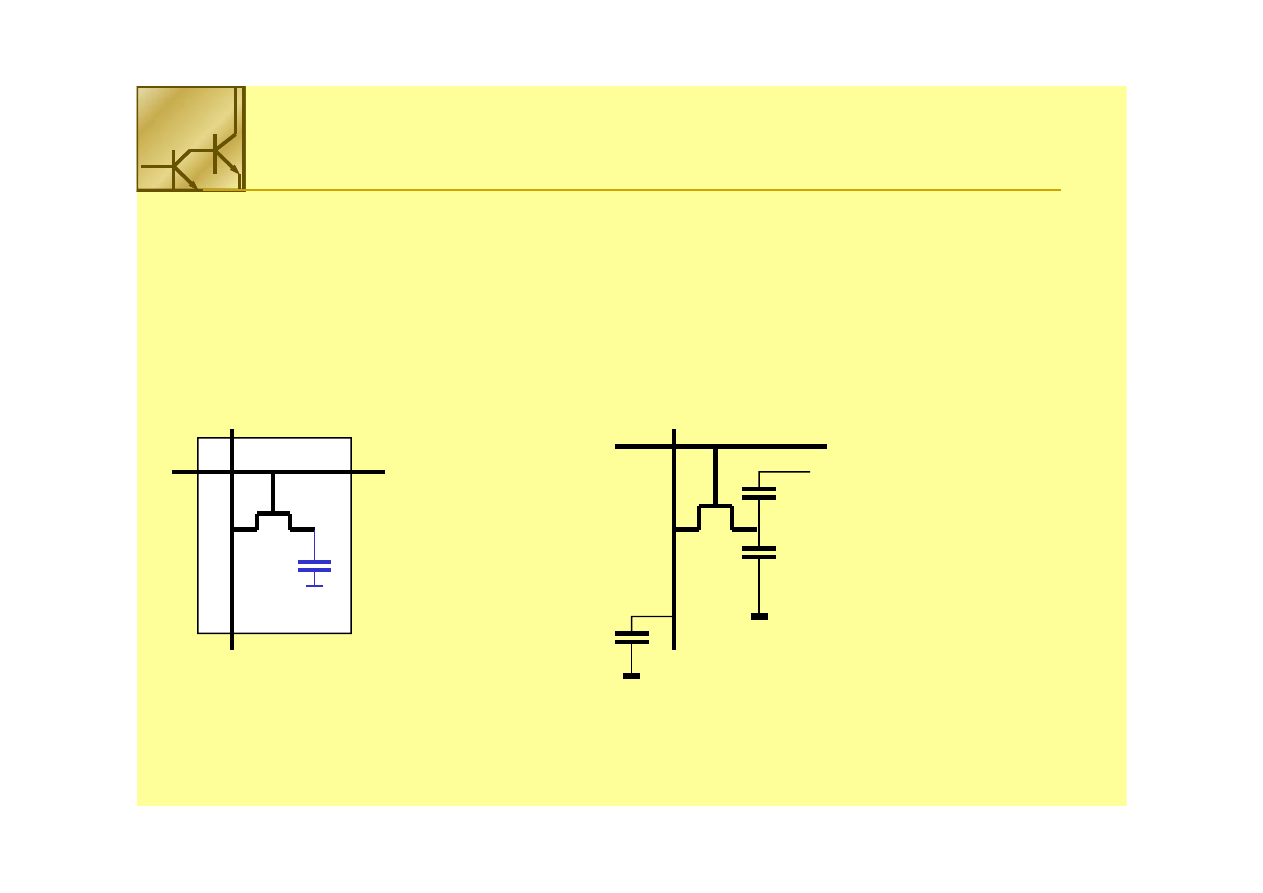

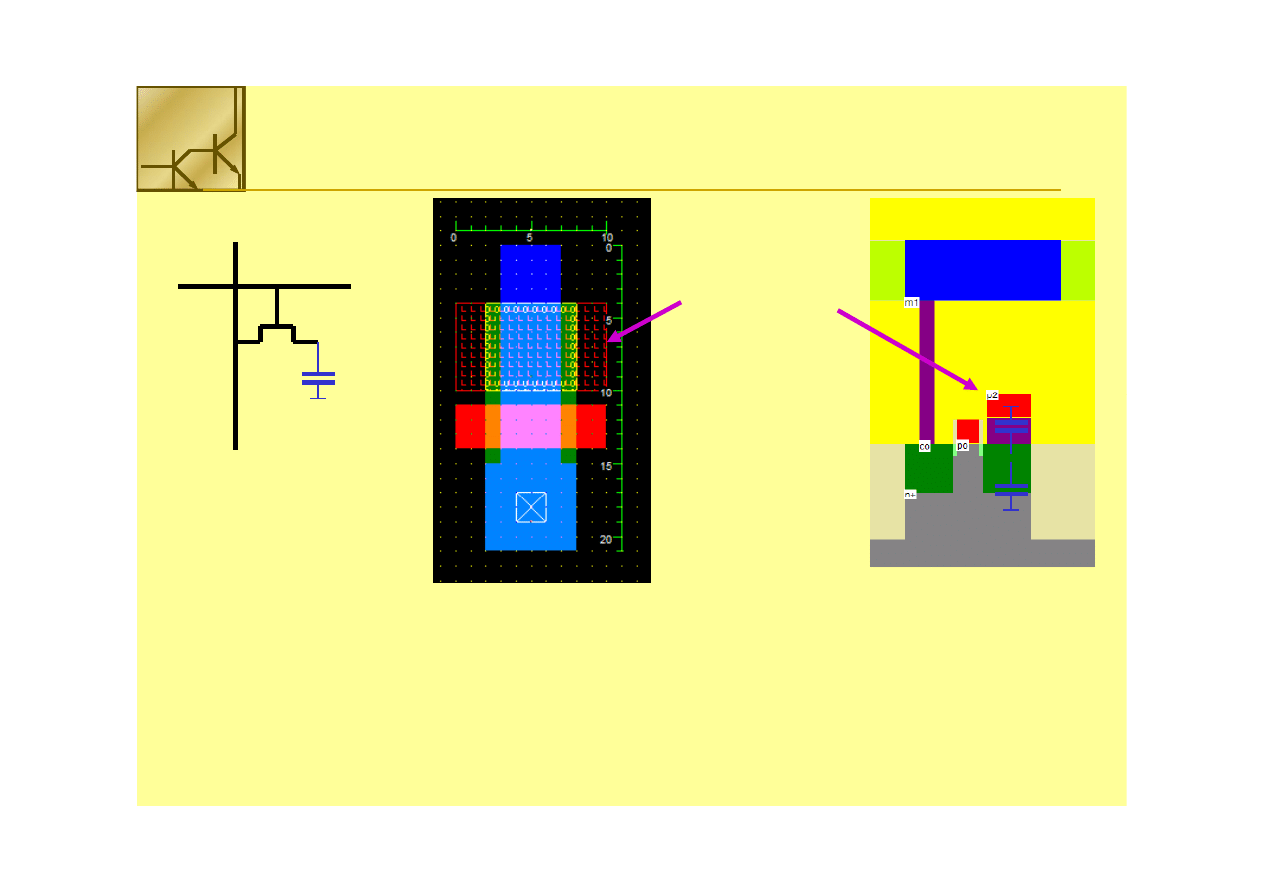

Pojemność jest rzędu 30

Pojemność jest rzędu 30 --50 fF i składają się na nią pojemności

50 fF i składają się na nią pojemności

pasożytnicze złącza źródła oraz pojemność dedykowana

pasożytnicze złącza źródła oraz pojemność dedykowana

pasożytnicze złącza źródła oraz pojemność dedykowana.

pasożytnicze złącza źródła oraz pojemność dedykowana.

Tranzystor MOS stanowi przełącznik łączący lub odłączający

Tranzystor MOS stanowi przełącznik łączący lub odłączający

kondensator C

kondensator C

od linii bitu zależnie od stanu linii słowa

od linii bitu zależnie od stanu linii słowa

kondensator C

kondensator C

cell

cell

od linii bitu zależnie od stanu linii słowa.

od linii bitu zależnie od stanu linii słowa.

Linia słowa

Linia słowa

Pamiętanie bitu informacji wynika z dwóch stanów ładunku

Pamiętanie bitu informacji wynika z dwóch stanów ładunku

zmagazynowanego w kondensatorze: stanu naładowania i

zmagazynowanego w kondensatorze: stanu naładowania i

Lini

a

Lini

a

Linia słowa

Linia słowa

CC

D S

D S

g y

g

g y

g

stanu neutralnego. Stany te reprezentują odpowiednio 1 i

stanu neutralnego. Stany te reprezentują odpowiednio 1 i

0.

0.

Naładowany kondensator ulega stopniowemu rozładowaniu

Naładowany kondensator ulega stopniowemu rozładowaniu

a bitua bitu

CC

cell

cell

K mó k p mi i DRAM

K mó k p mi i DRAM

Naładowany kondensator ulega stopniowemu rozładowaniu

Naładowany kondensator ulega stopniowemu rozładowaniu

wskutek nieuniknionych upływności. Aby nie dopuścić do

wskutek nieuniknionych upływności. Aby nie dopuścić do

rozładowania kondensatora i tym samym przejścia stanu 1

rozładowania kondensatora i tym samym przejścia stanu 1

w stan 0 ładunek musi być co jakiś czas (kilkanaście

w stan 0 ładunek musi być co jakiś czas (kilkanaście

śś

6 marca 2011

Wojciech Kucewicz

27

Komórka pamięci DRAM

Komórka pamięci DRAM

milisekund) regenerowany w procesie odświeżania.

milisekund) regenerowany w procesie odświeżania.

Pamięć DRAM

Pamięć DRAM

Pamięć DRAM

Pamięć DRAM

Pojemność jest rzędu 30

Pojemność jest rzędu 30 -- 50 fF i składają się na nią pojemności

50 fF i składają się na nią pojemności

pasożytnicze złącza źródła oraz pojemność dedykowana

pasożytnicze złącza źródła oraz pojemność dedykowana

pasożytnicze złącza źródła oraz pojemność dedykowana.

pasożytnicze złącza źródła oraz pojemność dedykowana.

Tranzystor MOS stanowi przełącznik łączący lub odłączający

Tranzystor MOS stanowi przełącznik łączący lub odłączający

kondensator C

kondensator C

od linii bitu zależnie od stanu linii słowa

od linii bitu zależnie od stanu linii słowa

Linia słowa

Linia słowa

Linia słowa

Linia słowa

CC

oo

kondensator C

kondensator C

cell

cell

od linii bitu zależnie od stanu linii słowa.

od linii bitu zależnie od stanu linii słowa.

U

U

DD

DD

Linia bit

u

Linia bit

u

CC

cell

cell

D S

D S

Linia bit

u

Linia bit

u

D S

D S

CC

jj

oo

CC

cell

cell

= C

= C

oo

+C

+C

jj

uu

uu

CC

LL

6 marca 2011

Wojciech Kucewicz

28

Pamięć DRAM

Pamięć DRAM

Pamięć DRAM

Pamięć DRAM

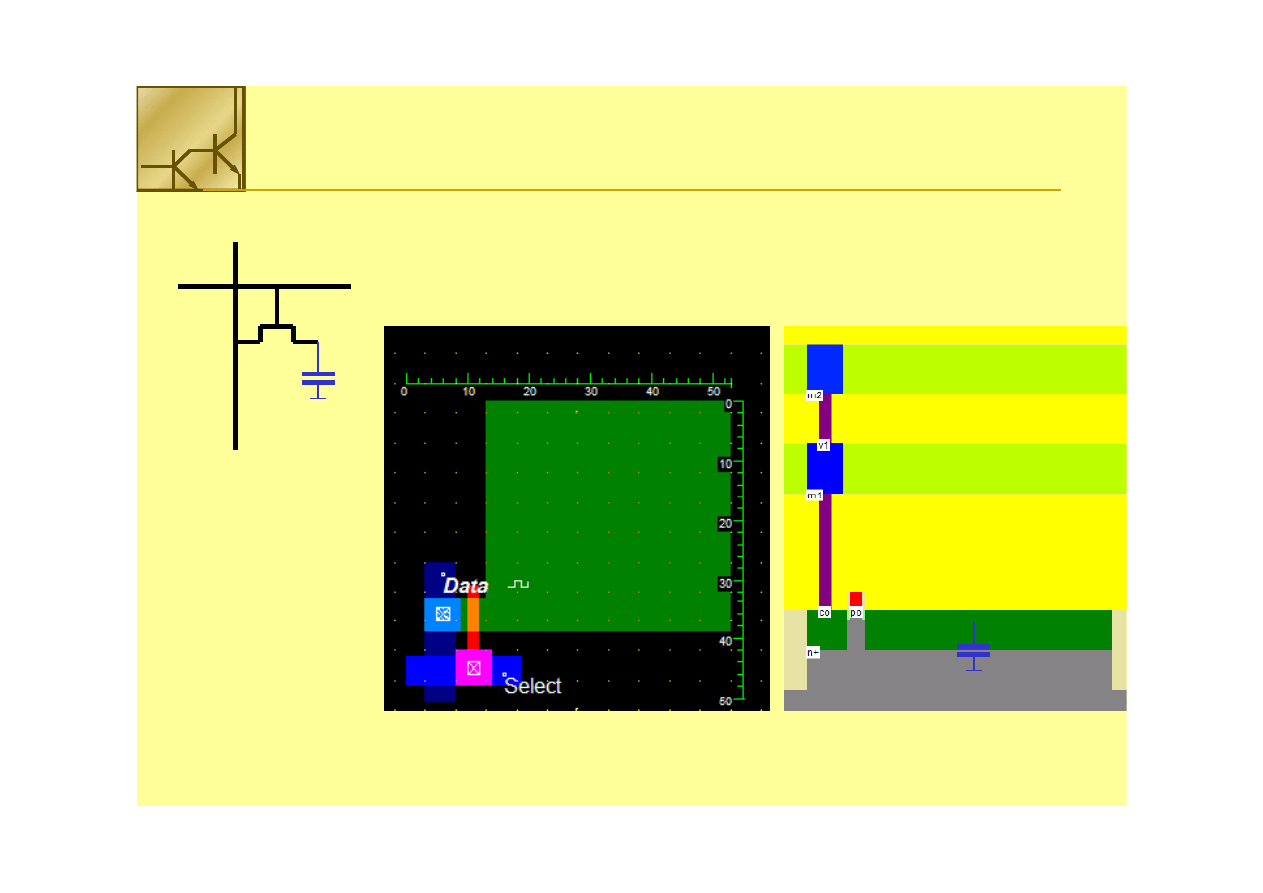

Data

Data

Select

Select

Typowa wartość pojemności C

cell

wynosi ok. 30fF.

CC

cell

cell

Komórka DRAM

Komórka DRAM

Komórka DRAM

Komórka DRAM

6 marca 2011

Wojciech Kucewicz

29

Gdyby była to pojemność złączowa źródła, to rozmiar

Gdyby była to pojemność złączowa źródła, to rozmiar

tranzystora znacznie się zwiększa

tranzystora znacznie się zwiększa..

Pamięć DRAM

Pamięć DRAM

Pamięć DRAM

Pamięć DRAM

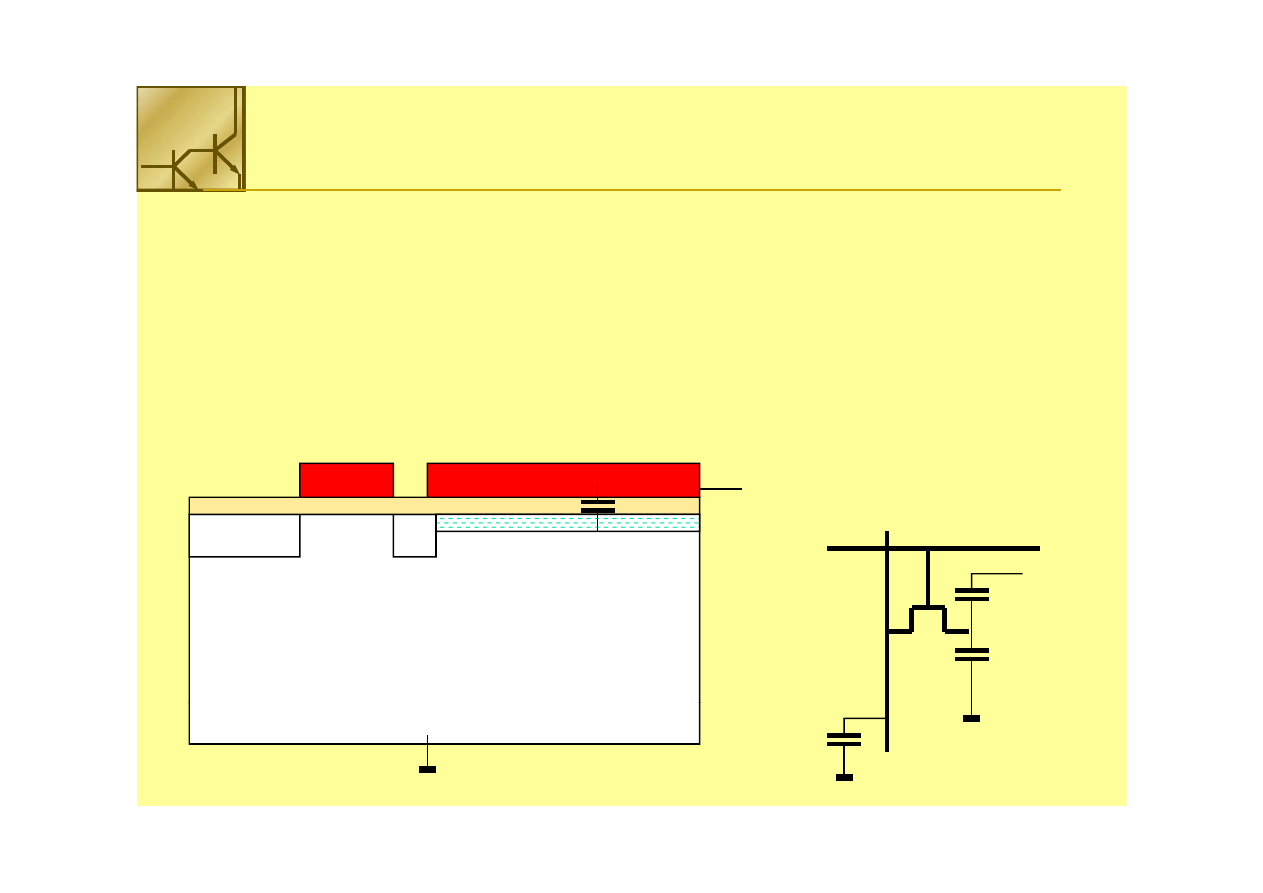

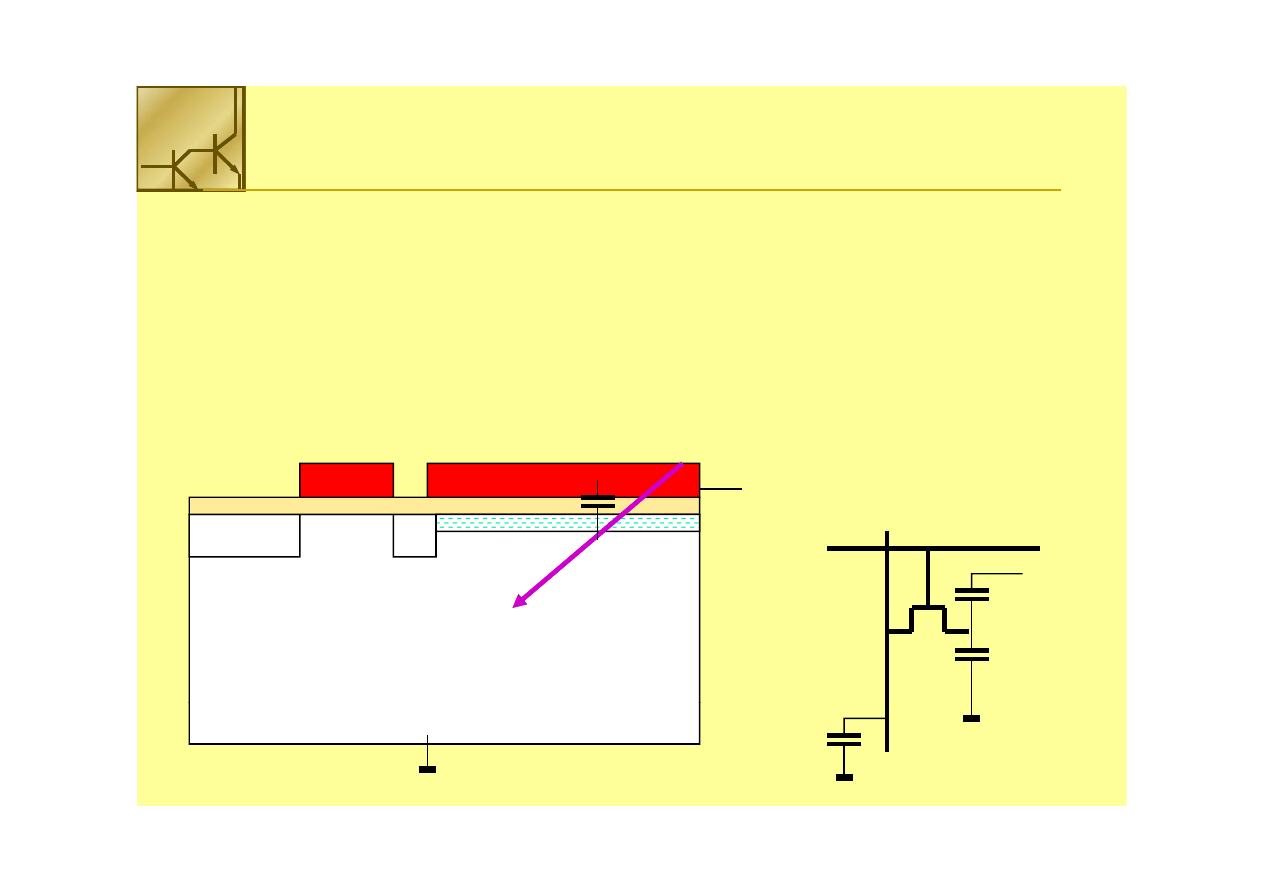

Odkrywcą koncepcji komórek dynamicznych był R. Dennard w roku

Odkrywcą koncepcji komórek dynamicznych był R. Dennard w roku

1968

1968

1968.

1968.

W komórce zastosowano metalowe elektrody bramki i górnej okładki

W komórce zastosowano metalowe elektrody bramki i górnej okładki

kondensatora C

kondensatora C Drugą okładkę stanowi część domieszkowana

Drugą okładkę stanowi część domieszkowana

kondensatora C

kondensatora C

oo

. Drugą okładkę stanowi część domieszkowana

. Drugą okładkę stanowi część domieszkowana

obszaru n

obszaru n

++

źródła tranzystora.

źródła tranzystora.

U

U

DD

DD

Linia słowa

Linia słowa

CC

oo

U

U

DD

DD

nn

++

nn

++

Linia bit

u

Linia bit

u

D S

D S

CC

jj

oo

6 marca 2011

Wojciech Kucewicz

30

uu

CC

LL

Pamięć DRAM

Pamięć DRAM

Pamięć DRAM

Pamięć DRAM

Data

Data

WL

WL

22

nd

nd

Polysilicon

Polysilicon

Komórka DRAM

Komórka DRAM

Komórka DRAM

Komórka DRAM

ść

ść

Druga

Druga wartwa

wartwa polikrzemowa

polikrzemowa tworzy dużą pojemność do

tworzy dużą pojemność do

źródła, dlatego znacząco obniża się rozmiar komórki.

źródła, dlatego znacząco obniża się rozmiar komórki.

6 marca 2011

Wojciech Kucewicz

31

Pamięć DRAM

Pamięć DRAM

Pamięć DRAM

Pamięć DRAM

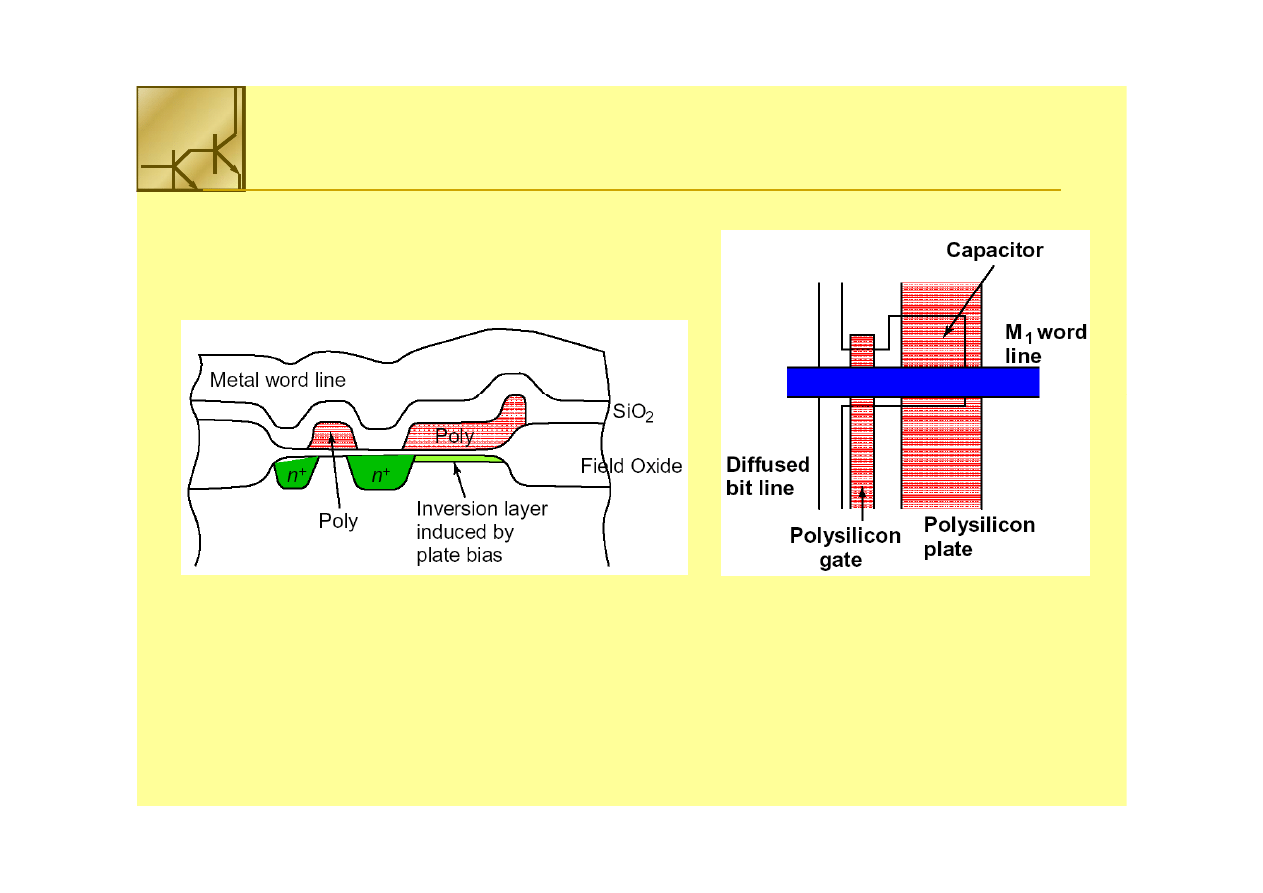

Innym rozwiązanie jest struktura Kosonocky’ego, gdzie dolną okładkę

Innym rozwiązanie jest struktura Kosonocky’ego, gdzie dolną okładkę

stanowi warstwa inwersyjna Jest ona tworzona przez przyłączenie

stanowi warstwa inwersyjna Jest ona tworzona przez przyłączenie

stanowi warstwa inwersyjna. Jest ona tworzona przez przyłączenie

stanowi warstwa inwersyjna. Jest ona tworzona przez przyłączenie

do górnej okładki wysokiego napięcia U

do górnej okładki wysokiego napięcia U

DD

DD

tj. powyżej napięcia

tj. powyżej napięcia

progowego. Stan nietrwały 1 odpowiada zmniejszeniu napięcia na

progowego. Stan nietrwały 1 odpowiada zmniejszeniu napięcia na

kondensatorze (czyli zmniejszeniu ładunku)

kondensatorze (czyli zmniejszeniu ładunku)

kondensatorze (czyli zmniejszeniu ładunku)

kondensatorze (czyli zmniejszeniu ładunku)

U

U

DD

DD

Linia słowa

Linia słowa

CC

oo

U

U

DD

DD

nn

++

nn

++

Linia bit

u

Linia bit

u

D S

D S

CC

jj

oo

6 marca 2011

Wojciech Kucewicz

32

uu

CC

LL

Pamięć DRAM

Pamięć DRAM

Pamięć DRAM

Pamięć DRAM

P

k ój k ó ki DRAM

P

k ój k ó ki DRAM

T p l i

T p l i

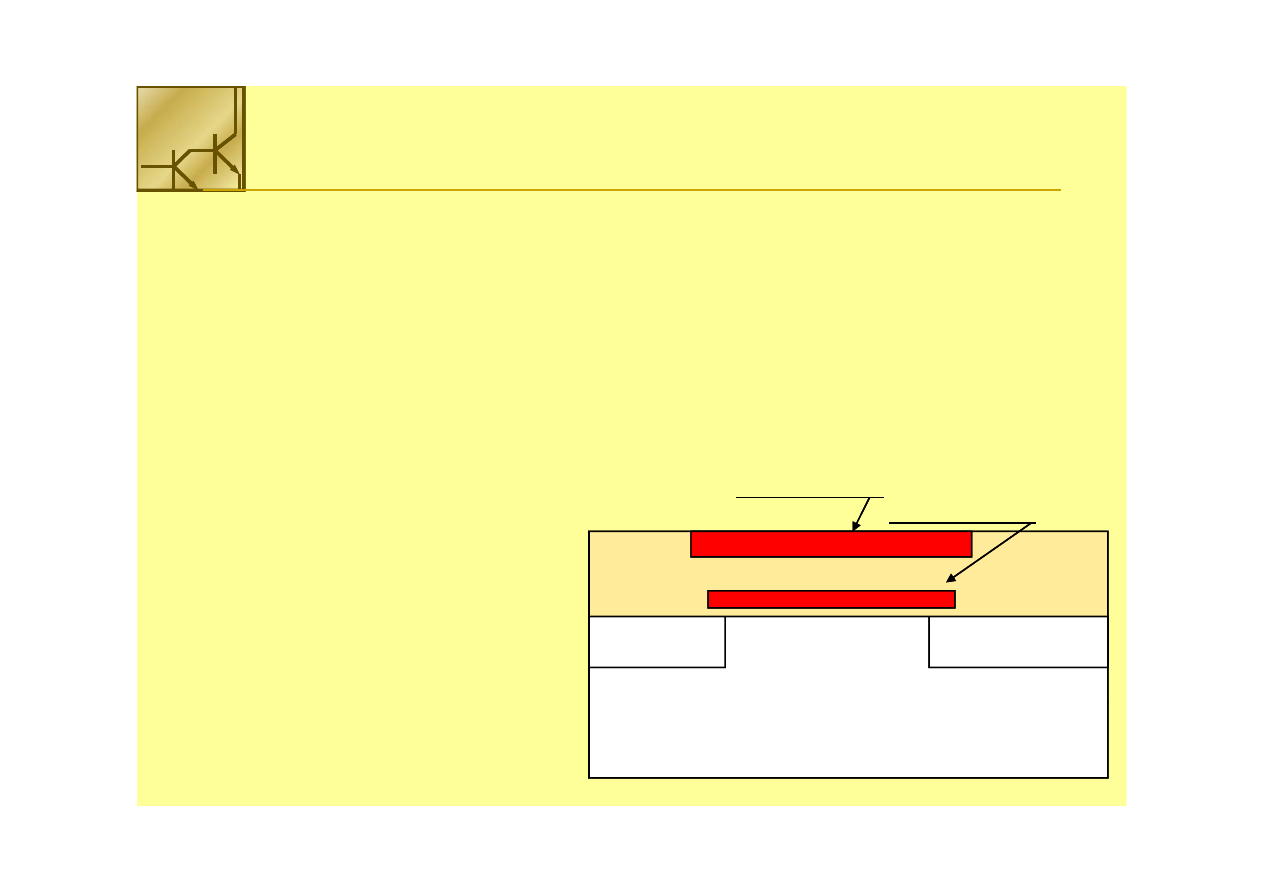

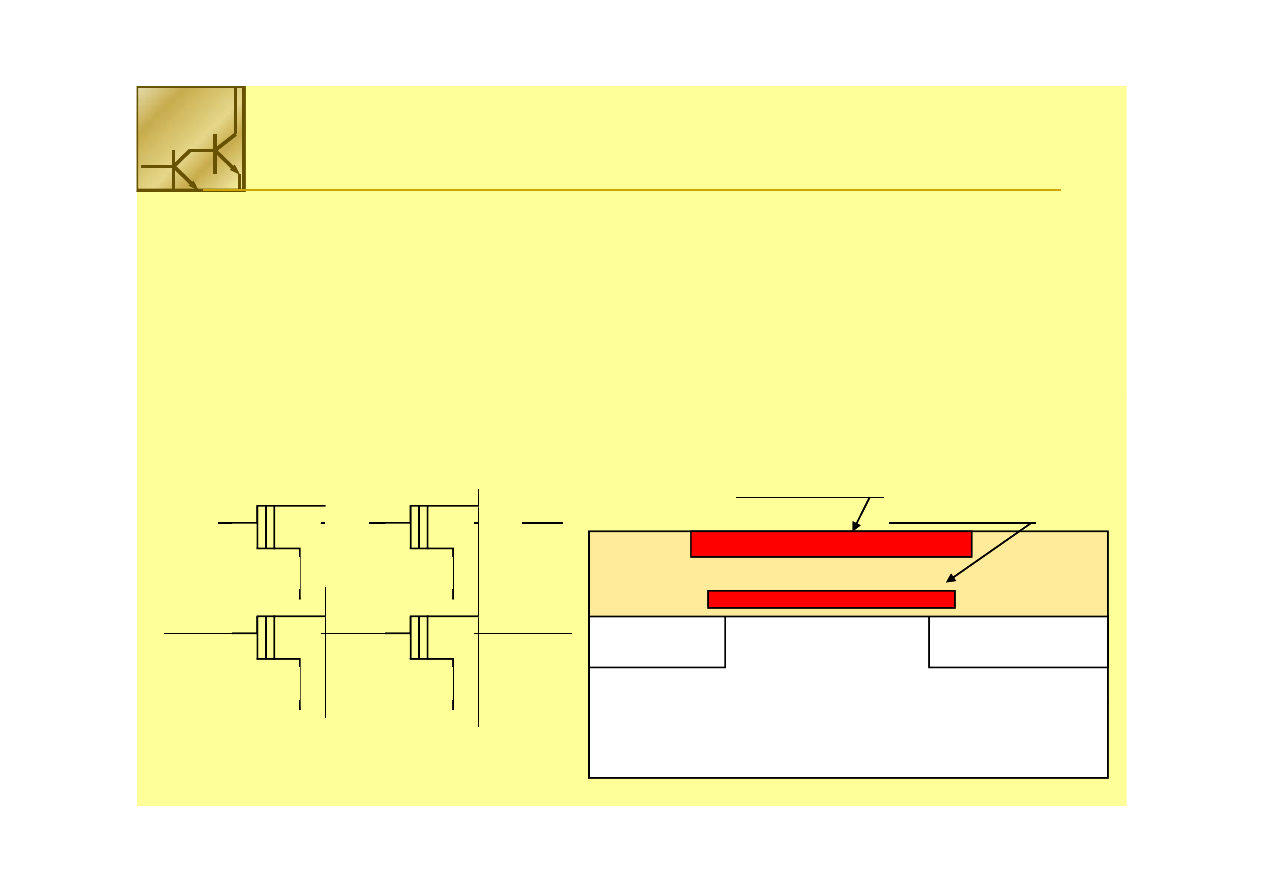

Przekrój komórki DRAM

Przekrój komórki DRAM

Topologia

Topologia

6 marca 2011

Wojciech Kucewicz

33

Pamięć DRAM

Pamięć DRAM

Pamięć DRAM

Pamięć DRAM

6 marca 2011

Wojciech Kucewicz

34

Pamięć DRAM

Pamięć DRAM

Pamięć DRAM

Pamięć DRAM

Charakterystycznym zjawiskiem dla pamięci DRAM jest występowanie

Charakterystycznym zjawiskiem dla pamięci DRAM jest występowanie

błędów powodowanych przez rozpad cząsteczek

błędów powodowanych przez rozpad cząsteczek αα. Cząsteczki

. Cząsteczki αα są

są

emitowane w wyniku rozpadów radioaktywnych

emitowane w wyniku rozpadów radioaktywnych

(np. uranu i toru, których śladowe

(np. uranu i toru, których śladowe

y

p

y y

y

p

y y

( p

,

y

( p

,

y

ilości znajdują się w typowych materiałach stosowanych na obudowy).

ilości znajdują się w typowych materiałach stosowanych na obudowy).

Błąd pamięci może pojawić się, gdy tor cząstki przecina strukturę

Błąd pamięci może pojawić się, gdy tor cząstki przecina strukturę

kondensatora. Przy przelocie cząstki tworzą się pary

kondensatora. Przy przelocie cząstki tworzą się pary el

el--dz

dz., które mogą być

., które mogą być

zbierane w obszarze zubożenia, co zwiększa napięcie kondensatora.

zbierane w obszarze zubożenia, co zwiększa napięcie kondensatora.

U

U

DD

DD

Linia słowa

Linia słowa

CC

oo

U

U

DD

DD

nn

++

nn

++

Linia bit

u

Linia bit

u

D S

D S

CC

jj

oo

6 marca 2011

Wojciech Kucewicz

35

uu

CC

LL

Pamięć DRAM

Pamięć DRAM

Pamięć DRAM

Pamięć DRAM

Bit Lines

Bit Lines

Word

Word

lines

lines

6 marca 2011

Wojciech Kucewicz

36

Pamięć DRAM

Pamięć DRAM

Pamięć DRAM

Pamięć DRAM

WL

Φ

Φ

22

U

U

S

S

P j

ść k ó ki

i i C

30 fF

C

cell

C

B

U

U

S

S

Pojemność komórki pamięci – C

cell

= 30 fF

Pojemność linii bitu - C

B

= 10 pF

Jakie napięcie na linii bitu wygeneruje ładunek

U

U

BB

Jakie napięcie na linii bitu wygeneruje ładunek

zgromadzony na pojemności C

cell

?

s

cell

cell

U

C

Q

⋅

=

Φ

Φ

11

s

s

B

cell

B

cell

B

s

cell

cell

U

U

C

C

C

Q

U

Q

⋅

⋅

=

⋅

=

=

−

3

10

3

Zmiana napięcia na linii bitu jest rzędu

Zmiana napięcia na linii bitu jest rzędu mV

mV

Zmiana napięcia na linii bitu jest rzędu

Zmiana napięcia na linii bitu jest rzędu mV

mV

6 marca 2011

Wojciech Kucewicz

37

Zmiana napięcia na linii bitu jest rzędu

Zmiana napięcia na linii bitu jest rzędu mV

mV

Zmiana napięcia na linii bitu jest rzędu

Zmiana napięcia na linii bitu jest rzędu mV

mV

Pamięć DRAM (odświeżanie)

Pamięć DRAM (odświeżanie)

Pamięć DRAM (odświeżanie)

Pamięć DRAM (odświeżanie)

WL

Φ

Φ

11

Φ

Φ

22

1 2 3

1 2 3

C

cell

C

B

Φ

Φ

22

U

U

BB

U

U

S

S

11

22

Φ

Φ

33

U

U

BB

U

U

S

S

Φ

Φ

11

Φ

Φ

33

Φ

Φ

33

1. Impuls

Φ

Φ

11

podłącza do linii bitu inwerter 1, który ustala na linii napięcie U

DD

/2

(napięcie przełączania).

2. Impuls

Φ

Φ

22

podłącza do linii bitu pojemność komórki DRAM, zgromadzony ładunek

podwyższa (obniża) nieco napięcie na linii bitu

6 marca 2011

Wojciech Kucewicz

38

podwyższa (obniża) nieco napięcie na linii bitu.

3. Impuls

Φ

Φ

33

podłącza oba inwertery (przerzutnik Schmitta) do linii bitu , które

wymuszają na linii napięcie U

DD

(U

SS

).

RRO

OM

M

RRO

OM

M

RRO

OM

M

RRO

OM

M

6 marca 2011

Wojciech Kucewicz

39

ROM

ROM

ROM

ROM

ROM (

ROM (Read

Read only

only Memory

Memory) są pamięciami stałymi, które są

) są pamięciami stałymi, które są

programowane jednorazowo maską w czasie procesu

programowane jednorazowo maską w czasie procesu

programowane jednorazowo maską w czasie procesu

programowane jednorazowo maską w czasie procesu

technologicznego. Pamięci ROM są najtańszymi, nieulotnymi

technologicznego. Pamięci ROM są najtańszymi, nieulotnymi

pamięciami półprzewodnikowymi.

pamięciami półprzewodnikowymi.

Budowa komórek pamięci ROM jest bardzo prosta, ponieważ stany

Budowa komórek pamięci ROM jest bardzo prosta, ponieważ stany

logiczne tych komórek są trwałe. Po zaadresowaniu komórki (na linii

logiczne tych komórek są trwałe. Po zaadresowaniu komórki (na linii

słowa) stan komórki jest przenoszony na linię bitu Linie słowa są

słowa) stan komórki jest przenoszony na linię bitu Linie słowa są

słowa) stan komórki jest przenoszony na linię bitu. Linie słowa są

słowa) stan komórki jest przenoszony na linię bitu. Linie słowa są

sterowanie dekoderem adresu słowa, a linie bitu są wybierane przez

sterowanie dekoderem adresu słowa, a linie bitu są wybierane przez

multipleksery sterowane adresem kolumn.

multipleksery sterowane adresem kolumn.

6 marca 2011

Wojciech Kucewicz

40

ROM

ROM

ROM

ROM

ROM (

ROM (Read

Read only

only Memory

Memory) może być zbudowana z komórek zawierających

) może być zbudowana z komórek zawierających

pojedynczą diodę. Wadą komórki jest mała szybkość działania, ponieważ przy

pojedynczą diodę. Wadą komórki jest mała szybkość działania, ponieważ przy

zmianie poziomu linii słowa z L na H wyjście dekodera musi ładować

zmianie poziomu linii słowa z L na H wyjście dekodera musi ładować

zmianie poziomu linii słowa z L na H wyjście dekodera musi ładować

zmianie poziomu linii słowa z L na H wyjście dekodera musi ładować

pojemność pasożytniczą C

pojemność pasożytniczą C

LL

na wszystkich liniach bitu (z 1)

na wszystkich liniach bitu (z 1)

Linia słowa A

Linia słowa A

Linia słowa A

Linia słowa A

Linia

b

Linia

b

Linia

b

Linia

b

Lini

a

Lini

a

Lini

a

Lini

a

Lini

a

Lini

a

Lini

a

Lini

a

LiniLiniLiniLini

1 0 1 0

1 0 1 0

1 0 1 0

1 0 1 0

Linia słowa B

Linia słowa B

Linia słowa B

Linia słowa B

bitu Dbitu Dbitu Dbitu D

a bitu Ca bitu Ca bitu Ca bitu C

a bitu Ba bitu Ba bitu Ba bitu B

a bitu Aa bitu Aa bitu Aa bitu A

Linia słowa C

Linia słowa C

Linia słowa C

Linia słowa C

6 marca 2011

Wojciech Kucewicz

41

CC

LL

CC

LL

CC

LL

CC

LL

CC

LL

CC

LL

CC

LL

CC

LL

ROM

ROM

ROM

ROM

ROM (

ROM (Read

Read only

only Memory

Memory) może być zbudowana z komórek zawierających

) może być zbudowana z komórek zawierających

tranzystor MOS.

tranzystor MOS.

yy

U

U

DD

DD

U

U

DD

DD

Linia słowa A

Linia słowa A

Linia słowa A

Linia słowa A

Linia

b

Linia

b

Linia

b

Linia

b

Lini

a

Lini

a

Lini

a

Lini

a

Lini

a

Lini

a

Lini

a

Lini

a

LiniLiniLiniLini

Linia słowa B

Linia słowa B

Linia słowa B

Linia słowa B

bitu Dbitu Dbitu Dbitu D

a bitu Ca bitu Ca bitu Ca bitu C

a bitu Ba bitu Ba bitu Ba bitu B

a bitu Aa bitu Aa bitu Aa bitu A

Linia słowa C

Linia słowa C

Linia słowa C

Linia słowa C

6 marca 2011

Wojciech Kucewicz

42

CC

LL

CC

LL

CC

LL

CC

LL

CC

LL

CC

LL

CC

LL

CC

LL

ROM

ROM

ROM

ROM

ROM (

ROM (Read

Read only

only Memory

Memory) z komórkami MOS pozwalają na budowę symetrycznej

) z komórkami MOS pozwalają na budowę symetrycznej

matrycy pamięciowej. Programowanie pamięci następuje przez selektywne wytwarzanie

matrycy pamięciowej. Programowanie pamięci następuje przez selektywne wytwarzanie

tranzystorów MOS w odpowiednich komórkach, czyli wytwarzanie bramek

tranzystorów MOS w odpowiednich komórkach, czyli wytwarzanie bramek

y

p

y

y

y

p

y

y

tranzystorów na cienkiej warstwie tlenku. W tych miejscach gdzie tranzystory nie

tranzystorów na cienkiej warstwie tlenku. W tych miejscach gdzie tranzystory nie

powinny być wytworzono zostawia się pod bramką gruby tlenek.

powinny być wytworzono zostawia się pod bramką gruby tlenek.

U

U

DD

DD

Linia słowa A

Linia słowa A

Linia słowa A

Linia słowa A

Li

n

Li

n

Li

n

Li

n

LLLL

LLLL

Linia słowa B

Linia słowa B

Linia słowa B

Linia słowa B

nia bitu Dnia bitu Dnia bitu Dnia bitu D

Linia bitu CLinia bitu CLinia bitu CLinia bitu C

Linia bitu BLinia bitu BLinia bitu BLinia bitu B

Linia bitu ALinia bitu ALinia bitu ALinia bitu A

Linia słowa C

Linia słowa C

Linia słowa C

Linia słowa C

6 marca 2011

Wojciech Kucewicz

Wojciech Kucewicz

43

CC

LL

CC

LL

CC

LL

CC

LL

CC

LL

CC

LL

CC

LL

CC

LL

ROM

ROM

ROM

ROM

ROM (

ROM (Read

Read only

only Memory

Memory) z komórkami MOS pozwalają na budowę

) z komórkami MOS pozwalają na budowę symetrycznej

symetrycznej

matrycy pamięciowej. Programowanie pamięci następuje przez selektywne

matrycy pamięciowej. Programowanie pamięci następuje przez selektywne wytworzenie

wytworzenie

tranzystorów MOS w odpowiednich komórkach, czyli wytwarzanie bramek

tranzystorów MOS w odpowiednich komórkach, czyli wytwarzanie bramek

y

p

y

y

y

p

y

y

tranzystorów na cienkiej

tranzystorów na cienkiej warstwie

warstwie tlenku. W tych miejscach gdzie tranzystory nie

tlenku. W tych miejscach gdzie tranzystory nie

powinny być wytworzono zostawia się pod bramką gruby tlenek.

powinny być wytworzono zostawia się pod bramką gruby tlenek.

U

U

DD

DD

U

U

DD

DD

Dyfuzja n

Dyfuzja n

++

Dyfuzja n

Dyfuzja n

++

D G S

D G S

D G S

D G S

6 marca 2011

Wojciech Kucewicz

Wojciech Kucewicz

44

44

ROM

ROM

ROM

ROM

ROM (

ROM (Read

Read only

only Memory

Memory) z komórkami MOS pozwalają na budowę

) z komórkami MOS pozwalają na budowę

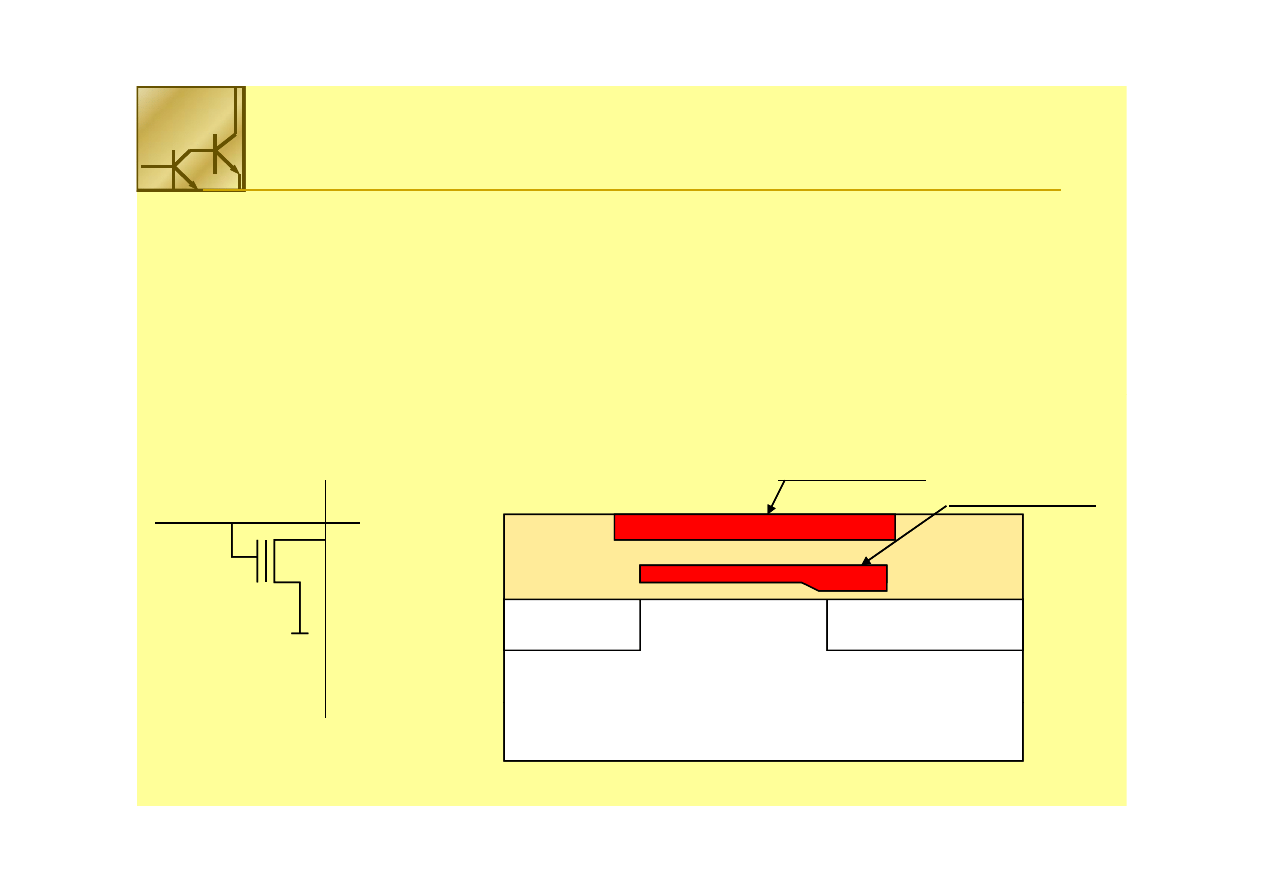

symetrycznej matrycy pamięciowej. Programowanie pamięci następuje przez

symetrycznej matrycy pamięciowej. Programowanie pamięci następuje przez

selektywne wytwarzanie tranzystorów MOS w odpowiednich komórkach czyli

selektywne wytwarzanie tranzystorów MOS w odpowiednich komórkach czyli

selektywne wytwarzanie tranzystorów MOS w odpowiednich komórkach, czyli

selektywne wytwarzanie tranzystorów MOS w odpowiednich komórkach, czyli

wytwarzanie bramek tranzystorów na cienkiej warstwie tlenku. W tych

wytwarzanie bramek tranzystorów na cienkiej warstwie tlenku. W tych

miejscach gdzie tranzystory nie powinny być wytworzono zostawia się pod

miejscach gdzie tranzystory nie powinny być wytworzono zostawia się pod

bramką gruby tlenek.

bramką gruby tlenek.

U

U

U

U

ą g

y

ą g

y

U

U

DD

DD

U

U

DD

DD

Linia słowa A

Linia słowa A

Linia słowa A

Linia słowa A

nn

++

nn

++

nn

++

nn

++

nn

++

nn

++

nn

++

nn

++

6 marca 2011

Wojciech Kucewicz

45

PROM

PROM

PROM

PROM

PROM

PROM

PROM

PROM

6 marca 2011

Wojciech Kucewicz

46

PROM

PROM

PROM

PROM

PROM (

PROM (Programmable

Programmable Read

Read only

only Memory

Memory) mogą być swobodnie

) mogą być swobodnie

programowane przez konstruktora. Są wytwarzane seryjnie jako „czyste”,

programowane przez konstruktora. Są wytwarzane seryjnie jako „czyste”,

czyli pełne zer lub jedynek Programowanie polega na wprowadzeniu zmian w

czyli pełne zer lub jedynek Programowanie polega na wprowadzeniu zmian w

czyli pełne zer lub jedynek. Programowanie polega na wprowadzeniu zmian w

czyli pełne zer lub jedynek. Programowanie polega na wprowadzeniu zmian w

wybranych komórkach pamięci, czyli na selektywnym przepalaniu połączeń

wybranych komórkach pamięci, czyli na selektywnym przepalaniu połączeń

bezpiecznikowych wykonanych w postaci przewężonych ścieżek

bezpiecznikowych wykonanych w postaci przewężonych ścieżek

polikrzemowych

polikrzemowych lub rezystorów nichromowych

lub rezystorów nichromowych

polikrzemowych

polikrzemowych lub rezystorów nichromowych.

lub rezystorów nichromowych.

Linia słowa A

Linia słowa A

Linia słowa A

Linia słowa A

Linia

b

Linia

b

Linia

b

Linia

b

Lini

a

Lini

a

Lini

a

Lini

a

Lini

a

Lini

a

Lini

a

Lini

a

LiniLiniLiniLini

Linia słowa B

Linia słowa B

Linia słowa B

Linia słowa B

bitu Dbitu Dbitu Dbitu D

a bitu Ca bitu Ca bitu Ca bitu C

a bitu Ba bitu Ba bitu Ba bitu B

a bitu Aa bitu Aa bitu Aa bitu A

Linia słowa C

Linia słowa C

Linia słowa C

Linia słowa C

6 marca 2011

Wojciech Kucewicz

47

CC

LL

CC

LL

CC

LL

CC

LL

CC

LL

CC

LL

CC

LL

CC

LL

EPROM

EPROM

EPROM

EPROM

EPROM

EPROM

EPROM

EPROM

6 marca 2011

Wojciech Kucewicz

48

EPROM

EPROM

EPROM

EPROM

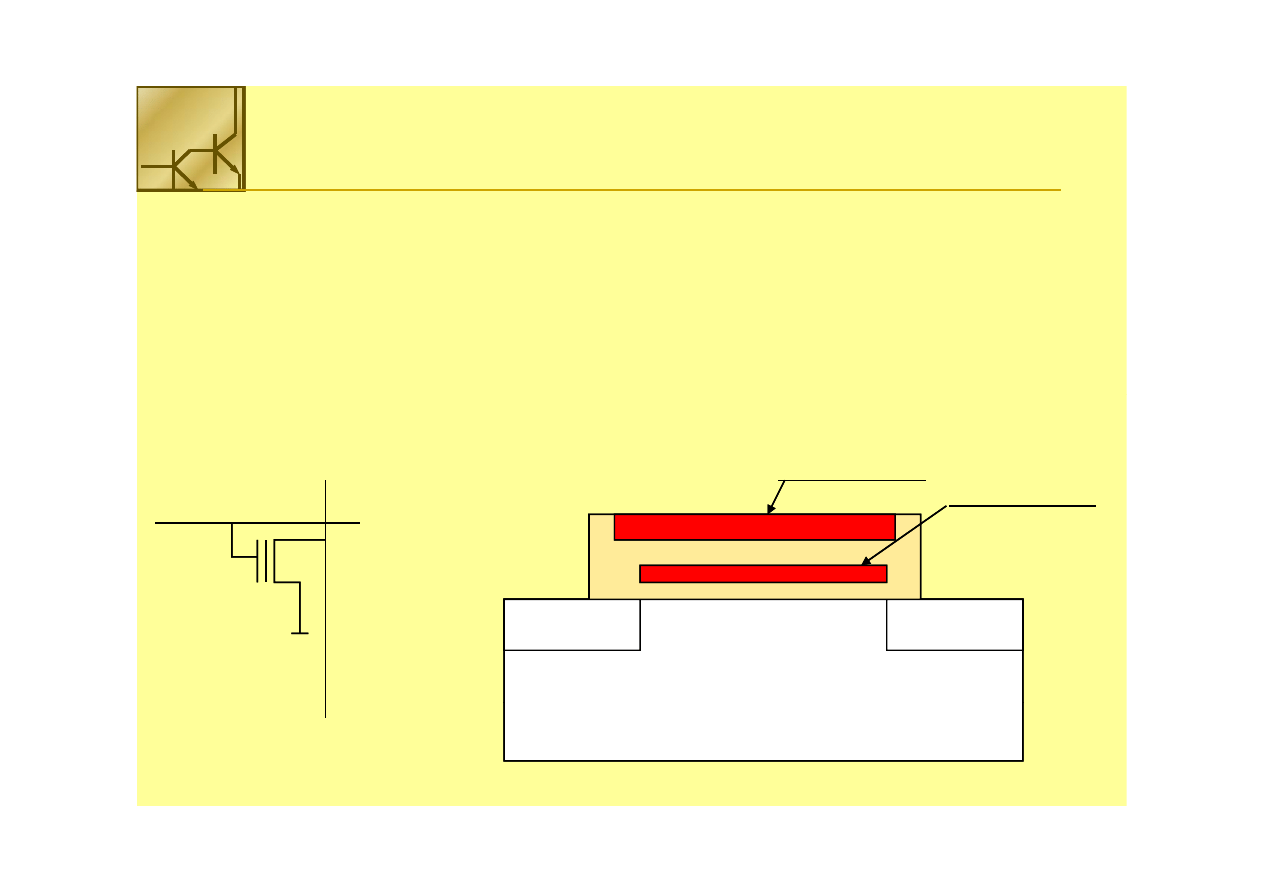

EPROM (

EPROM (Erasable

Erasable Programmable

Programmable Read

Read Only

Only Memory

Memory) umożliwiają wielokrotne

) umożliwiają wielokrotne

programowanie i kasowanie zawartości. Komórkę pamięciową układu EPROM stanowi

programowanie i kasowanie zawartości. Komórkę pamięciową układu EPROM stanowi

tranzystor w którym wykorzystuje się zjawisko trwałego magazynowania ładunku w

tranzystor w którym wykorzystuje się zjawisko trwałego magazynowania ładunku w

tranzystor, w którym wykorzystuje się zjawisko trwałego magazynowania ładunku w

tranzystor, w którym wykorzystuje się zjawisko trwałego magazynowania ładunku w

podbramkowej warstwie dielektrycznej, wprowadzonego przez wymuszenie napięciowe.

podbramkowej warstwie dielektrycznej, wprowadzonego przez wymuszenie napięciowe.

Zjawisko takie występuje w strukturach z polaryzowalnym dielektrykiem , takim jak

Zjawisko takie występuje w strukturach z polaryzowalnym dielektrykiem , takim jak

azotek krzemu (MNOS). Najbardziej znaną strukturą jest FAMOS (

azotek krzemu (MNOS). Najbardziej znaną strukturą jest FAMOS (Floating

Floating gate

gate

A l

h

A l

h i j t d

i j t d MOS)

t kt

b d j

b

ki

MOS)

t kt

b d j

b

ki

Avalanche

Avalanche--injected

injected MOS) zwaną strukturą swobodnej bramki.

MOS) zwaną strukturą swobodnej bramki.

Bramka sterująca

Bramka sterująca

Bramka sterująca

Bramka sterująca

Bramka swobodna

Bramka swobodna

Bramka swobodna

Bramka swobodna

Linia słowa A

Linia słowa A

Linia słowa A

Linia słowa A

Linia bit

u

Linia bit

u

Linia bit

u

Linia bit

u

S

S

S

S

Bramka swobodna

Bramka swobodna

Bramka swobodna

Bramka swobodna

u Au Au Au A

nn

++

nn

++

6 marca 2011

Wojciech Kucewicz

49

EPROM

EPROM

EPROM

EPROM

Programowanie następuje przy ustaleniu wystarczająco dużych napięć dodatnich na

Programowanie następuje przy ustaleniu wystarczająco dużych napięć dodatnich na

bramce sterującej i drenie. Wówczas elektrony w obszarze zubożonym są

bramce sterującej i drenie. Wówczas elektrony w obszarze zubożonym są

przyspieszane w kierunku największego natężenia pola znajdującego się w okolicy

przyspieszane w kierunku największego natężenia pola znajdującego się w okolicy

przyspieszane w kierunku największego natężenia pola znajdującego się w okolicy

przyspieszane w kierunku największego natężenia pola znajdującego się w okolicy

drenu. Przy natężeniu pola > 10

drenu. Przy natężeniu pola > 10

55

V/cm elektrony mają tak dużą energię, że są w stanie

V/cm elektrony mają tak dużą energię, że są w stanie

pokonać barierę potencjału Si/SiO

pokonać barierę potencjału Si/SiO

22

(3.2

(3.2 eV

eV) między podłożem a cienkim dielektrykiem

) między podłożem a cienkim dielektrykiem

pod swobodną bramką. Bramka swobodna łapie elektrony, które nie mogą jej już

pod swobodną bramką. Bramka swobodna łapie elektrony, które nie mogą jej już

ś ić W t

ób

b d b

k ł d j i

j

i d

i i

ś ić W t

ób

b d b

k ł d j i

j

i d

i i ΔΔU

U Q

Q /C

/C

opuścić. W ten sposób swobodna bramka ładuje się ujemnie do napięcia

opuścić. W ten sposób swobodna bramka ładuje się ujemnie do napięcia ΔΔU

U

T

T

=

= --Q

Q

FG

FG

/C

/C

gdzie C jest pojemnością między bramką swobodną i bramką sterującą.

gdzie C jest pojemnością między bramką swobodną i bramką sterującą.

Bramka sterująca

Bramka sterująca

Bramka sterująca

Bramka sterująca

Bramka swobodna

Bramka swobodna

Bramka swobodna

Bramka swobodna

25V

25V

25V

25V

Linia słowa A

Linia słowa A

Linia słowa A

Linia słowa A

Linia bit

u

Linia bit

u

Linia bit

u

Linia bit

u

S

S

S

S

Bramka swobodna

Bramka swobodna

Bramka swobodna

Bramka swobodna

S

S

S

S

D

D

D

D

25V

25V

25V

25V

u Au Au Au A

nn

++

nn

++

---- ----

---- ----

6 marca 2011

Wojciech Kucewicz

50

EPROM

EPROM

EPROM

EPROM

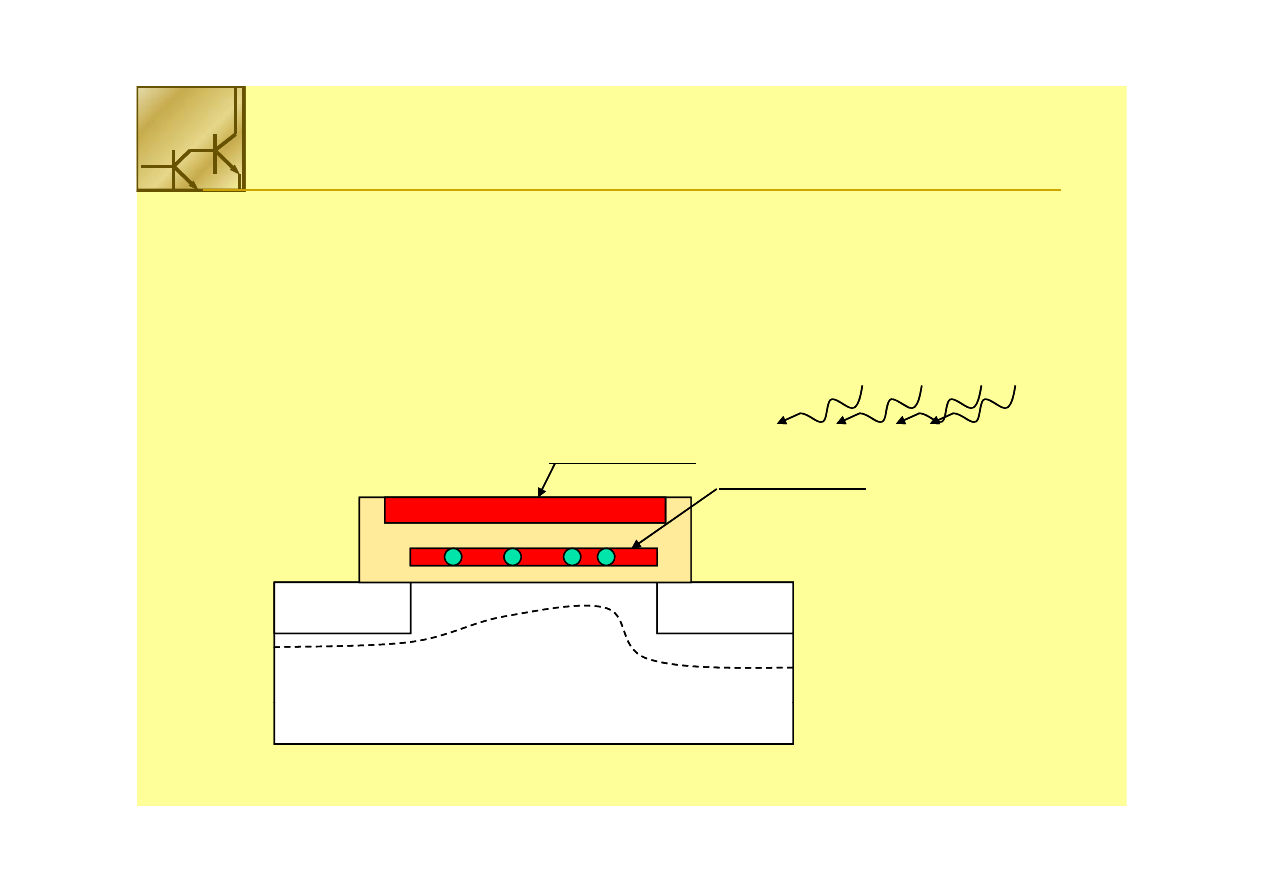

Kasowanie zawartości komórki jest jednoznaczne z kasowaniem całej pamięci EPROM i

Kasowanie zawartości komórki jest jednoznaczne z kasowaniem całej pamięci EPROM i

polega na naświetleniu pamięci źródłem promieniowania nadfioletowego (4.9

polega na naświetleniu pamięci źródłem promieniowania nadfioletowego (4.9 eV

eV).).

Ulotność pamięci EPROM jest niezwykle mała (

Ulotność pamięci EPROM jest niezwykle mała (∼∼10

10

--44

% w czasie 10 lat)

% w czasie 10 lat)

Ulotność pamięci EPROM jest niezwykle mała (

Ulotność pamięci EPROM jest niezwykle mała ( 10

10 % w czasie 10 lat)

% w czasie 10 lat)

Bramka sterująca

Bramka sterująca

Bramka sterująca

Bramka sterująca

Bramka swobodna

Bramka swobodna

Bramka swobodna

Bramka swobodna

0V

0V

0V

0V

S

S

S

S

D

D

D

D

----

----

----

----

nn

++

nn

++

6 marca 2011

Wojciech Kucewicz

51

EPROM

EPROM

EPROM

EPROM

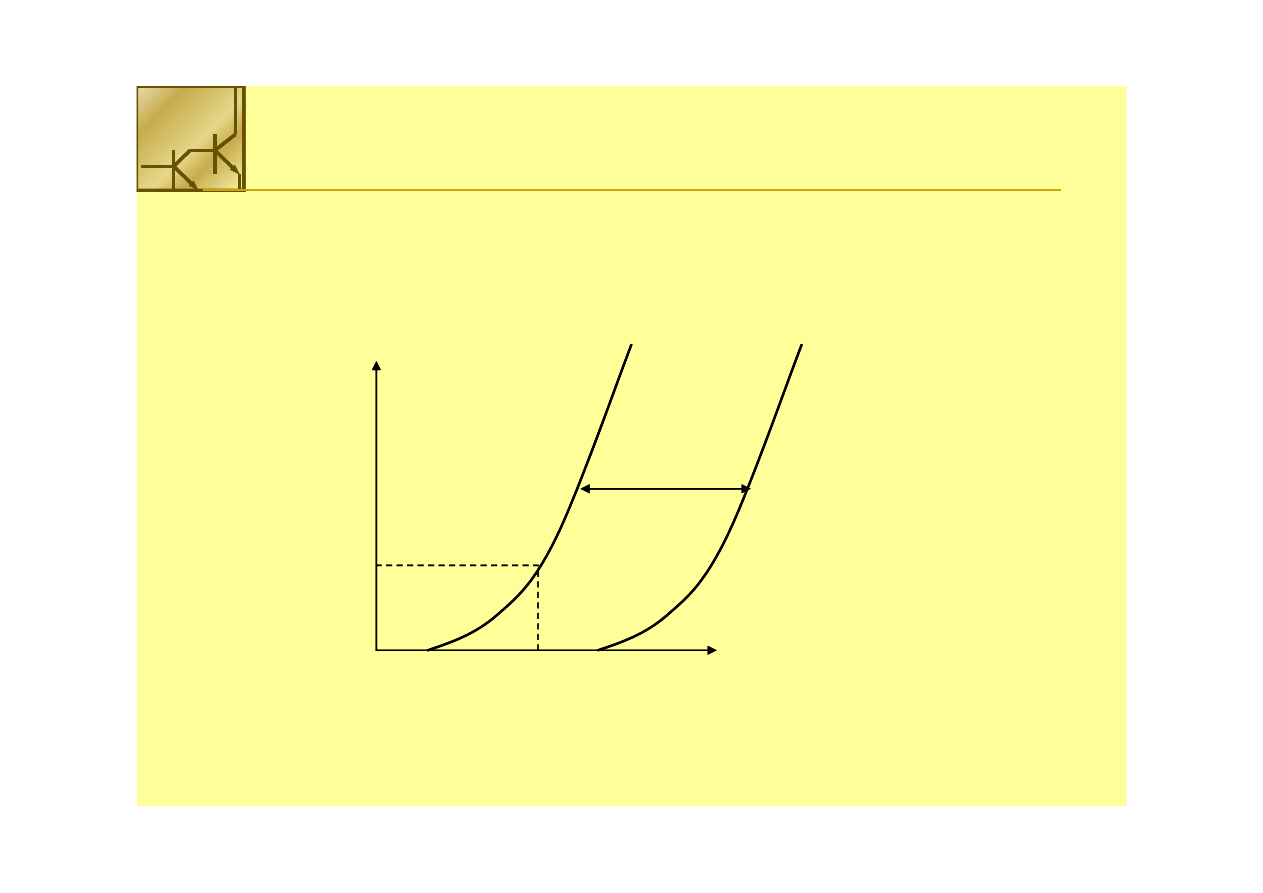

Po zaprogramowaniu napięcie odcięcia U

Po zaprogramowaniu napięcie odcięcia U

T

T

tranzystora zwiększa się o

tranzystora zwiększa się o ΔΔU

U

T

T

i stan bramki

i stan bramki

nie zmienia się po przyłożeniu napięcia 1 na bramkę sterującą

nie zmienia się po przyłożeniu napięcia 1 na bramkę sterującą

II

D

D

II

D

D

ΔΔ

U

U

T

T

ΔΔ

U

U

T

T

Odczyt 1

Odczyt 1

Odczyt 1

Odczyt 1

U

U

GS

GS

U

U

GS

GS

Odczyt 0

Odczyt 0

Odczyt 0

Odczyt 0

1111

6 marca 2011

Wojciech Kucewicz

52

EEPROM

EEPROM

EEPROM

EEPROM

EEPROM (

EEPROM (Electricaly

Electricaly Erasable

Erasable Programmable

Programmable Read

Read Only

Only Memory

Memory) umożliwiają

) umożliwiają

wielokrotne programowanie i kasowanie zawartości

wielokrotne programowanie i kasowanie zawartości –– podobnie jak EPROM, ale

podobnie jak EPROM, ale

kasowanie może być selektywne Komórkę pamięciową układu EPROM stanowi

kasowanie może być selektywne Komórkę pamięciową układu EPROM stanowi

kasowanie może być selektywne. Komórkę pamięciową układu EPROM stanowi

kasowanie może być selektywne. Komórkę pamięciową układu EPROM stanowi

tranzystor, w którym wykorzystuje się zjawisko trwałego magazynowania ładunku w

tranzystor, w którym wykorzystuje się zjawisko trwałego magazynowania ładunku w

podbramkowej warstwie dielektrycznej, wprowadzonego przez wymuszenie napięciowe.

podbramkowej warstwie dielektrycznej, wprowadzonego przez wymuszenie napięciowe.

Przykładem może być struktura FLOTOX (

Przykładem może być struktura FLOTOX (Floating

Floating Gate

Gate Tunnel

Tunnel Oxide

Oxide), która

), która

h

kt

j

i b d

i k

t tl k

d d

któ

żli i

h

kt

j

i b d

i k

t tl k

d d

któ

żli i

charakteryzuje się bardzo cienką warstwą tlenku ponad drenem, która umożliwia

charakteryzuje się bardzo cienką warstwą tlenku ponad drenem, która umożliwia

przepływ elektronów w procesie tunelowania z drenu do bramki swobodnej

przepływ elektronów w procesie tunelowania z drenu do bramki swobodnej

Bramka sterująca

Bramka sterująca

Bramka sterująca

Bramka sterująca

Bramka swobodna

Bramka swobodna

Bramka swobodna

Bramka swobodna

Linia słowa A

Linia słowa A

Linia słowa A

Linia słowa A

Linia bit

u

Linia bit

u

Linia bit

u

Linia bit

u

S

S

S

S

Bramka swobodna

Bramka swobodna

Bramka swobodna

Bramka swobodna

u Au Au Au A

nn

++

nn

++

6 marca 2011

Wojciech Kucewicz

53

EEPROM

EEPROM

EEPROM

EEPROM

Przy U

Przy U

G

G

> 0 i U

> 0 i U

D

D

= 0 bramka swobodna jest sprzężona pojemnościowo z dodatnim

= 0 bramka swobodna jest sprzężona pojemnościowo z dodatnim

potencjałem bramki sterującej i elektrony są do niej przyciągane z drenu. Z kolei przy

potencjałem bramki sterującej i elektrony są do niej przyciągane z drenu. Z kolei przy

U

U

G

G

= 0 i U

= 0 i U

D

D

> 0 następuje rozładowanie swobodnej bramki

> 0 następuje rozładowanie swobodnej bramki

U

U

G

G

0 i U

0 i U

D

D

0 następuje rozładowanie swobodnej bramki.

0 następuje rozładowanie swobodnej bramki.

W pierwszym przypadku otrzymuje się zwiększenie napięcia progowego tranzystora U

W pierwszym przypadku otrzymuje się zwiększenie napięcia progowego tranzystora U

T

T

( w praktyce do ok. 10V), w drugim zmniejszenie U

( w praktyce do ok. 10V), w drugim zmniejszenie U

T

T

poniżej 0V, tak, że otrzymuje się

poniżej 0V, tak, że otrzymuje się

tranzystor z kanałem zubożanym. Wartości tych napięć zależą od długości procesów

tranzystor z kanałem zubożanym. Wartości tych napięć zależą od długości procesów

ii

programowania.

programowania.

Bramka sterująca

Bramka sterująca

Bramka sterująca

Bramka sterująca

Bramka swobodna

Bramka swobodna

Bramka swobodna

Bramka swobodna

U

U

G

G

= 20V

= 20V

U

U

G

G

= 20V

= 20V

Linia słowa A

Linia słowa A

Linia słowa A

Linia słowa A

Linia bit

u

Linia bit

u

Linia bit

u

Linia bit

u

S

S

S

S

Bramka swobodna

Bramka swobodna

Bramka swobodna

Bramka swobodna

G

G

G

G

u Au Au Au A

S D

S D

nn

++

nn

++

---- ----

----

----

U

U

D

D

= 0V

= 0V

U

U

D

D

= 0V

= 0V

6 marca 2011

Wojciech Kucewicz

54

EEPROM

EEPROM

EEPROM

EEPROM

Przy U

Przy U

G

G

> 0 i U

> 0 i U

D

D

= 0 bramka swobodna jest sprzężona pojemnościowo z dodatnim

= 0 bramka swobodna jest sprzężona pojemnościowo z dodatnim

potencjałem bramki sterującej i elektrony są do niej przyciągane z drenu. Z kolei przy

potencjałem bramki sterującej i elektrony są do niej przyciągane z drenu. Z kolei przy

U

U

G

G

= 0 i U

= 0 i U

D

D

> 0 następuje rozładowanie swobodnej bramki

> 0 następuje rozładowanie swobodnej bramki

U

U

G

G

0 i U

0 i U

D

D

0 następuje rozładowanie swobodnej bramki.

0 następuje rozładowanie swobodnej bramki.

W pierwszym przypadku otrzymuje się zwiększenie napięcia progowego tranzystora U

W pierwszym przypadku otrzymuje się zwiększenie napięcia progowego tranzystora U

T

T

( w praktyce do ok. 10V), w drugim zmniejszenie U

( w praktyce do ok. 10V), w drugim zmniejszenie U

T

T

poniżej 0V, tak, że otrzymuje się

poniżej 0V, tak, że otrzymuje się

tranzystor z kanałem zubożanym. Wartości tych napięć zależą od długości procesów

tranzystor z kanałem zubożanym. Wartości tych napięć zależą od długości procesów

ii

programowania.

programowania.

Bramka sterująca

Bramka sterująca

Bramka sterująca

Bramka sterująca

Bramka swobodna

Bramka swobodna

Bramka swobodna

Bramka swobodna

U

U

G

G

= 0V

= 0V

U

U

G

G

= 0V

= 0V

Linia słowa A

Linia słowa A

Linia słowa A

Linia słowa A

Linia bit

u

Linia bit

u

Linia bit

u

Linia bit

u

S

S

S

S

Bramka swobodna

Bramka swobodna

Bramka swobodna

Bramka swobodna

----

----

----

----

G

G

G

G

u Au Au Au A

S D

S D

nn

++

nn

++

U

U

D

D

= 20V

= 20V

U

U

D

D

= 20V

= 20V

6 marca 2011

Wojciech Kucewicz

55

EEPROM

EEPROM

EEPROM

EEPROM

Jednobitowe komórki pamięci EEPROM tworzy się przez połączenie

Jednobitowe komórki pamięci EEPROM tworzy się przez połączenie

tranzystora FLOTOX z normalnym tranzystorem MOS

tranzystora FLOTOX z normalnym tranzystorem MOS

LLLL

0000

++++

Linia bitu 0VLinia bitu 0VLinia bitu 0VLinia bitu 0V

0V 0V -

-U

tr

zy

m

a

Utrzym

a

0V 0V -

-U

tr

zy

m

a

Utrzym

a

18V 18V -

-Z

ap

is

Zapis

18V 18V -

-Z

ap

is

Zapis

Linia programowania 20V

Linia programowania 20V

Linia programowania 20V

Linia programowania 20V

Linia słowa 20V

Linia słowa 20V

Linia słowa 20V

Linia słowa 20V

0V

0V

0V

0V

anie 1anie 1anie 1anie 1

20V

20V

20V

20V

0000

S

S

S

S

S

S

S

S

S

S

S

S

Rozładowanie bramki

Rozładowanie bramki

Ładowanie

Ładowanie bramki

bramki

Kasowanie (ustalanie 1)

Kasowanie (ustalanie 1)

Selektywny zapis 0

Selektywny zapis 0

K ó k

ł d

b

k b d j

i

i

d

i

6 marca 2011

Wojciech Kucewicz

56

Komórka z naładowana bramką swobodną pozostaje w stanie nieprzewodzenia,

natomiast komórka rozładowana będzie przewodzić.

Flash

Flash EEPROM

EEPROM

Flash

Flash EEPROM

EEPROM

Flash

Flash EEPROM

EEPROM

Flash

Flash EEPROM

EEPROM

6 marca 2011

Wojciech Kucewicz

57

Flash EEPROM

Flash EEPROM

Flash EEPROM

Flash EEPROM

Pamięci

Pamięci Flash

Flash EEPROM są specyficzną odmianą pamięci EEPROM charakteryzujących

EEPROM są specyficzną odmianą pamięci EEPROM charakteryzujących

się błyskawicznym kasowaniem zawartości bloków lub całej pamięci (1ms) w porównaniu

się błyskawicznym kasowaniem zawartości bloków lub całej pamięci (1ms) w porównaniu

z kasowanie zawartości

z kasowanie zawartości EPROM

EPROM (ok 15 min

(ok 15 min)

)

z kasowanie zawartości

z kasowanie zawartości EPROM

EPROM (ok. 15 min

(ok. 15 min).

).

Przykładem

Przykładem flash

flash EEPROM może być struktura ETOX (EPROM

EEPROM może być struktura ETOX (EPROM with

with Tunnel

Tunnel Oxide

Oxide))

Tlenek pod bramką swobodną ma grubość 10 nm.

Tlenek pod bramką swobodną ma grubość 10 nm.

Bramka sterująca

Bramka sterująca

Bramka sterująca

Bramka sterująca

Cykl programowania jest dwuetapowy i musi być poprzedzony kasowaniem

jjjj

Bramka swobodna

Bramka swobodna

Bramka swobodna

Bramka swobodna

Kasowanie jest wykonywane w

Kasowanie jest wykonywane w

procesie tunelowym (jak w

procesie tunelowym (jak w

EEPROM) przy napięciu na bramce

EEPROM) przy napięciu na bramce

0V i źródle +5V

0V i źródle +5V

S D

S D

nn

++

nn

++

0V i źródle +5V.

0V i źródle +5V.

Programowanie realizowane jest

Programowanie realizowane jest

przez wstrzykiwanie gorących

przez wstrzykiwanie gorących

elektronów (jak w EPROM) przy

elektronów (jak w EPROM) przy

i i

b

i d

i 12V

i i

b

i d

i 12V

6 marca 2011

Wojciech Kucewicz

58

S D

S D

napięciu na bramce i drenie +12V.

napięciu na bramce i drenie +12V.

Flash EEPROM

Flash EEPROM

Flash EEPROM

Flash EEPROM

Architektura pamięci

Architektura pamięci Flash

Flash

Bramka sterująca

Bramka sterująca

Bramka sterująca

Bramka sterująca

LiLiLiLi

LiLiLiLi

jjjj

Bramka swobodna

Bramka swobodna

Bramka swobodna

Bramka swobodna

LS A

LS A

LS A

LS A

inia bitu Ainia bitu Ainia bitu Ainia bitu A

S

S

S

S

inia bitu Binia bitu Binia bitu Binia bitu B

S

S

S

S

S D

S D

nn

++

nn

++

LS B

LS B

LS B

LS B

S

S

S

S

S

S

S

S

6 marca 2011

Wojciech Kucewicz

59

S D

S D

Rejestry

Rejestry

Rejestry

Rejestry

Rejestry

Rejestry

Rejestry

Rejestry

j

y

j

y

6 marca 2011

Wojciech Kucewicz

60

Rejestry

Rejestry

Rejestry

Rejestry

Rejestr to jest układ pamięci służący do chwilowego zapamiętywania

Rejestr to jest układ pamięci służący do chwilowego zapamiętywania

danych i wyników operacji oraz do ich przetwarzania.

danych i wyników operacji oraz do ich przetwarzania.

y

y

p

j

p

y

y

p

j

p

Podobnie jak w pamięciach rozróżniamy rejestry statyczne i

Podobnie jak w pamięciach rozróżniamy rejestry statyczne i

dynamiczne.

dynamiczne.

dynam czne.

dynam czne.

Rejestr statyczny jest złożony z n przerzutników i zapisana w nim

Rejestr statyczny jest złożony z n przerzutników i zapisana w nim

i f

j

t i ł

i f

j

t i ł

bit

ż i

t

ć

bit

ż i

t

ć

informacja w postaci słowa n

informacja w postaci słowa n--bitowego może w nim pozostawać

bitowego może w nim pozostawać

dowolnie długo.

dowolnie długo.

W rejestrze dynamicznym, podobnie jak w pamięciach dynamicznych

W rejestrze dynamicznym, podobnie jak w pamięciach dynamicznych

ść

ć

ś

ść

ć

ś

zawartość rejestru musi być odświeżana.

zawartość rejestru musi być odświeżana.

6 marca 2011

Wojciech Kucewicz

61

Rejestry

Rejestry

Rejestry

Rejestry

Ze względu na sposób wprowadzania i wyprowadzania informacji

Ze względu na sposób wprowadzania i wyprowadzania informacji

rejestry dzielimy na:

rejestry dzielimy na:

Szeregowe

Szeregowe

–– umożliwiające szeregowe wprowadzanie i

umożliwiające szeregowe wprowadzanie i

wyprowadzanie informacji, tj. bit po bicie;

wyprowadzanie informacji, tj. bit po bicie;

Ró

l ł

Ró

l ł

żli i j

ó

l ł

d

i

i

żli i j

ó

l ł

d

i

i

Równoległe

Równoległe

–– umożliwiające równoległe wprowadzanie i

umożliwiające równoległe wprowadzanie i

wyprowadzanie informacji, tj. jednoczesne do wszystkich pozycji

wyprowadzanie informacji, tj. jednoczesne do wszystkich pozycji

rejestru np. bajtami;

rejestru np. bajtami;

óó

Szeregowo

Szeregowo--równoległe

równoległe

–– umożliwiające szeregowe wprowadzanie

umożliwiające szeregowe wprowadzanie

i równolegle wyprowadzanie informacji;

i równolegle wyprowadzanie informacji;

Równoległo

Równoległo--szeregowe

szeregowe

–– umożliwiające równolegle wprowadzanie i

umożliwiające równolegle wprowadzanie i

gg

gg

j

g

p

j

g

p

szeregowe wyprowadzanie informacji.

szeregowe wyprowadzanie informacji.

6 marca 2011

Wojciech Kucewicz

62

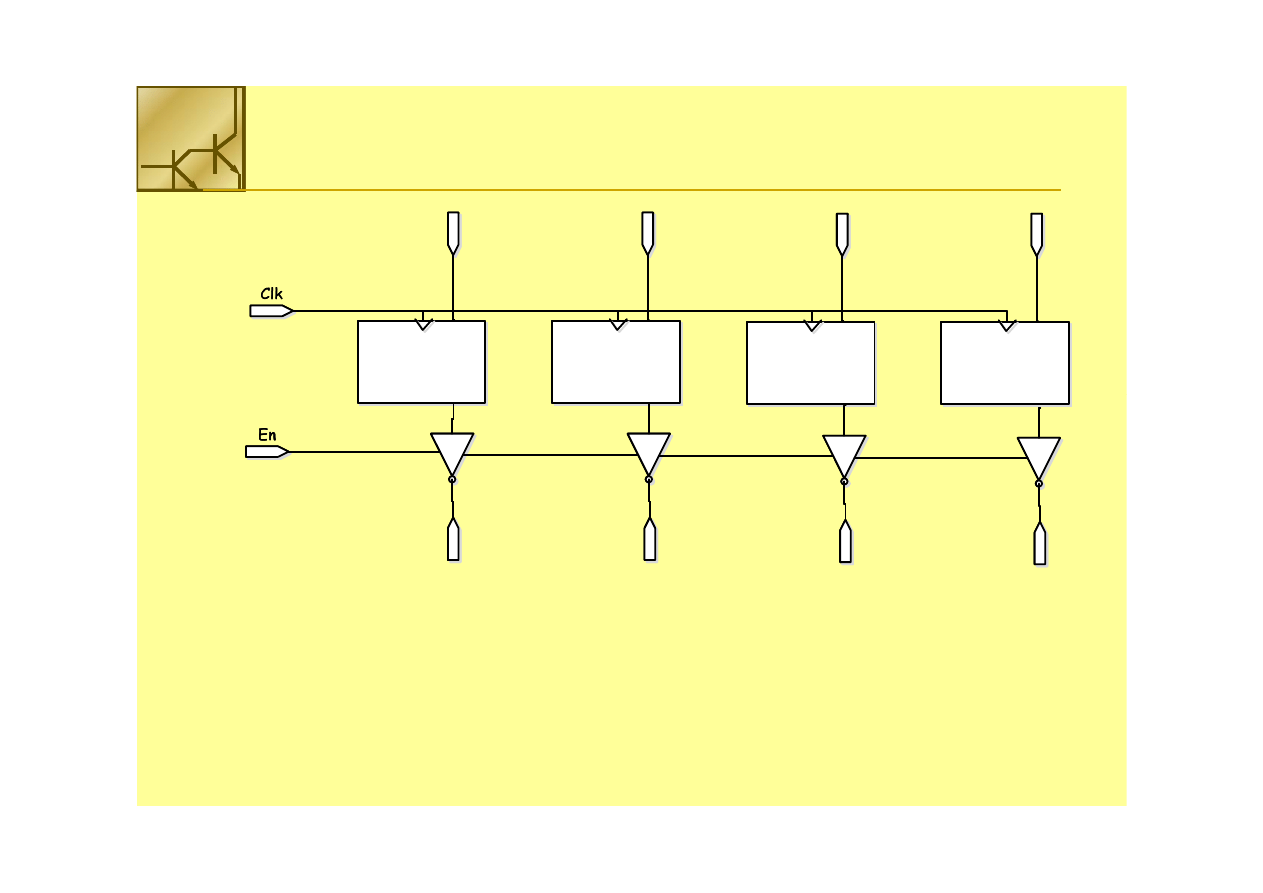

Rejestr równoległy

Rejestr równoległy

Rejestr równoległy

Rejestr równoległy

X0

X1

X2

X3

X0

X1

X2

X3

1 0 1 0

1 0 1 0

D

Q

Cl

k

Q

Res

D

Q

Cl

k

Q

Res

D

Q

Cl

k

Q

Res

D

Q

Cl

k

Q

Res

D

Q

Cl

k

Q

Res

D

Q

Cl

k

Q

Res

D

Q

Cl

k

Q

Res

D

Q

Cl

k

Q

Res

Clock

Clock = 1

= 1Î

Î

00

Q

’

Q

Q

’

Q

Q

’

Q

Q

’

Q

Q

’

Q

Q

’

Q

Q

’

Q

Q

’

Q

0 1 0 1

0 1 0 1

Enable

Enable= 1

= 1

Q0

Q1

Q2

Q3

Q0

Q1

Q2

Q3

Rejestry równoległe

Rejestry równoległe

nazywane są

nazywane są

rejestrami buforowymi

rejestrami buforowymi

1 0 1 0

1 0 1 0

Rejestry równoległe

Rejestry równoległe

nazywane są

nazywane są

rejestrami buforowymi

rejestrami buforowymi

Najczęściej budowane są z przerzutników typu D wyzwalanych poziomem

Najczęściej budowane są z przerzutników typu D wyzwalanych poziomem

sygnału lub zboczem.

sygnału lub zboczem.

6 marca 2011

Wojciech Kucewicz

63

Dostęp do informacji jest możliwy poprzez bramki buforowe przy

Dostęp do informacji jest możliwy poprzez bramki buforowe przy

odpowiednim wymuszeniu na wejściu

odpowiednim wymuszeniu na wejściu enable

enable..

Rejestr równoległy

Rejestr równoległy

Rejestr równoległy

Rejestr równoległy

X0

X1

X2

X3

En

X0

X1

X2

X3

En

1 0 1 0

1 0 1 0

Input

Input enable

enable =1

=1

Clock

Clock = 1

= 1Î

Î

00

Input

Input enable

enable =0

=0

Clock

Clock = 1

= 1Î

Î

00

D

Q

Cl

k

Res

Clk

D

Q

Cl

k

Res

D

Q

Cl

k

Res

D

Q

Cl

k

Res

D

Q

Cl

k

Res

Clk

D

Q

Cl

k

Res

D

Q

Cl

k

Res

D

Q

Cl

k

Res

Q

’

Q

Q0

Q

’

Q

Q1

Q

’

Q

Q2

Q

’

Q

Q3

Q

’

Q

Q0

Q

’

Q

Q1

Q

’

Q

Q2

Q

’

Q

Q3

k d

ó

l

ś

k d kl

k d

ó

l

ś

k d kl

6 marca 2011

Wojciech Kucewicz

64

Przykład rejestru równoległego z przepisywaniem wejścia przy każdym cyklu

Przykład rejestru równoległego z przepisywaniem wejścia przy każdym cyklu

zegarowym

zegarowym

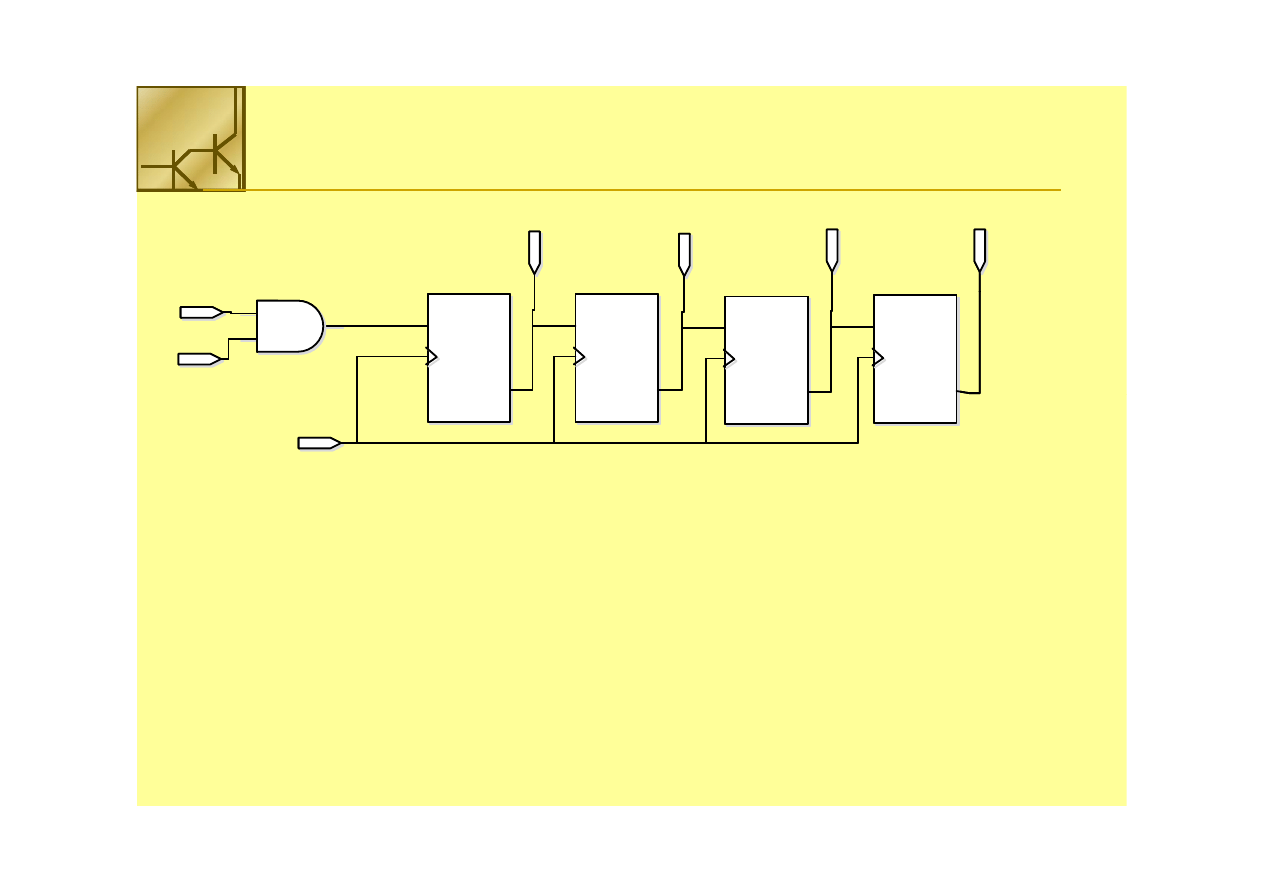

Rejestr przesuwny

Rejestr przesuwny -- szeregowy

szeregowy

Rejestr przesuwny

Rejestr przesuwny -- szeregowy

szeregowy

Enable

Enable= 1

= 1

0011001100

Clock

Clock = 1

= 1Î

Î

00

b d

kó

l b

h

b d

kó

l b

h

Rejestr przesuwny budowany jest z przerzutników D, JK lub RS połączonych

Rejestr przesuwny budowany jest z przerzutników D, JK lub RS połączonych

kaskadowo w taki sposób, że stan logiczny przerzutnika jest przesuwany do

kaskadowo w taki sposób, że stan logiczny przerzutnika jest przesuwany do

następnego przerzutnika w takt sygnału zegarowego.

następnego przerzutnika w takt sygnału zegarowego.

N j

sts

j st

s

j st

N j

sts

j st

s

j st

j st s

j st s

któ

któ

6 marca 2011

Wojciech Kucewicz

65

Najprostszym rejestrem przesuwnym jest

Najprostszym rejestrem przesuwnym jest

rejestr szeregowy

rejestr szeregowy

, w którym

, w którym

informacje są wprowadzane i wyprowadzane szeregowo.

informacje są wprowadzane i wyprowadzane szeregowo.

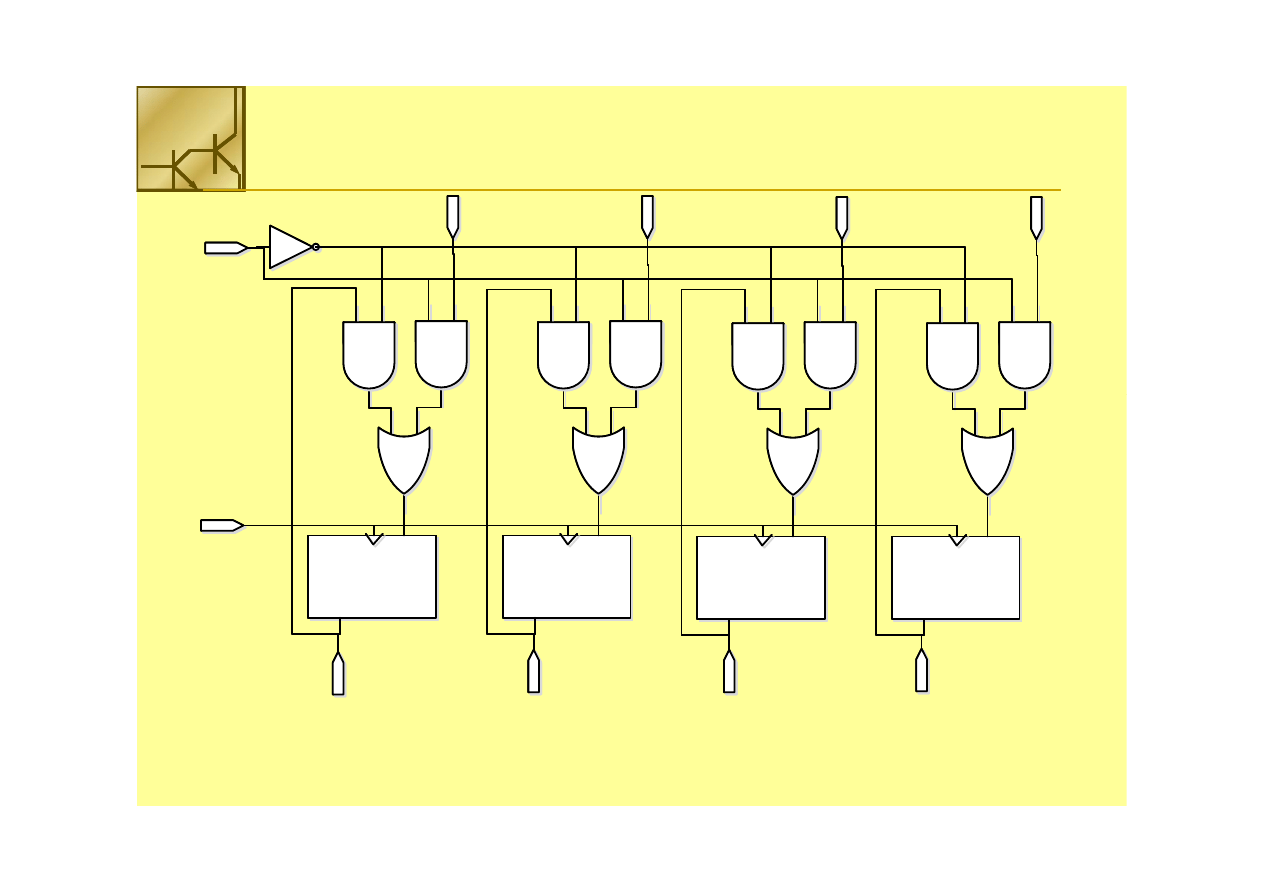

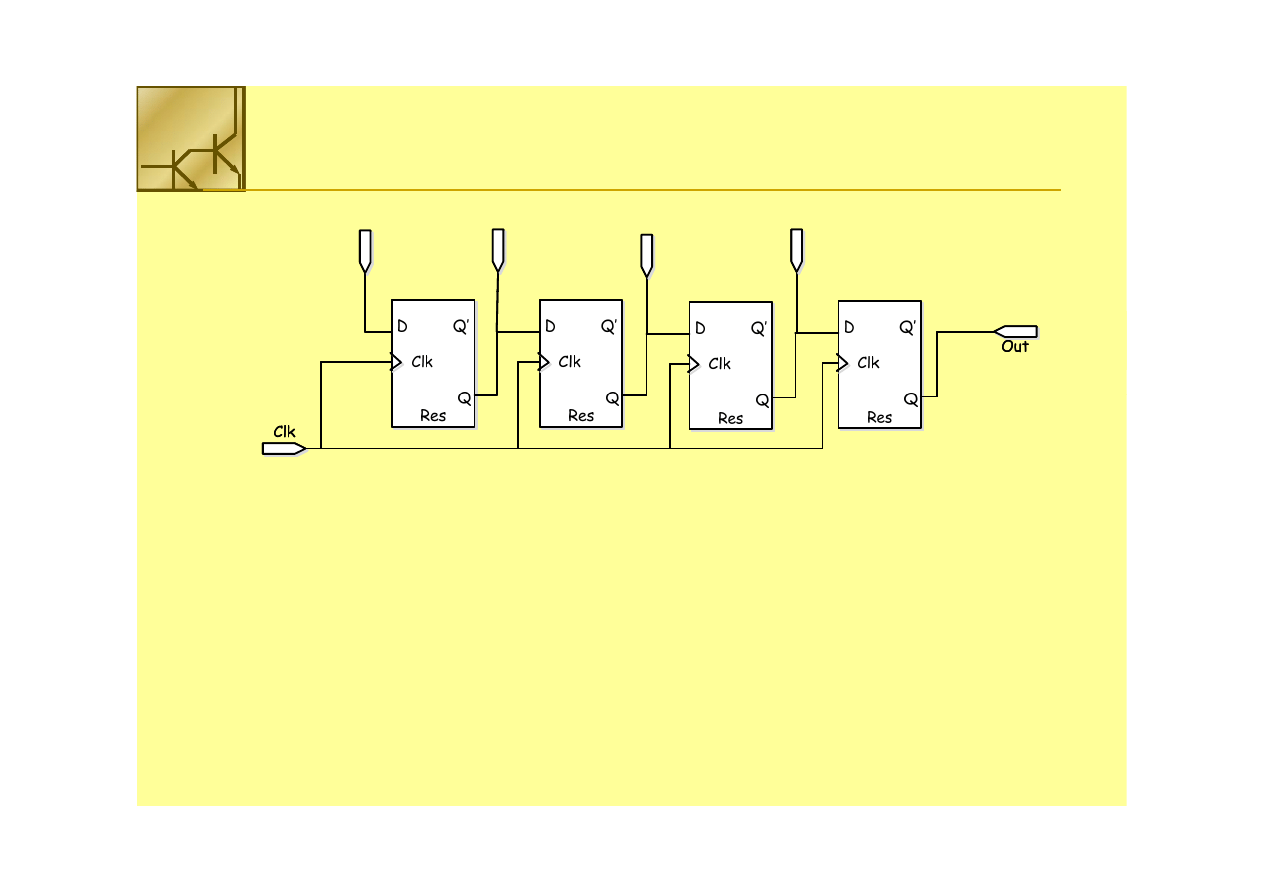

Rejestr przesuwny

Rejestr przesuwny –– szeregowo

szeregowo--równoległy

równoległy

Rejestr przesuwny

Rejestr przesuwny –– szeregowo

szeregowo--równoległy

równoległy

E

Q3

Q2

Q1

Q0

E

Q3

Q2

Q1

Q0

Enable

Enable= 1

= 1

D Q’

Clk

Q

D Q’

Clk

Q

D Q’

Clk

Q

D Q’

Clk

Q

En

Inp

D Q’

Clk

Q

D Q’

Clk

Q

D Q’

Clk

Q

D Q’

Clk

Q

En

Inp

0011001100

Q

Res

Q

Res

Q

Res

Q

Res

Clk

Q

Res

Q

Res

Q

Res

Q

Res

Clk

Clock

Clock = 1

= 1Î

Î

00

Rejestr przesuwny budowany jest z przerzutników D, JK lub RS połączonych

Rejestr przesuwny budowany jest z przerzutników D, JK lub RS połączonych

kaskadowo w taki sposób, że stan logiczny przerzutnika jest przesuwany do

kaskadowo w taki sposób, że stan logiczny przerzutnika jest przesuwany do

następnego przerzutnika w takt sygnału zegarowego

następnego przerzutnika w takt sygnału zegarowego

następnego przerzutnika w takt sygnału zegarowego.

następnego przerzutnika w takt sygnału zegarowego.

Przykładem

Przykładem

rejestru szeregowo

rejestru szeregowo--równoległego

równoległego

jest rejestr SIPO SISO

jest rejestr SIPO SISO

((serial

serial--in

in parallel

parallel--out

out), który zamienia informację z postaci szeregowej na

), który zamienia informację z postaci szeregowej na

równoległą

równoległą

6 marca 2011

Wojciech Kucewicz

66

równoległą.

równoległą.

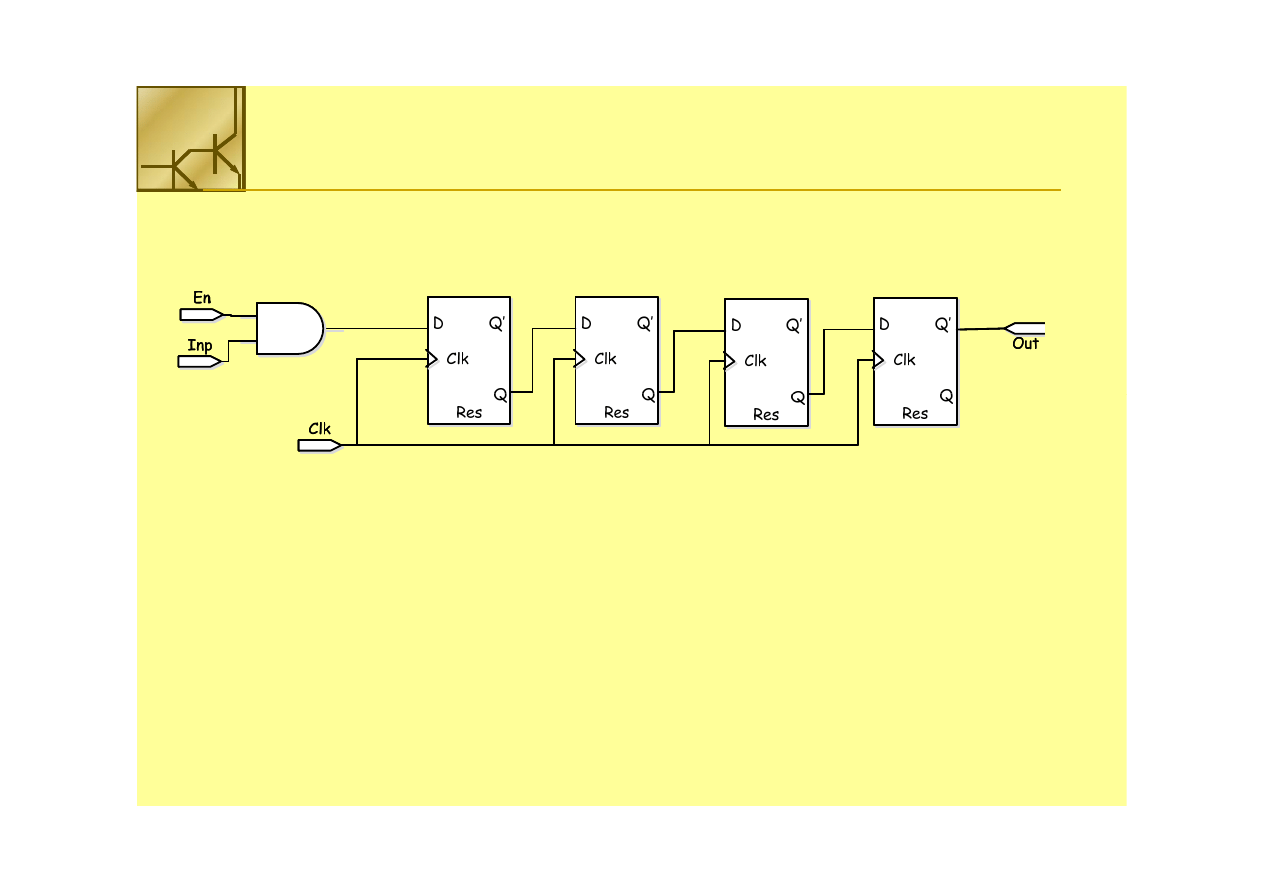

Rejestr przesuwny

Rejestr przesuwny –– równoległo

równoległo--szeregowy

szeregowy

Rejestr przesuwny

Rejestr przesuwny –– równoległo

równoległo--szeregowy

szeregowy

X3

X2

X1

X0

X3

X2

X1

X0

1 0 1 0

1 0 1 0

Rejestr przesuwny budowany jest z przerzutników D, JK lub RS połączonych

Rejestr przesuwny budowany jest z przerzutników D, JK lub RS połączonych

kaskadowo w taki sposób, że stan logiczny przerzutnika jest przesuwany do

kaskadowo w taki sposób, że stan logiczny przerzutnika jest przesuwany do

następnego przerzutnika w takt sygnału zegarowego

następnego przerzutnika w takt sygnału zegarowego

następnego przerzutnika w takt sygnału zegarowego.

następnego przerzutnika w takt sygnału zegarowego.

Rejestr równoległo

Rejestr równoległo--szeregowy

szeregowy

PISO (

PISO (parallel

parallel--in

in serial

serial--out)zamienia

out)zamienia

informację z postaci równoległej na szeregową.

informację z postaci równoległej na szeregową.

6 marca 2011

Wojciech Kucewicz

67

Wyszukiwarka

Podobne podstrony:

Fizjologia Cwiczenia 11 id 1743 Nieznany

Biologia Cwiczenia 11 id 87709 Nieznany (2)

dodatkowe1 analiza 11 12 2 sem Nieznany

moje wykresy 11 id 306777 Nieznany

11 21id 12110 Nieznany (2)

G2 PB 02 B Rys 3 11 id 185401 Nieznany

III CZP 33 11 id 210275 Nieznany

11 14id 12096 Nieznany (2)

2013 11 04id 28244 Nieznany (2)

mat bud cwicz 10 11 id 282450 Nieznany

Odpowiedzi 1 3 5 8 9 11 13 id 3 Nieznany

grupa 11 id 441853 Nieznany

24 11 id 30514 Nieznany (2)

mnozenie do 25 11 id 304283 Nieznany

cwiczenie 11 id 125145 Nieznany

11 transportid 12256 Nieznany (2)

11 bucid 12376 Nieznany (2)

więcej podobnych podstron