Architektura Systemów Komputerowych

Laboratorium

Nr ćwiczenia: 1

Temat ćwiczenia: Ćwiczenie wprowadzające w tematykę laboratorium.

Imię i nazwisko prowadzącego kurs: Maciej Huk

Wykonawca:

Jakub Bartusiak

Imię i Nazwisko

nr Indeksu, wydział

Jakub Bartusiak

197914, SKP

Termin zajęć: dzień tygodnia, godzina

Wtorek, 15

15

Data oddania sprawozdania:

Ocena końcowa

Ewentualne adnotacje dotyczące wymaganych poprawek oraz daty otrzymania poprawionego

sprawozdania:

1 |

S t r o n a

Spis treści

5. ODRĘCZNE RYSUNKI ................................................................................................................. 8

Bibliografia

1. Strona Texas Insruments, specyfikacja układu SN74194:

http://www.ti.com/product/sn74194

2. Strona Silicon Far East, informację na temat technologii TTL:

http://www.siliconfareast.com/ttl.htm

2 |

S t r o n a

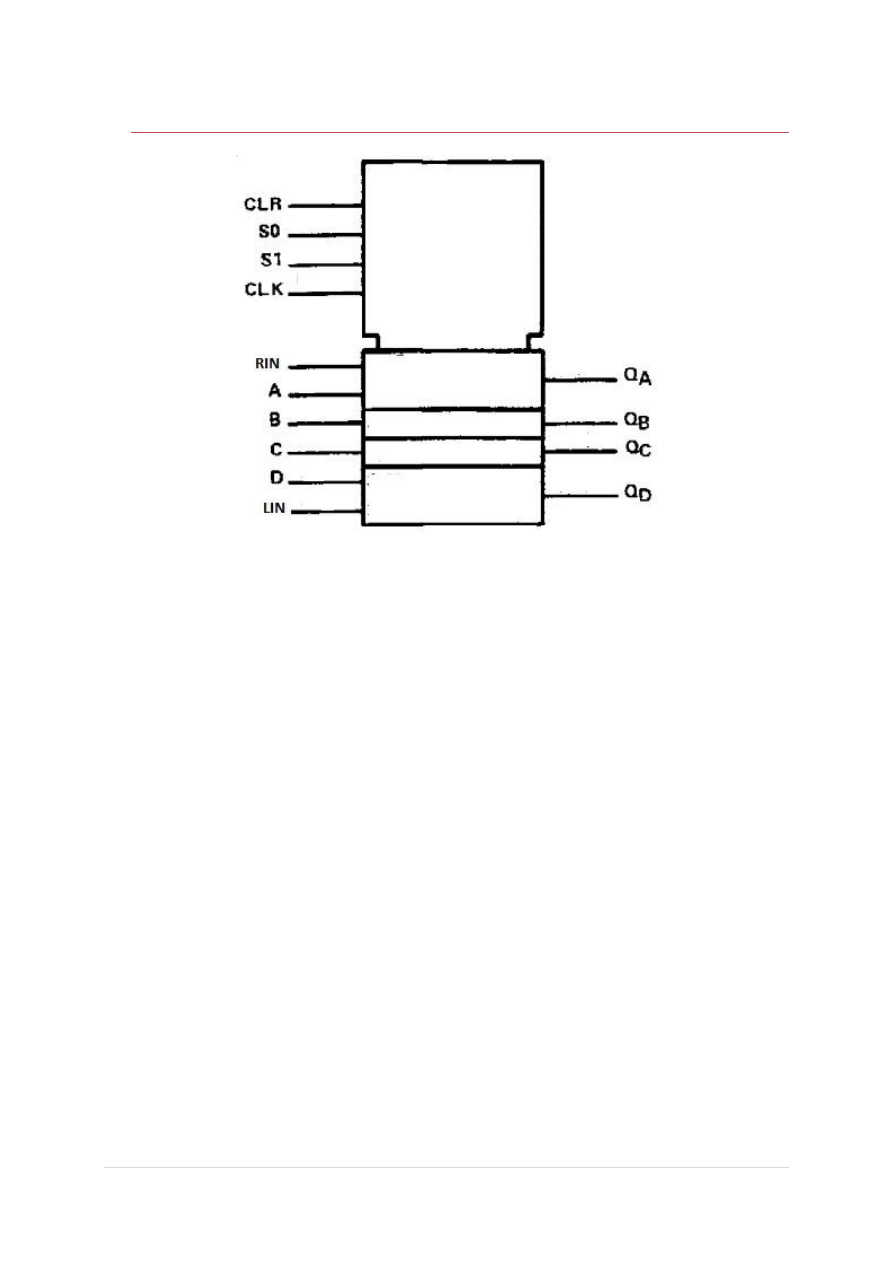

1. Schemat układu

Rysunek 1. Wejścia i wyjścia układu 74194

CLR- sygnał Clear

S0 i S1- wejścia rodzaju pracy

CLK- wejście zegara

RIN i LIN – wejścia szeregowe prawe i lewe

A, B, C, D- wejścia danych

Q

A

, Q

B

, Q

C

, Q

D

- wyjścia danych

3 |

S t r o n a

2. Specyfikacja układu i sposób działania

Układ UCY 74194 jest uniwersalnym czterobitowym dwukierunkowym rejestrem przesuwającym.

Realizuje on wszystkie podstawowe funkcje wymagane przez projektanta urządzeń lub systemów.

Rejestr ma równoległe wejścia i wyjścia, szeregowe wejścia do przesuwania w prawo i w lewo,

wejścia rodzaju pracy oraz asynchroniczne wejście zerowania.

Rejestr ma cztery podstawowe funkcje:

a) wprowadzanie równoległe,

b) przesuwanie w prawo,

c) przesuwanie w lewo,

d) blokada zegara.

a) Wprowadzanie równoległe: przeprowadzony poprzez ustawienie wejść S0 i S1 w stan wysoki,

oraz wprowadzenie czterech bitów danych do odpowiednich wejść- które po przetworzeniu

są ładowane do odpowiednich wyjść. W czasie wprowadzania równoległego, wejścia

szeregowe są zablokowane.

b) Przesuwanie rejestru w prawo realizowane jest poprzez utrzymanie stanu wysokiego na

wejściu S0, oraz stanu niskiego na wejściu S1. Dane są wprowadzane z wejścia prawego SR i

przesuwane w prawo wzdłóż rejestru synchronicznie ze wzrostem zbocza impulsu

zegarowego. W czasie przesuwania w prawo wejścia równoległe (ABCD) są zablokowane.

c) Przesuwanie rejestru w lewo realizowane jest poprzez utrzymanie stanu wysokiego na

wejściu S1, oraz stanu niskiego na wejściu S0. Dane są wprowadzane z wejścia lewego (SL) i

przesuwane w lewo wzdłóż rejestru synchronicznie ze wzrostem zbocza impulsu zegarowego.

W czasie przesuwania w lewo, wejścia równoległe (ABCD) są zablokowane.

d) Blokada zegara następuje, gdy na obu wejściach rodzaju pracy (S0 i S1) jest przyłożony stan

niski. Zmiany stanu na wejściach powinny być realizowane, gdy na wejściu zegarowym

istnieje stan wysoki.

Z racji technologii zastosowanej w układzie (TTL), wejścia które nie mają określonych wartości (nie są

podłączone, ani uziemione), najprawdopodobniej mają wysoki stan logiczny. Nie mamy jednak do

tego 100% pewności, więc bezpieczniejszym wyjściem jest uziemienie lub podłączenie danego

wejścia.

Rola zegara- każdy takt zegara pozwala przeprowadzać kolejne kroki obliczeń.

Sygnał CLEAR powoduje ustawienie wszystkich wartości układu do 0.

Sygnał RESET jest zadajnikiem wartości logicznej. Dzięki niemu możemy dostosować sygnał, jaki jest

wysyłany.

Różnica pomiędzy RIN i LIN- przy przesuwaniu w prawo, wartość jest kopiowana do wyjścia Q

A

, z

wejścia RIN. Przy przesuwaniu w lewo, wartość jest kopiowana do wyjścia Q

B

z wejścia LIN.

Wejścia A, B, C, D- pozwalają zadać wartości na odpowiadające im wyjścia Q

A

, Q

B

, Q

C

, Q

D

, przy

wprowadzaniu równoległym.

4 |

S t r o n a

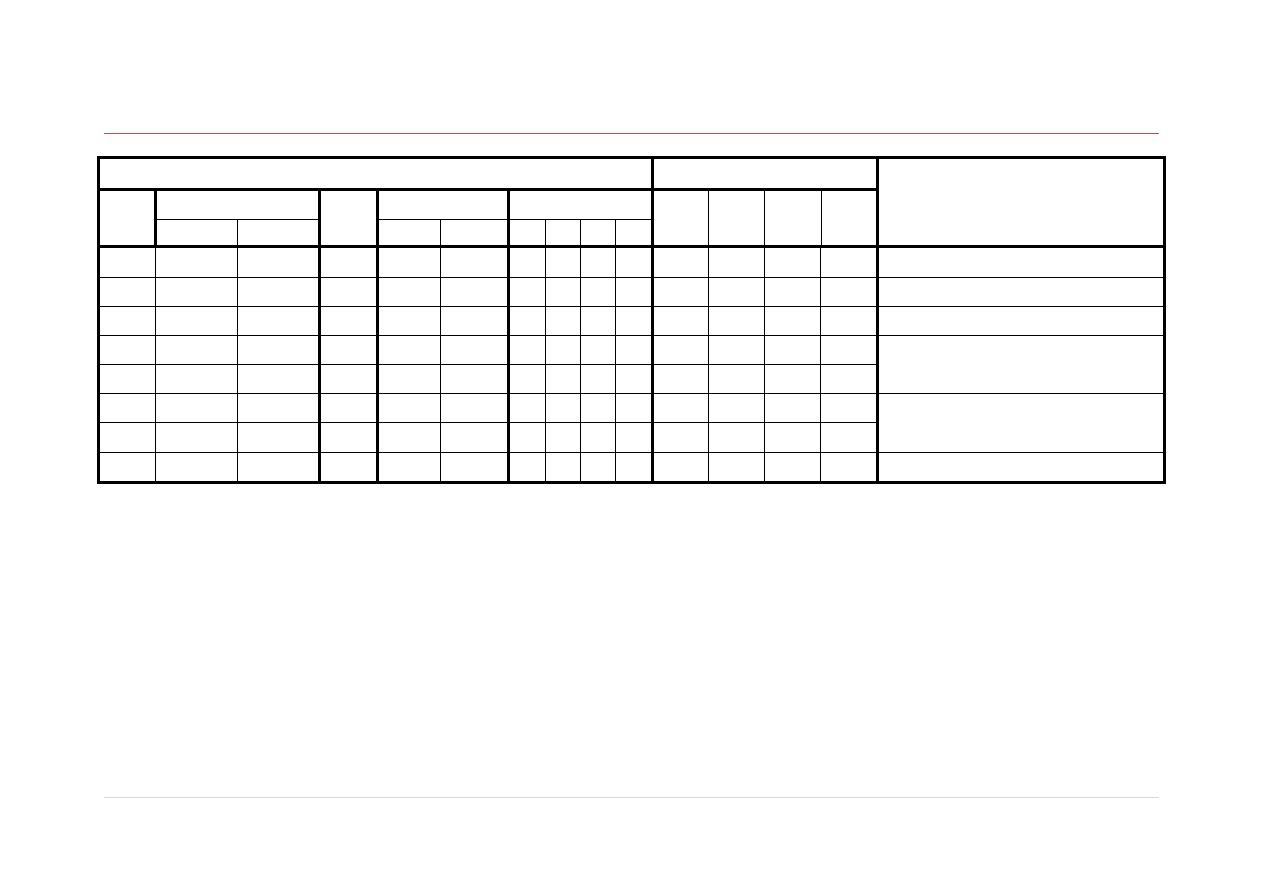

3. Działanie logiczne rejestru- tabela stanów

Wejścia

Wyjścia

Funkcja

CLRN

Rodzaju pracy

CLK

Szeregowe

Równoległe

Q

A

Q

B

Q

C

Q

D

S1

S0

LIN

RIN

A

B

C

D

L

X

X

X

X

X

X

X

X

X

L

L

L

L

Zerowanie asynchroniczne

H

X

X

L

X

X

X

X

X

X

Q

A0

Q

B0

Q

C0

Q

D0

-

H

H

H

↑

X

X

a

b

c

d

a

b

c

d

Wprowadzanie równoległe

H

L

H

↑

X

H

X

X

X

X

H

Q

An

Q

Bn

Q

Cn

Przesuwanie w prawo

H

L

H

↑

X

L

X

X

X

X

L

Q

An

Q

Bn

Q

Cn

H

H

L

↑

H

X

X

X

X

X

Q

Bn

Q

Cn

Q

Dn

H

Przesuwanie w lewo

H

H

L

↑

L

X

X

X

X

X

Q

Bn

Q

Cn

Q

Dn

L

H

L

L

X

X

X

X

X

X

X

Q

A0

Q

B0

Q

C0

Q

D0

Blokada

Tabela 1.

Legenda:

H- Stan wysoki, L- Stan niski, X- Stan dowolny (logicznie obojętny);

QA0, QB0, QC0, QD0- wartości odpowiednio QA, QB, QC, QD, przed modyfikacją (takie jak na wejściu);

Qan, QBn, QCn, QDn- wartości odpowienio QA, QB, QC i QD na wyjściu przerzutników, przed ostatnią zmianą na wejściu zegarowym ze stanu niskiego na

wysoki;

a, b, c, d- wartości ustalone na wejściach A, B, C, D;

↑- narastające zbocze sygnału zegarowego.

5 |

S t r o n a

4. Analiza działania układów.

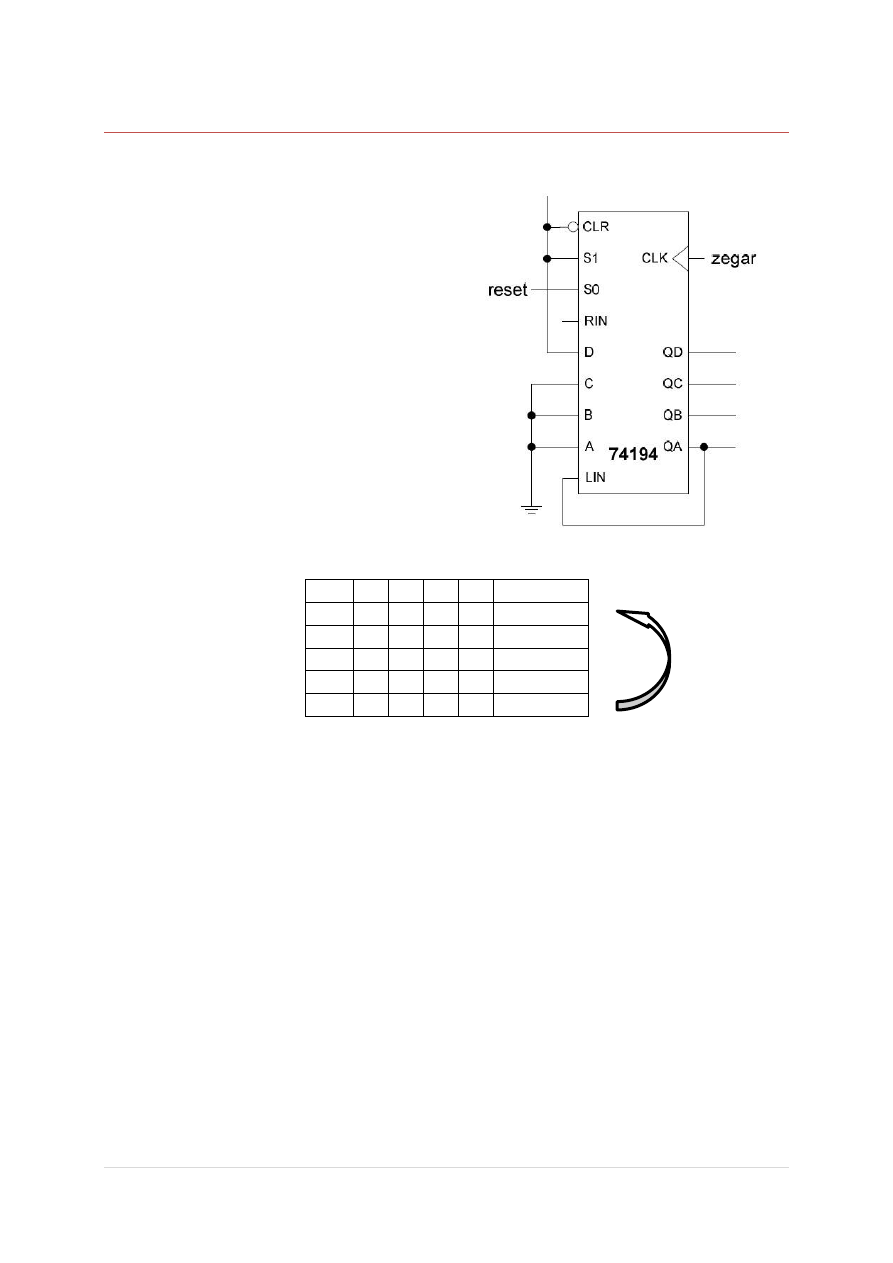

Układ A.

1. Wejście Clear (CLR) jest nieaktywne (aktywne

stanem wysokim).

2. Tryb działania:

a) Przy założeniu że sygnał reset ma wysoki

stan

logiczny-

wprowadzanie

równoległe (S0-1, S1- 1),

b) przy założeniu że sygnał reset ma nistki

stan logiczny- przsuwanie w lewo (S1-

1, S2- 0).

3. Wejście RIN- prawdopodobnie 1.

4. Wejście LIN:

5. Wejście D- sygnał 1.

6. Wejścia A, B, C- sygnały 0.

Takie ustawienie (gdy reset-1) wczyta wartości z

wejść A, B, C, D do wyjść QA, QB, QC, QD. Po zmianie

sygnału reset na 0 układ zacznie przesuwanie w

lewo.

Takt Q

D

Q

C

Q

B

Q

A

1

1

0

0

0

0

2

0

1

0

0

0

3

0

0

1

0

0

4

0

0

0

1

1

5

1

0

0

0

0

Cykl jest stały i powtarza się co cztery takty.

6 |

S t r o n a

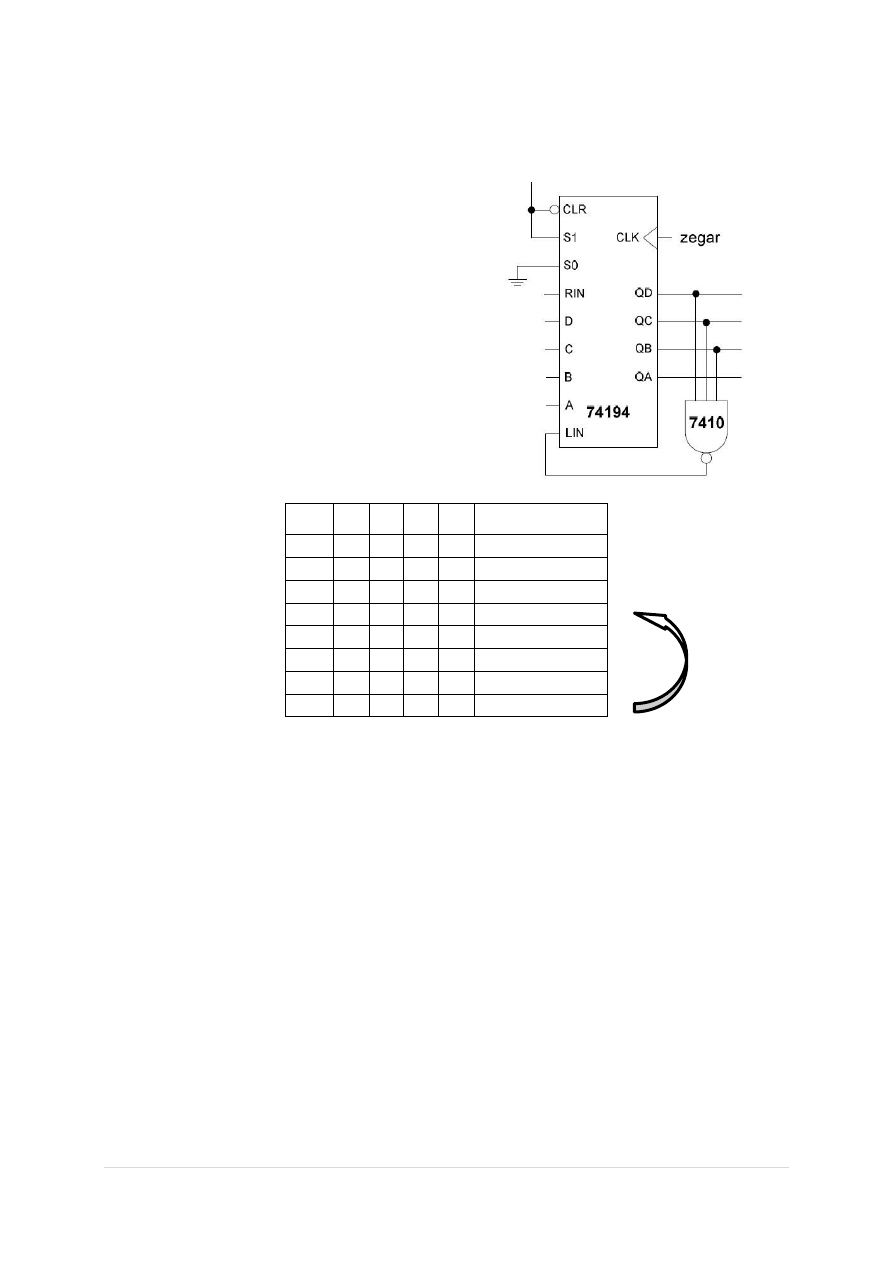

Układ B.

1. Wejście Clear (CLR) jest nieaktywne (aktywne stanem

wysokim).

2. Tryb działania: przesuwanie w lewo (S0- 0, S1- 1).

3. Wejście RIN- prawdopodobnie 1.

4. Wejście LIN:

̅̅̅̅̅̅̅̅̅̅̅

5. Wejścia A, B, C, D- prawdopodobnie 1.

Takie ustawienie układu spowoduje przesuwanie w lewo.

Wartości wejściowe ABCD nie zostaną skopiowane do

odpowiadającym im wejść Q

A

,

Q

B

,

Q

C

,

Q

D

. Ich domyślne

wartości to prawdopodobnie 1, 1, 1, 1. Dlatego przed

uruchomieniem, warto ustawić wejście CLR w stan niski,

aby zresetować wartości logiczne układu do niskich.

Takt Q

D

Q

C

Q

B

Q

A

̅̅̅̅̅̅̅̅̅̅̅

1

0

0

0

0

1

2

1

0

0

0

1

3

1

1

0

0

1

4

1

1

1

0

0

5

0

1

1

1

1

6

1

0

1

1

1

7

1

1

0

1

1

8

1

1

1

0

0

Cykl jest stały od czwartego taktu zegara i powtarza się co cztery takty.

7 |

S t r o n a

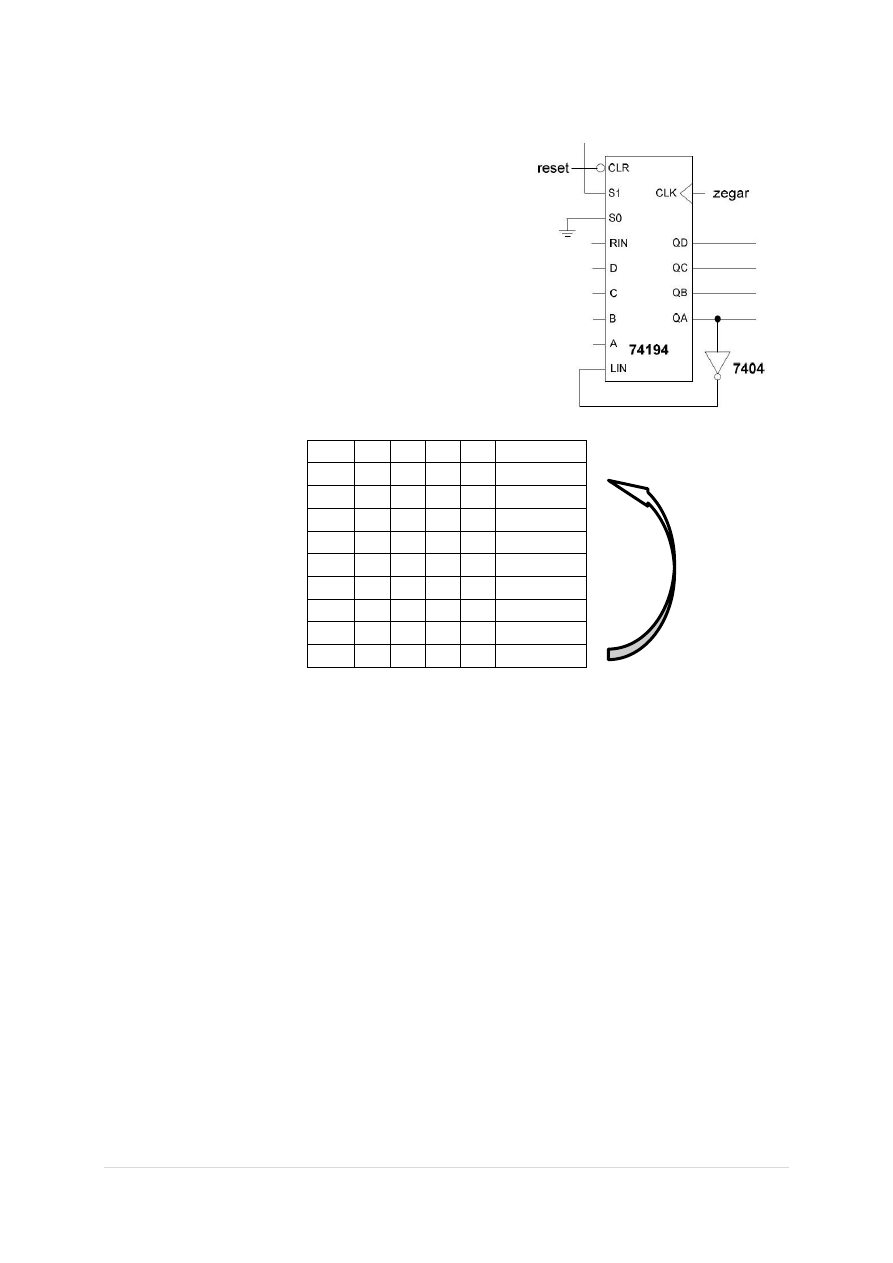

Układ C.

1. Do wejścia Clear (CLR) podłączony jest sygnał reset.

2. Tryb działania: przesuwanie w lewo (S0- 0, S1- 1).

3. Wejście RIN-0;

4. Wejście LIN:

̅̅̅̅

5. Wejścia A, B, C, D- 0.

Takie ustawienie powoduje przesuwanie w lewo. Aby mieć

pewność do obliczeń, najpierw należy ustawić sygnał na 0,

aby zresetować wartoścli logiczne układu do niskiego stanu

logicznego. Następnie, należy ustawić sygnał reset na 1.

Takt Q

D

Q

C

Q

B

Q

A

̅̅̅̅

1

0

0

0

0

1

2

1

0

0

0

1

3

1

1

0

0

1

4

1

1

1

0

1

5

1

1

1

1

0

6

0

1

1

1

0

7

0

0

1

1

0

8

0

0

0

1

0

9

0

0

0

0

1

Cykl jest stały i powtarza sie co osiem taktów zegara.

Wyszukiwarka

Podobne podstrony:

09 Architektura systemow rozproszonychid 8084 ppt

Wstęp do informatyki z architekturą systemów kompuerowych, Wstęp

Architekrura SystemAlw Lab5 (1) Nieznany

66 251103 projektant architekt systemow teleinformatycznych

Architekrura Systemów Lab3

tranzystory mosfet(1), Architektura systemów komputerowych, Sentenza, Sentenza

sciaga-skrocona, Informatyka Stosowana, Architektura systemów komputerowych, ASK

ukl 74xx, Informatyka PWr, Algorytmy i Struktury Danych, Architektura Systemów Komputerowych, Archit

Architektura systemów komputerowych przeliczanie systemów, Notatki

kol x86 IID GAK, studia wsiz, semestr 5, Architektora systemow lab

Architekrura Systemów Lab2

T 3 Architektura systemow komputerowych wytyczne

Architektura systemu

ASK, Informatyka Stosowana, Architektura systemów komputerowych, ASK

R5 Budowa mikroprocesora, Architektura Systemów Komputerowych

więcej podobnych podstron