Piotr Kawalec

Wykład VII - 1

Wykład VII

Podstawowe pojęcia języka

opisu i projektowania

sprzętu VHDL

Komputerowe projektowanie układów srt

Piotr Kawalec

Wykład VII - 2

Komputerowe projektowanie układów srt

Plan wykładu VII

Powstanie języka VHDL

Podstawowe pojęcia leksykalne

Literały pojedyncze i wielokrotne

Deklaracje obiektów

Wyrażenia

Zapis projektów w języku VHDL

Piotr Kawalec

Wykład VII - 3

Komputerowe projektowanie układów srt

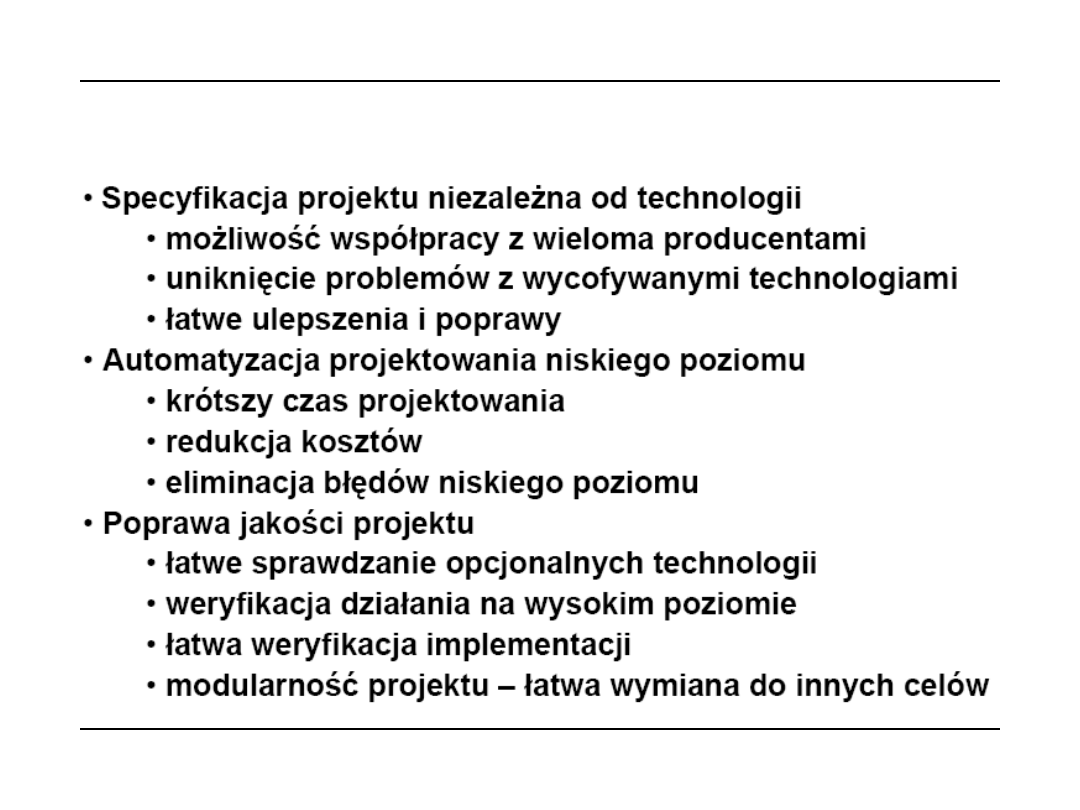

Zalety języka VHDL

Piotr Kawalec

Wykład VII - 4

Komputerowe projektowanie układów srt

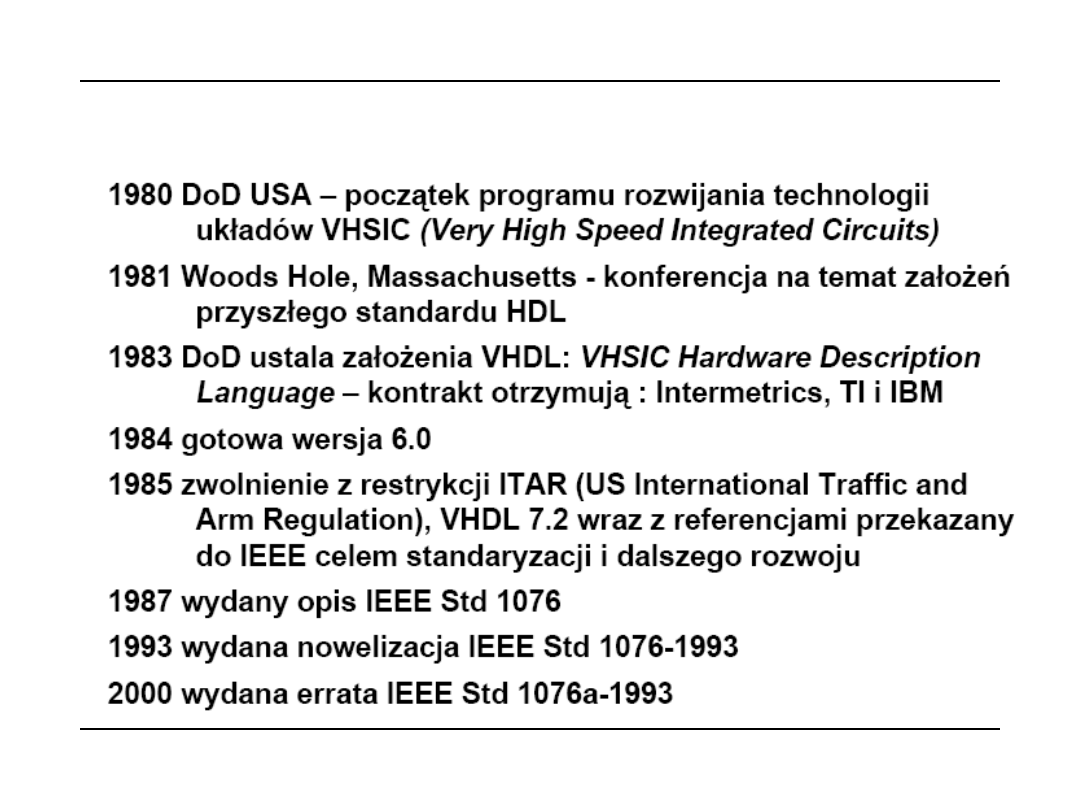

Kalendarz powstawania języka VHDL

Piotr Kawalec

Wykład VII - 5

Komputerowe projektowanie układów srt

Podstawowe pojęcia leksykalne

języka VHDL

literały -

napisy reprezentujące dane - z ich

sposobu zapisu wynikają ich

wszystkie

właściwości w tym ich

wartości

identyfikatory

(nazwy)

- ciągi liter i cyfr

rozpoczynające się od litery

deklaracje obiektów -

deklaracje stałych ,

zmiennych, sygnałów i plików

wyrażenia -

wzory ujmujące operatory i

argumenty

określające sposób

obliczenia lub

określenia

wartości

Piotr Kawalec

Wykład VII - 6

Komputerowe projektowanie układów srt

Literały pojedyncze (skalary)

character

- pojedynczy znak kodu ASCII

objęty

apostrofami np:

‘A’

lub

‘a’

bit

- reprezentuje wartość sygnałów

‘1’

lub

‘0’

std_logic

reprezentuje wartość sygnałów wg.

IEEE1164:

U

niezainicjalizowany

X

nieznany (forcing an unknown)

0

silne zero (forcing 0)

1

silne jeden (forcing 1)

Z

wysoka impedancja

W

słaby nieznany (weak unknown)

L

słabe zero (weak 0)

H

słabe jeden (weak 1)

-

nieistotny

Piotr Kawalec

Wykład VII - 7

Komputerowe projektowanie układów srt

Literały pojedyncze (skalary)

booloean

- reprezentuje dwie dyskretne

wartości:

TRUE FALSE

real

- reprezentuje wartość

zmiennoprzecinkową

typowo od -1.0E+38 do 1.0 E+38 z precyzją

sześciu

cyfr po przecinku

integer

- reprezentuje wartość całkowitą

typowo od -2 147 483 647 do + 2 147 483 647

time -

reprezentuje jedyną zdefiniowaną

wielkość

fizyczną –

to jest czas fs, ps, ns, us,

ms, sec, min, h

Piotr Kawalec

Wykład VII - 8

Komputerowe projektowanie układów srt

Literały wielokrotne (tablice)

string

- ciąg znaków kodu ASCII objęty

cudzysłowami

“Taki sobie

string” “xqre”

bit_vector

- ciąg wartości sygnałów w

zapisie

binarnym lub

heksadecymalnym objęty

cudzysłowami

”0001_1100”

”00FF”

std_logic_vector

- ciąg wartości sygnałów

std_logic

objęty

cudzysłowami

”1L0Z”

Piotr Kawalec

Wykład VII - 9

Komputerowe projektowanie układów srt

Deklaracje obiektów

Identyfikatory

muszą

zaczynać się od

litery

, a

dalej można dołączać

litery , cyfry

lub podkreślnik

(pojedynczy )

VHDL

nie rozróżnia

wielkości liter (not case

sensitive)

Identyfikatorami

nie mogą być

słowa

kluczowe

języka !!!

Piotr Kawalec

Wykład VII - 10

Komputerowe projektowanie układów srt

Deklaracje obiektów

Są to deklaracje stałych , zmiennych,

sygnałów

Ograniczenia zakresu sygnałów i zmiennych:

range

{low_val

to

high_val |

high_val

downto

low_val}

integer

range

1

to

10 ;

bit_vector (7

downto

0) ;

deklaracje stałych

pojedynczych

constant

name : TYPE := wyrażenie;

constant

Cycle : time := 50 ns;

Piotr Kawalec

Wykład VII - 11

Komputerowe projektowanie układów srt

Deklaracje obiektów

deklaracje stałych

tablice

constant

name : ARRAY_TYPE

[(ogr.indeksu)] := wyrażenie;

constant

SIX : bit_vector := “0110”;

constant

SIX : std_logic_vector (0 to

3):= “0110”;

Piotr Kawalec

Wykład VII - 12

Komputerowe projektowanie układów srt

Deklaracje obiektów

deklaracje sygnałów

pojedyncze

signal

name(s) : TYPE[ogr. zakresu]

[:= wyrażenie];

tablice

signal

name(s) : ARRAY_TYPE[ogr.

zakresu][:= wyrażenie];

Entity port

(name(s):DIR_TYP[ogr.

zakresu][:=

wyrażenie]);

Piotr Kawalec

Wykład VII - 13

Komputerowe projektowanie układów srt

Wyrażenia

W języku VHDL argumenty wyrażeń

muszą

być tego samego typu

Operatory wyrażeń

logiczne

and ornand nor xor not

relacji

= /= < <= > >=

połączenia &

arytmetyczne + - * / mod rem **

abs

VHDL 93 sll srl slasra rolror xnor

Piotr Kawalec

Wykład VII - 14

Komputerowe projektowanie układów srt

Priorytet operatorów

operatory różne

**

abs not

operatory multiplikatywne

* /

mod

rem

operatory znaku

+

-

operatory addytywne

+ - &

operatory przesunięć

sll srl sla sra

rol ror

operatory relacji

= \= < <=

> >=

operatory logiczne

and or nand nor

xor xnor

Piotr Kawalec

Wykład VII - 15

Komputerowe projektowanie układów srt

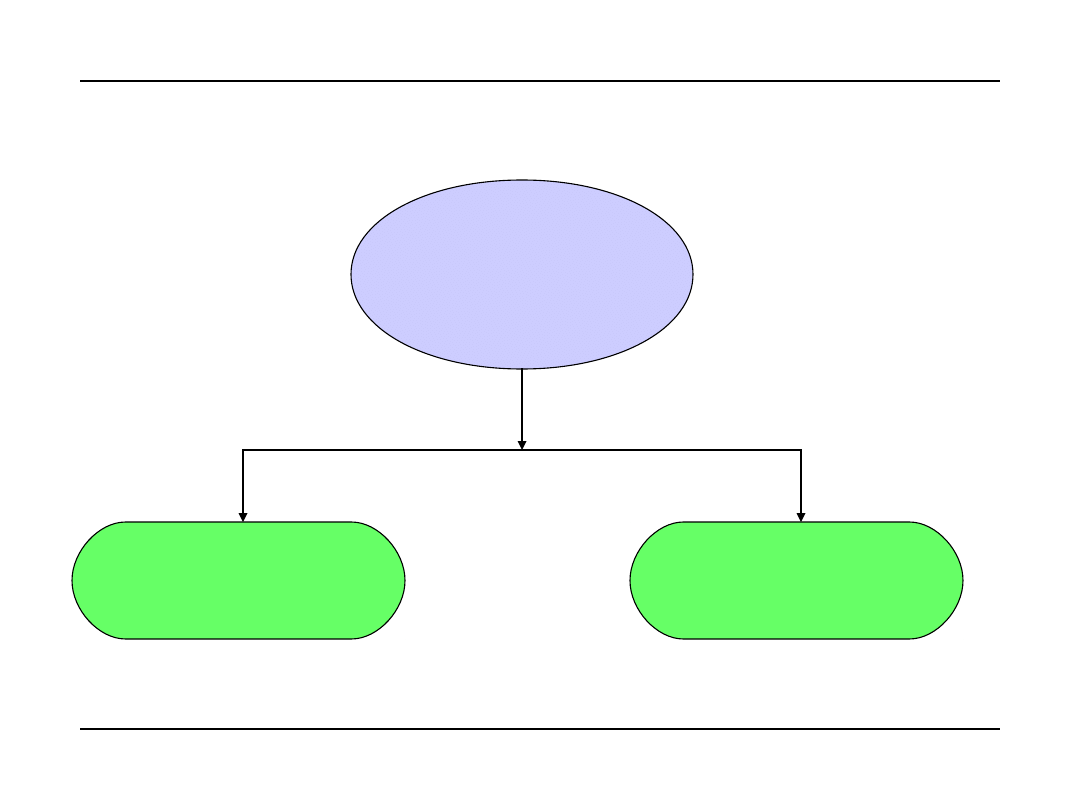

Zasady specyfikacji w języku VHDL

Projekt w języku VHDL powstaje w

dwóch

etapach:

deklaracja jednostki projektowej

(entity)

opis architektury projektu

(architecture)

Dla każdego projektu istniej tylko jedna

deklaracja jednostki projektowej,

natomiast

może istnieć kilka deklaracji architektur

połączonych z jedną jednostką

projektową

Piotr Kawalec

Wykład VII - 16

Komputerowe projektowanie układów srt

Struktura projektu w języku VHDL

Jednostka projektowa

ENTITY

Architektura projektu

ARCHITECTURE

1

Architektura projektu

ARCHITECTURE

n

• • •

Piotr Kawalec

Wykład VII - 17

Komputerowe projektowanie układów srt

Tworzenie jednostki projektowej

Deklaracja

entity

jest interfejsem

projektowanego

układu

deklaracja_jednostki_projektowej:=

entity

identyfikator

is

[

generic

(lista_parametrów); ]

[

port

(lista_portów); ]

[deklaracje {stałych, typów,

sygnałów }]

[

begin

instrukcje_współbieżne ]

end

[

entity

] [ nazwa jednostki ];

Piotr Kawalec

Wykład VII - 18

Komputerowe projektowanie układów srt

Tworzenie jednostki projektowej

Deklaracja

entity

zapewnia kompletną

informację

do połączenia układu ze światem

zewnętrznym dla

celów funkcjonalnego działania i testowania.

Słowo kluczowe

port

definiuje listę i typ

wyprowadzeń

Piotr Kawalec

Wykład VII - 19

Komputerowe projektowanie układów srt

Deklaracje wyprowadzeń

Rodzaje wyprowadzeń:

in

-

wejście;

out

-

wyjście;

inout

-

wyprowadzenie dwukierunkowe;

buffer

-

wyjście buforowe

Piotr Kawalec

Wykład VII - 20

Komputerowe projektowanie układów srt

Przykłady opisu jednostki

projektowej

deklaracja układu o 4 wejściach i jednym wyjściu

entity

bramki

is

port

(

A:

in

BIT_VECTOR (0

to

3);

B:

out

BIT

);

end

bramki;

Piotr Kawalec

Wykład VII - 21

Komputerowe projektowanie układów srt

Przykłady opisu jednostki

projektowej

deklaracja układu o dwóch wejściach

256 bitowych oraz jednym wyjściu

entity

KOMPARATOR

is

port

(

A:

in

BIT_VECTOR (255

downto

0);

B:

in

BIT_VECTOR (255

downto

0);

C:

out

BIT

);

end

KOMPARATOR;

Piotr Kawalec

Wykład VII - 22

Komputerowe projektowanie układów srt

Tworzenie architektury układu

ciało_architektoniczne : =

architecture

identyfikator

of

nazwa_jednostki_projektowej

is

część_deklaracyjna_ciała

[

begin

instrukcje_współbieżne ]

end

[

architecture

]

[ identyfikator ];

Piotr Kawalec

Wykład VII - 23

Modelowanie elementów dyskretnych

o charakterystyce przekaźnikowej

Elementy elektroniczne (czas propagacji t

p

~ ns)

symulacja funkcjonalna

symulacja czasowa

Elementy przekaźnikowe (czas propagacji ~

ms)

symulacja funkcjonalna

symulacja czasowa ???

x

1

x

n

y

1

y

m

Symulatory logiczne

Symulatory logiczne

Piotr Kawalec

Wykład VII - 24

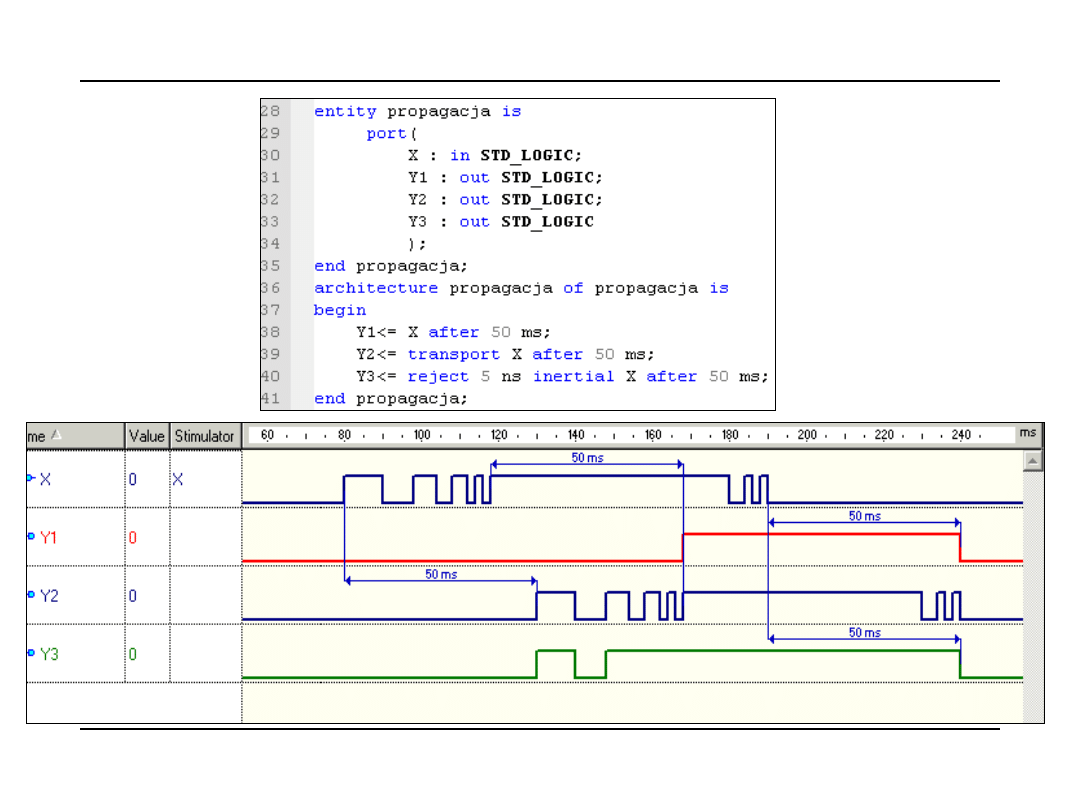

Określanie zależności czasowych w języku

VHDL

Y1<= X

after

t;

t,t1 [fs - hr]

Y2<=

transport

X

after

t;

t1 << t

Y3<=

reject

t1

inertial

X

after

t;

X

Y1

Y2

Y3

propagacja

Piotr Kawalec

Wykład VII - 25

Modelowanie zależności czasowych

w języku VHDL

Piotr Kawalec

Wykład VII - 26

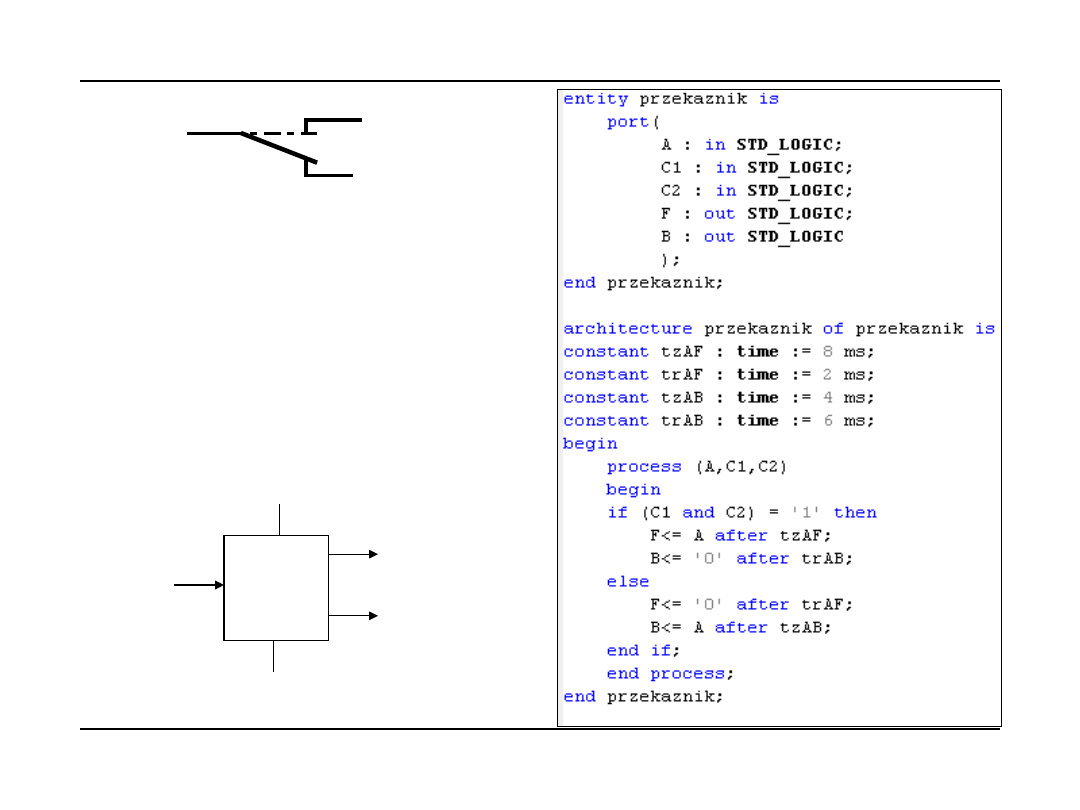

Specyfikacja działania przekaźnika w języku VHDL

С1

A

F

B

С2

A

F

B

Parametry czasowe przekaźnika

przy wzbudzaniu

trAB = 6 ms; tzAF = 8 ms

przy odwzbudzaniu

trAF = 2 ms; tzAB = 4 ms

Piotr Kawalec

Wykład VII - 27

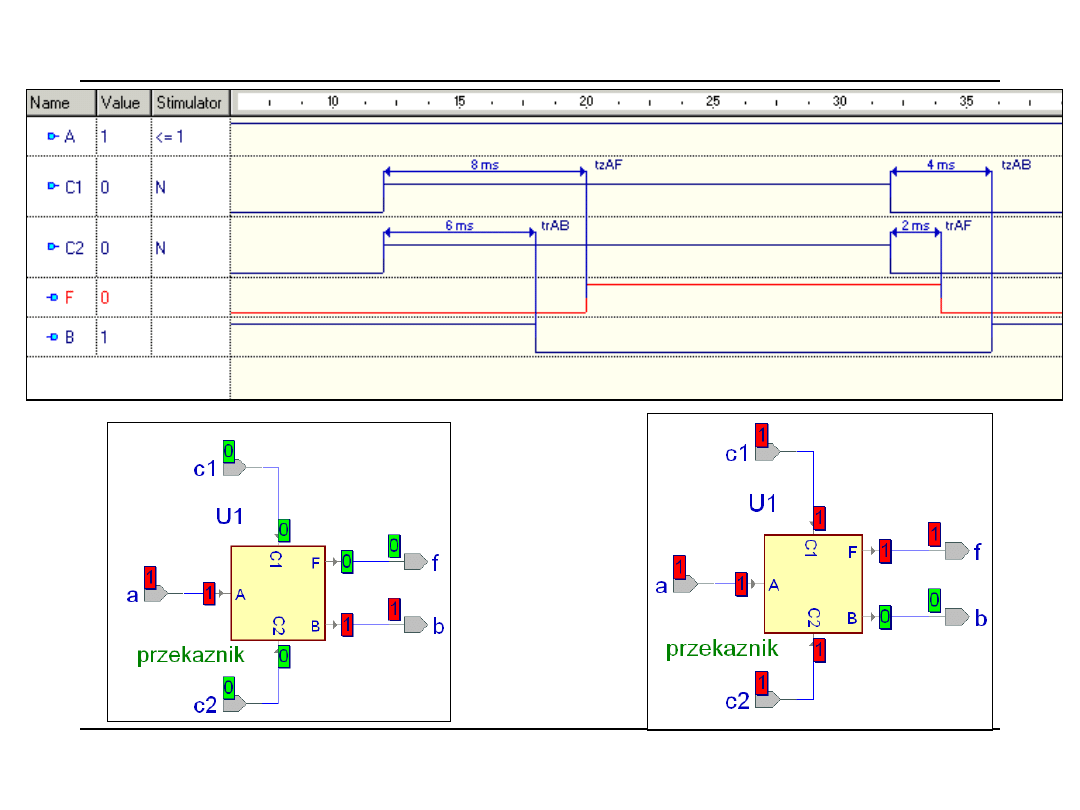

Modelowanie działania przekaźnika w języku VHDL

Piotr Kawalec

Wykład VII - 28

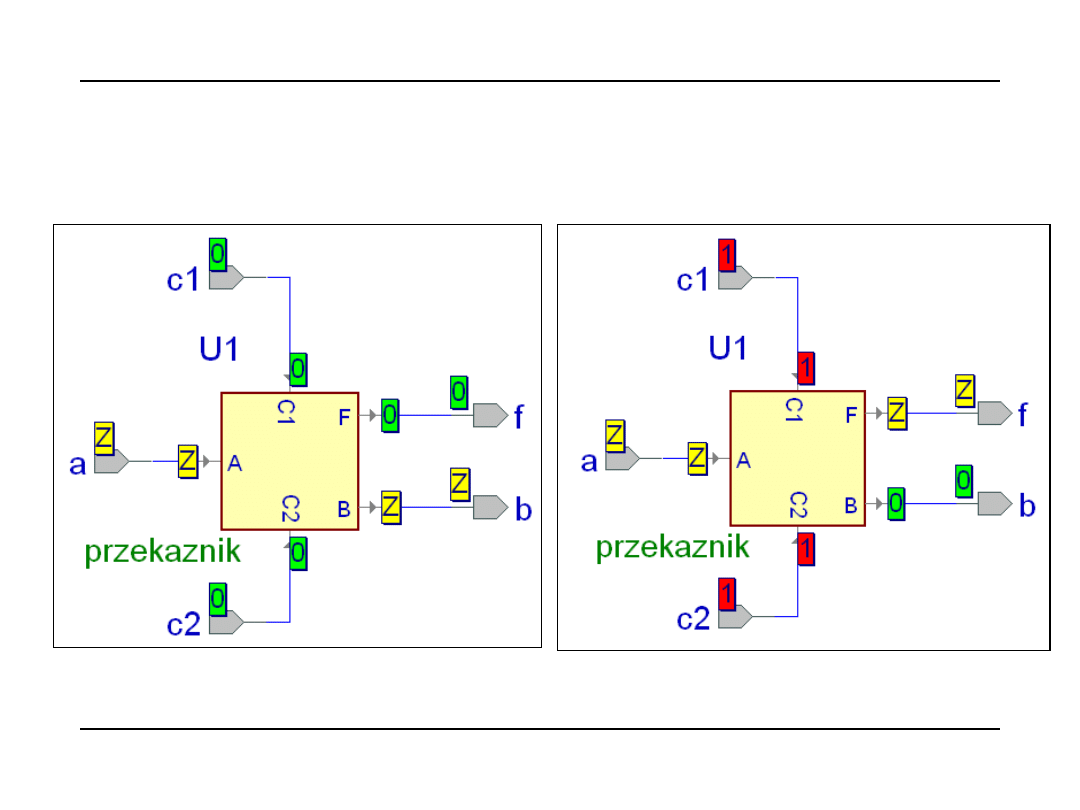

Modelowanie działania przekaźnika w języku VHDL

odwzorowanie przekazywania stanu wysokiej

impedancji

Piotr Kawalec

Wykład VII - 29

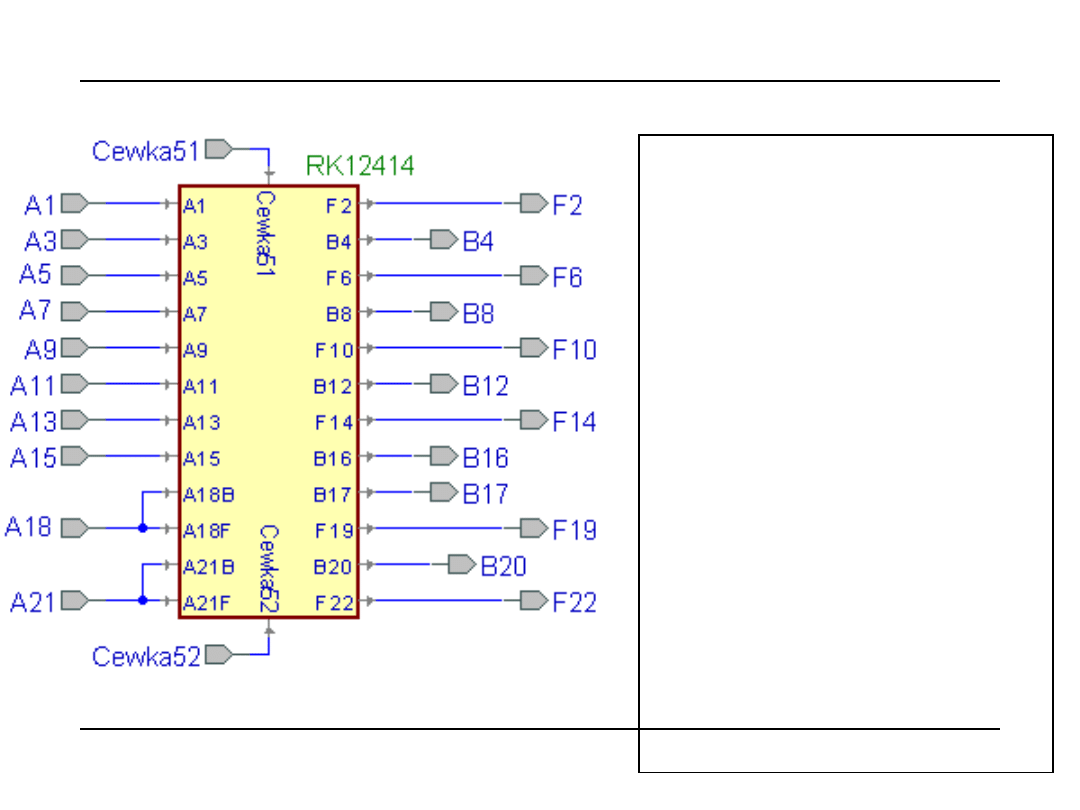

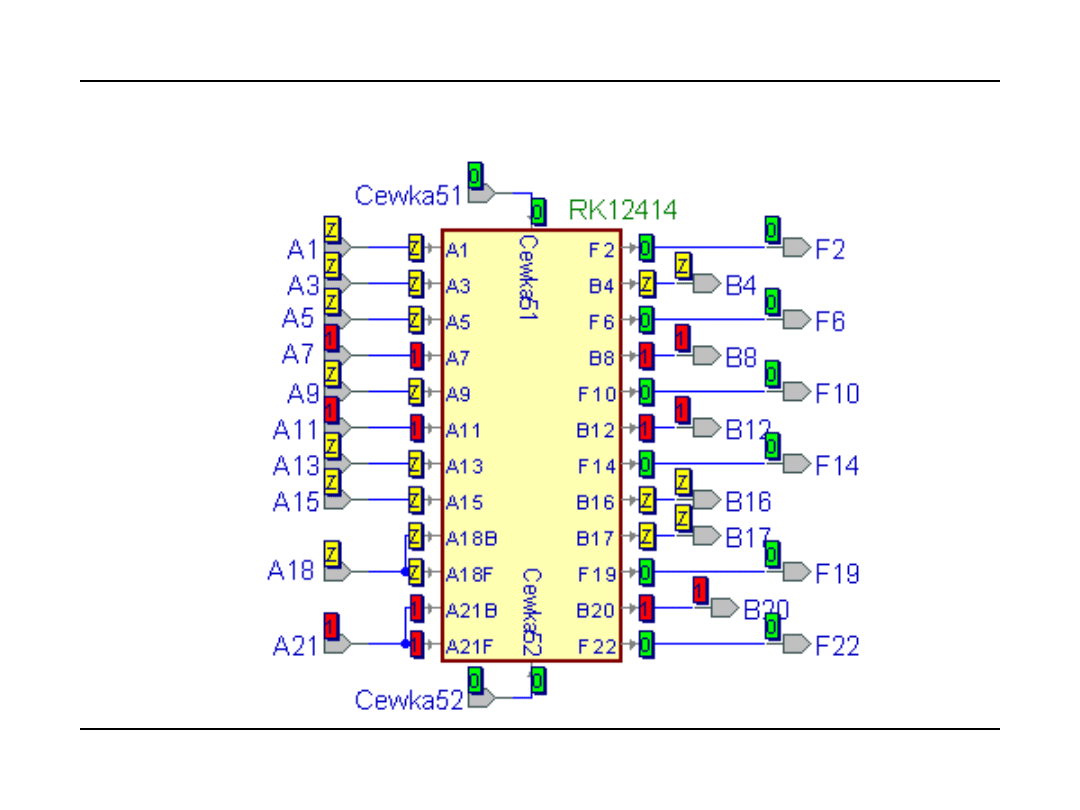

Modelowanie działania przekaźnika w

języku VHDL

Nominalne czasy

przekaźnika

RK12414

przy wzbudzaniu

trAB = 16 ms;

tzAF = 230 ms

przy

odwzbudzaniu

trAF = 12 ms;

tzAB = 170 ms

Piotr Kawalec

Wykład VII - 30

Моделирование работы реле RK12414

в языке VHDL

Piotr Kawalec

Wykład VII - 31

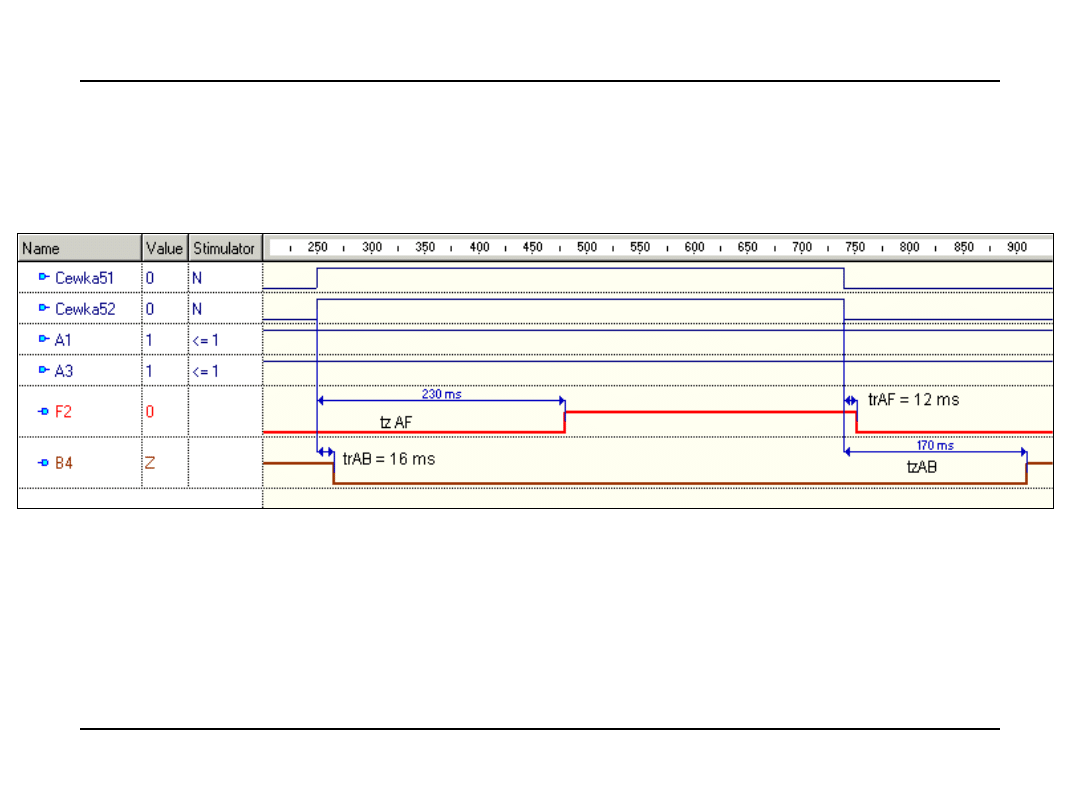

Badania symulacyjne modelu przekaźnika RK12414

wzbudzanie

przekaźnika

przekaźnik

odwzbudzony

Piotr Kawalec

Wykład VII - 32

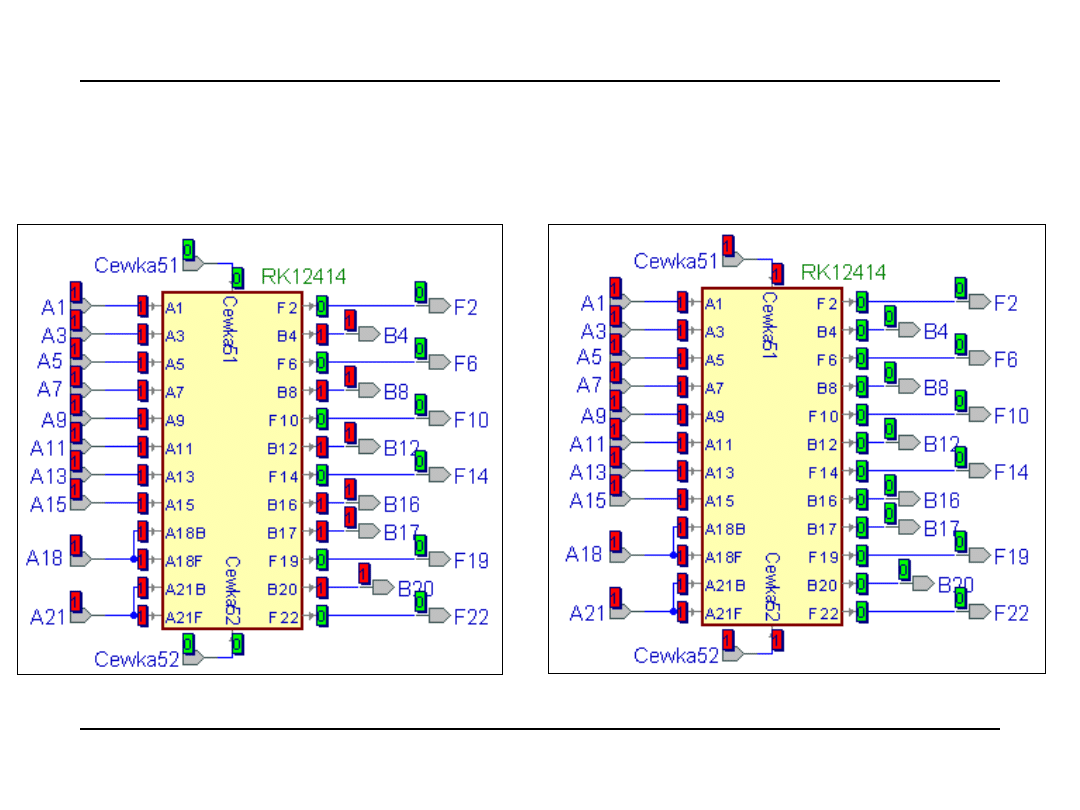

Badania symulacyjne modelu przekaźnika RK12414

odwzbudzani

e

przekaźnika

przekaźnik

wzbudzony

Piotr Kawalec

Wykład VII - 33

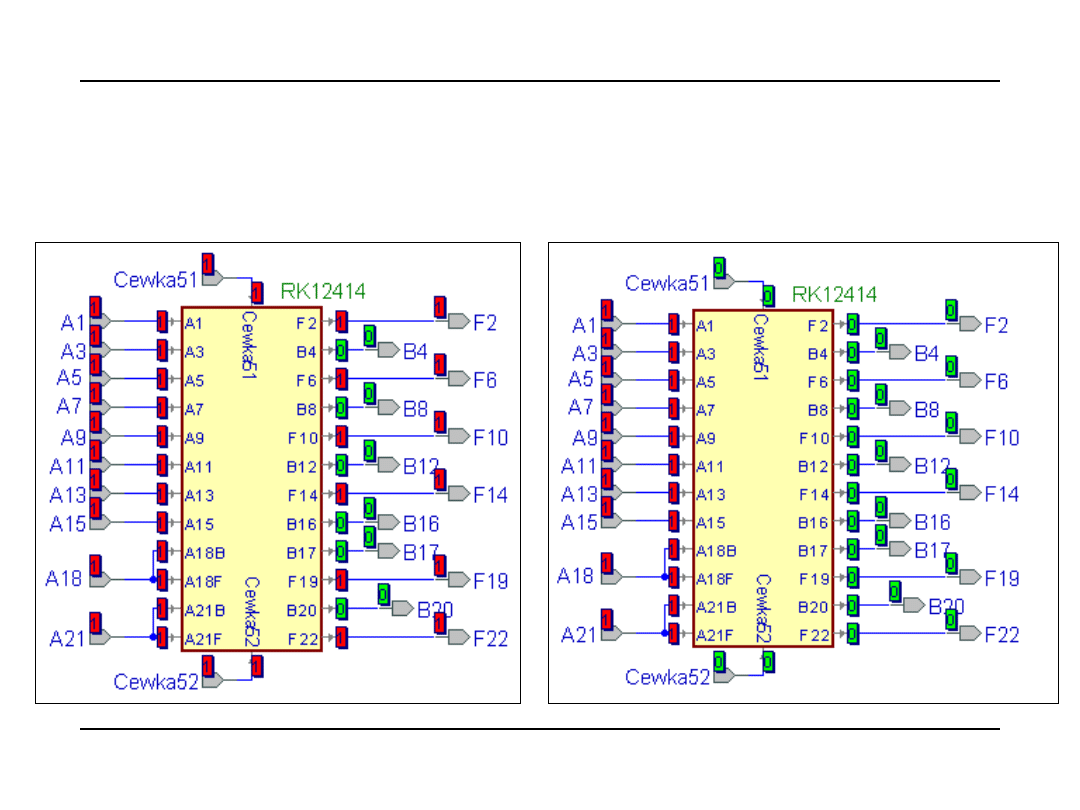

Badania symulacyjne modelu przekaźnika RK12414

odwzorowanie przekazywania stanu wysokiej

impedancji

Document Outline

- Slide 1

- Slide 2

- Slide 3

- Slide 4

- Slide 5

- Slide 6

- Slide 7

- Slide 8

- Slide 9

- Slide 10

- Slide 11

- Slide 12

- Slide 13

- Slide 14

- Slide 15

- Slide 16

- Slide 17

- Slide 18

- Slide 19

- Slide 20

- Slide 21

- Slide 22

- Slide 23

- Slide 24

- Slide 25

- Slide 26

- Slide 27

- Slide 28

- Slide 29

- Slide 30

- Slide 31

- Slide 32

- Slide 33

Wyszukiwarka

Podobne podstrony:

Język opisu sprzętu VHDL (K Kołek) vhdl ksiazka

Język opisu sprzętu VHDL

Jezyki opisu sprzetu VHDL

WYKŁAD VII

Wykład XI Metody opisu układów cyfrowych

Wykład VII hazard, realizacja na NAND i NOR

Wykład VII, politechnika infa 2 st, Projektowanie Systemów Informatycznych

wykład VII, LEŚNICTWO SGGW, MATERIAŁY LEŚNICTWO SGGW, Transport, TRANSPORT

Wykład VII, Studia Biologia, Mikrobiologia, wykłady z ogólnej

(Wykład VII)id 1478

Fakultet - Wykłąd VII, Fakultet seksuologia

WYKŁAD VII (5)

pytania treningowe, pytania tren wykład VII 2013

Wykład VII! 11 2012

Wykład VII mechanizacja antastic pl

więcej podobnych podstron