CS2204

CS2204

Digital Logic and State

Digital Logic and State

Machine Design

Machine Design

Introduction to

VHDL

Haldun Hadimioglu

Polytechnic University

Fall 2005

Fall 2005

CS2204 Digital Logic and State Machine

Design

Page 2

Outline

Outline

Introduction

Language Overview

VHDL Details

Future Directions

Conclusions

Acknowledgements

John Wakerly, Cisco Systems, Stanford University

Vijay Polavarapu, Polytechnic University

Fall 2005

CS2204 Digital Logic and State Machine

Design

Page 3

Introduction :

Introduction :

Background

Background

VHDL is a language to write programs to

describe digital circuits

Design, simulate and synthesize hardware

A VHDL program describes a digital circuit

Just like a schematic describes a digital circuit

Why VHDL, why not schematics ?

Real life circuits are too complex to be

designed by schematics.

Fall 2005

CS2204 Digital Logic and State Machine

Design

Page 4

Introduction :

Introduction :

Background

Background

VHDL was developed in the mid-1980s under

Department of Defense (DoD) sponsorship

Mandated for federally-sponsored VLSI designs

VHDL :

V

HSIC

H

ardware

D

escription

L

anguage

VHSIC :

V

ery

H

igh

S

peed

I

ntegrated

C

ircuit

VHSIC was a DoD research program to encourage

research on high-speed integrated circuit

technologies

Fall 2005

CS2204 Digital Logic and State Machine

Design

Page 5

Introduction :

Introduction :

Background

Background

Established as IEEE standard IEEE

1076 in 1987

Extended in IEEE standard IEEE1164

in1993

In 1996, IEEE 1076.3 became a VHDL

synthesis

standard

Today VHDL is widely used across the

industry

Fall 2005

CS2204 Digital Logic and State Machine

Design

Page 6

Introduction :

Introduction :

Background

Background

Another common HDL language :

Verilog HDL

VHDL has ADA flavor

ADA is a software language developed under

the DoD sponsorship in the 1980s

Verilog has C flavor

Knowing one language helps learn

another

Fall 2005

CS2204 Digital Logic and State Machine

Design

Page 7

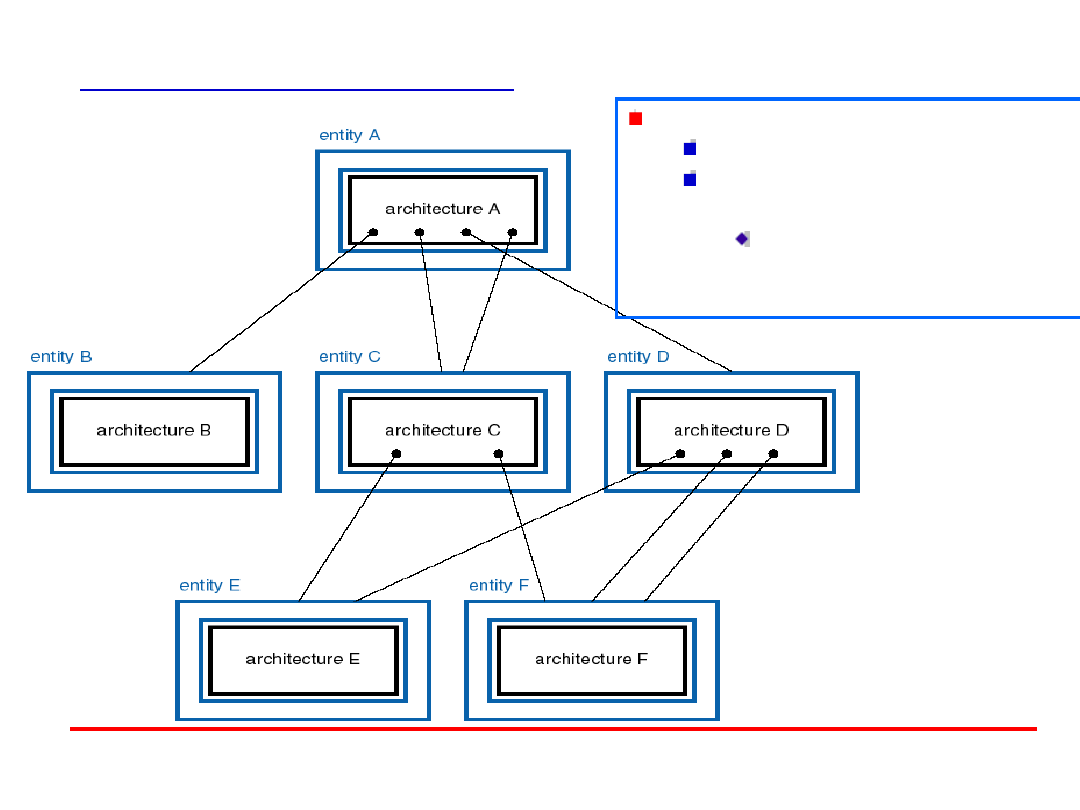

Introduction :

Introduction :

Motivation

Motivation

VHDL allows

Top-down

design (hierarchical designs)

for large projects

Designs described at various levels of

abstraction

More details at lower levels

Block-based design

Team-based

design

Core-based

design

Fall 2005

CS2204 Digital Logic and State Machine

Design

Page 8

Language Overview :

Language Overview :

Basics

Basics

In software, everything is sequential

The sequence of statements is significant,

since they are executed in that order

Java, C++, C, Ada, Pascal, Fortran,…

In hardware, events are concurrent

A software language cannot be used for

describing and simulating hardware.

Concurrent software languages cannot be used

either

But

, programs in C and other languages will be

converted to HDL programs in the future

Fall 2005

CS2204 Digital Logic and State Machine

Design

Page 9

Language Overview :

Language Overview :

Basics

Basics

VHDL is

STRONGLY

typed

VHDL is

not

case sensitive

“A” or “a” does not matter

A VHDL program describes a

system

A

system

is a digital system

A

system

is a collection of one or more

modules

(blocks)

A

module

consists of an

entity

and an

architecture

Fall 2005

CS2204 Digital Logic and State Machine

Design

Page 10

Language Overview :

Language Overview :

VHDL System

VHDL System

Description

Description

A VHDL program describes a

A VHDL program describes a system

system

A

A system

system

is a digital system

is a digital system

A

A system

system

is a collection of

is a collection of

one or more

one or more modules

modules

A

A module

module

consists of

consists of

an

an entity

entity

and

and

an

an architecture

architecture

Fall 2005

CS2204 Digital Logic and State Machine

Design

Page 11

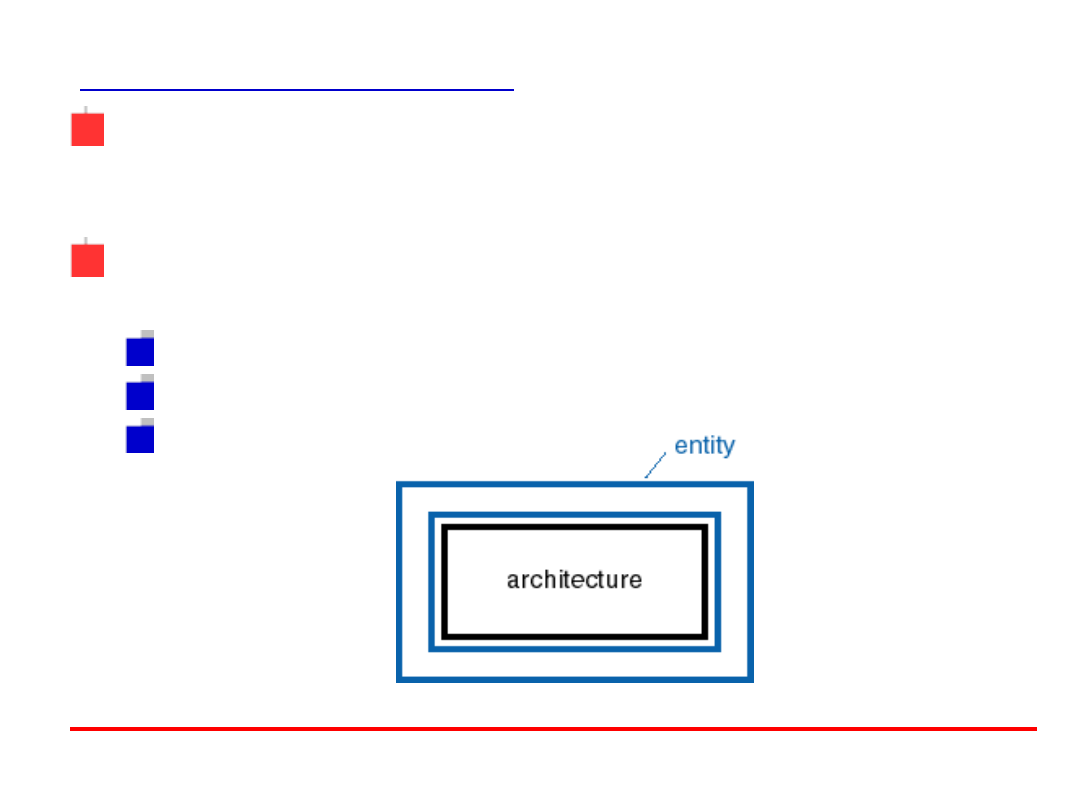

Language Overview :

Language Overview :

Module

Module

Entity

: shows inputs and outputs :

black box view

of module

Architecture

: internal description :

implementation

Structural

(very detailed)

Dataflow

(less detailed)

Behavioral

(least detailed)

Fall 2005

CS2204 Digital Logic and State Machine

Design

Page 12

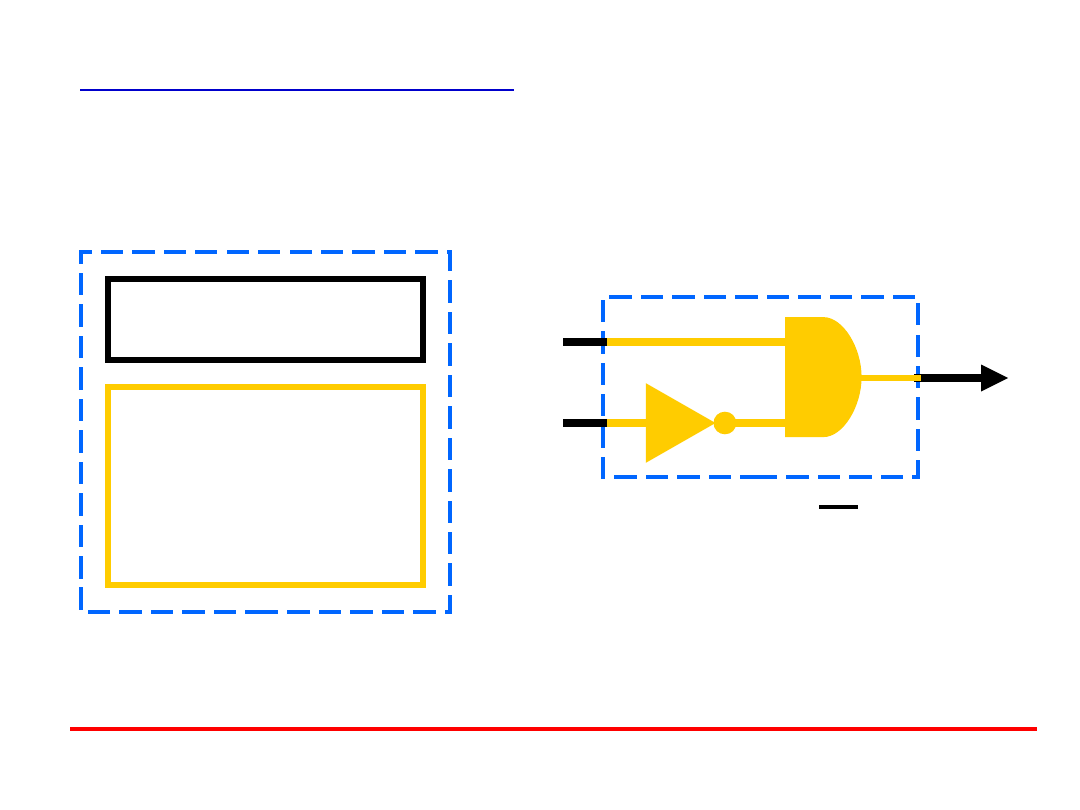

Language Overview :

Language Overview :

Module

Module

entity declaration

architecture definition

The VHDL program =

The text file (e.g., caralarm.vhd) :

belt

engine

AND

alarm

NOT

Car Alarm Schematic

alarm = engine belt

Fall 2005

CS2204 Digital Logic and State Machine

Design

Page 13

Language Overview :

Language Overview :

Xilinx VHDL Programs for Car Alarm

Xilinx VHDL Programs for Car Alarm

Circuit

Circuit

library

IEEE;

use

IEEE.std_logic_1164.

all

;

entity

caralarm

is

port

(

engine:

in

STD_LOGIC;

belt:

in

STD_LOGIC;

alarm:

out

STD_LOGIC

);

end

caralarm;

architecture

caralarm_dataflow

of

caralarm

is

begin

alarm <= engine

and

not

belt ;

end

caralarm_dataflow ;

library

IEEE;

use

IEEE.std_logic_1164.

all

;

entity

caralarm

is

port

(

engine:

in

STD_LOGIC;

belt:

in

STD_LOGIC;

alarm:

out

STD_LOGIC

);

end

caralarm;

architecture

caralarm_dataflow

of

caralarm

is

begin

alarm <= ‘1’

when

engine = ‘1’

and

belt

= ‘0’

else

‘0’ ;

end

caralarm_dataflow ;

Structural (very detailed)

Dataflow

(less detailed)

Behavioral (least detailed)

Fall 2005

CS2204 Digital Logic and State Machine

Design

Page 14

Language Overview :

Language Overview :

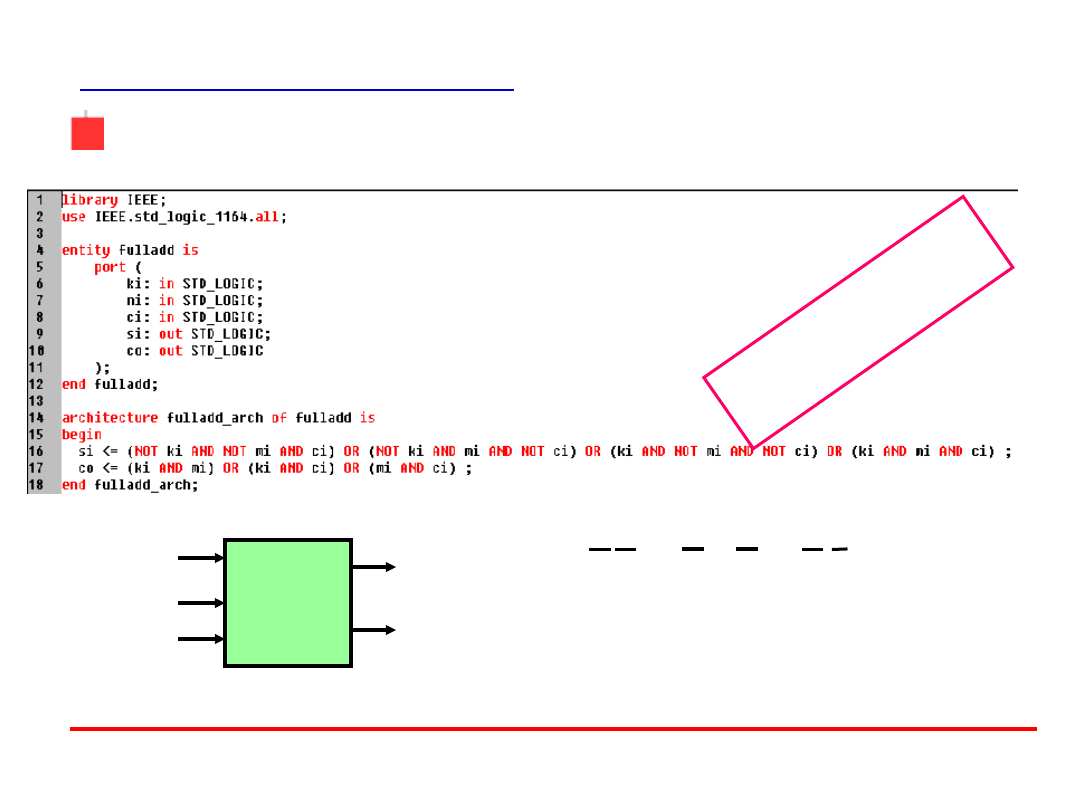

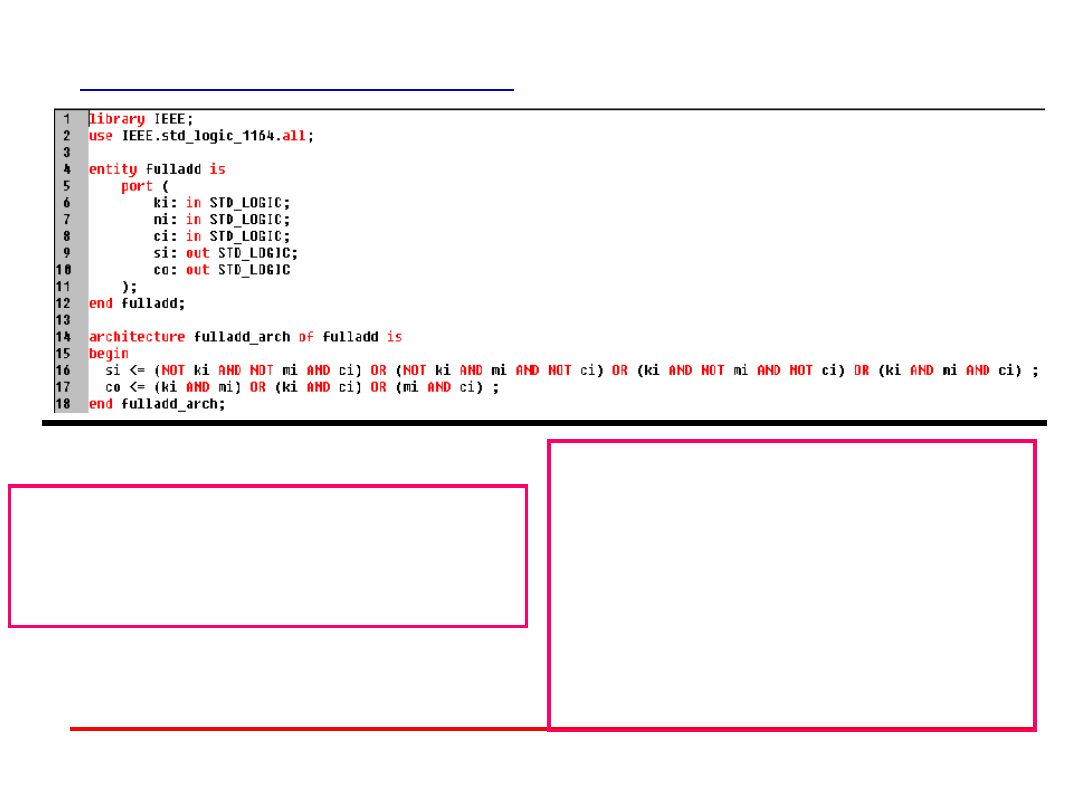

Full Adder VHDL

Full Adder VHDL

Program

Program

Data-flow description of the Full Adder

circuit :

Full

Adder

ki

mi

si

ci

co

si = ki mi ci + ki mi ci + ki mi ci + ki mi ci

co = ki mi + ki ci + mi ci

St

ru

ctu

ra

l (

ve

ry

de

tai

led

)

Da

ta

flo

w

(l

es

s d

eta

ile

d)

Be

ha

vio

ra

l (

lea

st

de

tai

led

)

Fall 2005

CS2204 Digital Logic and State Machine

Design

Page 15

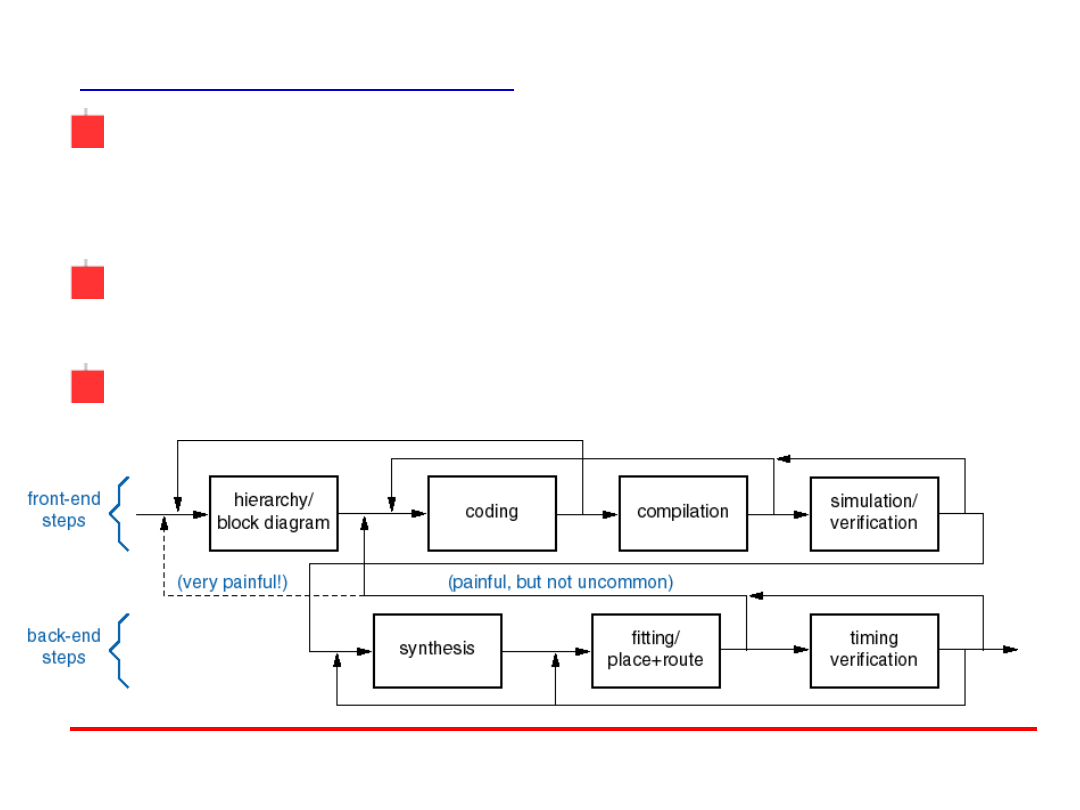

Language Overview :

Language Overview :

Design Flow

Design Flow

VHDL

compiler

analyzes VHDL code for

syntax errors and checks for compatibility with

other modules

Synthesizer

converts VHDL program to a

circuit with components

Place and route

fits the circuit to a die

Fall 2005

CS2204 Digital Logic and State Machine

Design

Page 16

VHDL Details :

VHDL Details :

Entity Syntax

Entity Syntax

The entity declares the ports

input and output signals

Syntax :

entity

entity-name

is

port

(signal-names :

mode

signal-

type ;

signal-names :

mode

signal-type ;

…..

signal-names :

mode

signal-type) ;

end

entity-name ;

entity

caralarm

is

port

(

engine:

in

STD_LOGIC;

belt:

in

STD_LOGIC;

alarm:

out

STD_LOGIC

);

end

caralarm

Fall 2005

CS2204 Digital Logic and State Machine

Design

Page 17

VHDL Details :

VHDL Details :

Architecture Syntax

Architecture Syntax

The architecture describes the internal

operations

By means of

concurrent statements

that use

Signals

inherited from the entity

Variables

used in functions, procedures and processes

architecture

architecture-name

of

entity-name

is

type declarations

signal declarations

constant declarations

function definitions

component declarations

begin

concurrent statement

….

concurrent statement

end

architecture-name ;

architecture

caralarm_dataflow

of

caralarm

is

begin

alarm <= engine

and

not

belt ;

end

caralarm_dataflow ;

Fall 2005

CS2204 Digital Logic and State Machine

Design

Page 18

VHDL Details :

VHDL Details :

Full Adder Example

Full Adder Example

architecture

architecture

architecture-name

architecture-name

of

of

entity-name

entity-name

is

is

type declarations

type declarations

signal declarations

signal declarations

constant declarations

constant declarations

function definitions

function definitions

component declarations

component declarations

begin

begin

concurrent statement

concurrent statement

…

…

.

.

concurrent statement

concurrent statement

end

end

architecture-name

architecture-name

;

;

entity

entity

entity-name

entity-name is

is

port

port

(signal-names :

(signal-names : mode

mode

signal-type ;

signal-type ;

signal-names :

signal-names : mode

mode

signal-type ;

signal-type ;

…

…

..

..

signal-names :

signal-names : mode

mode

signal-type) ;

signal-type) ;

end

end

entity-name ;

entity-name ;

Fall 2005

CS2204 Digital Logic and State Machine

Design

Page 19

VHDL Details :

VHDL Details :

Types

Types

Every

signal

,

variable

,

function parameter

,

and

function result

has a “

type

”.

Type

specifies the set or range of

values

an

object can take on

Type

also specifies the set of

operators

associated with it

A few

built-in types

, plus

user defined

types

.

In

assignment statements

,

comparisons

,

and

function calls

, types must match.

Fall 2005

CS2204 Digital Logic and State Machine

Design

Page 20

VHDL Details :

VHDL Details :

Types

Types

Predefined types

bit

bit_vector

boolean

character

integer

real

severity_level

string

time

User-defined types

Most commonly used one : enumerated types

Fall 2005

CS2204 Digital Logic and State Machine

Design

Page 21

VHDL Details :

VHDL Details :

Types

Types

Enumerated type is defined by listing its

values :

User defined enumerated type :

type

type-name

is

(value-list) ;

type

COLOR

is

(RED, ORANGE, YELLOW, BLUE, INDIGO, VIOLET) ;

Subtypes of a type allowed :

subtype

subtype-name

is

type-name start

to

end ;

subtype

LONGWAVE

is

color RED

to

YELLOW ;

subtype

subtype-name

is

type-name start

downto

end ;

Constants are allowed :

constant

constant-name : type-name := value ;

constant

BUS_SIZE : integer := 32 ;

Fall 2005

CS2204 Digital Logic and State Machine

Design

Page 22

VHDL Details :

VHDL Details :

Predefined Operators

Predefined Operators

Boolean operators

And

AND

Or

OR

Nand

NAND

nor

NOR

xor

Exclusive OR

xnor

Exclusive NOR

Not

Complement

Fall 2005

CS2204 Digital Logic and State Machine

Design

Page 23

VHDL Details :

VHDL Details :

Predefined Operators

Predefined Operators

Integer operations

+

addition

-

subtraction

*

multiplication

/

division

mod

modulo division

rem

modulo remainder

abs

absolute value

**

exponentiation

Fall 2005

CS2204 Digital Logic and State Machine

Design

Page 24

VHDL Details :

VHDL Details :

Library

Library

Library

keeps VHDL compiler generated

information about a project

The library maintains the state of the design

Intermediate files used in analysis, simulation

and synthesis

Previously analyzed entities and architectures

Entity and architecture definitions for different

modules can be in different files.

Compiler

maintains a “

work

” library and

keeps track of definitions using entity

and architecture names

Fall 2005

CS2204 Digital Logic and State Machine

Design

Page 25

VHDL Details :

VHDL Details :

Library

Library

Work library contains analysis results

No need to include in the VHDL

program

Library work ;

Resource library contains shared

definition

IEEE standard definitions library

must

be included

:

Library ieee ;

Fall 2005

CS2204 Digital Logic and State Machine

Design

Page 26

VHDL Details :

VHDL Details :

Package

Package

A package contains definitions of objects

Signal, type, constant, procedure,

component declarations

Standard logic defined by a “package” :

IEEE 1164 STD_LOGIC

Must be included in the program.

Keyword “

use

” needed to specify a package

Use

ieee.std.logic.1164.

all

Uses all definitions in the ieee library containing

package std.logic.1164

Fall 2005

CS2204 Digital Logic and State Machine

Design

Page 27

VHDL Details :

VHDL Details :

Standard Logic Types

Standard Logic Types

Commonly used IEEE-1164 types:

STD_LOGIC

(one bit)

STD_LOGIC_VECTOR(range)

(multi-bit vector)

INTEGER

(built-in integer type)

library

IEEE;

use

IEEE.std_logic_1164.

all

;

entity

caralarm

is

port

(

engine:

in

STD_LOGIC;

belt:

in

STD_LOGIC;

alarm:

out

STD_LOGIC);

end

caralarm;

architecture

caralarm_dataflow

of

caralarm

is

begin

alarm <= engine

and

not

belt ;

end

caralarm_dataflow ;

library

name

Compiler knows where

to find this (system-

dependent)

package

name

Use all

definition

s in

package

Fall 2005

CS2204 Digital Logic and State Machine

Design

Page 28

VHDL Details :

VHDL Details :

Design Hierarchy Levels

Design Hierarchy Levels

Structural

Define explicit

components

and the

connections between them.

Dataflow

Most are like

assigning

expressions to signals

Behavioral

Write an

algorithm

that describes the circuit’s

output

Structural (very detailed)

Dataflow (less detailed)

Behavioral (least detailed)

Fall 2005

CS2204 Digital Logic and State Machine

Design

Page 29

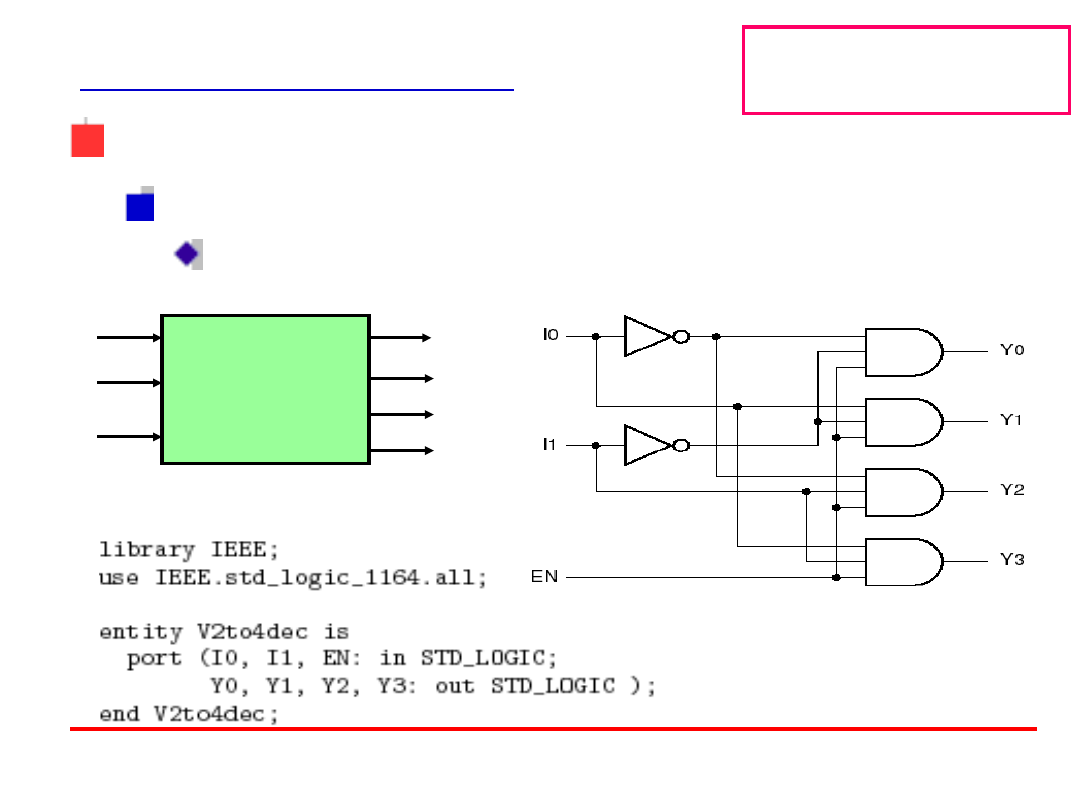

VHDL Details :

VHDL Details :

Structural Level

Structural Level

A structural description is just like the

schematic

Includes concurrent statements

A

component

statement is a concurrent statement

2-to4

DCD

V2to4dec

I1

I0

EN

Y0

Y1

Y2

Y3

Entity Part :

Structural

(very detailed)

Dataflow (less detailed)

Behavioral (least detailed)

Fall 2005

CS2204 Digital Logic and State Machine

Design

Page 30

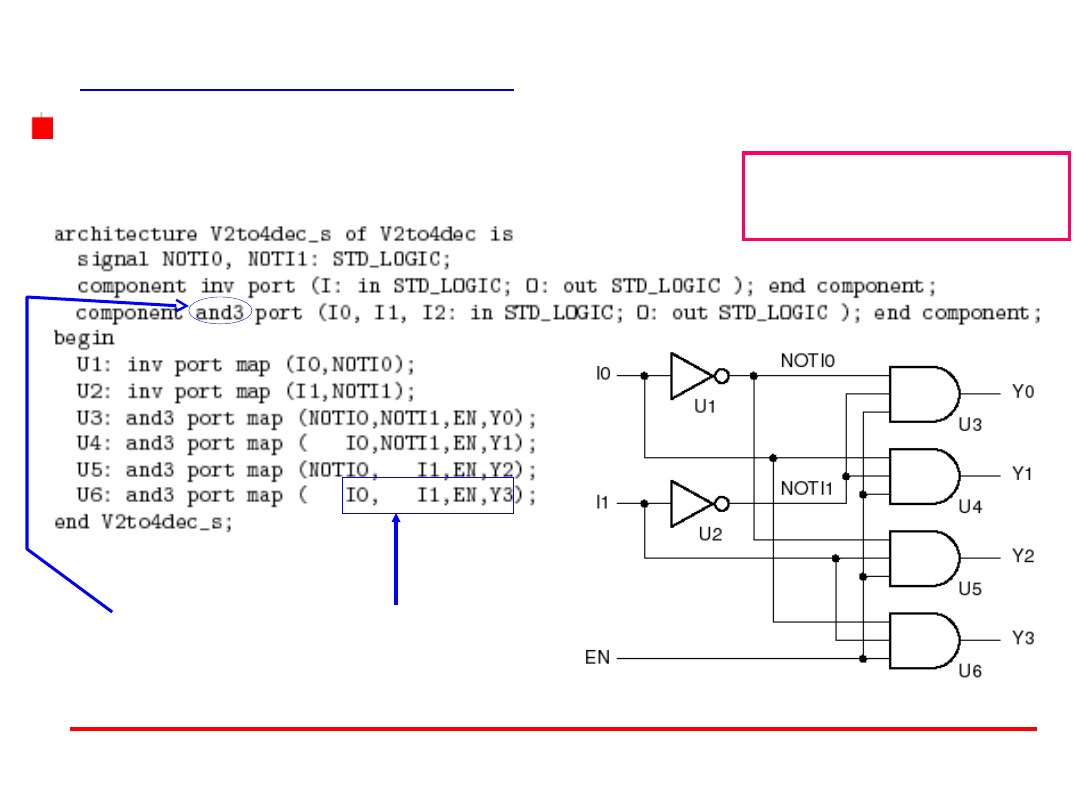

VHDL Details :

VHDL Details :

Structural Description of a 2-

Structural Description of a 2-

to4 Decoder

to4 Decoder

built-in library

components

positional

correspondence

with component definition

Architecture Part :

All Interconnections are precisely described

Structural

(very detailed)

Dataflow (less detailed)

Behavioral (least detailed)

Fall 2005

CS2204 Digital Logic and State Machine

Design

Page 31

VHDL Details :

VHDL Details :

Dataflow Level

Dataflow Level

Dataflow description

The detail is less compared with structural description

“Concurrent” statements include assignment and

select statements

Concurrency is needed to model the behavior of

parallel, interconnected hardware elements

Data dependencies described, not the components

and connections

Includes “

when-else

” and “

with-

select

” statements

Structural (very detailed)

Dataflow

(less detailed)

Behavioral (least detailed)

Fall 2005

CS2204 Digital Logic and State Machine

Design

Page 32

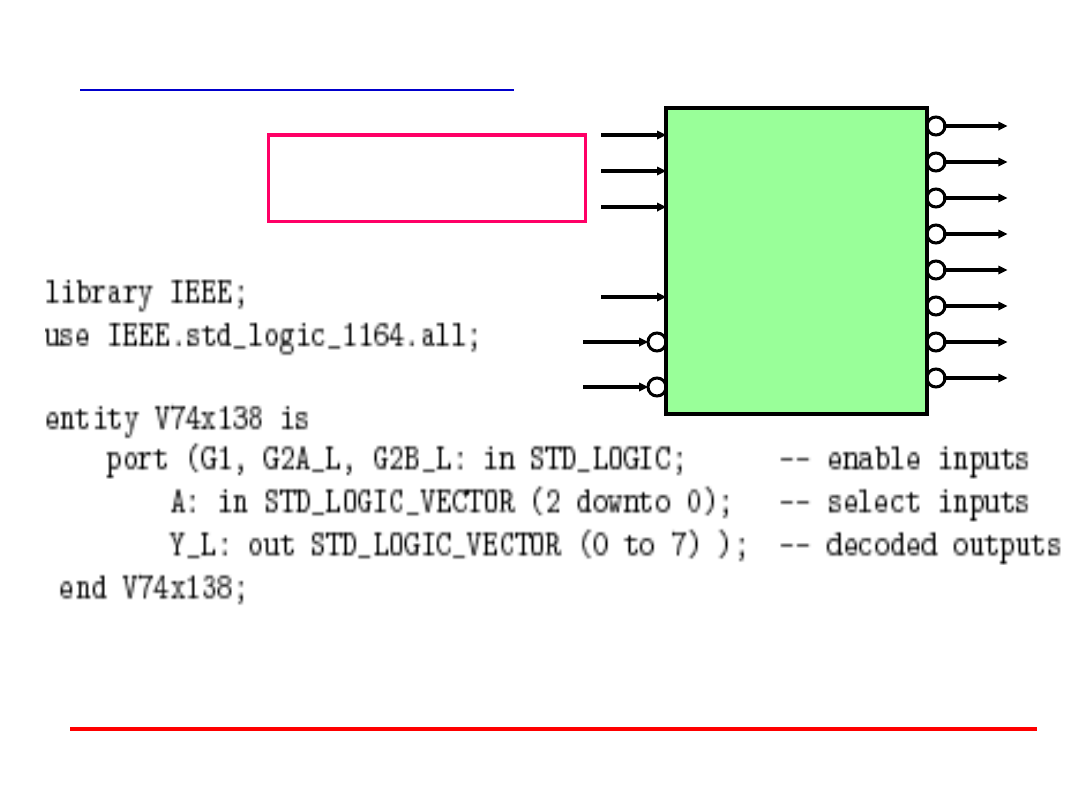

VHDL Details :

VHDL Details :

Dataflow Description of a 3-

Dataflow Description of a 3-

to-8 Decoder

to-8 Decoder

Entity Part :

3-to-8

DCD

A0

G1

Y_L0

A1

A2

Y_L1

Y_L2

Y_L3

Y_L4

Y_L5

Y_L6

Y_L7

G2A_L

G2B_L

V74x138

Structural (very detailed)

Dataflow

(less detailed)

Behavioral (least detailed)

Fall 2005

CS2204 Digital Logic and State Machine

Design

Page 33

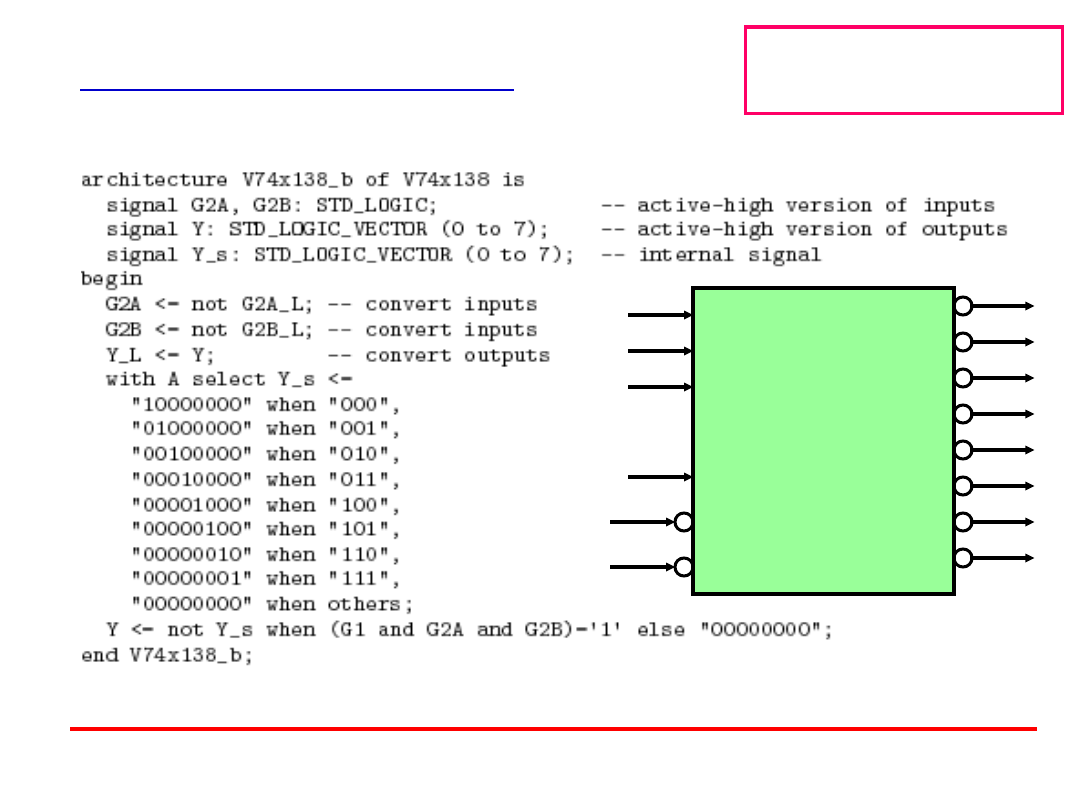

VHDL Details :

VHDL Details :

Dataflow Description of a 3-to-8

Dataflow Description of a 3-to-8

Decoder

Decoder

All

assignment statements operate concurrently : combinational

circuit

Architecture Part :

3-to-8

DCD

A0

G1

Y_L0

A1

A2

Y_L1

Y_L2

Y_L3

Y_L4

Y_L5

Y_L6

Y_L7

G2A_L

G2B_L

V74x138

Structural (very detailed)

Dataflow

(less detailed)

Behavioral (least detailed)

Fall 2005

CS2204 Digital Logic and State Machine

Design

Page 34

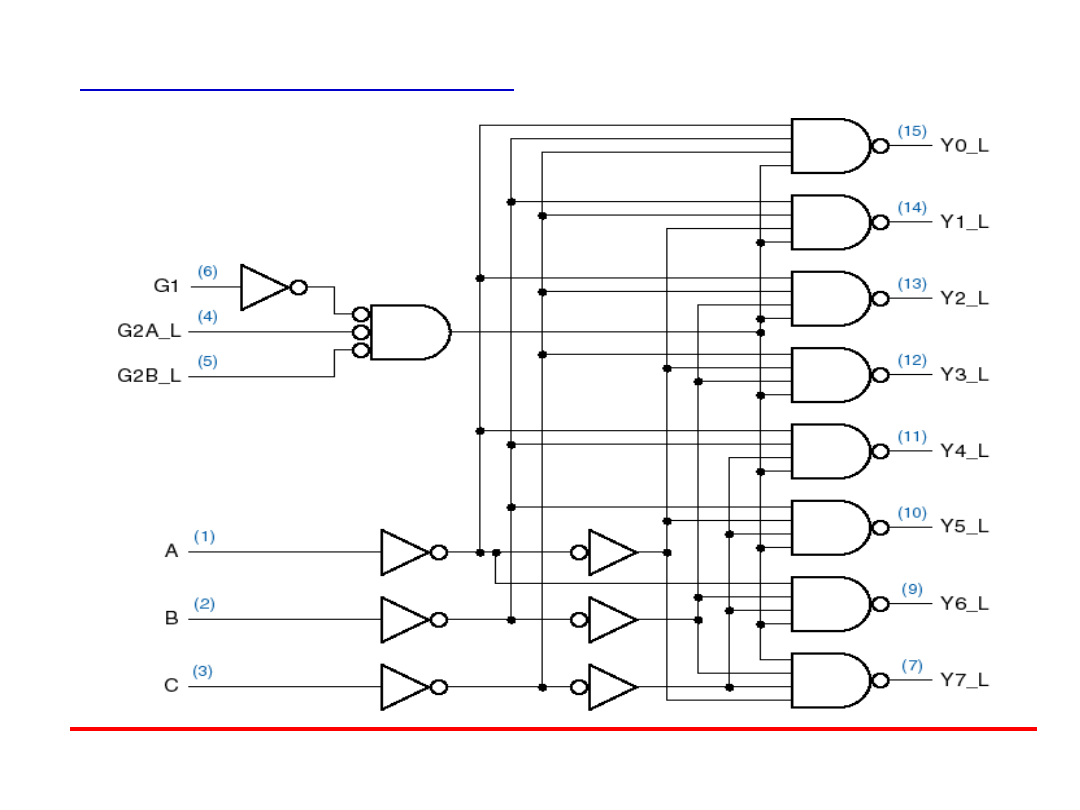

VHDL Details :

VHDL Details :

3-to-8 Decoder Translation to

3-to-8 Decoder Translation to

Hardware

Hardware

Fall 2005

CS2204 Digital Logic and State Machine

Design

Page 35

VHDL Details :

VHDL Details :

Behavioral Level

Behavioral Level

Behavioral description

May not be synthesizable or may lead to

a very large circuit

Primarily used for simulation

Normally uses VHDL “

processes

”

Each VHDL process executes in parallel with

other VHDL processes and concurrent

statements

But “

sequential

” statements can be used

within a process

Structural (very detailed)

Dataflow (less detailed)

Behavioral

(least detailed)

Fall 2005

CS2204 Digital Logic and State Machine

Design

Page 36

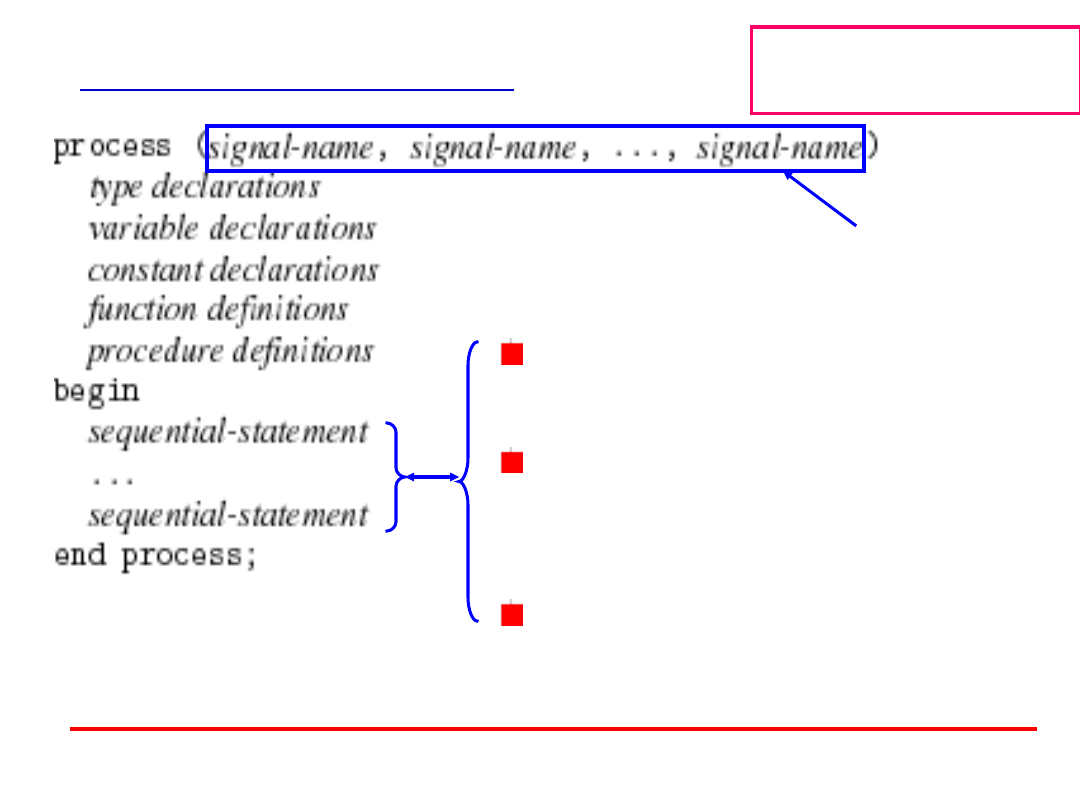

VHDL Details :

VHDL Details :

Process

Process

Sensitivity List

A sequence of “sequential

statements”.

Activated when any signal

in the “sensitivity list”

changes.

Primarily a simulation

concept, but can be

synthesized

Structural (very detailed)

Dataflow (less detailed)

Behavioral

(least detailed)

Fall 2005

CS2204 Digital Logic and State Machine

Design

Page 37

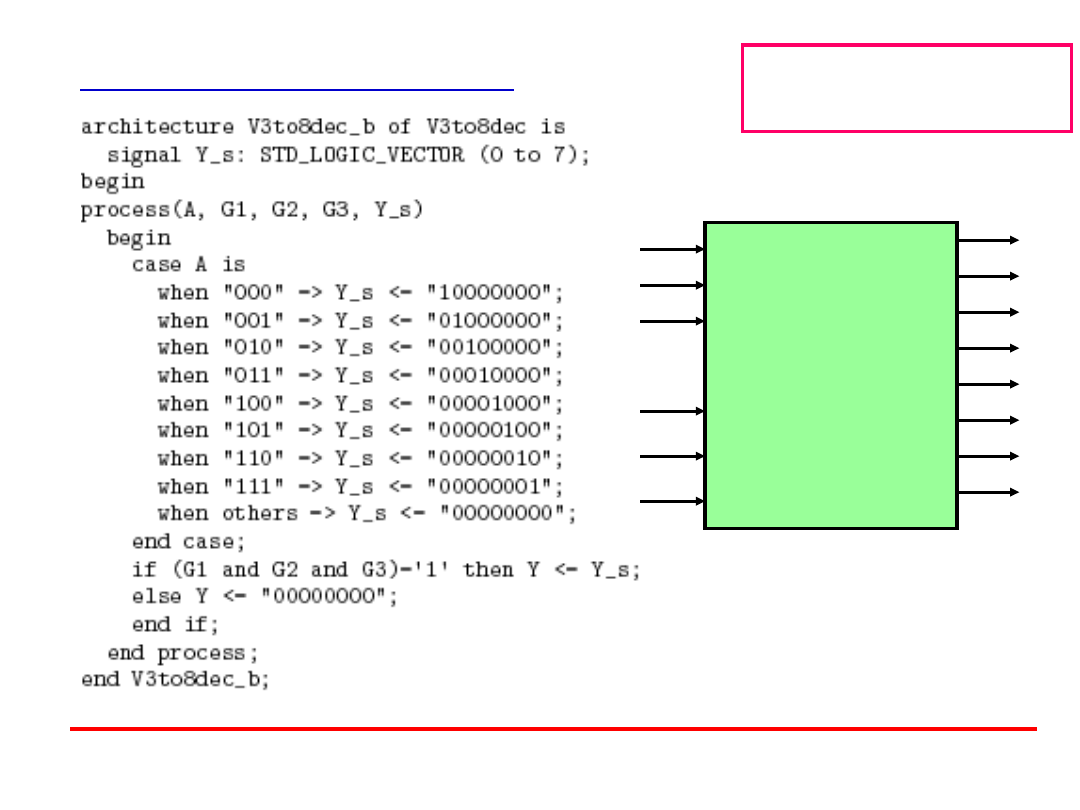

VHDL Details :

VHDL Details :

Behavioral Description of a 3-to-8

Behavioral Description of a 3-to-8

Decoder

Decoder

3-to-8

DCD

A0

G1

Y0

A1

A2

Y1

Y2

Y3

Y4

Y5

Y6

Y7

G2

G3

V3to8dec

Structural (very detailed)

Dataflow (less detailed)

Behavioral

(least detailed)

Fall 2005

CS2204 Digital Logic and State Machine

Design

Page 38

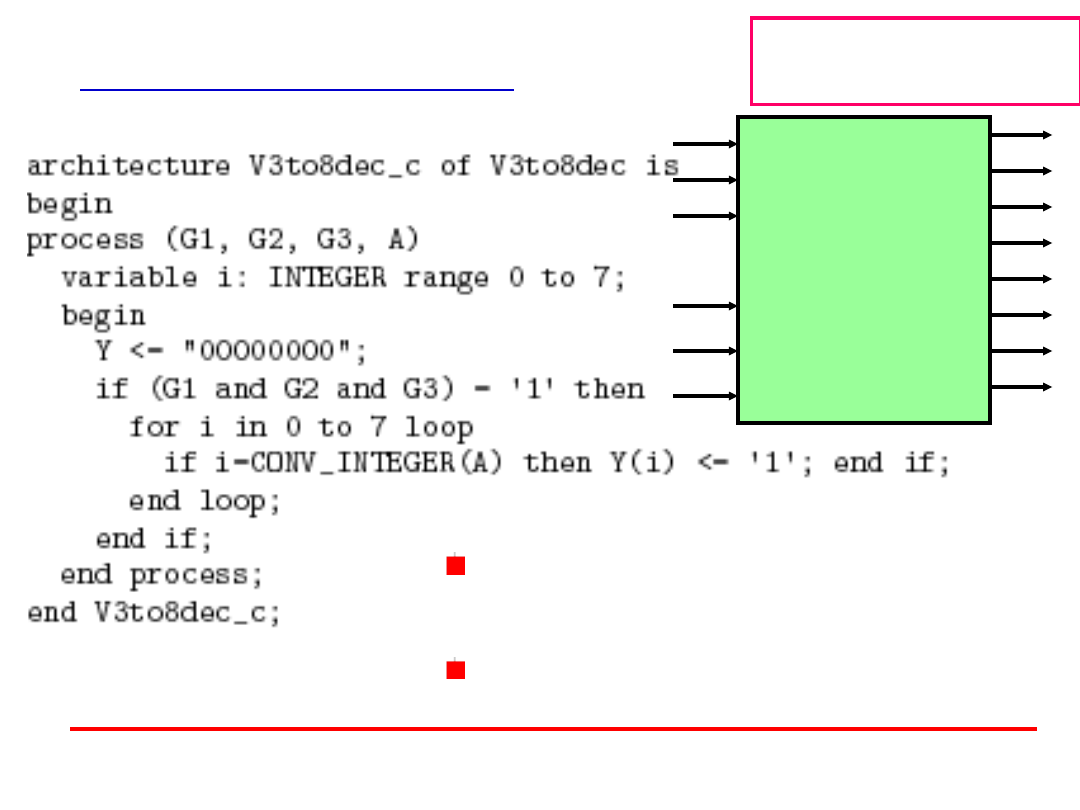

VHDL Details :

VHDL Details :

Another Behavioral Description of a 3-to-8 Decoder

Another Behavioral Description of a 3-to-8 Decoder

May not be synthesizable, or may

have a slow or inefficient realization.

But just fine for simulation and

verification.

3-to-8

DCD

A0

G1

Y0

A1

A2

Y1

Y2

Y3

Y4

Y5

Y6

Y7

G2

G3

V3to8dec

Structural (very detailed)

Dataflow (less detailed)

Behavioral

(least detailed)

Fall 2005

CS2204 Digital Logic and State Machine

Design

Page 39

VHDL Details :

VHDL Details :

Is it always VHDL-only

Is it always VHDL-only

System Description ?

System Description ?

One can mix schematic and VHDL

Xilinx example :

1.

Start a schematic project

2.

Write a VHDL program

3.

Convert the VHDL program to a Xilinx

macro

(Custom Design Block, CDB)

4.

The macro is appended to the

component library list

5.

Place the CDB in the schematic just like

any other Xilinx block

Fall 2005

CS2204 Digital Logic and State Machine

Design

Page 40

Future Directions

Future Directions

Digital Logic evolution will continue :

Faster

,

cheaper

,

smaller

,

lighter

,

less

power consuming

,

higher reliability

digital

products

Due to converging research in various areas :

Mathematics

Computer Science

Computer Engineering

Electrical Engineering

Mechanical Engineering

Physics

Chemistry

Material Science

Biology ?

The

Biochip

Group at

Mesa+,

University of Twente,

Holland

Fall 2005

CS2204 Digital Logic and State Machine

Design

Page 41

Future Directions

Future Directions

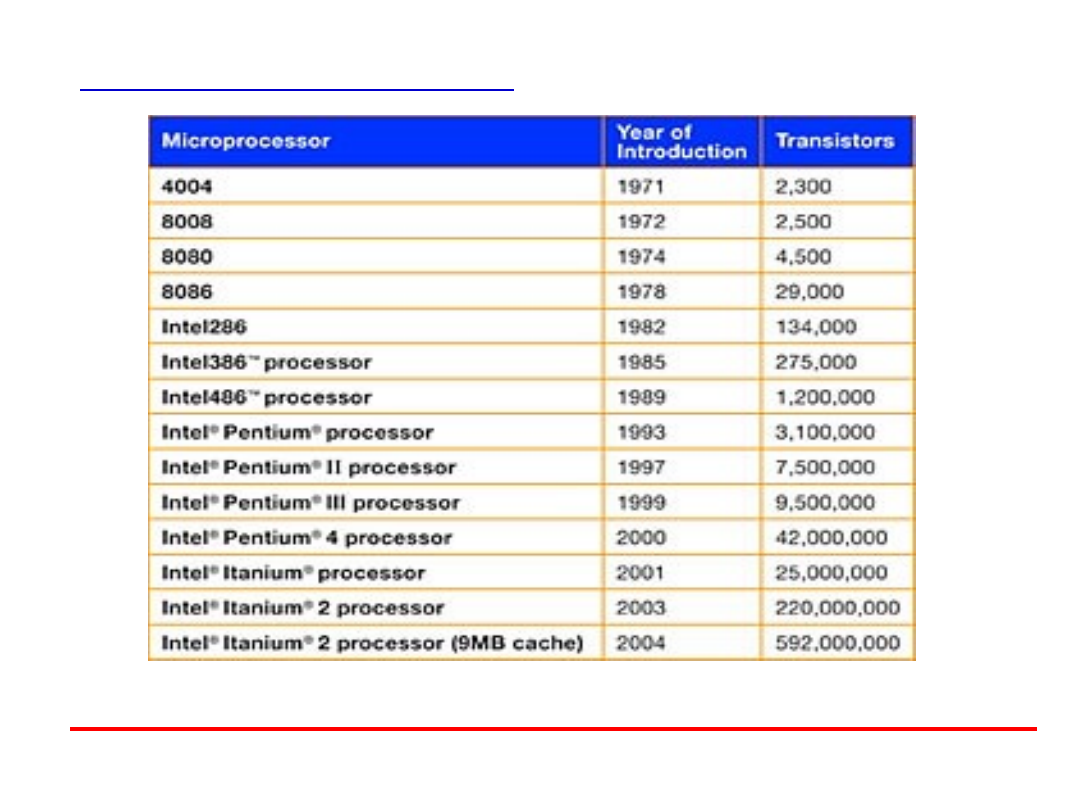

Intel Dual-core Itanium ® processor 2006 1,720,000,000

Fall 2005

CS2204 Digital Logic and State Machine

Design

Page 42

Future Directions

Future Directions

SEMATECH

: consortium of semiconductor

manufacturers from America, Asia and Europe.

SEMATECH predictions for year

2018

(from its

updated 2004 International Technology

Roadmap for Semiconductors, ITRS, study) :

Clock speed :

52 GHz

Number of transistors on a microprocessor

chip :

14 Billion

128Gbit

DRAM chips

http://www.sematech.org

Fall 2005

CS2204 Digital Logic and State Machine

Design

Page 43

Future Directions

Future Directions

Microelecromechanical systems,

MEMS

Microcameras, microsensors,

micromirrors, micromotors,…with

computing elements

Bio MEMS

Nanotechnology

NEMS

Bio NEMS

Nanocomputing

IBM Blue Gene/L molecular dynamics

demo

Fall 2005

CS2204 Digital Logic and State Machine

Design

Page 44

Future Directions

Future Directions

Hardware-software boundary is

being

blurred

Reconfigurable

computing

Program = hardware + software

Many interconnected varying-size computers

using each other’s results

Ubiquitous computing with little human

intervention

Macro scale applications : internet

Medium scale : supercomputer to hand-held

Micro-/Nano-scale : Micro/Nanoelectromechanical

Systems (

MEMS/NEMS

) with computing elements

Fall 2005

CS2204 Digital Logic and State Machine

Design

Page 45

Future Directions

Future Directions

Long term predictions by

individuals

If

power and fault-tolerance issues

are handled well

Brain download’s possible by 2050

, Ian

Pearson, Head of British Telecom’s

futurology unit, CNN.com, 5/23/2005

By 2019 a $1000 computer will match

the processing power of the human

brain

, Raymond Kurzweil,

KurzweilAI.net, 9/1/1999

Fall 2005

CS2204 Digital Logic and State Machine

Design

Page 46

Conclusions

Conclusions

VHDL simplifies design of complex digital

circuits

VHDL allows core-based, top-down, team-

based design

VHDL and other HDLs will be used in

foreseeable future as chip densities increase

Sophomores will learn more VHDL in near future

High-level language programs will be

converted hardware

Document Outline

- Slide 1

- Outline

- Introduction : Background

- Slide 4

- Slide 5

- Slide 6

- Introduction : Motivation

- Language Overview : Basics

- Slide 9

- Language Overview : VHDL System Description

- Language Overview : Module

- Language Overview : Module

- Language Overview : Xilinx VHDL Programs for Car Alarm Circuit

- Language Overview : Full Adder VHDL Program

- Language Overview : Design Flow

- VHDL Details : Entity Syntax

- VHDL Details : Architecture Syntax

- VHDL Details : Full Adder Example

- VHDL Details : Types

- Slide 20

- Slide 21

- VHDL Details : Predefined Operators

- Slide 23

- VHDL Details : Library

- Slide 25

- VHDL Details : Package

- VHDL Details : Standard Logic Types

- VHDL Details : Design Hierarchy Levels

- VHDL Details : Structural Level

- VHDL Details : Structural Description of a 2-to4 Decoder

- VHDL Details : Dataflow Level

- VHDL Details : Dataflow Description of a 3-to-8 Decoder

- Slide 33

- VHDL Details : 3-to-8 Decoder Translation to Hardware

- VHDL Details : Behavioral Level

- VHDL Details : Process

- VHDL Details : Behavioral Description of a 3-to-8 Decoder

- VHDL Details : Another Behavioral Description of a 3-to-8 Decoder

- VHDL Details : Is it always VHDL-only System Description ?

- Future Directions

- Slide 41

- Slide 42

- Slide 43

- Slide 44

- Slide 45

- Conclusions

Wyszukiwarka

Podobne podstrony:

268257 Introduction to Computer Systems Worksheet 1 Answer sheet Unit 2

Introduction To Scholastic Ontology

Evans L C Introduction To Stochastic Differential Equations

Zizek, Slavoj Looking Awry An Introduction to Jacques Lacan through Popular Culture

Introduction to Lagrangian and Hamiltonian Mechanics BRIZARD, A J

Introduction to Lean for Poland

An Introduction to the Kabalah

Introduction to Apoptosis

Syzmanek, Introduction to Morphological Analysis

Brief Introduction to Hatha Yoga

0 Introduction to?onomy

Introduction to politics szklarski pytania

INTRODUCTION TO VERBS

An Introduction to USA 6 ?ucation

introdution to capabilities classes 5WEH7OVOF6IJEZ7SO6GMF63NSJPWSXDLGIJQTMA

An Introduction to Database Systems, 8th Edition, C J Date

Introduction to the MOSFET and MOSFET Inverter(1)

więcej podobnych podstron