ARCHITEKTURA

ARCHITEKTURA

KOMPUTERÓW

KOMPUTERÓW

WPROWADZENIE

WARUNKI ZALICZENIA

WARUNKI ZALICZENIA

1 lub 2 kolokwia w sumie za 50

punktów

Zaliczenie zajęć laboratoryjnych

Egzamin pisemny i ustny

LITERATURA

LITERATURA

Piotr Metzger “Anatomia PC”, Helion 2002

J.L.Hennessy, D.A. Patterson “Computer

Organization & Design The

Hardware/Software Interface”, Morgan

Kaufmann Publishers Inc.1994

J.L.Hennessy, D.A. Patterson “Computer

architecture A Quantitative Approach”,

Morgan Kaufmann Publishers Inc.1996

G.Kane “MIPS RISC Architecture”,

Prentice-Hall 1988

DEFINICJA

DEFINICJA

ARCHITEKTURY

ARCHITEKTURY

KOMPUTERA

KOMPUTERA

„Architektura komputera zdefiniowana

jest poprzez atrybuty komputera widoczne

dla programisty piszącego program w

języku maszynowym. Ta definicja obejmuje

listę instrukcji, format instrukcji, kody

operacji, tryby adresowania, oraz

wszystkie rejestry i lokacje pamięci, które

mogą być bezpośrednio modyfikowane

przez program napisany w języku

maszynowym.”

DEFINICJA

DEFINICJA

ARCHITEKTURY

ARCHITEKTURY

KOMPUTERA

KOMPUTERA

„Implementacja jest zdefiniowana

poprzez rzeczywistą strukturę sprzętu,

organizację układów logicznych i

organizację dróg przepływu danych”

G.M. Amdhal, G.A. Blaaw, F.P. Brooks

„Architecture of the IBM System/360”,

IBM Journal of Research and

Development, vol.8 no.2 1964, pp.87-

101

ARCHITEKTURA I

ARCHITEKTURA I

ORGANIZACJA

ORGANIZACJA

Architektura komputera opisuje te

atrybuty systemu, które widziane są

dla programisty

lista rozkazów, liczba bitów wykorzystywanych

do prezentacji różnych typów danych,

mechanizmy we/wy, metody adresowania

pamięci.

Organizacja komputera odnosi się do

jednostek operacyjnych i ich połączeń

rozwiązania sprzętowe niewidzialne dla

programisty, takie jak sygnały sterujące,

interfejsy między komputerem a urządzeniami

peryferyjnymi oraz wykorzystywana technologia

pamięci.

ARCHITEKTURA I

ARCHITEKTURA I

ORGANIZACJA

ORGANIZACJA

Architektura może przeżyć wiele lat,

organizacja zmienia się wraz z technologią

Rodzina Intel x86 ma tą samą architekturę

System/370 IBM ma tą samą architekturę

Zmiany technologii nie tylko wpływają na

organizację, ale także umożliwiają

budowanie komputerów o potężniejszej i

bogatszej architekturze

ARCHITEKTURA

ARCHITEKTURA

Na architekturę wpływ mają:

uwarunkowania historyczne

technologia

języki programowania

systemy operacyjne

aplikacje

ARCHITEKTURA

ARCHITEKTURA

Cechy przejrzystej architektury:

spójność – możliwość rekonstrukcji na

podstawie nie pełnej specyfikacji. W szczególności

rozkazy powinny mieć taką samą strukturę kodu,

używać takich samych typów i formatów danych.

Jednakowe dla wszystkich rozkazów powinny być

reguły zaokrąglania wyniku, reakcji na błędny

argument, reguły obsługi wyjątków

ortogonalność – niezależna (rozłączna)

specyfikacja funkcji zaliczanych do odrębnych

klas

ARCHITEKTURA

ARCHITEKTURA

Cechy przejrzystej architektury:

trafność – specyfikacja i implementacja tylko tych

funkcji które są logicznie spójne z definicją

architektury. Przejawami trafności są:

Ekonomiczność – wyeliminowanie funkcji logicznie

niespójnych

Przeźroczystość – oddzielenie architektury od organizacji

ogólność – pełny zakres działania

specyfikowanych funkcji, wyznaczonych tylko ich

dziedziną i nie ograniczony aspektami

organizacyjnymi. Cechami ogólności są:

Kompletność – funkcjonalna pełność w obrębie klas

funkcji, której ubocznym skutkiem jest nieoszczędne

wykorzystanie przestrzeni kodowej

Otwartość – możliwość rozwoju w ramach architektury

STRUKTURA I

STRUKTURA I

DZIAŁANIE

DZIAŁANIE

Struktura to sposób wzajemnego

powiązania składników

Funkcje określają działanie

poszczególnych składników jako

części struktury

DZIAŁANIE

DZIAŁANIE

Podstawowe funkcje, które realizuje

komputer:

przetwarzanie danych

przechowywanie danych

przenoszenie danych

sterowanie

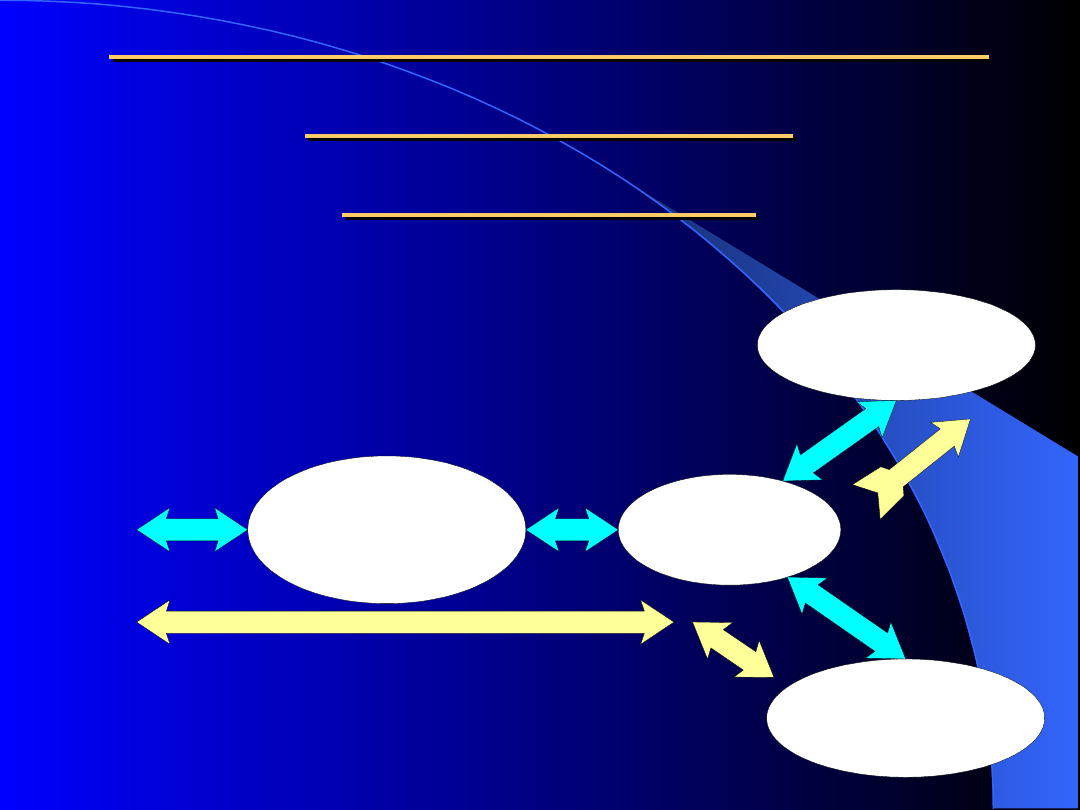

PRZEGLĄD FUNKCJI

PRZEGLĄD FUNKCJI

Obraz funkcjonalny komputera

URZADZENIE

STERUJ ACE

URZADZENIE DO

PRZEMIESZCZANIA

DANYCH

URZADZENIE DO

PRZECHOWYWANIA

DANYCH

URZADZENIE DO

PRZETWARZANIA

DANYCH

OPERACJE KTÓRE MOŻE

OPERACJE KTÓRE MOŻE

REALIZOWAĆ

REALIZOWAĆ

KOMPUTER

KOMPUTER

Przenoszenie danych

od jednego urządzenia peryferyjnego

( linii transmisyjnej ) do drugiego

URZADZENIE

STERUJ ACE

URZADZENIE DO

PRZEMIESZCZANIA

DANYCH

URZADZENIE DO

PRZECHOWYWANIA

DANYCH

URZADZENIE DO

PRZETWARZANIA

DANYCH

OPERACJE KTÓRE MOŻE

OPERACJE KTÓRE MOŻE

REALIZOWAĆ

REALIZOWAĆ

KOMPUTER

KOMPUTER

Przechowywanie danych

dane przenoszone z urządzenia do

komputera i odwrotnie (np. Internet)

URZADZENIE

STERUJ ACE

URZADZENIE DO

PRZEMIESZCZANIA

DANYCH

URZADZENIE DO

PRZECHOWYWANIA

DANYCH

URZADZENIE DO

PRZETWARZANIA

DANYCH

OPERACJE KTÓRE MOŻE

OPERACJE KTÓRE MOŻE

REALIZOWAĆ

REALIZOWAĆ

KOMPUTER

KOMPUTER

Przetwarzanie zarchiwizowanych

danych

Obróbka danych z pomiarów

URZADZENIE

STERUJ ACE

URZADZENIE DO

PRZEMIESZCZANIA

DANYCH

URZADZENIE DO

PRZECHOWYWANIA

DANYCH

URZADZENIE DO

PRZETWARZANIA

DANYCH

OPERACJE KTÓRE MOŻE

OPERACJE KTÓRE MOŻE

REALIZOWAĆ

REALIZOWAĆ

KOMPUTER

KOMPUTER

Przetwarzanie danych

będących w drodze między miejscem

przechowywania a otoczeniem (np.

drukowanie rachunków bankowych)

URZADZENIE

STERUJ ACE

URZADZENIE DO

PRZEMIESZCZANIA

DANYCH

URZADZENIE DO

PRZECHOWYWANIA

DANYCH

URZADZENIE DO

PRZETWARZANIA

DANYCH

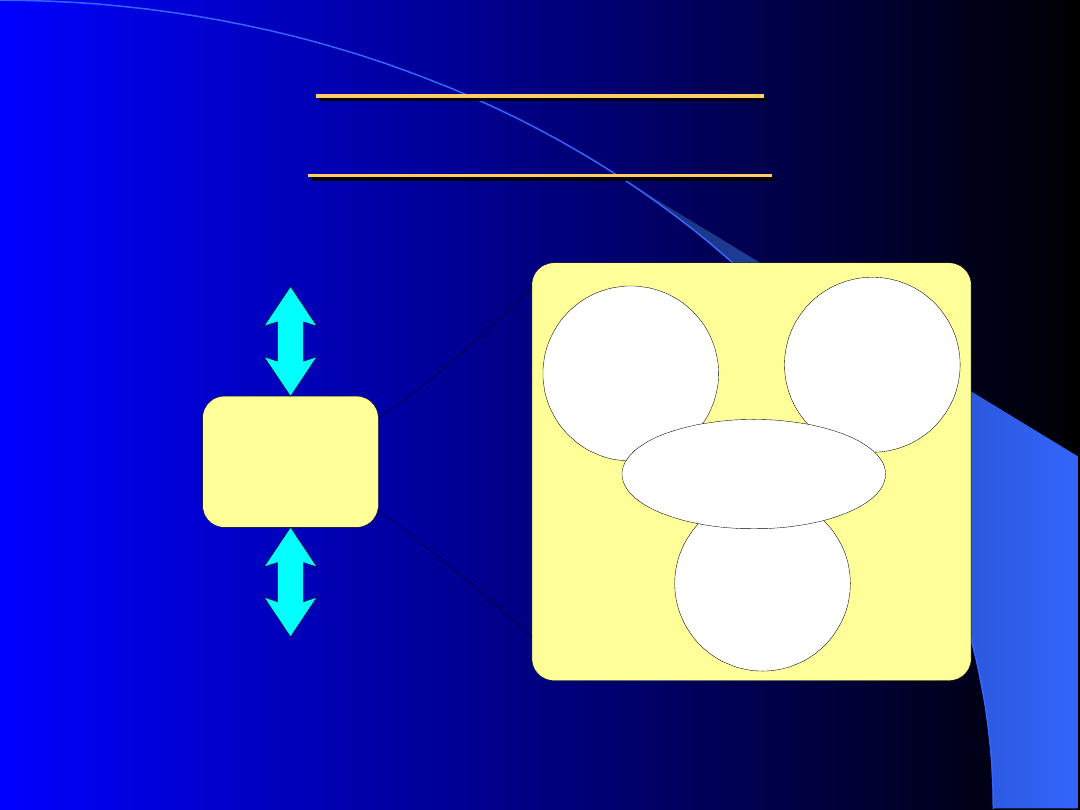

STRUKTURA

STRUKTURA

KOMPUTERA

KOMPUTERA

KOMPUTER

OTOCZENIE

LINIE KOMUNIKACYJ NE

OTOCZENIE

URZADZENIA PERYFERYJ NE

J EDNOSTKA

CENTRALNA

PAMIEC

RAM

WEJ SCIE

WYJ SCIE

POLACZENIA

SYSTEMOWE

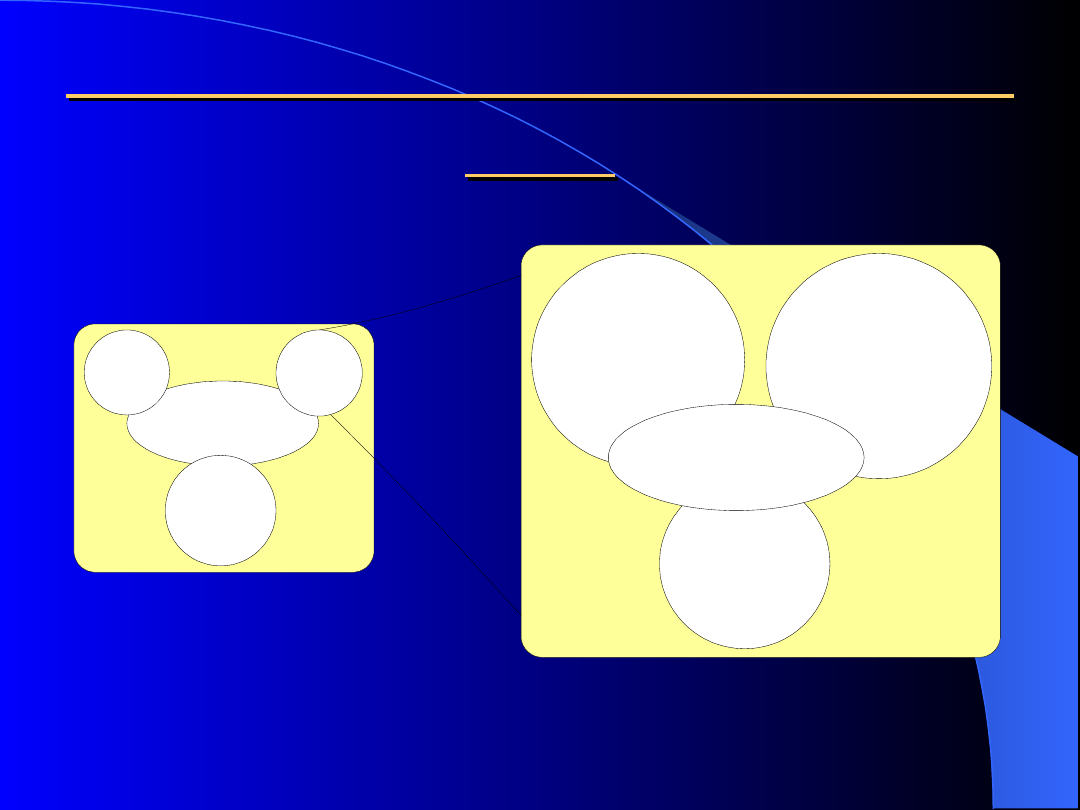

JEDNOSTKA CENTRALNA -

JEDNOSTKA CENTRALNA -

CPU

CPU

REJ ESTRY

ALU

J EDNOSTKA

ARYTMETYCZNO

LOGICZNA

J EDNOSTKA

STERUJ ACA

POLACZENIA

WEWNETRZNE

MAGISTRAL

WEWNETRZNA

I/O

PAMIEC

CPU

KOMPUTER

CPU

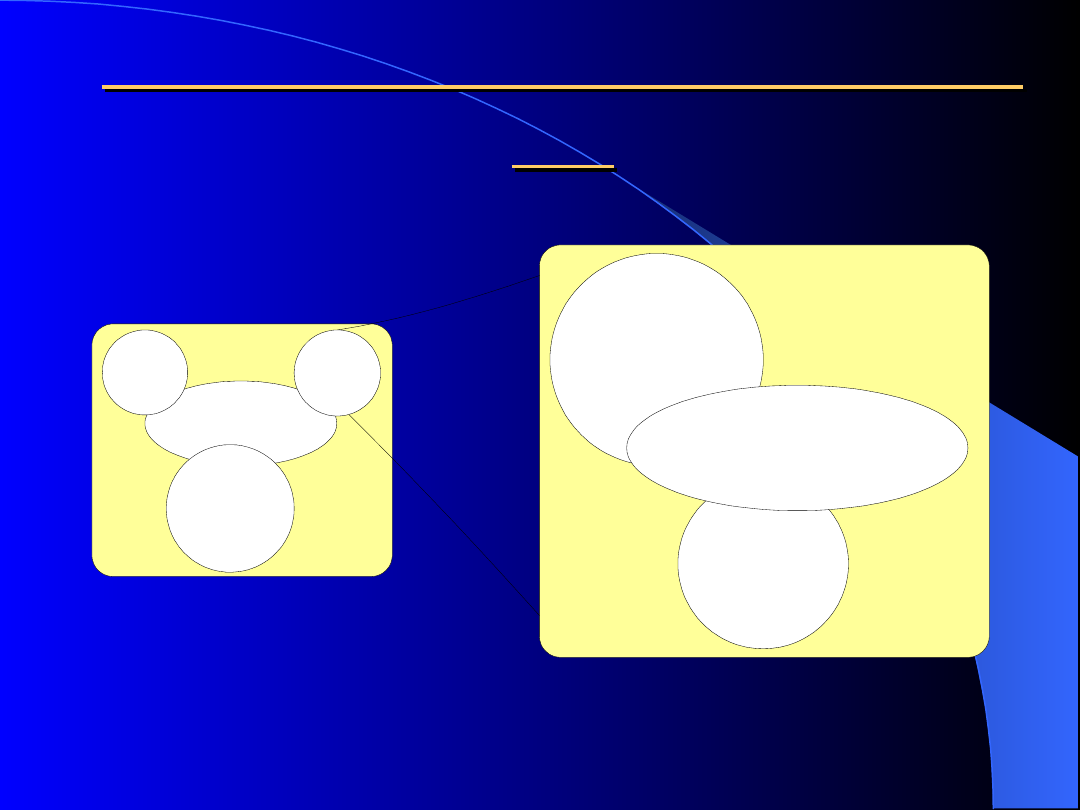

JEDNOSTKA STERUJĄCA -

JEDNOSTKA STERUJĄCA -

CU

CU

UKLADY

LOGICZNE

PAMIEC

STERUJ ACA

REJ ESTRY I DEKODERY

J EDNOSTKI STERUJ ACEJ

MAGISTRAL

WEWNETRZNA

ALU

REJ ESTRY

CU

CPU

CPU

TROCHĘ HISTORII

TROCHĘ HISTORII

ABACUS

5000 lat temu Azja Środkowa

system liczenia dwójkowo – piątkowy

CODEX MADRID

Leonardo da Vinci

Dr.Roberto Guatelli – replika 1968r.

PASCALINE

Blaise Pascal 1642

sumowała liczby 8-mio cyfrowe

TROCHĘ HISTORII

TROCHĘ HISTORII

Gotfried Wilhelm von Leibnitz 1649r.

udoskonala maszynę Pascala i wzbogaca ją o

operację mnożenia

Xavier Thomas de Colmar 1820r.

konstruuje arytmometr umożliwiający

wykonywanie czterech podstawowych

działań matematycznych

PASCAL, LEIBNITZ, COLMAR to

twórcy mechanicznych urządzeń

liczących

TROCHĘ HISTORII

TROCHĘ HISTORII

Charles Babbage (1791-1871)

matematyk

W 1822 zaproponował skonstruowanie

maszyny „Difference Engine”, która

umożliwiłaby rozwiązywanie równań

różniczkowych

maszyna napędzana parą, miała pamiętać

program obliczeń i automatycznie

drukować wyniki

Następnym pomysłem jego był uniwersalny

komputer zdolny do rozwiązywania

różnorodnych zagadnień matematycznych

TROCHĘ HISTORII

TROCHĘ HISTORII

Augusta Ada King- Lovelace

(1815-1842)

córka Byron’a

współpracowniczką Babbage’a

stworzyła instrukcję (pierwowzór

programu) dla konstruowanej maszyny

Powstały w Departamencie obrony

USA język ADA nazwę swą wywodzi od

jej imienia

TROCHĘ HISTORII

TROCHĘ HISTORII

Komputer parowy posiadał

„urządzenie wejściowe” mogące

odczytywać karty perforowane z

instrukcjami dla maszyny

(wymyślone przez Jacquad’a),

„pamięć” zdolną pamiętać 1000 liczb

50-cyfrowych, zawierał także

urządzenie pozwalające na zmianę

kolejności obliczeń i urządzenie

wyjściowe – drukujące wyniki.

TROCHĘ HISTORII

TROCHĘ HISTORII

George Boole (1815 - 1864)

zajmował się pracami teoretycznymi

w dziedzinie logiki. W latach 1847 i

1854 opublikował prace pozwalające

na prezentację wyrażeń logicznych za

pomocą wyrażeń algebraicznych

znanych dzisiaj jako „Algebra Boole’a”

August DeMorgan

określił operacje logiczne nazywane

dzisiaj prawami DeMorgana.

TROCHĘ HISTORII

TROCHĘ HISTORII

W 1889 amerykański wynalazca, Herman

Hollerith (1860-1929)

wykorzystał pomysł maszyny Jacquard’a do

obliczeń matematycznych

Swój pomysł wykorzystał do obliczenia

wyników spisu ludności, poprzedni spis trwał 7

lat dzięki jego pomysłowi obliczenia

przeprowadzono w ciągu 6 tygodni

Utworzył firmę, która w połączeniu z kilkoma

innymi w 1924 roku stała się jedną z

najważniejszych dla rozwoju techniki

komputerowej IBM (International Business

Machines).

TROCHĘ HISTORII

TROCHĘ HISTORII

1906 Lee de Forest

konstruuje lampę elektronową triodę.

Mogła ona pełnić zarówno funkcje

wzmacniacza jak i przełącznika.

Koniec lat 30-tych Claude

E.Shannon

dochodzi do wniosku, że algebra Boole’a

jest idealnym systemem dla maszyn

liczących.

TROCHĘ HISTORII

TROCHĘ HISTORII

1931Vannevar Bush

skonstruował kalkulator rozwiązujący

skomplikowane równania różniczkowe.

1937 Atanasoff

zbudował maszynę, która miała służyć

jego studentom i asystentom do

rozwiązywania układów równań

różniczkowych cząstkowych. Potrafiła

rozwiązać układ 29 równań z 29

niewiadomymi

TROCHĘ HISTORII

TROCHĘ HISTORII

Konrad Zuse (1910-1995) Henschel Aircraft

Company Berlin

na początku II Wojny Światowej zbudował kilka

automatycznych kalkulatorów. Zwrócił uwagę na fakt, że

jednym z najtrudniejszych problemów w trakcie

wykonywania skomplikowanych obliczeń na kalkulatorach

mechanicznych jest przechowywanie danych pośrednich.

Postulował by automatyczny kalkulator posiadał trzy

podstawowe zespoły:

układy sterujące

Pamięć

kalkulator do obliczeń arytmetycznych

w 1941 komputer Z3 zbudowany przez Zuse z

przekażników wykorzystywał system binarny, mógł

wykonywać operacje zmiennoprzecinkowe, do

przechowywania danych i zapisu programu

wykorzystywał stare filmy

TROCHĘ HISTORII

TROCHĘ HISTORII

w 1946 Zuse opracował pierwszy

algorytmiczny język „Plankalul” i użył go do

napisania programu gry w szachy. Język

pozwalał na użycie tablic i rekordów oraz

przyporządkowanie zmiennym wartości

podanego wyrażenia algebraicznego.

1944 Howard H.Aiken skonstruował

pierwszy elektroniczny kalkulator. 15m x

2.5m ważyła 5 ton zawierała ok.800km

przewodów łączących elementy. Program

wprowadzano na taśmie perforowanej.

Pod koniec II Wojny Światowej powstał

komputer ENIAC 18000 lamp, 70000

rezystorów i pobierała 180kW energii, ważył

około 30ton. Jednego roku wymieniono w nim

około 19000 lamp

TROCHĘ HISTORII

TROCHĘ HISTORII

Połowa lat 40-tych John von Neumann stawia

postulaty dotyczące architektury komputera:

komputer powinien posiadać pamięć w której

przechowywane będą zarówno dane jak i instrukcje

z możliwością zapisu i odczytu w dowolnej

kolejności

powinien być wyposażony w jednostkę obliczeniową

pozwalającą na operacje arytmetyczne i logiczne

powinien zawierać takie układy sterujące jego

pracą, które pozwalałyby na interpretację rozkazów

pobieranych z pamięci oraz wybór alternatywnych

działań w zależności od wyniku poprzednich

operacji.

TROCHĘ HISTORII

TROCHĘ HISTORII

1958 Texas Instruments demonstruje pierwszy

układ scalony

1964 John Kemeny i Thomas Kurtz dostarczają

język programowania BASIC

1969

Intel informuje o wprowadzeniu do produkcji kości

pamięci 1KB RAM

Powstaje Advanced Micro Devices

1970 Dennis M. Ritchie, Ken Thompson, Brian

Kernighan wprowadzają język C umożliwiający

abstakcyjne programowanie plików, otwierając mu

drogę do tworzenia różnych aplikacji pod różne

systemy operacyjne

TROCHĘ HISTORII

TROCHĘ HISTORII

1971

Intel wprowadza pierwszy mikroprocesor

4004 (cena $200) prędkość 60000 operacji

na sekundę

Niklaus Wirth opracowuje język PASKAL

1972 Intel 8008, 300000 operacji na

sekundę, można dołączyć 16kB RAM

1973 Scelbi-8H computer kit

(8008,1KB RAM, $565)

TROCHĘ HISTORII

TROCHĘ HISTORII

1974

Intel8080 75instrukcji, 3 MIPS, 64KB

MEMORY,

Motorola 6800

Gary Kildall tworzy CP/M

1975

Bill Gates i Paul Allen tworzą TrafO-Data

MC6501 $20, MC6502 $25 Intel 8080 $150

IBM 5100 (BASIC,16KB RAM, pamięć

taśmowa) $9000

TROCHĘ HISTORII

TROCHĘ HISTORII

1976 „Frugal Floppy” 8-calowy

$1200

1977 oficjalnie powstaje Microsoft

1980

Z80, Timex1000

Winchester dysk twardy

PCDOS,MSDOS

Intel tworzy iAPX432 32bitowy

procesor, krokiem pomiedzy 8086 a

432 ma być 80286

TROCHĘ HISTORII

TROCHĘ HISTORII

1981

Hayes sprzedaje 300bitowy modem

IBM PC (4.77MHz, 8088, 64KB RAM, 40KB ROM,

floppy 5’25,MSDOS 1.0, $3000)

IBM CGA 640x200 16 kolorów,

1982 Compaq wprowadza Portable PC (4.77MHz,

8088,12KB RAM, 9 cali monochromatyczny

monitor, 320KB 5’25 dysk, $3000)

1984

Apple 300bodów modem $300, 1200 bodów $500

640x350 EGA $850, karta 16kolorów z 64KB RAM $524

MSDOS 3.0

Hewlet-Packard laserjet laser printer 300dpi $3600

Intel 80186,80286

TROCHĘ HISTORII

TROCHĘ HISTORII

1985

obroty Compaq’a sięgają 329milionów $

Windows 1.0

1986

IBM PC (80c86,256KB RAM, 2 floppy 720KB, $2000)

wprowadzane 80286,zegar 8MHz

wprowadzane 80386, 16MHz

1987

Apple open architecture Macintosh II $3900 (1MB

RAM,800K floppy, 40MB dysk $5500)

pierwszy system plug and play dla kart

rozszerzających

Windows 2.0

TROCHĘ HISTORII

TROCHĘ HISTORII

1991

Microsoft mysz, tracball

CD-ROM $400

OS2->Windows NT

Dostęp dla bisnesu do internetu

MIPS Computer Systems R4000 64bitowy

RISC

1993

Pentium 60MHz

Apple 80MHz PowerPC 601

25 milionów zarejestrowanych użytkowników

WINDOWS

TROCHĘ HISTORII

TROCHĘ HISTORII

1994

poczwórny CD-ROM $1000

AMD486DX2-80

WINDOWS NT 3.5

1995 pentium 133

GENERACJE

GENERACJE

KOMPUTERÓW

KOMPUTERÓW

GENERACJA 0

GENERACJA 0

konstrukcje eksperymentalne oparte o elementy

elektromechaniczne

Alan TURING wykazał, że każdy algorytm można

wykonać automatycznie jako skończony ciąg

podstawowych operacji – maszyna Turinga –1937

GENERACJA 1

GENERACJA 1 1951-1960

Powszechnie stosowane lampy elektronowe

Pierwszy komercyjny komputer z firmy REMINGTON

RAND – UNIVAC(Universal Automatic

Computer), oraz pierwszy elektroniczny z firmy IBM

Powstaje tranzystor bipolarny W.B.Shockley 1951

Każdy komputer posługiwał się specyficznym

językiem maszynowym (rozkazy kodowane były

binarnie).

GENERACJE

GENERACJE

KOMPUTERÓW

KOMPUTERÓW

GENERACJA 2

GENERACJA 2 1954-1964

Układy przełączające używane w komputerach w tym

okresie bazowały na elementach dyskretnych (diody i

tranzystory), które pozwalały na uzyskanie czasów

przełączania ok. 0,3 mikrosekundy

Prototyp pierwszego komputera PDP-1 1960 z klawiaturą i

monitorem ekranowym

TRADIX zbudowany w Bell Laboratories w roku 1954 i TX-0

MIT's pochodzący z Lincoln Laboratory posiadały pamięci

oparte o rdzenie ferrytowe.

Nowością w dziedzinie architektury komputerów było

zastosowanie rejestrów indeksowych do kontroli realizacji

pętli i uproszczenia operacji zmiennoprzecinkowych na

liczbach rzeczywistych.

W tym okresie weszły do powszechnego użytku bardziej

wyrafinowane języki programowania wysokiego poziomu

takie jak COBOL (Common Business-Oriented Language)

oraz FORTRAN (Formula Translator)

GENERACJE

GENERACJE

KOMPUTERÓW

KOMPUTERÓW

GENERACJA 3

GENERACJA 3 1964-1975

Dominacja technologii TTL

rozwój systemów operacyjnych ( w tym wielozadaniowych).

GENERACJA 4

GENERACJA 4 1975-czasy współczesne

rozwój układów (LSI – Large Scale Integration)

GENERACJA 5

GENERACJA 5 czasy współczesne i

przyszłość

sztuczna inteligencja

możliwość konwersacji z operatorem

wejście wizyjne (a więc również możliwość

rozpoznawania operatora)

możliwość uczenia się na podstawie własnych

doświadczeń

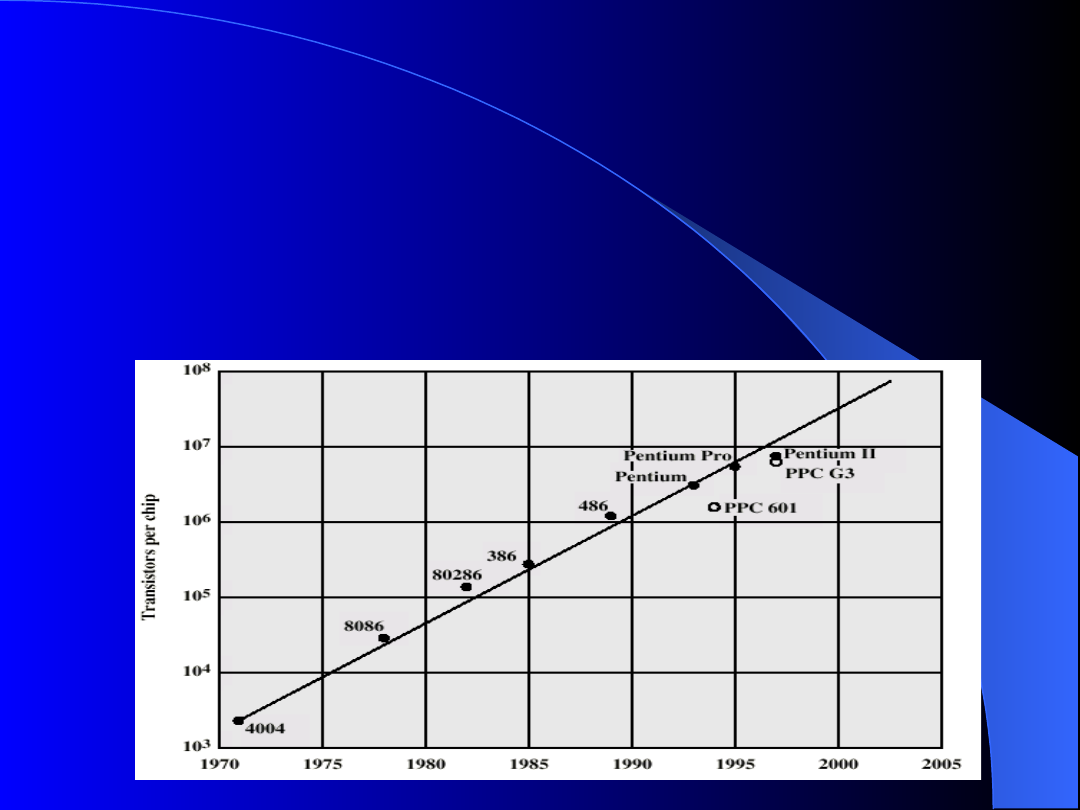

PRAWO GORDONA

PRAWO GORDONA

MOORA

MOORA

Zgodnie z empirycznie sformułowanym

prawem MOORA gęstość upakowania

układów scalonych i ich szybkość

działania podwaja się co 18 miesięcy

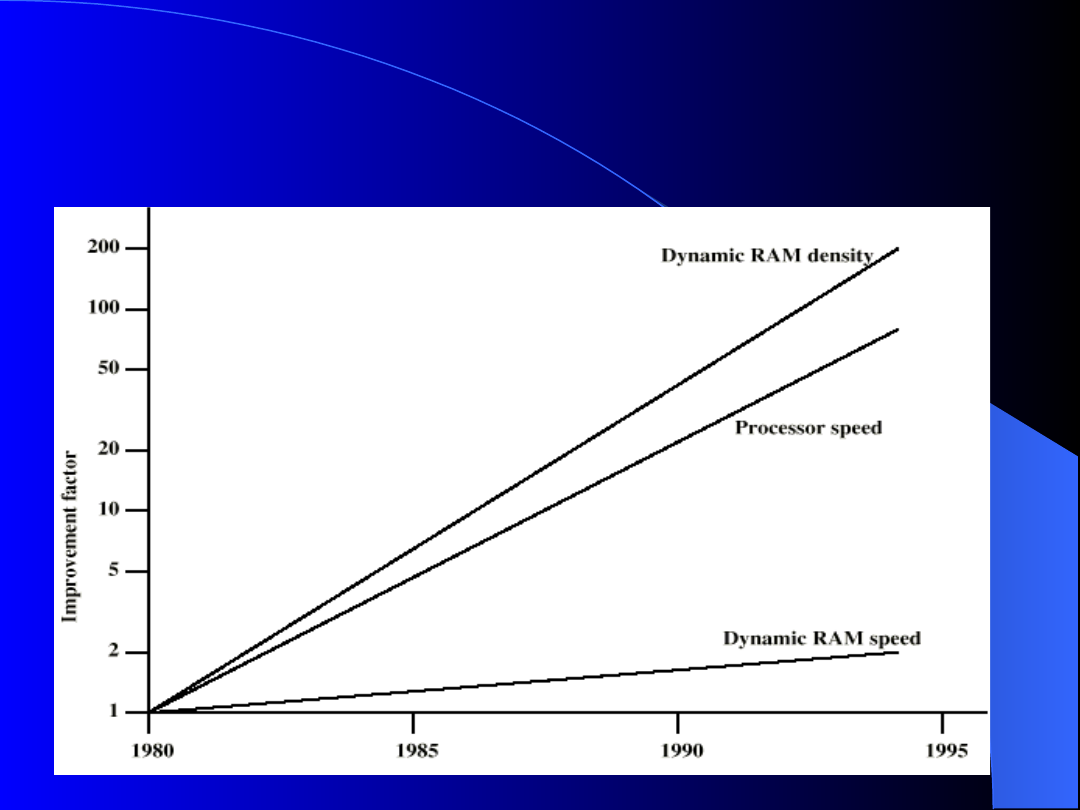

POSTĘP TECHNOLOGII

POSTĘP TECHNOLOGII

Ewolucja pamięci DRAM i procesorów

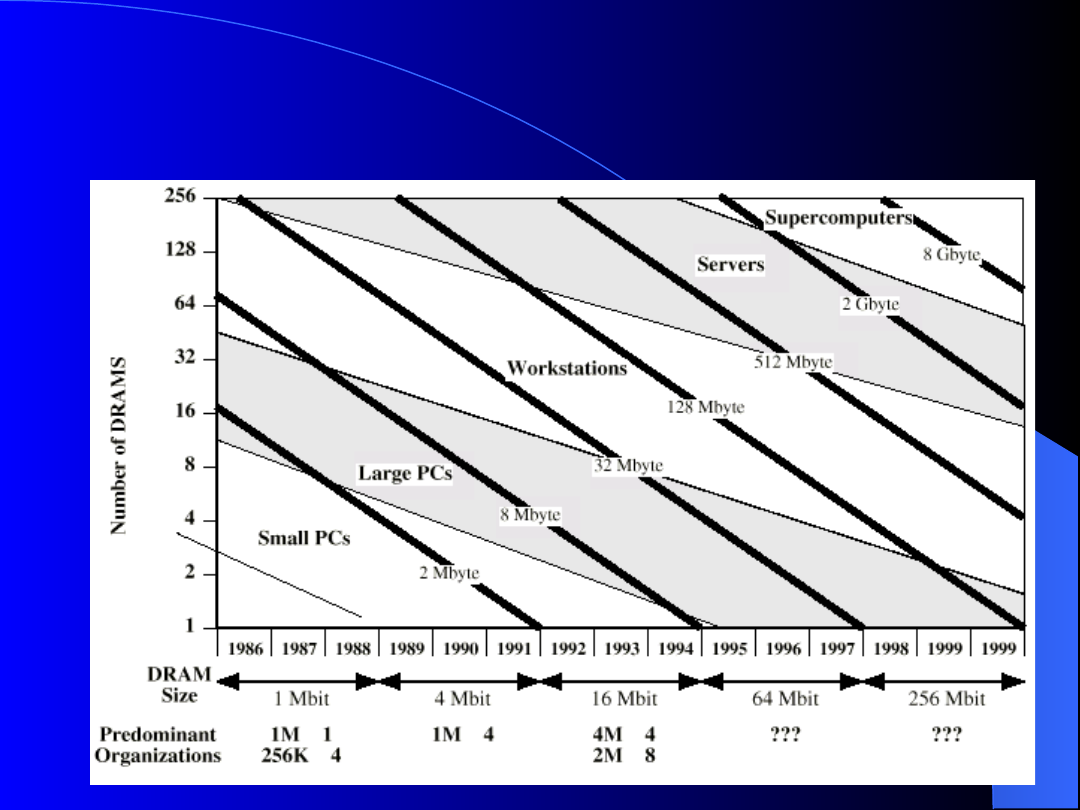

POSTĘP TECHNOLOGII

POSTĘP TECHNOLOGII

Tendencje rozwoju pamięci DRAM

POSTĘP TECHNOLOGII

POSTĘP TECHNOLOGII

Zmniejszenie fizycznego rozmiaru elementu

logicznego pozwala na stosowanie niższego napięcia

zasilania oraz powoduje wprowadzenie mniejszego

czasu opóźnienia dla sygnału elektrycznego (można

stosować wyższe częstotliwości taktowania układów)

Niższe napięcie zasilania zmniejsza ilość

emitowanego przez układ ciepła, które jest wprost

proporcjonalne do kwadratu napięcia zasilającego i

częstotliwości pracy. Intel dual voltage (mniejsze

napięcie zasilania jądra procesora niż układów

we/wy).

Dąży się do zmniejszania średnicy ścieżek

przewodzących – obecnie 0.13mikrona

WZROST WYDAJNOŚCI

WZROST WYDAJNOŚCI

Zwiększanie prędkości procesora

Zwiększanie pojemności pamięci

Podążanie szybkości dostępu do pamięci

za prędkością procesora

Pamięć cache na płycie

Pamięć cache L1 i L2

Przewidywanie skoków

Analiza struktury danych

Potokowość

Prognozowanie

WZROST WYDAJNOŚCI

WZROST WYDAJNOŚCI

Zwiększenie ilości bitów dostępnych w

jednym cyklu

Zmiana interfejsu dostępu do pamięci

Cache

Redukcja częstotliwości dostępu do

pamięci

Zwiększenie szybkości magistral

Magistrale hierarchiczne

DZIAŁANIE KOMPUTERA

DZIAŁANIE KOMPUTERA

Podstawowa funkcja komputera –

wykonywanie programów

Na najwyższym poziomie możemy

opisać system komputerowy poprzez:

Opisanie zewnętrznego zachowania

każdego modułu (danych i sygnałów

kontrolnych, które wymienia on z innymi

modułami)

Podanie struktury połączeń i sterowania

wymaganego do zarządzania tą strukturą

KOMPUTER -

KOMPUTER -

STRUKTURA

STRUKTURA

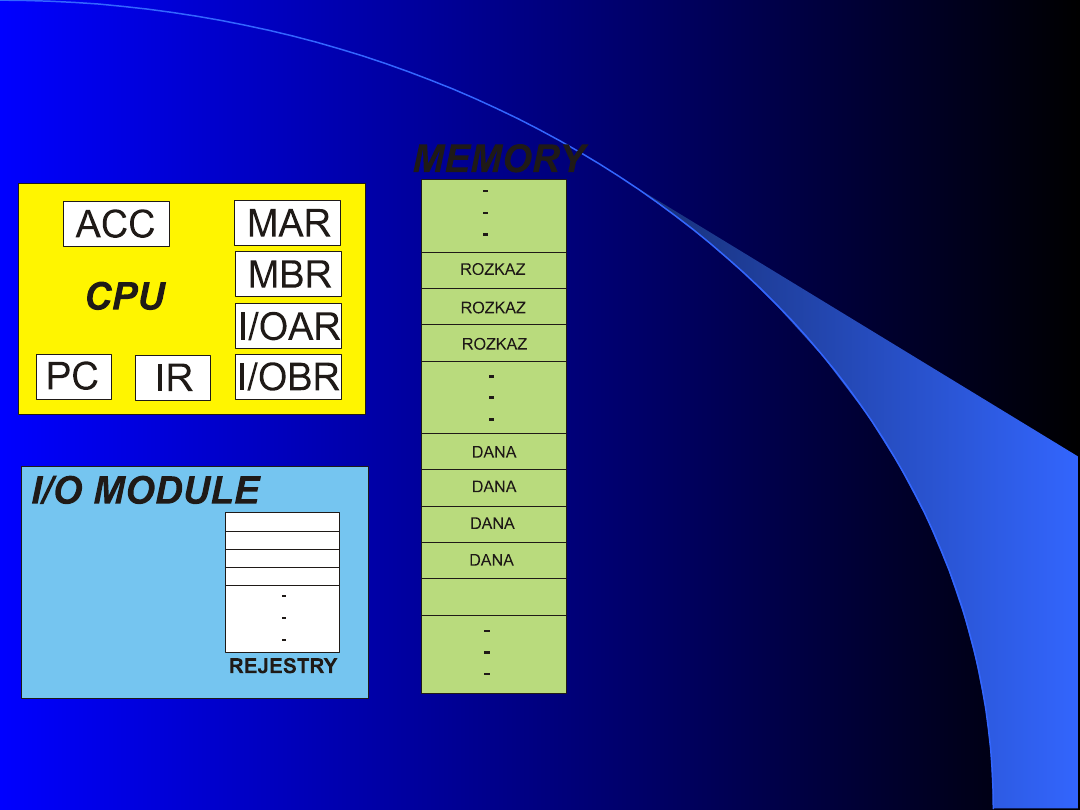

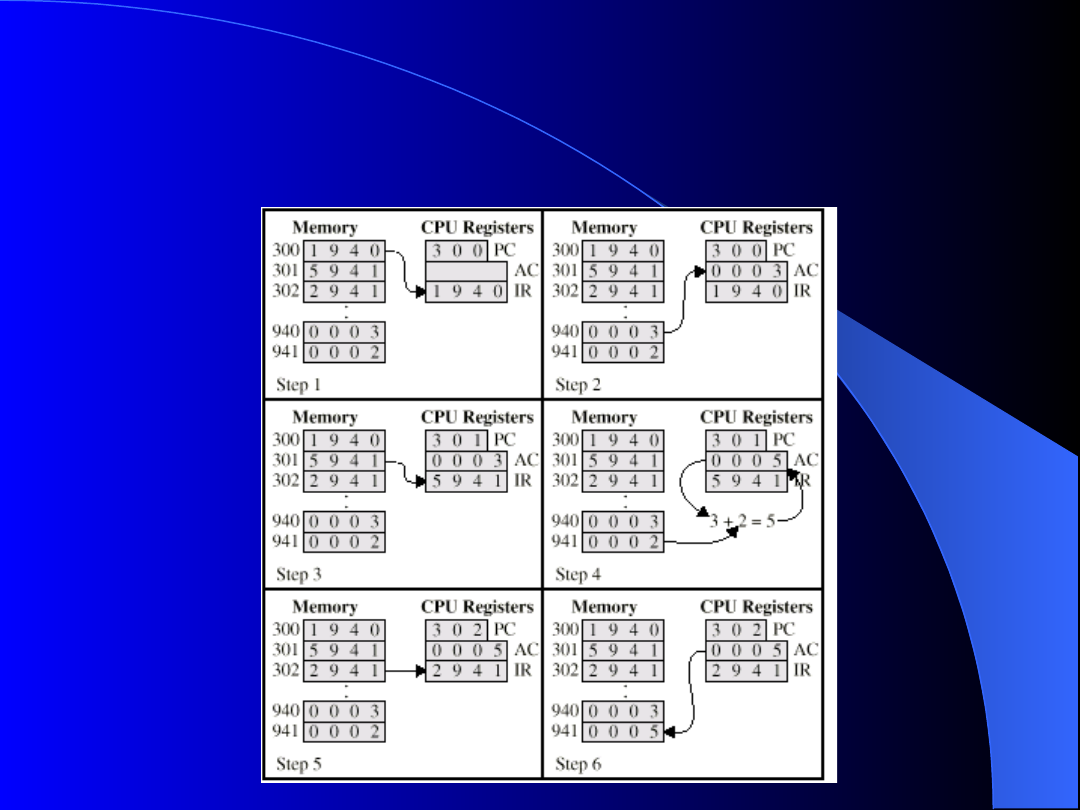

MAR - rejestr adresowy pamięci

- określa adres w pamięci

następnego zapisu lub odczytu

MBR - rejestr buforowy pamięci

- zawiera dane, które mają być

zapisane w pamięci lub dane

odczytane z pamięci

I/OAR - rejestr adresowy we/wy -

określa konkretne urządzenie

we/wy

I/OBR - rejestr buforowy we/wy -

wykorzystywany do wymiany

danych między modułem we/wy a

jednostką centralną

PC - licznik rozkazu - rejestr

zawierający informacje który

rozkaz ma być pobrany

IR - rejestr rozkazu - do

przechowywania pobranego

rozkazu

ACC – akumulator – rejestr w

którym wykonywane są wszystkie

operacje arytmetyczno logiczne

KOMPUTER – CYKL

KOMPUTER – CYKL

ROZKAZOWY

ROZKAZOWY

Wykonywanie programu:

Program składa się z zestawu rozkazów

przechowywanych w pamięci

Jednostka centralna realizuje program poprzez

wykonywanie rozkazów w nim zawartych

Przetwarzanie rozkazów realizowane jest

przez procesor w dwóch krokach:

Pobranie rozkazu z pamięci

Wykonanie rozkazu

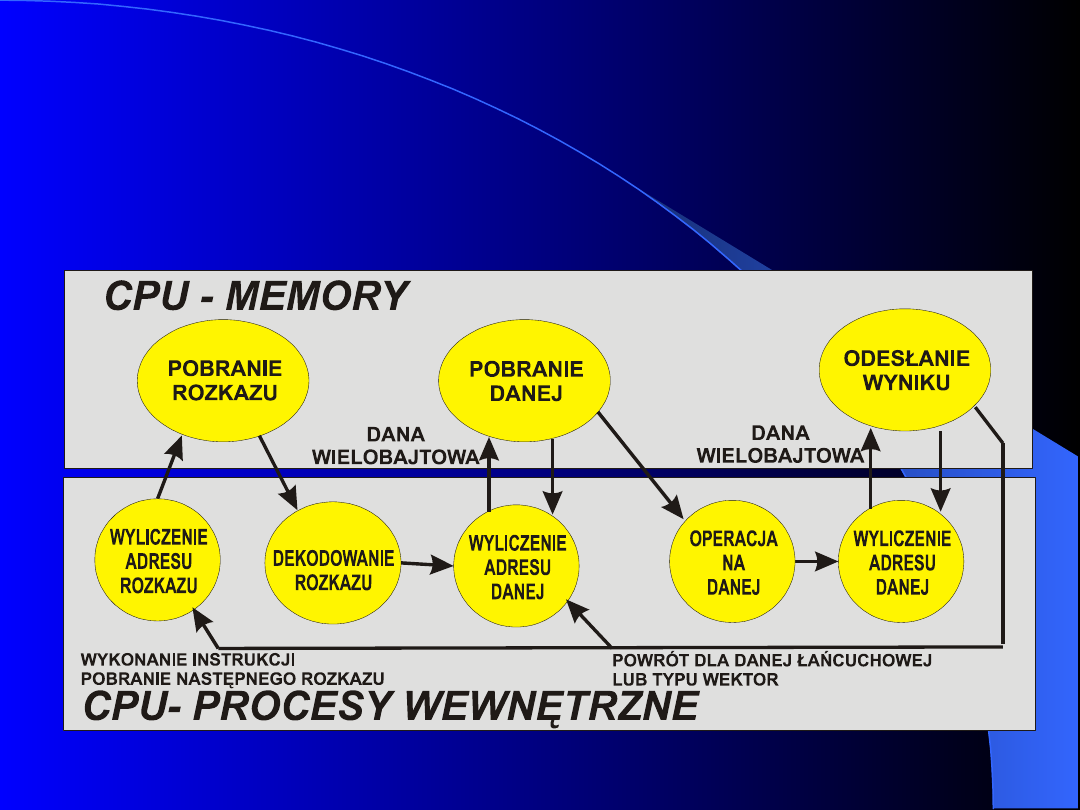

KOMPUTER – FAZY

KOMPUTER – FAZY

PRZETWARZANIA ROZKAZU

PRZETWARZANIA ROZKAZU

F – pobranie kodu rozkazu z pamięci

(fetch)

D – dekodowanie (decode)

E – wykonanie (execute), w

szczególności transfer rejestr – pamięć

(load/store)

W – zapamiętanie wyniku (write)

KOMPUTER – CYKL

KOMPUTER – CYKL

ROZKAZOWY - POBIERANIE

ROZKAZOWY - POBIERANIE

Licznik programu (PC – Program Counter)

przechowuje adres następnej instrukcji do

wykonania

Procesor pobiera instrukcję z pamięci spod adresu

wskazywanego przez PC

Zwiększany jest licznik PC (incrementacja PC)

Instrukcja ładowana jest do rejestru rozkazowego

(IR – Instruction Register)

Procesor interpretuje rozkaz i przeprowadza

wymagane działanie (przechodzi do cyklu

wykonywania)

KOMPUTER – CYKL

KOMPUTER – CYKL

ROZKAZOWY -

ROZKAZOWY -

WYKONYWANIE

WYKONYWANIE

Cztery kategorie działań:

Przesłanie procesor pamięć

Przesłanie procesor wejście/wyjście

Przetwarzanie danych (operacje

arytmetyczne lub logiczne na danych)

Sterowanie – zmiana sekwencji operacji np.

rozkaz skoku

Kombinacja wyżej wymienionych działań

KOMPUTER – PRZYKŁAD

KOMPUTER – PRZYKŁAD

WYKONANIA PROGRAMU

WYKONANIA PROGRAMU

KOMPUTER – GRAF CYKLU

KOMPUTER – GRAF CYKLU

ROZKAZOWEGO

ROZKAZOWEGO

KOMPUTER –

KOMPUTER –

ROZWIĄZANIA

ROZWIĄZANIA

ZWIĘKSZAJĄCE PRĘDKOŚĆ

ZWIĘKSZAJĄCE PRĘDKOŚĆ

DZIAŁANIA PROCESORA

DZIAŁANIA PROCESORA

PIPELINING

PIPELINING – odseparowanie układów

wykonujących kolejne etapy realizacji

rozkazu umożliwia ich współbieżne

wykonywanie. Podział każdego etapu na

podetapy umożliwia skrócenie cyklu a co za

tym idzie dalszy wzrost wydajności.

Ograniczeniem jest głębokość potoku gdyż

wraz z głębokością rośnie ilość buforów

separujących i czas potrzebny do ich obsługi

rzutuje na przepustowość potoku.

KOMPUTER –

KOMPUTER –

ROZWIĄZANIA

ROZWIĄZANIA

ZWIĘKSZAJĄCE PRĘDKOŚĆ

ZWIĘKSZAJĄCE PRĘDKOŚĆ

DZIAŁANIA PROCESORA

DZIAŁANIA PROCESORA

PRZETWARZANIE SUPERSCALARNE

PRZETWARZANIE SUPERSCALARNE –

powielenie jednostki wykonawczej i

współbieżne wykonywanie rozkazów w

równoległych potokach. Możliwe jest wtedy

gdy między rozkazami nie zachodzi konflikt

danych. Stosuje się także specjalizowane

współbieżne jednostki realizujące określone

klasy rozkazów (jednostka stałoprzecinkowa,

jednostka zmiennoprzecinkowa, układ

wykonania/przewidywania skoku)

KOMPUTER –

KOMPUTER –

ROZWIĄZANIA

ROZWIĄZANIA

ZWIĘKSZAJĄCE PRĘDKOŚĆ

ZWIĘKSZAJĄCE PRĘDKOŚĆ

DZIAŁANIA PROCESORA

DZIAŁANIA PROCESORA

Wydajność potoku może zostać zmniejszona na skutek:

–

Konfliktu sterowania – zaburzenie sekwencji na skutek skoku

–

Konfliktu zasobu – jednoczesne żądanie dostępu do pamięci lub

innego zasobu unikatowego w komputerze (np. we/wy)

–

Konfliktu danych – jednoczesne użycie tej samej danej

W celu wyeliminowania konfliktów w przetwarzaniu

potokowym spowodowanym jednoczesnym żądaniem

dostępu do pamięci w celu przesłania danych i pobrania

rozkazu pamięć podręczną pierwszego poziomu dzieli się

na dwa niezależne obszary danych i programu.

KOMPUTER – ROZWIĄZANIA

KOMPUTER – ROZWIĄZANIA

ZWIĘKSZAJĄCE PRĘDKOŚĆ

ZWIĘKSZAJĄCE PRĘDKOŚĆ

DZIAŁANIA PROCESORA

DZIAŁANIA PROCESORA

Czas trwania wykonania rozkazu zależy także od stopnia

złożoności listy rozkazów.

Analiza częstości użycia rozkazów wykazuje, iż dużo

częściej wykonywane są rozkazy o małym stopniu

złożoności.

Program złożony z rozkazów prostych będzie dłuższy,

lecz prędkość jego przetwarzania może wzrosnąć na

skutek eliminacji rozkazów złożonych. Spostrzeżenia te

są źródłem koncepcji architektury RISC (Reduced

Instruction Set Computer), w której uboższą listę

instrukcji niż w architekturze CISC (Complex

Instruction Set Computer) kompensuje szybsze ich

dekodowanie i wykonywanie.

KOMPUTER –

KOMPUTER –

ADRESOWANIE

ADRESOWANIE

Pamięć to zbiór komórek o jednakowych rozmiarach.

Każda komórka zawiera jednostkę informacyjną

zwaną słowem.

Każda komórka posiada unikatowy numer – adres.

Sposób przydzielania indeksów (adresów) jest cechą

architektury.

Stosowane są dwie konwencje numeracji bitów i

bajtów:

–

Ważniejszy niższy (big endian) – słowo (lub bit)

zawierające bardziej znaczącą część informacji posiada

niższy numer porządkowy (adres)

–

Ważniejszy wyższy (little endian) – słowo (lub bit)

zawierające bardziej znaczącą część informacji posiada

wyższy numer porządkowy

INTEL 80x86 – little endian, PowerPC big endian, MC 680x0

bajty big endian a bity little endian

KOMPUTER – ROZDZIELCZOŚĆ

KOMPUTER – ROZDZIELCZOŚĆ

ADRESOWANIE

ADRESOWANIE

Rozdzielczość adresowania jest cechą architektury mającą

wpływ na organizację kompilatora. Podstawową jednostką

informacji jest słowo maszynowe. Dane systemowe są

tworzone w formacie zgodnym z rozmiarem słowa

maszynowego lub stanowiącym jego wielokrotność.

Szerokość magistrali systemowej musi umożliwiać co

najmniej przesłanie jednego słowa maszynowego w jednym

cyklu pamięci.

W przypadku gdy rozdzielczość adresowania jest większa niż

rozmiar słowa lub szerokość magistrali jest wielokrotnością

podstawowej jednostki adresowej powstaje problem

wpasowania danych w strukturę pamięci. (Problem ten

powinien być rozwiązany podczas kompilacji programu).

Umieszczenie danych o rozmiarze jednostkowym równym

rozmiarowi komórki pamięci jest dowolne, jeśli słowo zajmuje

dwie komórki pamięci to adres słowa powinien być parzysty,

cztery komórki to adres podzielny przez cztery.

KOMPUTER – PRZESTRZENIE

KOMPUTER – PRZESTRZENIE

ADRESOWE

ADRESOWE

Ze względu na sposób adresowania wyróżnia

się następujące przestrzenie adresowe:

–

Obszar roboczy – rejestry procesora

–

Pamięć główna

–

Przestrzeń sterowania

–

Stos

–

Przestrzeń wejścia/wyjścia

–

Identyfikator przychodzącego przerwania

KOMPUTER – ODWZOROWANIE

KOMPUTER – ODWZOROWANIE

PRZESTRZENI ADRESOWYCH

PRZESTRZENI ADRESOWYCH

ROZDZIELNE PRZESTRZENIE ADRESOWE

– używa się różnych rozkazów dla każdej z

przestrzeni

JEDNOLITA PRZESTRZEŃ ADRESOWA – te

same rozkazy, natomiast w zależności od

adresu można adresować różne urządzenia lub

różne fragmenty pamięci.

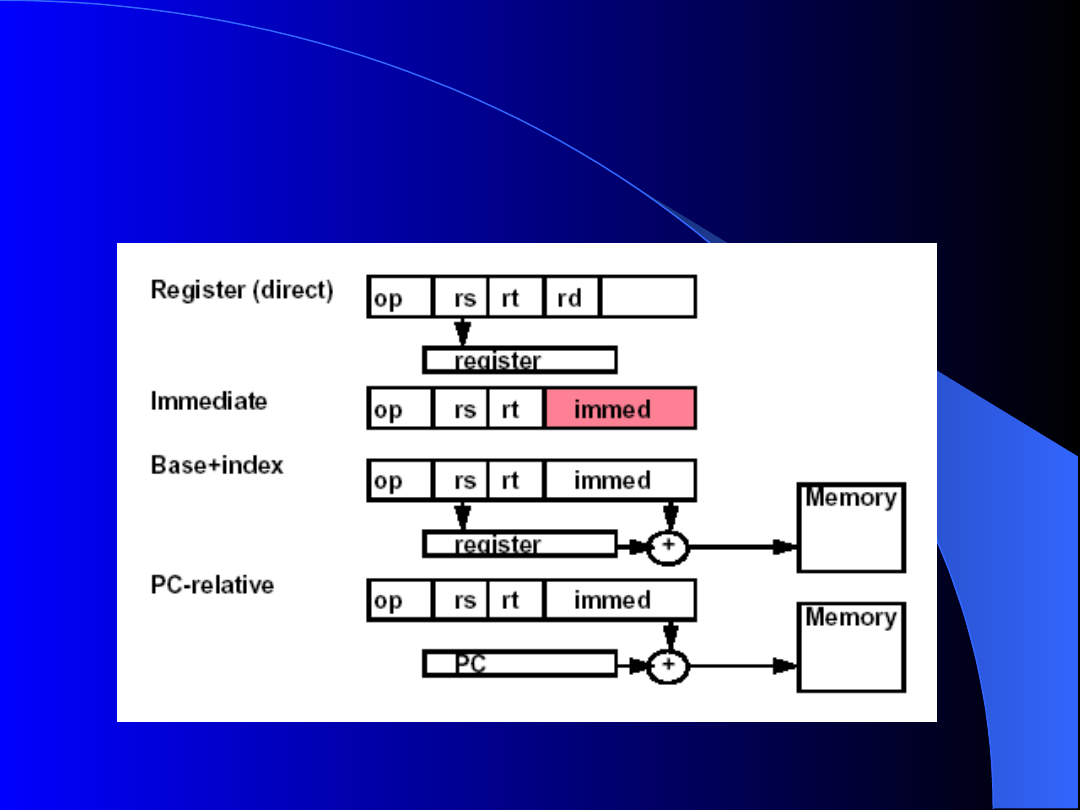

KOMPUTER – TRYBY

KOMPUTER – TRYBY

ADRESOWANIA

ADRESOWANIA

Adresowanie zeroelementowe – adresowanie

bezpośrednie adres niejawny:

–

Błyskawiczne – kod danej jest częścią kodu rozkazu

–

Natychmiastowe – za pomocą licznika rozkazów. Kod

danej lub jego rozszerzenie jest umieszczony w pamięci

bezpośrednio po kodzie rozkazu.

Adresowanie jednoelementowe bezpośrednie

–

Bezwzględne – skrócony adres danej w kodzie rozkazu

lub pełny adres danej w rozszerzeniu kodu rozkazu

–

Rejestrowe pośrednie – argument umieszczony w

rejestrze, identyfikowanym w kodzie rozkazu

KOMPUTER – TRYBY

KOMPUTER – TRYBY

ADRESOWANIA

ADRESOWANIA

Adresowanie jednoelementowe pośrednie

–

Bezwzględne pośrednie – adres danej jest słowem

rozszerzenia kodu rozkazu

–

Rejestrowe pośrednie – adres danej umieszczony w

rejestrze identyfikowanym w kodzie rozkazu

–

Rejestrowe pośrednie z modyfikacją – adres danej

w rejestrze jest automatycznie zwiększany

(inkrementacja) lub zmniejszany (dekrementacja) po

użyciu (postinkrementacja i postdekrementacja) lub

przed użyciem (preinkremntacja i predekrementacja)

KOMPUTER – TRYBY

KOMPUTER – TRYBY

ADRESOWANIA

ADRESOWANIA

Adresowanie wieloelementowe

jednopoziomowe (pośrednie) – suma

składowych adresu wyznacza adres danej w

pamięci.

Adresowanie wieloelementowe

dwupoziomowe (pośrednie)

–

Bazowe z przemieszczeniem

–

Indeksowe z przemieszczeniem

–

Bazowo – indeksowe

–

Względne z przemieszczeniem – bazą jest zawartość

licznika rozkazów

–

Względne indeksowe

KOMPUTER – TRYBY

KOMPUTER – TRYBY

ADRESOWANIA

ADRESOWANIA

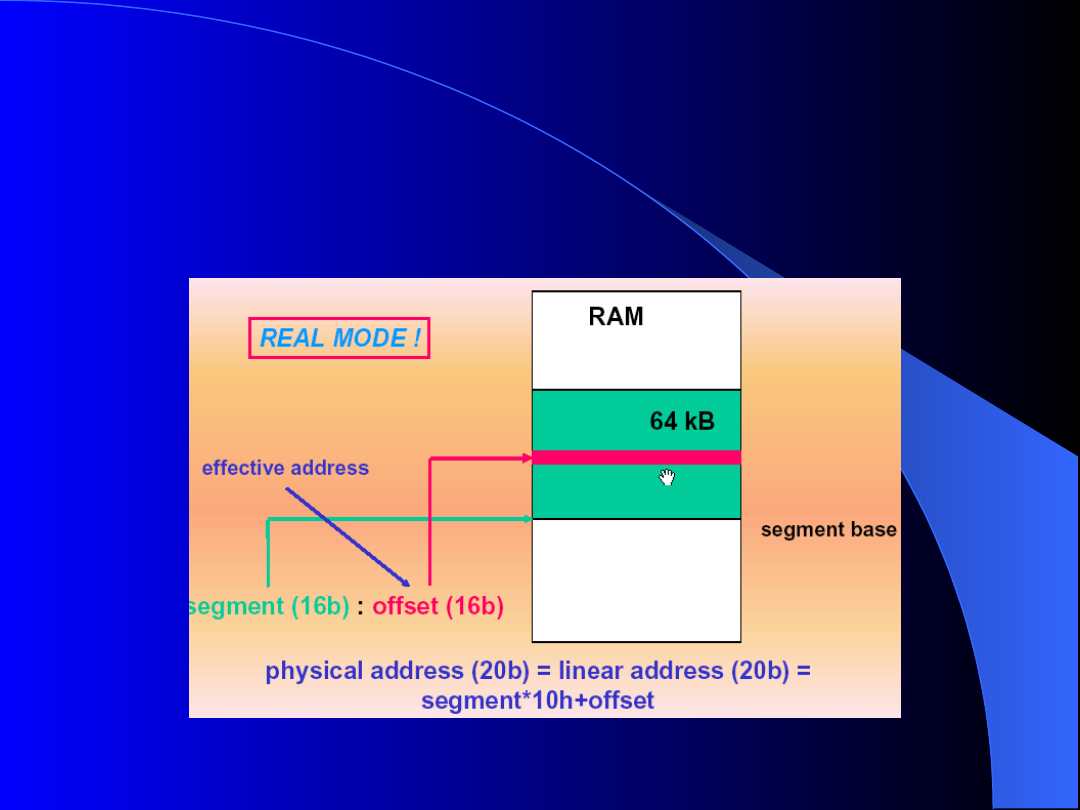

W architekturze Intel 80x86 zaadresowanie danej w

pamięci wymaga dwóch wskaźników: identyfikatora

spójnego bloku pamięci zwanego segmentem i

adresu względnego wewnątrz segmentu o wartości

nie przekraczającej rozmiaru segmentu.

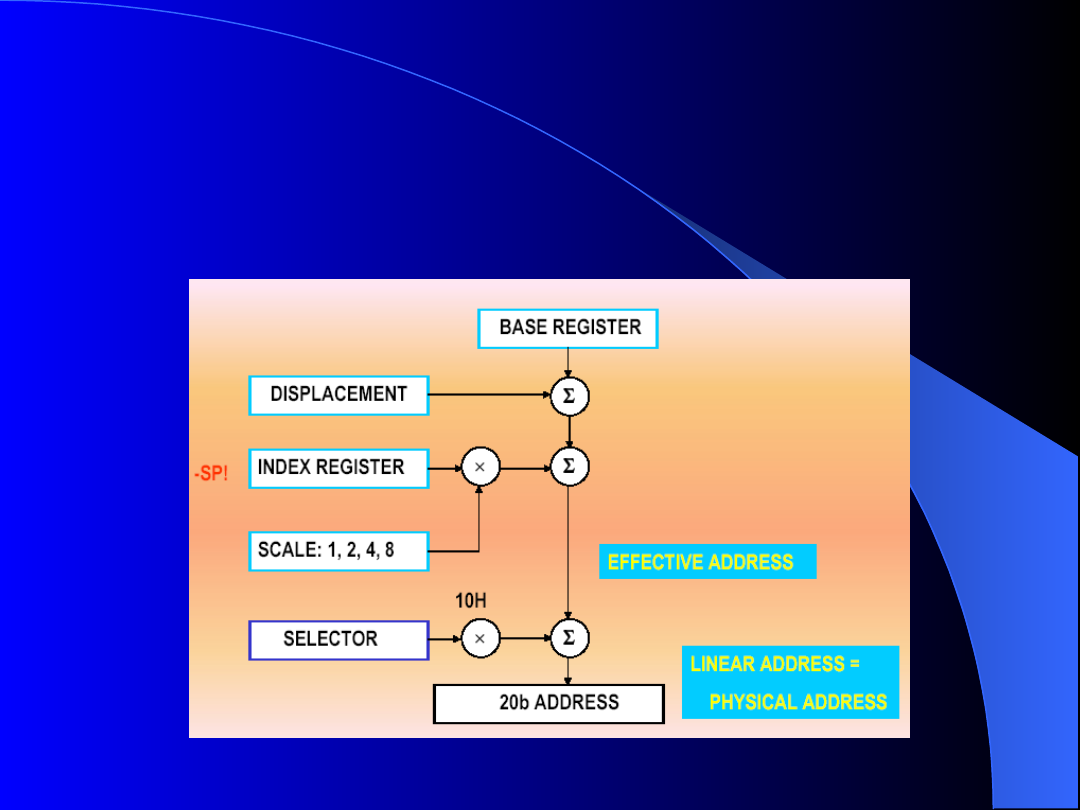

Najbardziej złożonym trybem adresowania

spotykanym w procesorach rodziny Intel 80x86 jest

dwuwskaźnikowe skalowalne adresowanie bazowo-

indeksowe z przemieszczeniem

LA=([wskaźnik segmentu])+(baza)+

(indeks)*skala+przemieszczenie

Nawias [...] oznacza adres pośredni, a nawias (...) oznacza,

że składowa adresu umieszczona jest w rejestrze procesora

KOMPUTER – TRYBY

KOMPUTER – TRYBY

ADRESOWANIA

ADRESOWANIA

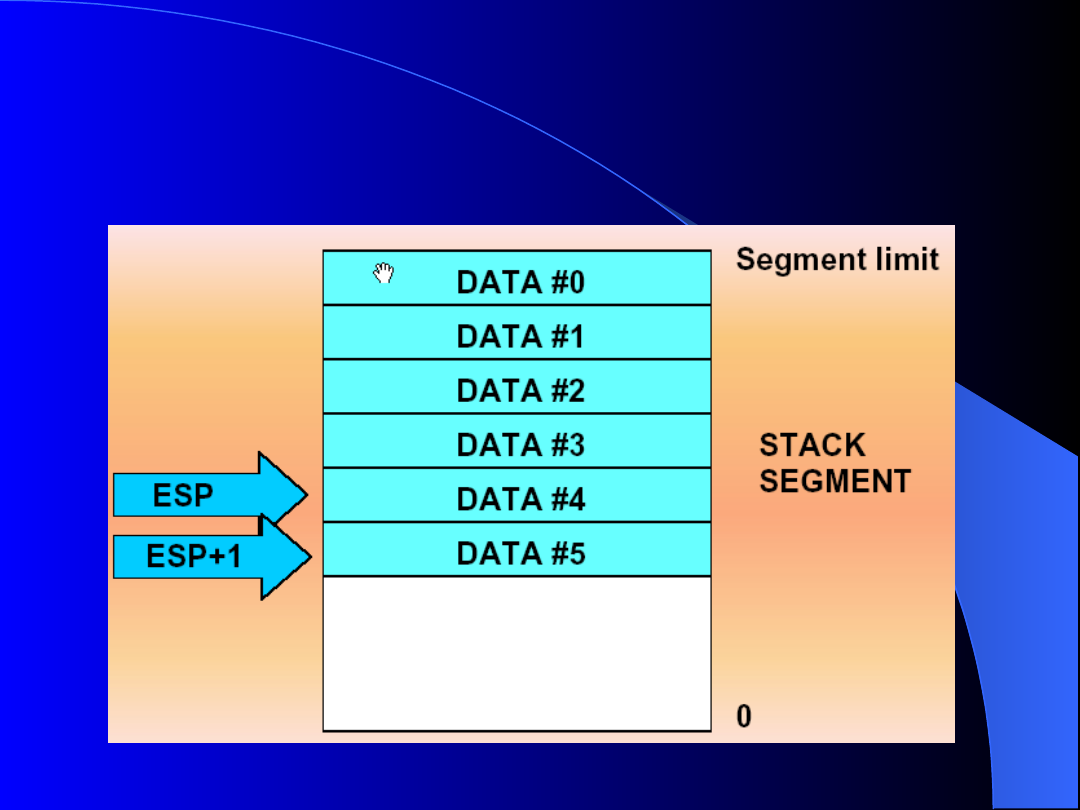

Stos programowy LIFO

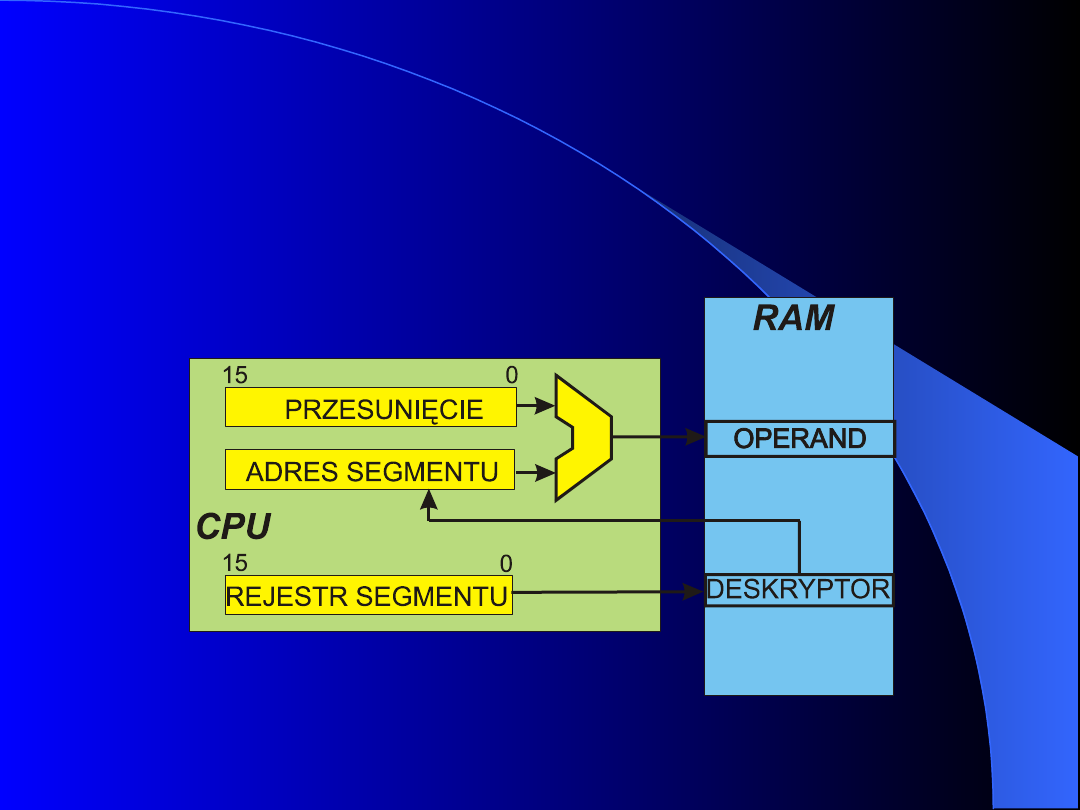

Adresowanie opisowe (deskryptorowe) – cechą

szczególną tego trybu adresowania jest odniesienie

wszystkich adresów spójnego obszaru pamięci do

adresu bazowego wyznaczonego na podstawie

deskryptora lokalizowanego poprzez wskaźnik.

Oprócz adresu bazowego opis zawiera również

informację umożliwiające realizację selektywnego

dostępu do bloku. Zaletą tej metody adresowania jest

elastyczne adresowanie zmiennych strukturalnych

przy jednoczesnym zapewnieniu prywatności. Taki

sposób adresowania jest stosowany przy realizacji

mechanizmów pamięci wirtualnej.

KOMPUTER – TRYBY

KOMPUTER – TRYBY

ADRESOWANIA

ADRESOWANIA

KOMPUTER – TRYBY

KOMPUTER – TRYBY

ADRESOWANIA

ADRESOWANIA

TRYB RZECZYWISTY

KOMPUTER – TRYBY

KOMPUTER – TRYBY

ADRESOWANIA

ADRESOWANIA

TRYB RZECZYWISTY

KOMPUTER – TRYBY

KOMPUTER – TRYBY

ADRESOWANIA

ADRESOWANIA

TRYB WIRTUALNY

KOMPUTER -

KOMPUTER -

ADRESOWANIE

ADRESOWANIE

STOS PROGRAMOWY (LIFO)

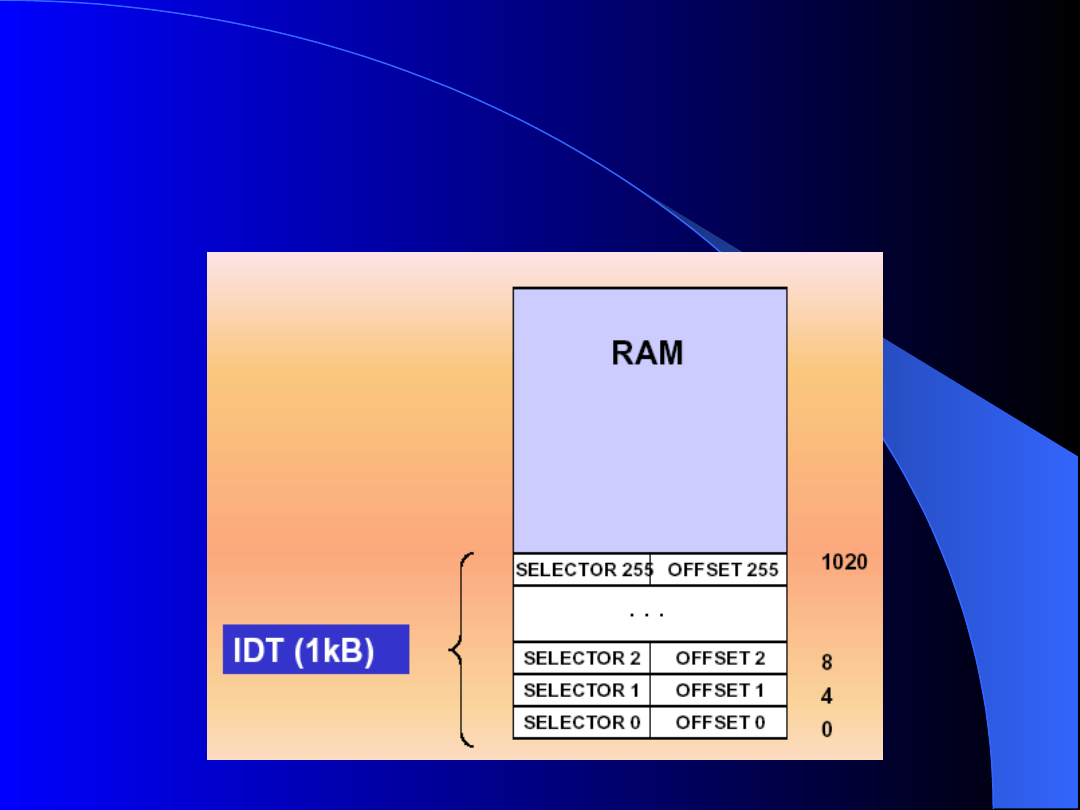

KOMPUTER –

KOMPUTER –

ADRESOWANIE

ADRESOWANIE

TABLICA WEKTORÓW PRZERWAŃ

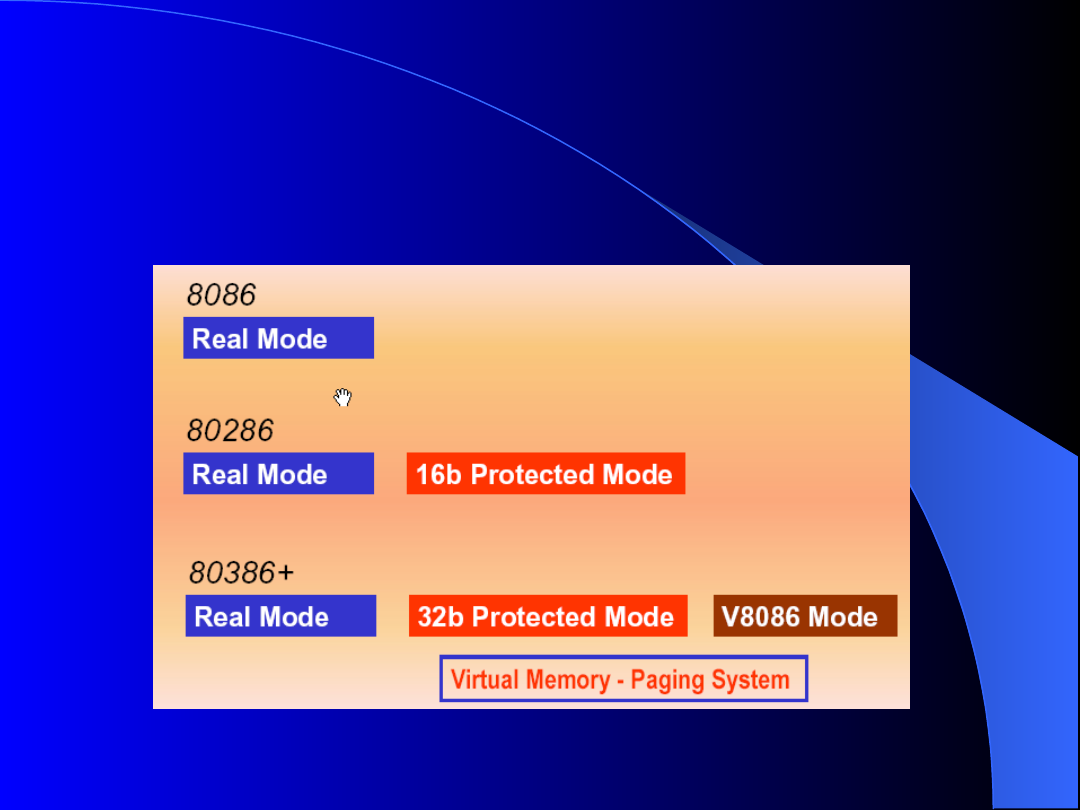

KOMPUTER – TRYBY

KOMPUTER – TRYBY

WIRTUALNY

WIRTUALNY

TRYB WIRTUALNY

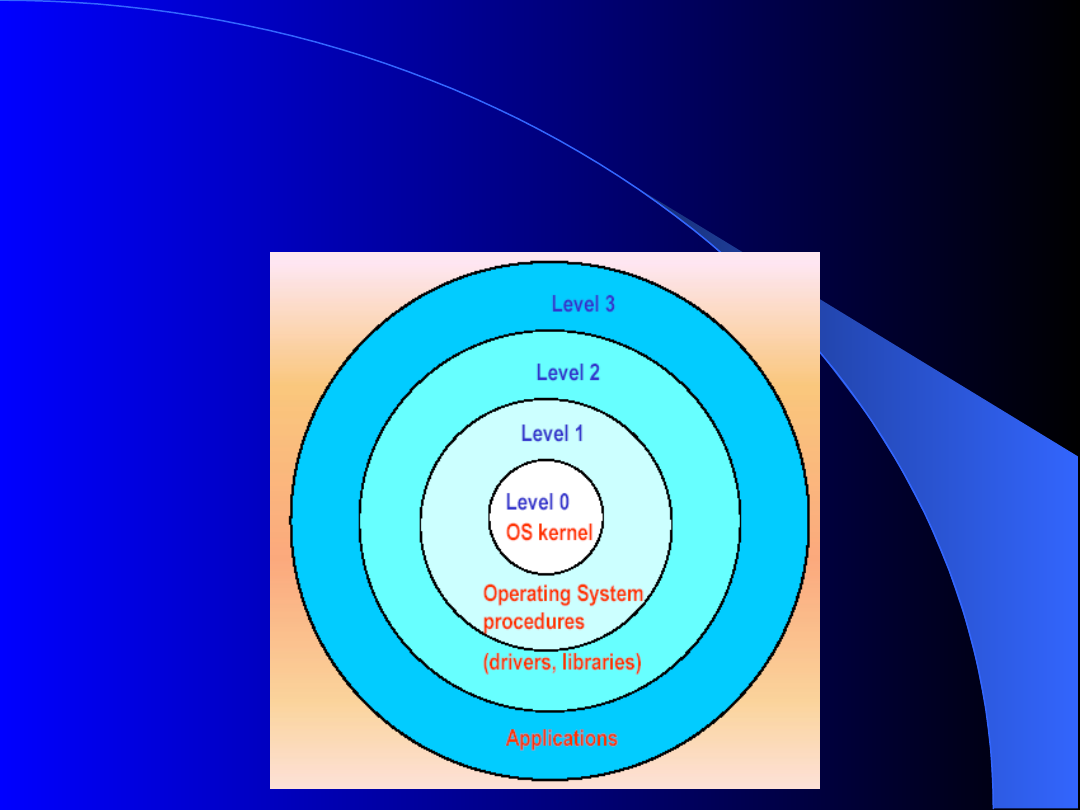

KOMPUTER – TRYBY

KOMPUTER – TRYBY

WIRTUALNY

WIRTUALNY

POZIOMY UPRZYWILEJOWANIA

Document Outline

- Slide 1

- Slide 2

- Slide 3

- Slide 4

- Slide 5

- Slide 6

- Slide 7

- Slide 8

- Slide 9

- Slide 10

- Slide 11

- Slide 12

- Slide 13

- Slide 14

- Slide 15

- Slide 16

- Slide 17

- Slide 18

- Slide 19

- Slide 20

- Slide 21

- Slide 22

- Slide 23

- Slide 24

- Slide 25

- Slide 26

- Slide 27

- Slide 28

- Slide 29

- Slide 30

- Slide 31

- Slide 32

- Slide 33

- Slide 34

- Slide 35

- Slide 36

- Slide 37

- Slide 38

- Slide 39

- Slide 40

- Slide 41

- Slide 42

- Slide 43

- Slide 44

- Slide 45

- Slide 46

- Slide 47

- Slide 48

- Slide 49

- Slide 50

- Slide 51

- Slide 52

- Slide 53

- Slide 54

- Slide 55

- Slide 56

- Slide 57

- Slide 58

- Slide 59

- Slide 60

- Slide 61

- Slide 62

- Slide 63

- Slide 64

- Slide 65

- Slide 66

- Slide 67

- Slide 68

- Slide 69

- Slide 70

- Slide 71

- Slide 72

- Slide 73

- Slide 74

- Slide 75

- Slide 76

- Slide 77

- Slide 78

Wyszukiwarka

Podobne podstrony:

architektury komputerow v1 1

Architektura Komputera, Informatyka, Płyta Główna

Architektury Komputerów zagadnienia

Architektura komputerów I 16 12 2008

gulczas 2001 opracowanie, Politechnika Wrocławska - Materiały, architektura komputerow 2, egzamin, o

Architektura komputerów I 09 12 2008

Architektura komputerów i systemy operacyjne

Architektura Komputerów wiedza ogólna

ak projekt, Studia, PWR, 4 semestr, Architektura komputerów 2, projekt

Tematy cwiczen, Architektóra komputerów

ako pytania zadania cz2 2010, Studia - informatyka, materialy, Architektura komputerów

Architektura komputerów I 25 11 2008

Architektura Komputerow lista 3

AK test, stud, IV semestr, Architektura Komputerow

Podstawy architektury komputera, Szkoła, Systemy Operacyjnie i sieci komputerowe, utk, semestr II

lista3 rozwiązania, Politechnika Wrocławska - Materiały, architektura komputerow 1, Rozwiazania lis

Sciaga 3 - Architektura, szkola, architektura komputerow

więcej podobnych podstron