Pamięć wewnętrzna

Wyższa Szkoła Biznesu

Architektura i organizacja

komputerów

Wykład 5

Wprowadzenie

Pamięć komputera, pozornie prostą koncepcyjnie,

cechuje najszerszy zakres rodzajów, technologii,

organizacji, wydajności i kosztów w stosunku do

pozostałych składników.

Nie istnieje jedna technologia, która optymalnie

spełniałaby wymagania systemu komputerowego

dotyczące pamięci. W rezultacie typowy system

komputerowy zawiera hierarchię podsystemów

pamięci: niektóre z nich są wewnętrzne w stosunku

do systemu (bezpośrednio dostępne dla procesora),

a inne zewnętrzne (dostępne dla procesora poprzez

moduł wejścia-wyjścia).

Położenie

Rozpoczynamy

od

najłatwiej

dostrzegalnego

aspektu pamięci: jej położenia. Jak sugerują tytuł

wykładu, istnieją pamięci zarówno wewnętrzne, jak

i zewnętrzne w stosunku do komputera.

Pamięć wewnętrzna jest często identyfikowana z

pamięcią główną. Są jednak inne formy pamięci

wewnętrznej np.. procesor wymaga własnej

pamięci lokalnej w postaci rejestrów, stanowiąca

część procesora jednostka sterująca może również

potrzebować własnej pamięci wewnętrznej.

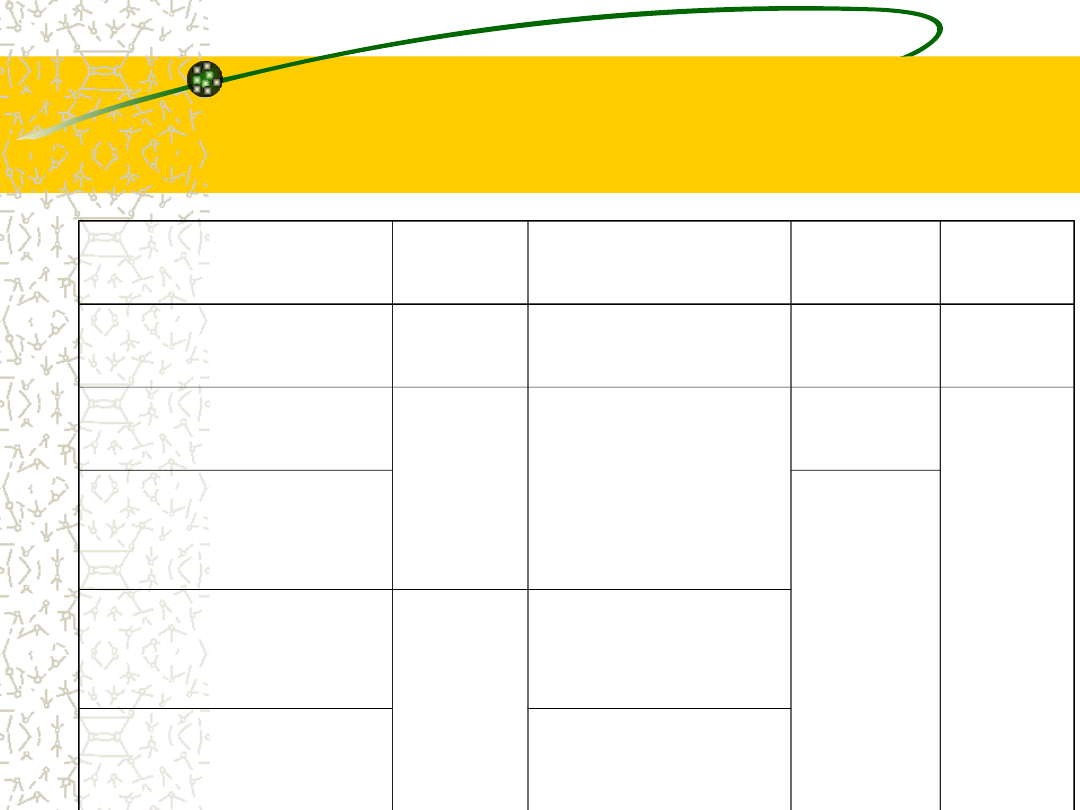

Podstawowe własności

komputerowych systemów

pamięciowych

Położenie

Pojemność

Procesor

Rozmiar słowa

Wewnętrzna (główna)

Liczba słów

Zewnętrzna (pomocnicza)

Jednostka transferu

Sposób dostępu

Słowo

Sekwencyjny

Blok

Bezpośredni

Rodzaj fizyczny

Swobodny

Półprzewodnikowa

Skojarzeniowy

Magnetyczna

Wydajność

Właściwości fizyczne

Czas dostępu

Ulotna/nieulotna

Czas cyklu

Wymazywalne/niewymazywalna

Szybkość transferu

Organizacja

Pojemność

Oczywistą własnością pamięci jest jej

pojemność.

W przypadku pamięci wewnętrznej jest ona

zwykle wyrażana w bajtach (1 bajt = 8

bitów) lub w słowach. Powszechnymi

długościami słów są: 8, 16 i 32 bity.

Pojemność pamięci zewnętrznej jest zwykle

wyrażana w bajtach.

Jednostka transferu

Parametrem związanym z pojemnością

jest

jednostka

transferu

(ang.

transfer unit).

W przypadku pamięci wewnętrznej

jednostka transferu jest równa liczbie

linii danych doprowadzonych do modułu

pamięci i wychodzących z niego.

Jest ona często równa długości słowa,

ale nie musi tak być.

Słowo, Jednostka

adresowalna

Słowo. „Naturalna” jednostka organizacji pamięci.

Zwykle rozmiar słowa jest równy liczbie bitów

wykorzystywanych do reprezentowania liczby lub długości

rozkazu. Niestety, jest wiele wyjątków. Na przykład CRAY-

1 wykorzystuje słowa 64-bitowe, jednak liczba całkowita

jest reprezentowana za pomocą 24 bitów. VAX ma

zdumiewająco różne długości rozkazów, wyrażone jako

wielokrotności bajtów, a rozmiar słowa wynosi 32 bity.

Jednostka adresowalna. W wielu systemach jednostką

adresowalną jest słowo. Jednak niektóre systemy

umożliwiają adresowanie na poziomie bajtów. W każdym

przypadku zależność między długością adresu A a liczbą

adresowalnych jednostek N jest następująca: 2

A

=N.

Jednostka transferu

Jednostka

transferu.

W

przypadku

pamięci głównej jest to liczba bitów

jednocześnie odczytywanych z pamięci lub

do niej zapisywanych.

Jednostka transferu nie musi być równa

słowu lub jednostce adresowalnej.

W przypadku pamięci zewnętrznej dane są

często przekazywane w jednostkach o wiele

większych niż słowo, określanych jako bloki.

Sposób dostępu

Jedna z najbardziej widocznych różnic między

różnymi rodzajami pamięci dotyczy sposobu

dostępu do jednostek danych. Można

wyróżnić cztery rodzaje dostępu:

dostęp sekwencyjny;

dostęp bezpośredni;

dostęp swobodny;

dostęp skojarzeniowy.

Dostęp sekwencyjny

Pamięć jest zorganizowana za pomocą jednostek danych

zwanych rekordami.

Dostęp jest możliwy w określonej sekwencji liniowej. Do

oddzielania rekordów i do pomocy przy odczycie są

wykorzystywane przechowywane informacje adresowe.

Odczyt i zapis są wykonywane za pomocą tego samego

mechanizmu, przy czym proces ten musi się przenosić z

pozycji bieżącej do pozycji pożądanej, przepuszczając i

odrzucając każdy rekord pośredni. W rezultacie czas

dostępu do różnych rekordów może się bardzo różnić.

Pamięci taśmowe (o których będzie mowa przy

omawianiu pamięci zewnętrznych), charakteryzują się

właśnie dostępem sekwencyjnym.

Dostęp bezpośredni

Podobnie jak w przypadku dostępu sekwencyjnego, proces

odczytu i zapisu w pamięciach o dostępie bezpośrednim

jest realizowany za pomocą tego samego mechanizmu.

Jednak poszczególne bloki lub rekordy mają unikatowy

adres oparty na lokacji fizycznej.

Dostęp jest realizowany przez bezpośredni dostęp do

najbliższego otoczenia, po którym następuje sekwencyjne

poszukiwanie, liczenie lub oczekiwanie w celu osiągnięcia

lokacji finalnej.

Jak poprzednio czas dostępu jest zmienny. Pamięci

dyskowe (które omówimy na wykładzie „pamięci

zewnętrzne”), charakteryzują się dostępem bezpośrednim.

Dostęp swobodny

Każda adresowalna lokacja w pamięci ma

unikatowy, fizycznie wbudowany mechanizm

adresowania.

Czas dostępu do danej lokacji nie zależy od

sekwencji poprzednich operacji dostępu i jest stały.

Dzięki temu dowolna lokacja może być wybierana

swobodnie

i

jest

adresowana

i

dostępna

bezpośrednio.

Systemy pamięci głównej wyróżniają się

dostępem swobodnym.

Dostęp skojarzeniowy

Jest to rodzaj dostępu swobodnego, który umożliwia

porównywanie

i

specyficzne

badanie

zgodności

wybranych bitów wewnątrz słowa, przy czym jest to

czynione dla wszystkich słów jednocześnie.

Tak więc słowo jest wyprowadzane raczej na podstawie

części swojej zawartości niż na podstawie adresu.

Podobnie jak w przypadku zwykłych pamięci o dostępie

swobodnym, każda lokacja ma własny mechanizm

adresowania, a czas dostępu jest stały i niezależny od

poprzednich operacji dostępu.

W pamięciach podręcznych, które omówimy w dalszej

części wykładu, może być używany dostęp skojarzeniowy.

Wydajność

Z punktu widzenia użytkownika dwiema

najważniejszymi własnościami pamięci są

pojemność

i

wydajność.

Wykorzystywane

są

trzy

parametry

będące miarą wydajności:

Czas dostępu;

Czas cyklu pamięci;

Szybkość przesyłania (transferu).

Czas dostępu

W przypadku pamięci o dostępie swobodnym

jest to czas niezbędny do zrealizowania

operacji odczytu lub zapisu, to znaczy czas

od chwili doprowadzenia adresu do chwili

zmagazynowania lub udostępnienia danych.

W

przypadku

pamięci

o

dostępie

nieswobodnym czas dostępu jest czasem

potrzebnym na umieszczenie mechanizmu

odczytu-zapisu w pożądanym miejscu.

Czas cyklu pamięci

Pojęcie to było pierwotnie stosowane do

pamięci o dostępie swobodnym.

Czas cyklu składa się z czasu dostępu oraz

z dodatkowego czasu, który musi upłynąć,

zanim będzie mógł nastąpić kolejny dostęp.

Ten dodatkowy czas może być potrzebny

dla zaniku sygnałów przejściowych lub do

regeneracji danych, jeśli odczyt jest

niszczący.

Szybkość przesyłania

(transferu)

Jest to szybkość, z jaką dane mogą być wprowadzane

do jednostki pamięci lub z niej wyprowadzane.

W przypadku pamięci o dostępie swobodnym jest ona

równa 1/(czas cyklu).

W przypadku pamięci o dostępie nieswobodnym

zachodzi następująca zależność:

gdzie:

T

N

– średni czas odczytu lub zapisu N bajtów

T

A

– średni czas dostępu

R – szybkość transferu w bitach na sekundę

R

N

T

T

A

N

Fizyczny rodzaj pamięci

Wykorzystywane są różne fizyczne rodzaje

pamięci. Dwa najbardziej powszechne

spośród nich obecnie to:

pamięć

półprzewodnikowa,

wykonana w technologii LSI lub VLSI, oraz

powierzchniowa

pamięć

magnetyczna w postaci dysków i taśm.

Własności fizyczne

W pamięci ulotnej informacja zanika naturalnie lub jest

tracona po wyłączeniu zasilania.

W pamięci nieulotnej informacja raz zapisana nie zmienia się

aż do chwili zamierzonej zmiany; zasilanie elektryczne nie jest

niezbędne do zachowania informacji.

– Powierzchniowe pamięci magnetyczne są nieulotne.

– Pamięć półprzewodnikowa może być albo ulotna, albo

nieulotna.

Zawartość pamięci niewymazywalnej nie może być

zmieniana, z wyjątkiem wypadku zniszczenia jednostki

pamięciowej. Pamięć półprzewodnikowa tego typu jest znana

jako pamięć stała (ang. read-only memory - ROM).

– Z konieczności pamięć niewymazywalna musi być także

nieulotna.

Organizacja

W

przypadku

pamięci

o

dostępie

swobodnym podstawowym problemem

przy projektowaniu jest organizacja.

Przez

organizację

rozumiemy tutaj

fizyczne uporządkowanie bitów w celu

uformowania słów. Jak wyjaśnimy, nie

zawsze

wykorzystywane

jest

uporządkowanie,

które

wydaje

się

oczywiste.

Ile? Jak szybko? Za ile?

Ograniczenia przy projektowaniu pamięci komputera mogą być

podsumowane za pomocą trzech pytań: Ile? Jak szybko? Za ile?

Pytanie „Ile?” jest wciąż w pewnym stopniu otwarte. Jeśli

dysponujemy określoną pojemnością, to z pewnością pojawi się

zastosowanie, w którym pojemność ta zostanie wykorzystana.

Odpowiedź na pytanie „Jak szybko?" jest w pewnym sensie

łatwiejsza. Aby osiągnąć największą wydajność, pamięć musi

być w stanie nadążyć za procesorem. Znaczy to, że nie

chcielibyśmy, aby procesor, wykonując rozkazy, czekał na

rozkazy lub argumenty.

Ostatnie z pytań również musi być rozważone. W przypadku

praktycznego systemu koszt pamięci musi pozostawać w

rozsądnej relacji do kosztu pozostałych składników.

Dylematy projektanta

Jak można było się spodziewać, istnieją wzajemne zależności między

podstawowymi parametrami pamięci, to znaczy między kosztem,

pojemnością i czasem dostępu. Jak zawsze przy konstruowaniu

systemów pamięciowych są wykorzystywane różne technologie. Jeśli

rozpatrujemy dostępne technologie, to zauważamy następujące

zależności:

mniejszy czas dostępu - większy koszt na bit,

większa pojemność - mniejszy koszt na bit,

większa pojemność - większy czas dostępu.

Dylemat, przed którym stoi projektant, jest jasny. Chciałby on

wykorzystać technologie pamięci, które umożliwiają wytworzenie

pamięci o dużej pojemności, ponieważ po pierwsze są one potrzebne,

a po drugie z powodu mniejszego kosztu na bit. Jednak aby osiągnąć

wymaganą wydajność, projektant wykorzystuje drogie i stosunkowo

małej pojemności pamięci o krótkim czasie dostępu.

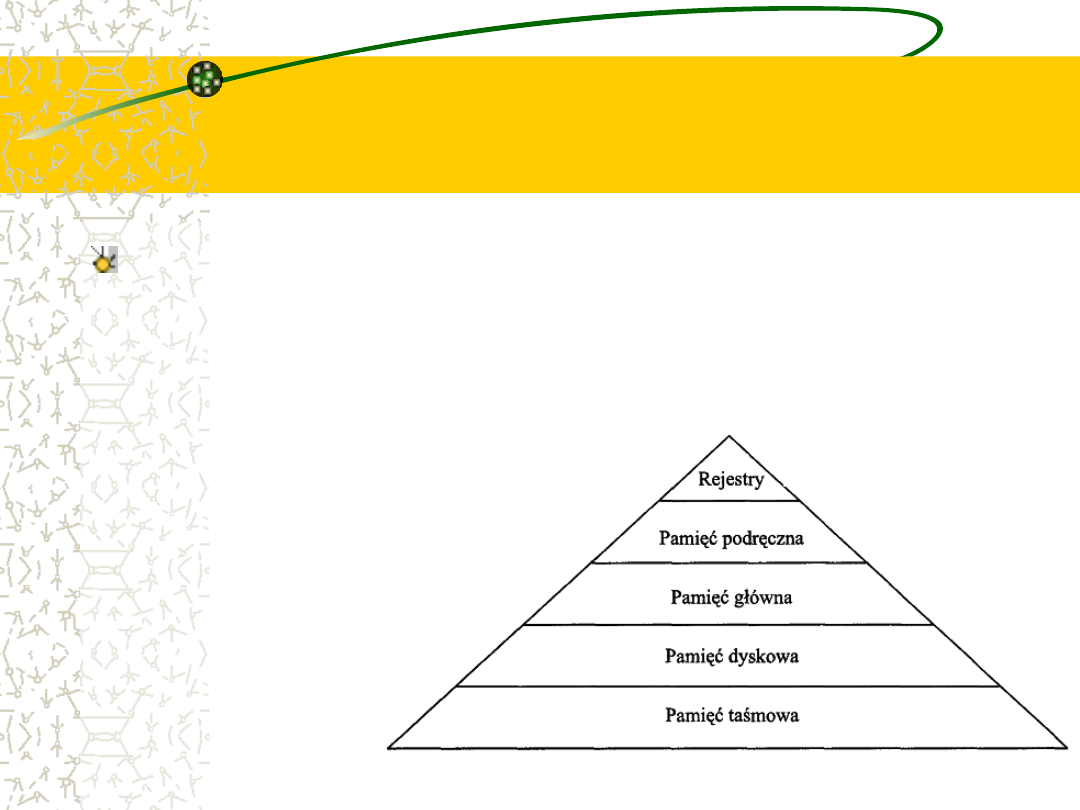

Hierarchia pamięci

Osiągnięcie kompromisu nie polega na wyborze

pojedynczego zespołu pamięci czy też określonej

technologii, lecz na wykorzystaniu hierarchii

pamięci. Rozpatrując tę hierarchię w kierunku od

góry do dołu, obserwujemy następujące zjawiska:

a) malejący koszt na bit,

b) rosnąca pojemność,

c) rosnący czas dostępu,

d) malejącą

częstotliwość

dostępu

do

pamięci

przez procesor.

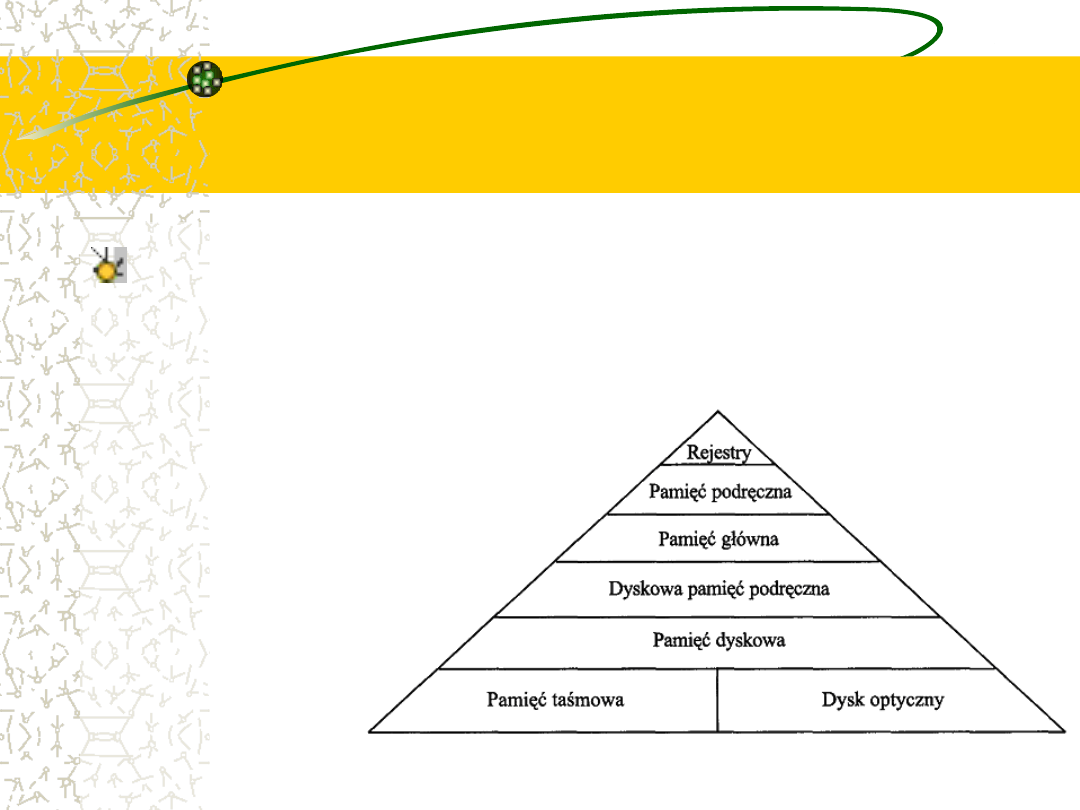

Współczesna hierarchia

pamięci

Jeśliby pamięć mogła być zorganizowana

przy uwzględnieniu zjawisk (a), (b) oraz (c)

i jeśli dane i rozkazy byłyby rozmieszczone

w pamięci przy uwzględnieniu (d), to

sądzimy

intuicyjnie,

że

taki

schemat

zredukowałby

łączne

koszty,

pozostawiając

określony

poziom

wydajności.

Przykład

Załóżmy, że procesor ma dostęp do dwóch poziomów

pamięci. Poziom pierwszy zawiera 1000 słów i ma czas

dostępu 1μs.

Poziom 2 zawiera 100 000 słów i ma czas dostępu 10μs.

Załóżmy dalej, że jeśli poszukiwane słowo znajduje się na

poziomie 1, to procesor ma do niego dostęp bezpośredni.

Jeśli natomiast jest ono na poziomie 2, to słowo jest

najpierw przenoszone na poziom 1, a następnie

udostępniane procesorowi.

Dla uproszczenia zaniedbajmy czas wymagany do tego,

aby procesor określił, czy słowo znajduje się na

pierwszym, czy też na drugim poziomie.

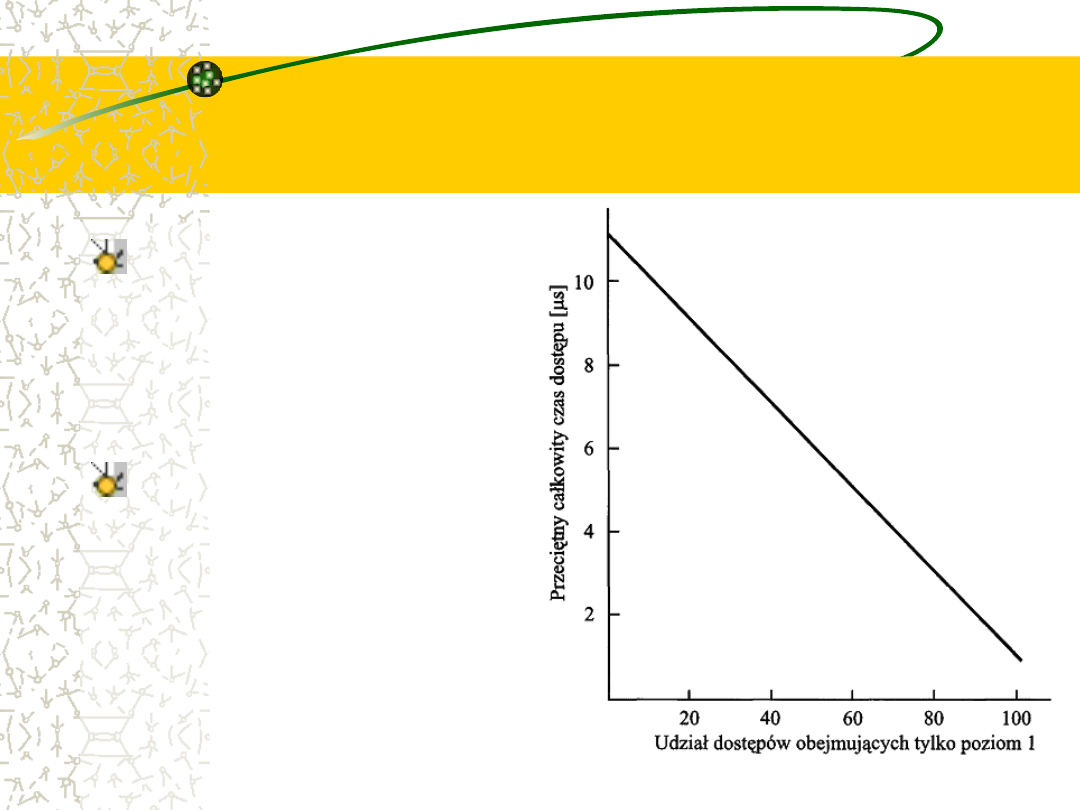

Przykład

Na rysunku jest pokazany

średni

całkowity

czas

dostępu

jako

funkcja

procentu czasu, w ciągu

którego

słowo

jest

znajdywane od razu na

poziomie 1.

Jak można zauważyć, przy

wysokim

udziale

bezpośrednich dostępów do

poziomu 1, średni całkowity

czas dostępu jest o wiele

bliższy

temu

czasowi

charakterystycznemu

dla

poziomu 1 niż dla 2.

Lokalność odniesień

Podstawą słuszności warunku (d) jest zasada lokalności

odniesień (locality of reference).

Podczas wykonywania programu odniesienia do pamięci

(zarówno dotyczące danych, jak i rozkazów) mają tendencję

do gromadzenia się. Programy typowo zawierają pewną

liczbę pętli iteracyjnych i podprogramów.

Gdy jest uruchomiona pętla lub podprogram, występują

powtarzające się odniesienia do niewielkiego zestawu

rozkazów. Podobnie, operacje na tablicach lub ciągach

danych polegają na dostępie do zgrupowanego zespołu słów.

W ciągu długiego czasu wykorzystywane ugrupowania

zmieniają się, jednak w krótkim czasie procesor pracuje z

ustalonymi grupami odniesień do pamięci.

Przykład cd.

W tej sytuacji jest możliwa taka organizacja układu danych w

hierarchii pamięci, żeby udział dostępów do każdego kolejnego

niższego poziomu był istotnie mniejszy niż do poziomu wyższego.

Rozpatrzmy dwupoziomowy przykład przedstawiony powyżej.

Przyjmijmy, że poziom 2 pamięci zawiera wszystkie rozkazy i

dane programu.

Bieżące ugrupowania danych mogą być czasowo umieszczane na

poziomie 1. Od czasu do czasu niektóre ugrupowania danych

będą musiały być przenoszone na poziom 2, żeby zwolnić

miejsce dla nowych zbiorów wprowadzanych do poziomu 1.

Przeciętnie jednak większość odniesień będzie dotyczyła

rozkazów i danych zawartych na poziomie 1.

Zasada ta może być stosowana do systemów zawierających

więcej niż dwa poziomy.

Organizacja hierarchii

pamięci

Najszybszy, najmniejszy i najdroższy rodzaj pamięci obejmuje

rejestry zawarte wewnątrz procesora. Typowo procesor zawiera

kilka tuzinów takich rejestrów, chociaż niektóre maszyny mają

ich setki.

Dwa poziomy niżej znajduje się pamięć główna, będąca

zasadniczym wewnętrznym systemem pamięciowym komputera.

Każda lokacja w pamięci głównej ma swój unikatowy adres, a

większość rozkazów maszynowych odnosi się do jednego lub

wielu adresów w pamięci głównej.

Pamięć główna jest zwykle poszerzana za pomocą szybszej i

mniejszej pamięci podręcznej. Ta ostatnia nie jest zwykle

widzialna dla programisty czy też, w istocie, dla procesora.

Urządzenie to stopniuje przepływ danych między pamięcią

główną a rejestrami procesora i ma na celu poprawienie

wydajności.

Organizacja hierarchii

pamięci

Trzy opisane wyżej rodzaje pamięci są zwykle ulotne i są

wykonane w technologii półprzewodnikowej. Zastosowanie

układu trójpoziomowego pozwala na wykorzystanie dostępnych

obecnie typów pamięci półprzewodnikowych różniących się

szybkością i kosztem.

Dane są przechowywane w sposób trwalszy w zewnętrznych,

masowych

urządzeniach

pamięciowych,

z

których

najpowszechniejsze są pamięci dyskowe i taśmowe. Do innych

postaci pamięci wtórnych należą dyski optyczne

Zewnętrzne pamięci nieulotne są określane jako pamięci wtórne

lub pomocnicze. Są używane do przechowywania programów i

plików danych; programista widzi je tylko poprzez pliki i rekordy,

a nie przez pojedyncze bajty czy słowa. Dyski są także

wykorzystywane do rozszerzania pamięci głównej, jako pamięci

wirtualne.

Bufory tymczasowego

przechowywania danych

Dodatkowe poziomy mogą być skutecznie dodane do hierarchii

za pomocą oprogramowania. Część pamięci głównej może być

wykorzystywana jako bufor do tymczasowego przechowywania

danych, które następnie mają być odczytane i wyprowadzone

na dysk. Taka technika, określana czasem jako dyskowa pamięć

podręczna , poprawia wydajność na dwa sposoby:

Zapisy dyskowe są zgrupowane. W miejsce wielu transferów

niewielkich ilości danych mamy do czynienia z niewieloma

wielkimi transferami. Poprawia to wydajność dysku i

minimalizuje zaangażowanie procesora.

Pewne dane przeznaczone do odczytania mogą być określone

przez program jeszcze przed następnym sięgnięciem do dysku.

W tym przypadku dane te mogą być wydobyte szybko z

programowej pamięci podręcznej, a nie powoli z dysku.

Pamięć główna

We wcześniejszych komputerach najpowszechniejszą

formą komputerowych pamięci głównych o swobodnym

dostępie były zespoły pierścieni ferromagnetycznych

nazywanych rdzeniami. Dlatego też pamięci główne

tego rodzaju były nazywane rdzeniowymi.

Termin ten funkcjonuje do dziś. Dość długo trwało,

zanim

nadejście

mikroelektroniki

i

jej

zalety

spowodowały

ustąpienie

rdzeniowych

pamięci

magnetycznych.

Dzisiaj

zastosowanie

mikroukładów

półprzewodnikowych w pamięciach głównych jest

prawie uniwersalne.

Rodzaje pamięci

półprzewodnikowych o

dostępie swobodnym

Wszystkie rodzaje pamięci rozpatrywane w tej części

charakteryzują się dostępem swobodnym. Znaczy to, że

pojedyncze słowa w pamięci są dostępne bezpośrednio za

pomocą wbudowanych układów logicznych adresowania.

W tabeli (następny slajd) są wymienione główne rodzaje

pamięci

półprzewodnikowych.

Najpowszechniejsza

jest

określana jako pamięć o dostępie swobodnym (RAM).

Oczywiście jest to niewłaściwe wykorzystanie tego określenia,

ponieważ wszystkie rodzaje pamięci wymienione w tablicy są

pamięciami o dostępie swobodnym. Cechą wyróżniającą

pamięci RAM jest to, że możliwe jest zarówno odczytanie

danych z pamięci, jak też łatwe i szybkie zapisanie do niej

nowych danych. Zarówno odczyt, jak i zapis są dokonywane

za pomocą sygnałów elektrycznych.

Rodzaje pamięci

półprzewodnikowych

Rodzaj pamięci

Kateg

oria

Wymazywanie Sposób

zapisu

Ulotno

ść

Pamięć o dostępie

swobodnym (RAM)

odczyt-

zapis

elektryczne, na

poziomie bajta

elektryc

zny

ulotna

Pamieć

stała

(ROM)

tylko

odczyt

Niemożliwe

maski

nieulot

ne

Programowalna

pamięć

stała

(PROM)

elektryc

zny

Wymazywalna

PROM (EPROM)

główni

e

odczyt

światłem

UV,

na

poziomie

mikroukładu

Pamięć

błyskawiczna

(FLASH)

elektryczne, na

poziomie bloku

Elektrycznie

wymazywalna

PROM (EEPROM)

elektryczne, na

poziomie bajta

Ulotność, pamięć

statyczna i dynamiczna

Inną własnością wyróżniającą pamięci RAM jest ich ulotność. Pamięć

RAM musi mieć źródło stałego zasilania. Jeśli zasilanie jest przerwane,

dane są tracone. Pamięć RAM może więc być używana tylko do

przechowywania czasowego. Pamięci RAM można podzielić na

statyczne i dynamiczne.

Dynamiczna pamięć RAM jest wykonana z komórek, które

przechowują dane podobnie, jak kondensatory przechowują ładunek

elektryczny. Obecność lub brak ładunku w kondensatorze są

interpretowane jako binarne 1 lub 0. Ponieważ kondensatory mają

naturalną tendencję do rozładowywania się, dynamiczne pamięci

RAM wymagają okresowego odświeżania ładunku w celu zachowania

danych.

W

statycznych

pamięciach

RAM

wartości

binarne

są

przechowywane za pomocą przerzutnikowych konfiguracji bramek

logicznych. Statyczne pamięci RAM zachowują dane tak długo, jak

długo są zasilane.

Statyczne vs. dynamiczne

Zarówno statyczne, jak i dynamiczne pamięci RAM są ulotne.

Dynamiczna komórka pamięciowa jest prostsza i dzięki temu

mniejsza niż statyczna. W rezultacie dynamiczna pamięć RAM

jest gęściej upakowana (mniejsze komórki = więcej komórek

na jednostkę powierzchni) i tańsza niż odpowiadająca jej

statyczna pamięć RAM.

Z drugiej strony, dynamiczna pamięć RAM wymaga układów

odświeżania. W przypadku dużych pamięci stały koszt układów

odświeżania jest z nawiązką skompensowany przez mniejszy,

zmienny koszt dynamicznych komórek pamięciowych.

W

rezultacie

istnieje

tendencja

do

faworyzowania

dynamicznych pamięci RAM w dużych pamięciach.

Statyczne pamięci RAM są nieco szybsze niż dynamiczne.

ROM

Silny kontrast w stosunku do pamięci RAM stanowią pamięci stałe

(read-only memory- ROM). Jak sugeruje ich nazwa, pamięci ROM

zawierają trwały wzór danych, który nie może być zmieniony. Podczas

gdy jest możliwe odczytywanie pamięci ROM, nie można zapisać w nich

nowych danych.

W przypadku umiarkowanych wymagań zaletą pamięci ROM jest to, że

dane lub program pozostają na stałe w pamięci głównej i nigdy nie

wymagają ładowania z urządzeń pamięci wtórnej.

Pamięć ROM powstaje podobnie, jak wszystkie mikroukłady scalone,

przy czym dane są wbudowywane podczas procesu wytwarzania.

Wynikają z tego dwa problemy.

Umieszczaniu danych w pamięci towarzyszy stosunkowo duży koszt

stały, niezależny od tego, czy wytwarza się 1000 kopii określonego

układu, czy tylko jedną.

Nie może wystąpić błąd. Jeśli jeden bit jest niewłaściwy, cała partia

układów ROM musi być wyrzucona.

PROM

Jeśli potrzebna jest tylko niewielka pamięć ROM o

określonej zawartości, tańszym rozwiązaniem jest

wykorzystanie programowalnej pamięci ROM (PROM).

Podobnie jak ROM pamięć PROM jest nieulotna i można

ją zapisać tylko raz. W przypadku pamięci PROM zapis

jest realizowany elektrycznie i może być wykonany przez

dostawcę lub przez klienta już po wyprodukowaniu

mikroukładu.

Do zapisu (lub „programowania") wymagane są

specjalne urządzenia. Pamięci PROM zapewniają

elastyczność i wygodę. Pamięci ROM natomiast

pozostają atrakcyjne w przypadku dużych ilości

produkowanego sprzętu.

Pamięci głównie do

odczytu

Inną odmianą pamięci stałych jest pamięć

głównie

do

odczytu

(read-mostly

memory), która jest użyteczna wtedy, gdy

operacje zapisu są znacznie częstsze niż

operacje zapisu, natomiast wymagana jest

nieulotność.

Powszechnie znane są trzy odmiany pamięci

głównie do odczytu: EPROM, EEPROM i

tzw. pamięć błyskawiczna (flash memory).

EPROM

Optycznie wymazywalna programowalna pamięć stała

(EPROM) jest odczytywana i zapisywana elektrycznie,

podobnie jak PROM.

Jednak przed operacją zapisu wszystkie komórki pamięci

muszą być wymazane przez naświetlenie znajdującego się już

w obudowie układu promieniowaniem ultrafioletowym. Proces

wymazywania może być wykonywany wielokrotnie; każde

wymazanie trwa do około 20 minut.

Zawartość pamięci EPROM może więc być zmieniana wiele

razy, poza tym pamięć ta przechowuje dane permanentnie,

jak ROM i PROM.

Przy porównywalnej pojemności pamięć EPROM jest droższa

niż PROM, jednak ma zaletę możliwości wielokrotnej

aktualizacji zawartości.

EEPROM

Bardziej atrakcyjną odmianą pamięci głównie do odczytu

jest

elektrycznie

wymazywalna

programowalna

pamięć stała (EEPROM).

Jest to pamięć głównie do odczytu, która może być

zapisana bez wymazywania poprzedniej zawartości;

aktualizowany jest tylko bajt (lub bajty) adresowane.

Operacja zapisu trwa znacznie dłużej niż odczytu i zajmuje

czas rzędu kilkuset mikrosekund na bajt.

EEPROM łączy zaletę nieulotności z możliwością aktualizacji

na miejscu, przy wykorzystaniu zwykłych magistralowych

linii sterowania, adresów i danych.

EEPROM jest droższa niż EPROM, a także mniej gęsto

upakowana (zawiera mniej bitów w mikroukładzie).

Pamięć błyskawiczna

Najnowszą postacią pamięci półprzewodnikowej jest pamięć

błyskawiczna (nazwana tak z powodu szybkości, z jaką może być

reprogramowana).

Wprowadzono ją po raz pierwszy w połowie lat osiemdziesiątych.

Zajmuje miejsce pośrednie między EPROM i EEPROM zarówno pod

względem kosztu, jak i funkcjonalności. Podobnie jak w EEPROM w

pamięci błyskawicznej wykorzystuje się metodę wymazywania

elektrycznego.

Cała pamięć błyskawiczna może być wymazana w ciągu kilku sekund,

a więc o wiele szybciej niż EPROM. Ponadto możliwe jest

wymazywanie bloków pamięci zamiast całego mikroukładu. Jednak

pamięć błyskawiczna nie umożliwia wymazywania na poziomie bajtów.

Podobnie jak w EPROM w pamięci błyskawicznej wykorzystuje się tylko

jeden tranzystor na bit, osiągając przez to wysoką gęstość

upakowania, podobną do EPROM.

Cechy komórek pamięci

Podstawowym

elementem

pamięci

półprzewodnikowej jest komórka pamięci. Chociaż

są wykorzystywane różne technologie, wszystkie

komórki pamięci półprzewodnikowych mają pewne

wspólne cechy:

Mają dwa stabilne (lub półstabilne) stany, które

mogą być użyte do reprezentowania binarnych 1 i

0.

Umożliwiają zapis (przynajmniej jednokrotny).

Umożliwiają odczyt.

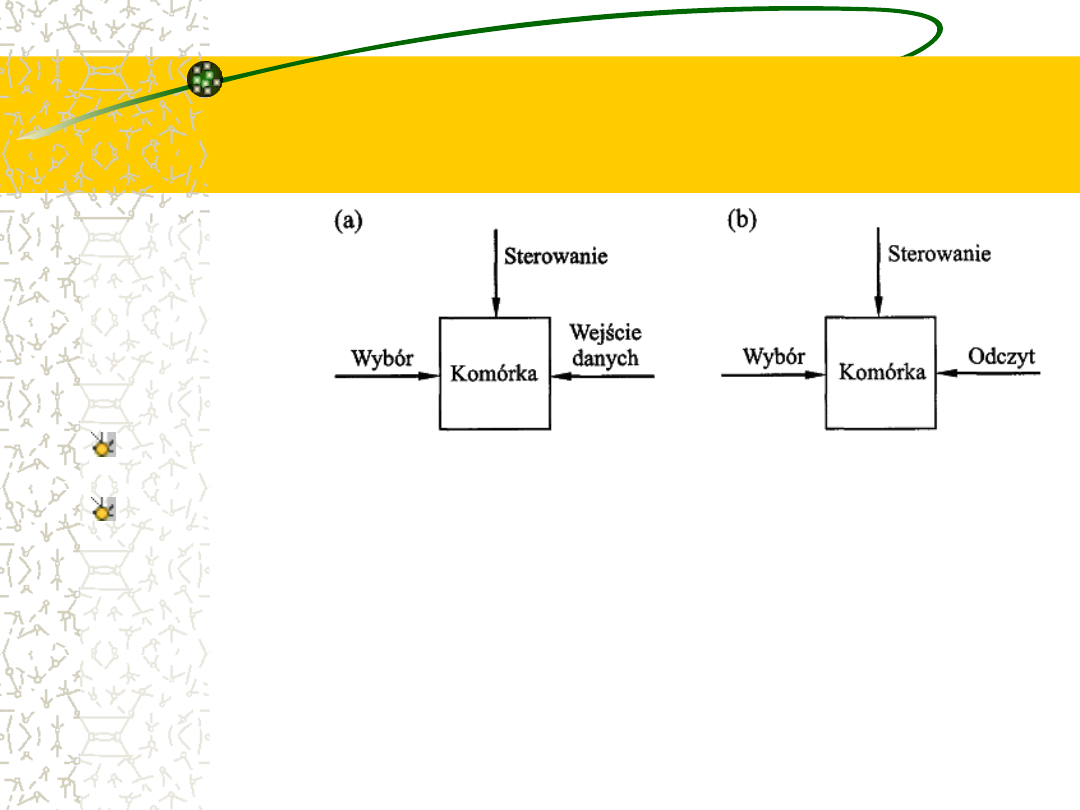

Działanie komórki

pamięci:

(a) zapis (b) odczyt

Na rysunku w sposób schematyczny, pokazano działanie komórki

pamięci.

Najczęściej komórka ma trzy końcówki funkcyjne służące do

przenoszenia sygnału elektrycznego.

–

Końcówka wyboru, jak sama nazwa wskazuje, służy do wybierania

komórki pamięci w celu przeprowadzenia operacji odczytu lub zapisu.

–

Końcówka sterowania umożliwia wskazanie rodzaju operacji (zapis lub

odczyt).

–

W przypadku zapisu przez inną końcówkę wprowadzany jest sygnał

elektryczny, który ustala stan komórki na 1 lub 0. W przypadku odczytu

ta sama końcówka służy do wyprowadzania sygnału o stanie komórki.

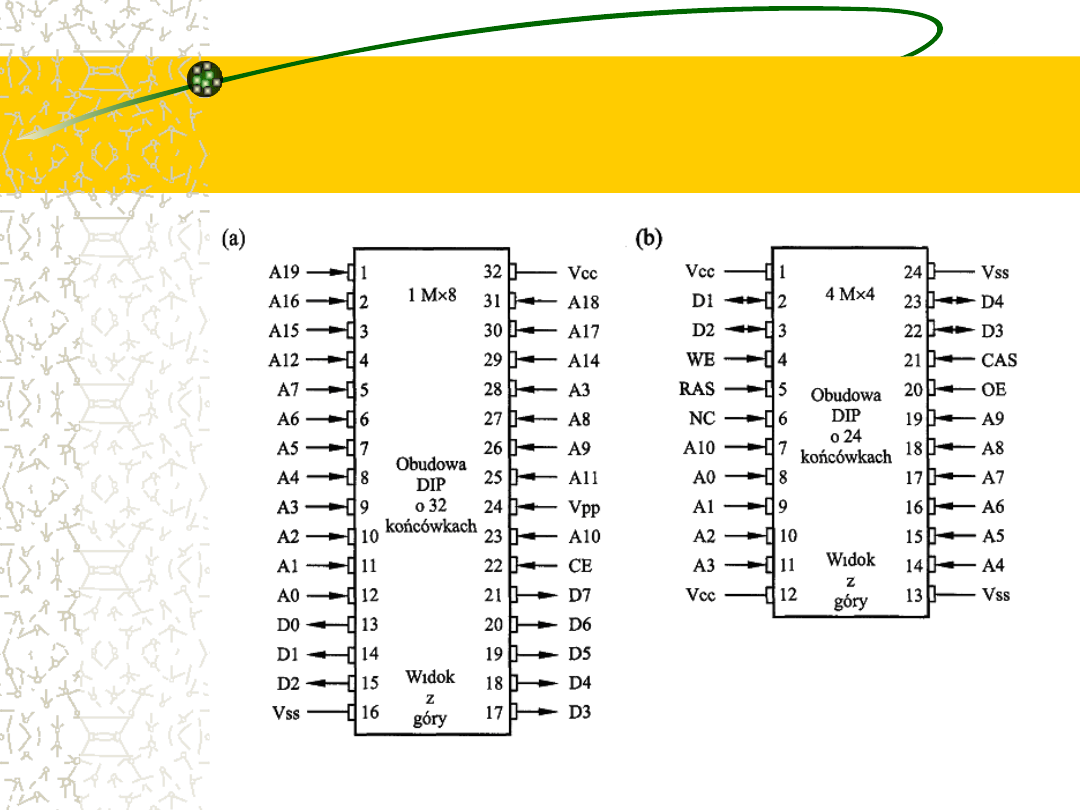

Pamięć – układ scalony w

obudowie

Podobnie jak inne układy scalone, pamięć

półprzewodnikowa

jest

w

postaci

obudowanego mikroukładu (rys.).

Każdy mikroukład zawiera zestaw komórek

pamięci. W przypadku aktualnie dostępnej

technologii, powszechne są mikroukłady o

pojemności

256

Mbit,

natomiast

wprowadzane są do użytku mikroukłady o

pojemności 1024 Mbit.

Rozkład wyprowadzeń i sygnały

typowej obudowy mikroukładu

pamięciowego: (a) pamięć EPROM

8Mbit, (b) pamięć DRAM 16Mbit

Układy logiczne

mikroukładu

Jak widzieliśmy, w hierarchicznym układzie pamięci występują

współzależności między szybkością, pojemnością a kosztem. Takie

współzależności istnieją również, jeśli rozpatrujemy organizację

komórek pamięci i funkcjonalne układy logiczne zawarte w

mikroukładzie.

W przypadku pamięci półprzewodnikowych jednym z kluczowych

problemów projektowych jest liczba bitów danych, które mogą być

jednocześnie odczytywane lub zapisywane.

– Na jednym biegunie znajduje się organizacja, w której fizyczne

uporządkowanie komórek w układzie jest takie samo, jak

uporządkowanie logiczne (postrzegane przez procesor) słów w

pamięci. Komórki są wtedy zorganizowane w postaci W słów B-

bitowych. Na przykład mikroukład 16 Mbit może być zorganizowany

jako 1 M (milion) słów 16-bitowych.

– Na drugim biegunie znajduje się organizacja 1-bitowa, w przypadku

której w określonym czasie odczytuje się lub zapisuje tylko jeden bit.

Przykład. Organizacja 16

Mbitowej pamięci RAM

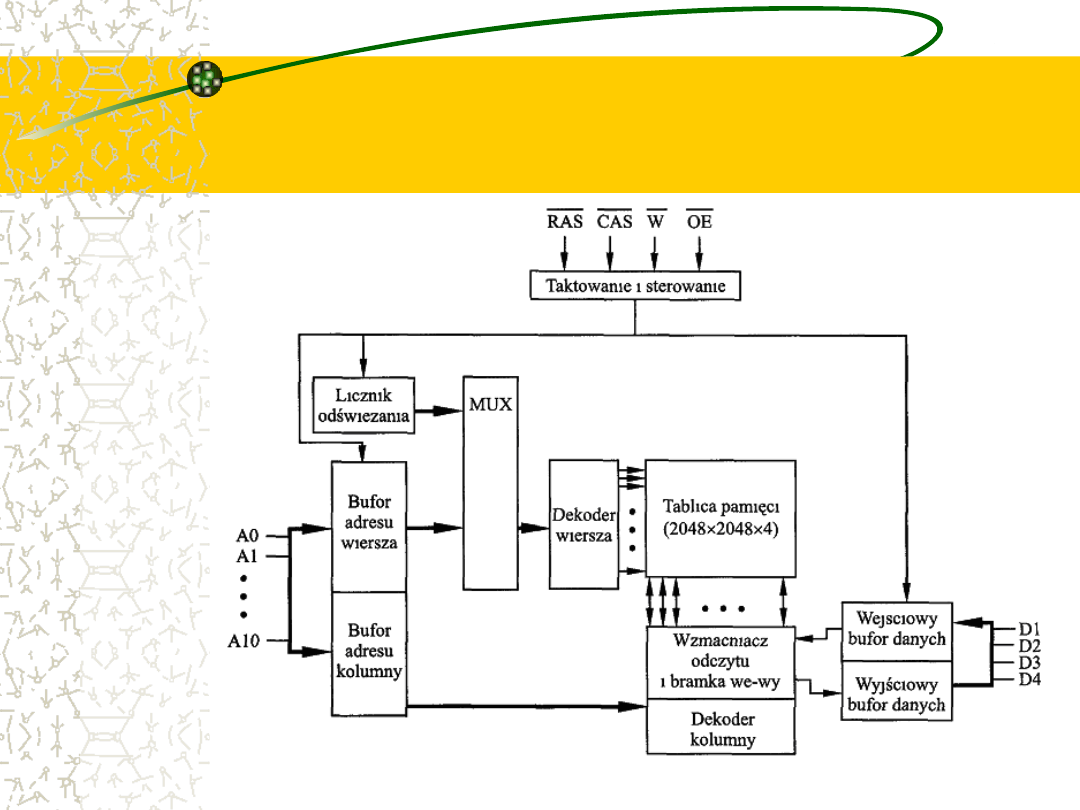

Na rys. jest pokazana typowa organizacja 16-

megabitowej pamięci DRAM. W tym przypadku

jednocześnie mogą być odczytywane lub zapisywane 4

bity.

Logicznie

rzecz

biorąc,

zespół

pamięci

jest

zorganizowany w postaci 4 kwadratowych układów 2048

na 2048 elementów. Możliwe są różne organizacje

fizyczne. W każdym przypadku elementy zespołu są

połączone zarówno przez linie poziome (wiersze), jak i

pionowe (kolumny). Każda linia pozioma jest połączona z

końcówkami „wybór” każdej komórki w wierszu; każda

linia

pionowa

jest

połączona

z

końcówkami

„zapis/odczyt” każdej komórki w kolumnie.

Przykład. Organizacja 16

Mbitowej pamięci RAM

Linie adresowe

Linie adresowe dostarczają adres słowa, które ma

być wybrane. Łącznie potrzeba log

2

W linii. W naszym

przykładzie wymaganych jest 11 linii w celu

wybrania 1 z 2048 wierszy. Linie te są doprowadzone

do dekodera wiersza mającego 11 linii wejściowych i

2048

wyjściowych.

Układ

logiczny

dekodera

aktywuje jedną z 2048 linii zależnie od wzoru

bitowego na 11 liniach wejściowych (2

11

=2048).

Dodatkowe 11 linii adresu wybiera 1 z 2048 kolumn,

przy czym na 1 kolumnę przypadają 4 bity. W celu

wprowadzania i wyprowadzania 4 bitów z bufora

danych są wykorzystywane 4 linie danych.

Linie adresowe

Na wejściu (zapis) sterownik bitowy każdej linii bitu jest

aktywowany do 1 lub 0, zależnie od wartości

odpowiedniej linii danych. Na wyjściu (odczyt) sygnał z

każdej

linii

bitowej jest

doprowadzany

poprzez

wzmacniacz odczytu do linii danych. Za pomocą linii

wiersza dokonuje się wyboru, który wiersz komórek jest

wykorzystywany przy odczycie lub zapisie.

Ponieważ do tej pamięci DRAM są zapisywane (lub

odczytywane) jednocześnie tylko 4 bity, wiele takich

pamięci musi być połączonych ze sterownikiem pamięci

w celu umożliwienia odczytu lub zapisu słowa i

przekazania go do magistrali.

Przeznaczenie RAS i CAS

Zauważmy, że występuje tylko 11 linii adresu (A0-A10),

połowa liczby, której moglibyśmy się spodziewać dla zespołu

2048 x 2048.

Czyni się tak, aby zmniejszyć liczbę doprowadzeń do układu.

Wymagane linie adresu (22) przechodzą przez układy logiczne

wyboru zewnętrzne w stosunku do mikroukładu, po czym są

multipleksowane do 11 linii adresu.

Najpierw do mikroukładu doprowadza się 11 sygnałów

adresowych określających adres wiersza w zespole, po czym

11 pozostałych sygnałów adresowych określa adres kolumny.

Sygnałom tym towarzyszą sygnały: wyboru adresu wiersza

(RAS) i wyboru adresu kolumny (CAS) umożliwiające

sterowanie czasowe mikroukładu.

Odświeżanie

Na rysunku są również pokazane układy odświeżania.

Wszystkie

pamięci

DRAM

wymagają

operacji

odświeżania.

Prostym sposobem odświeżania jest uniemożliwienie

używania mikroukładu DRAM w czasie, gdy wszystkie

komórki danych są odświeżane.

Licznik

odświeżania

przechodzi

kolejno

przez

wszystkie wiersze.

W przypadku każdego wiersza linie wyjściowe licznika

odświeżania są łączone z dekoderem wiersza i

wzbudzana jest linia RAS. Powoduje to odświeżenie

każdej komórki w wierszu.

Montaż układów EPROM w

obudowie

Na rysunku (a) (slajd 46) jest pokazana

przykładowa

obudowa

pamięci

EPROM

o

pojemności 8 Mbit, zorganizowanej jako 1M x 8.

W tym przypadku organizacja ta może być

traktowana jako oparta na słowach.

Obudowa ma 32 końcówki, co jest jednym z

rozwiązań

standardowych.

Końcówkom

są

przypisywane następujące linie sygnałowe:

– adres słowa; w przypadku 1M słów wymagane

jest 20 (2

20

= 1 M) końcówek (A0-A19);

– odczytywane dane, wymagające 8 linii (DO-D7);

Montaż układów EPROM w

obudowie

– zasilanie mikroukładu (V

cc

), uziemienie (V

ss

)

– uaktywnienie mikroukładu (CE); ponieważ może

występować wiele mikroukładów pamięciowych, z

których każdy jest dołączony do tej samej szyny

adresowej, końcówka CE jest wykorzystywana do

określania, czy adres dotyczy danego mikroukładu;

końcówka CE jest pobudzana przez układy logiczne

dołączone do linii najbardziej znaczących bitów

szyny adresowej (tzn. do linii bitów powyżej A19).

– napięcie

programowania

(V

pp

),

które

jest

doprowadzane podczas programowania (operacje

zapisu).

Montaż układów DRAM w

obudowie

Typowy układ końcówek pamięci DRAM jest pokazany na rys.

(b) dla mikroukładu 16 Mbit zorganizowanego jako 4 M x 4.

Występuje tu kilka różnic w stosunku do układu ROM. Ponieważ

pamięć RAM może być aktualizowana, końcówki danych są

końcówkami wejścia/wyjścia.

Końcówki

zezwolenia

zapisu

(WE)

i

zezwolenia

na

wyprowadzanie (OE) wskazują na to, czy prowadzona jest

operacja zapisu lub odczytu.

Ponieważ pamięć DRAM jest adresowana za pomocą wierszy i

kolumn, a adres jest multipleksowany, tylko 11 końcówek

adresu potrzeba do określenia 4M kombinacji wiersz/kolumna

(2

11

x2

11

=2

22

=4M).

Funkcje wyboru adresu wiersza (RAS) i wyboru adresu kolumny

(CAS) zostały już przedyskutowane uprzednio.

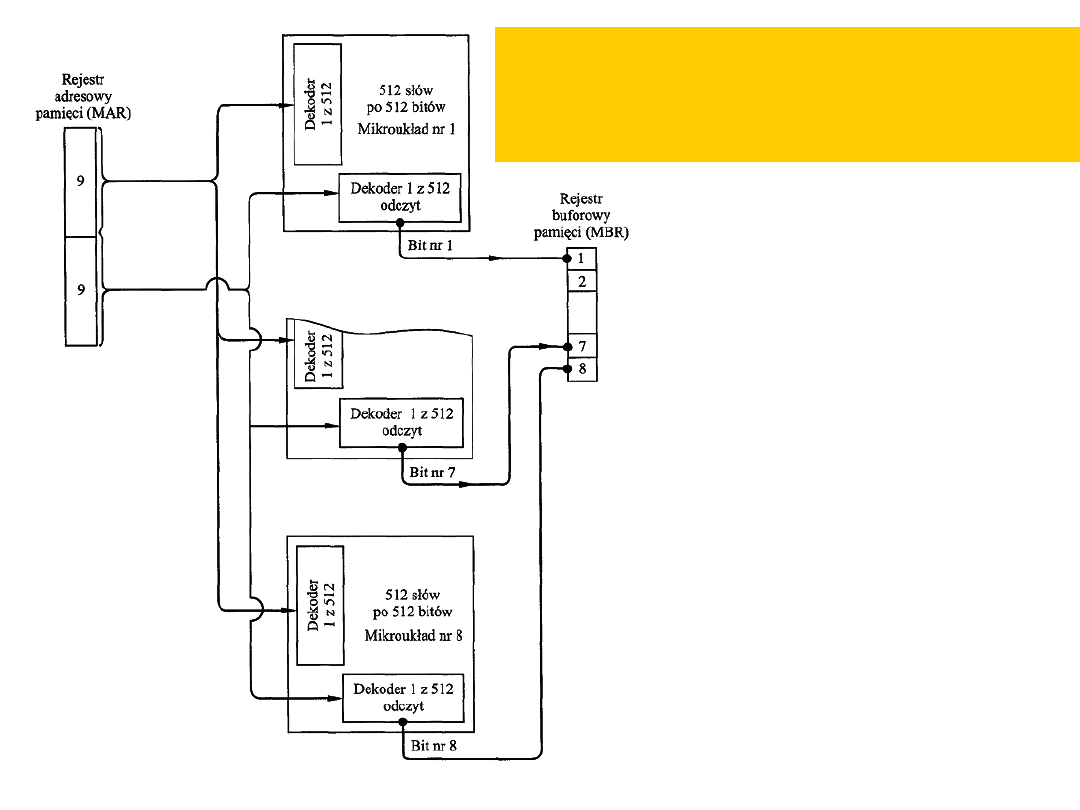

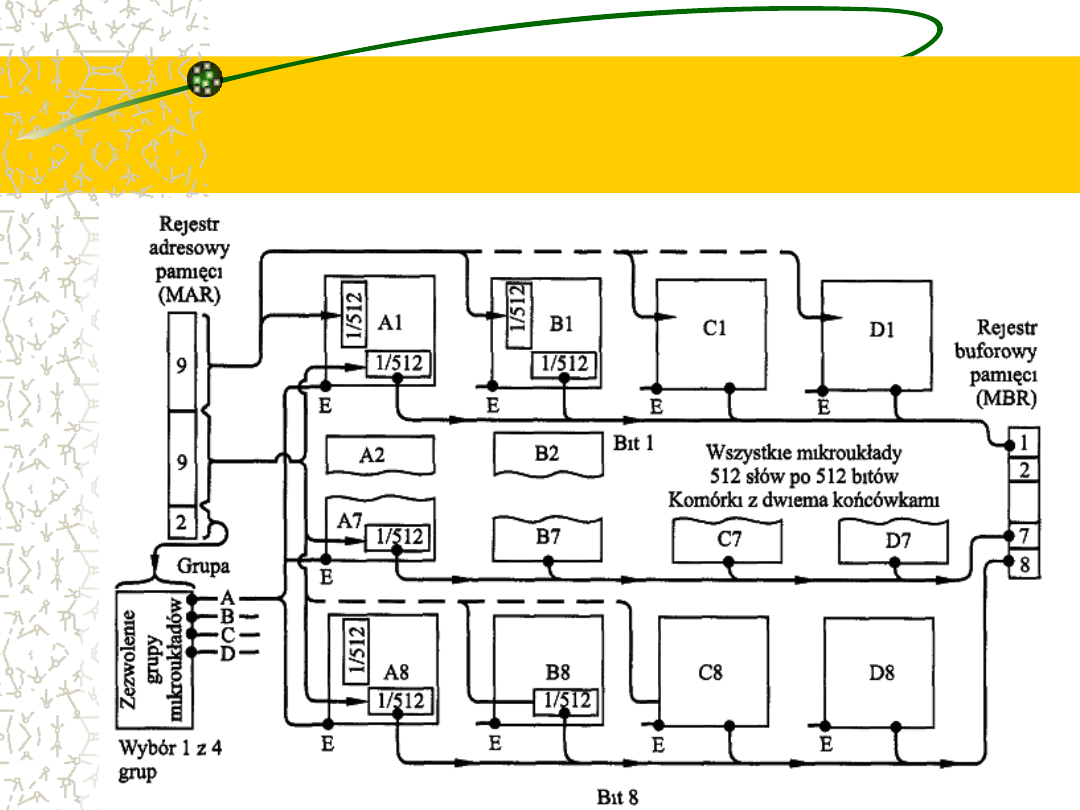

Organizacja modułu

Jeśli mikroukład RAM zawiera tylko 1 bit na słowo,

będziemy oczywiście potrzebowali przynajmniej

liczby mikroukładów równej liczbie bitów w słowie. Na

rysunku jest pokazane przykładowo, jak może być

zorganizowany moduł pamięci zawierający 256K słów

8-bitowych.

W przypadku 256K słów wymagany jest adres 18-

bitowy; jest on dostarczany do modułu z pewnego

źródła zewnętrznego (np. z linii adresowych

magistrali, do której moduł jest dołączony).

Adres jest doprowadzany do 8 mikroukładów 256K1,

z których każdy umożliwia wejście/wyjście 1 bita.

Organizacja

pamięci 256KB

Organizacja pamięci 1MB

Organizacja taka jest odpowiednia, dopóki rozmiar pamięci

mierzony w słowach jest równy liczbie bitów w mikroukładzie.

W przypadku gdy wymagana jest większa pamięć, potrzebna jest

matryca mikroukładów. Na kolejnym rysunku jest pokazana

możliwa organizacja pamięci składającej się z 1M słów 8-

bitowych.

W tym przypadku występują 4 kolumny mikroukładów; każda

kolumna zawiera 256K słów uporządkowanych w sposób

pokazany na poprzednim rys.

W przypadku 1M słów wymaganych jest 20 linii adresowych.

Osiemnaście najmniej znaczących bitów doprowadza się do

wszystkich 32 modułów. Dwa najbardziej znaczące bity są

doprowadzone do modułu logicznego wyboru grupy, który wysyła

sygnał uaktywnienia mikroukładu do jednej z 4 kolumn modułów.

Organizacja pamięci 1MB

Błędy stałe i przypadkowe

W systemach pamięci półprzewodnikowych występują błędy.

Można je podzielić na błędy stałe i przypadkowe.

Błąd stały jest permanentnym defektem fizycznym

powodującym, że uszkodzona komórka lub komórki

pamięciowe nie są w stanie niezawodnie przechowywać

danych, lecz pozostają w stanie 0 lub 1, albo błędnie

przeskakują między 0 a 1. Błędy stałe mogą być wywołane

przez działanie ostrych narażeń środowiskowych, defekty

produkcyjne lub zużycie.

Błąd przypadkowy jest losowym i nieniszczącym

zjawiskiem, które zmienia zawartość jednej lub wielu

komórek pamięciowych, bez uszkadzania samej pamięci.

Błędy takie mogą być spowodowane przez problemy

zasilania lub cząsteczki alfa.

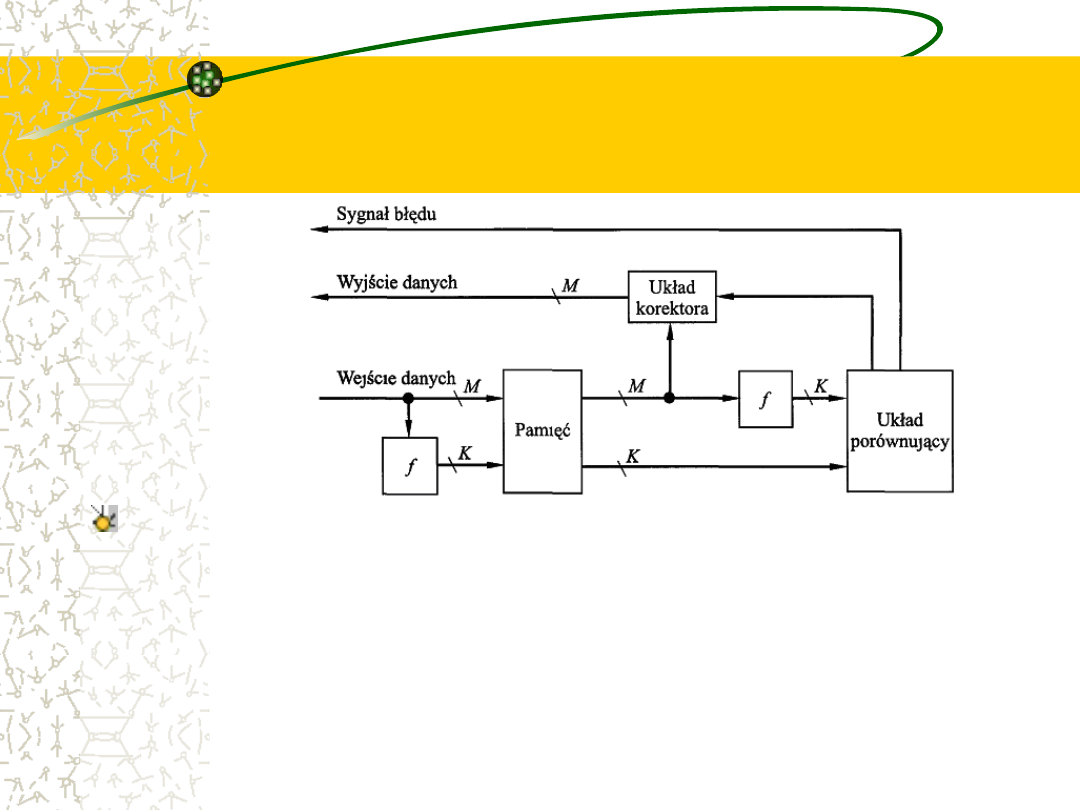

Działanie kodu

korekcyjnego

Na rysunku jest pokazane w sposób ogólny, jak ten proces

jest przeprowadzany. Gdy dane mają być wczytane do

pamięci, przeprowadza się na tych danych obliczenia,

określane jako funkcja f, w celu utworzenia kodu do korekty

błędów. Zarówno kod, jak i dane są przechowywane. W

rezultacie, jeśli ma być zapisane M-bitowe słowo danych, a

kod ma długość K bitów, to aktualna długość

przechowywanego słowa wynosi M+K bitów.

Możliwe wynik: nie ma

błędów, korekta lub

sygnalizacja

Gdy uprzednio zmagazynowane słowo jest odczytywane, kod

jest wykorzystywany do wykrywania i ewentualnej korekty

błędów. Generowany jest nowy zestaw K bitów kodowych z M

bitów danych, po czym porównuje się go z pobranymi bitami

kodowymi. Porównanie prowadzi do jednego z trzech wyników:

Nie wykryto żadnych błędów. Pobrane bity danych są wysyłane.

Wykryto błąd, którego korekta jest możliwa. Bity danych i bity

korekty błędu są doprowadzane do układu korektora, który

tworzy poprawiony zestaw M bitów przeznaczony do wysłania.

Wykryto błąd niemożliwy do poprawienia. Stan ten jest

zgłaszany.

Kody korekcyjne

Kody funkcjonujące w ten sposób są

określane jako kody korekcyjne. Kod

jest charakteryzowany przez liczbę

błędów bitowych w słowie, którą może

on wykryć i poprawić.

Najprostszym kodem korekcyjnym jest

kod Hamminga, opracowany przez

Richarda Hamminga z Bell Laboratories.

Ale o tym już następnym razem...

Document Outline

- Slide 1

- Slide 2

- Slide 3

- Slide 4

- Slide 5

- Slide 6

- Slide 7

- Slide 8

- Slide 9

- Slide 10

- Slide 11

- Slide 12

- Slide 13

- Slide 14

- Slide 15

- Slide 16

- Slide 17

- Slide 18

- Slide 19

- Slide 20

- Slide 21

- Slide 22

- Slide 23

- Slide 24

- Slide 25

- Slide 26

- Slide 27

- Slide 28

- Slide 29

- Slide 30

- Slide 31

- Slide 32

- Slide 33

- Slide 34

- Slide 35

- Slide 36

- Slide 37

- Slide 38

- Slide 39

- Slide 40

- Slide 41

- Slide 42

- Slide 43

- Slide 44

- Slide 45

- Slide 46

- Slide 47

- Slide 48

- Slide 49

- Slide 50

- Slide 51

- Slide 52

- Slide 53

- Slide 54

- Slide 55

- Slide 56

- Slide 57

- Slide 58

- Slide 59

- Slide 60

- Slide 61

- Slide 62

- Slide 63

- Slide 64

Wyszukiwarka

Podobne podstrony:

Architektura i organizacja komuterów W6 Pamięć wewnętrzn

Architektura i organizacja komuterów W6 Pamięć zewnętrzna

Architektura i organizacja komuterów W7 Pamięć zewnętrzn

Architektura i organizacja komuterów W3 Działanie komput

Architektura i organizacja komuterów W1 Co to jest i skąd to się wzięło

Architektura i organizacja komuterów W4 Połączenia magistralowe

Architektura i organizacja komuterów W4 Połączenia magis

Architektura i organizacja komuterów W7 Wejście Wyjście

Architektura i organizacja komuterów W3 Działanie komputera

Architektura i organizacja komuterów W9 Wspieranie systemu operacyjnego

Architektura i organizacja komuterów 11 Procesor

Architektura i organizacja komuterów W8 Wejście Wyjście

Architektura i organizacja komuterów W9 Procesor

Architektura i organizacja komuterów W1 i 2 Co to jest i skąd to się wzięło

Architektura i organizacja komuterów W2 Ewolucja i wydaj

Pamiec wewnetrzna id 348371 Nieznany

Zarządzanie pamięcią wewnętrzną

więcej podobnych podstron