1

1

W6. PRZETWORNIKI A-

C

2

2

SCHEMAT BLOKOWY PRZETWORNIKA A-C

• Prefilter - Avoids the aliasing of high frequency signals back into the

baseband of the ADC;

• Sample-and-hold - Maintains the input analog signal constant during

conversion;

• Quantizer - Finds the subrange that corresponds to the sampled

analog input;

• Encoder - Encoding of the digital bits corresponding to the subrange.

3

3

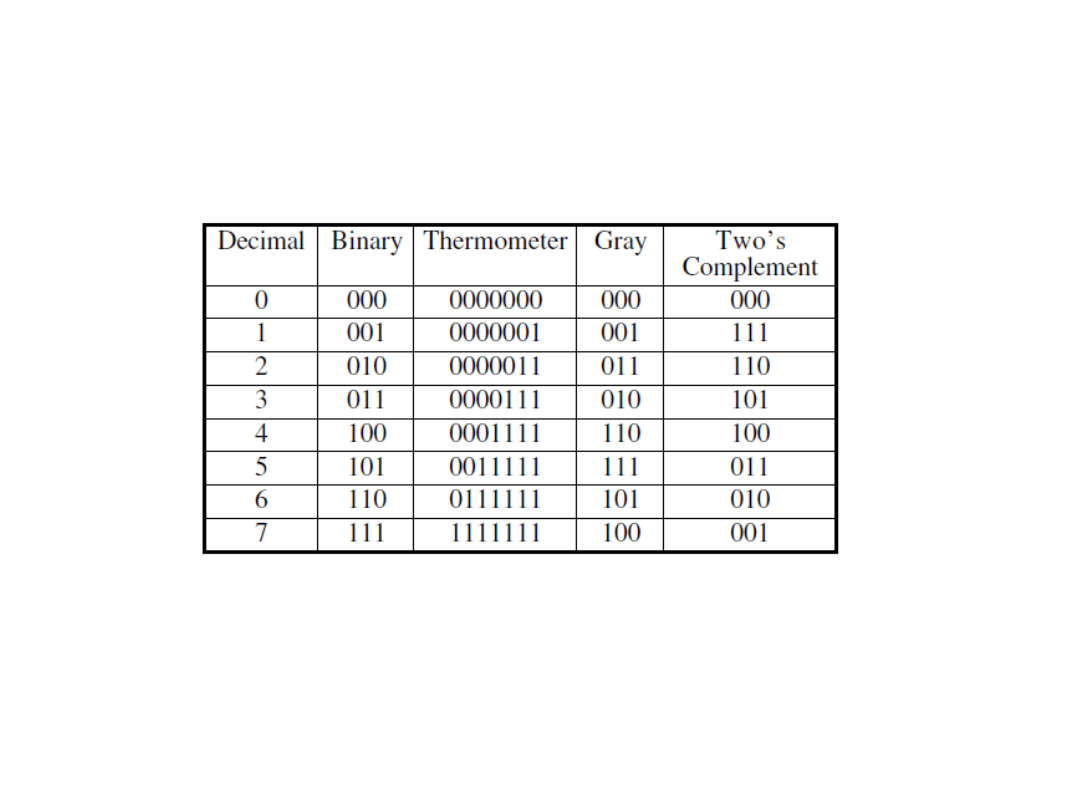

Cyfrowe kody wyjściowe (Digital

Output Codes)

4

4

5

5

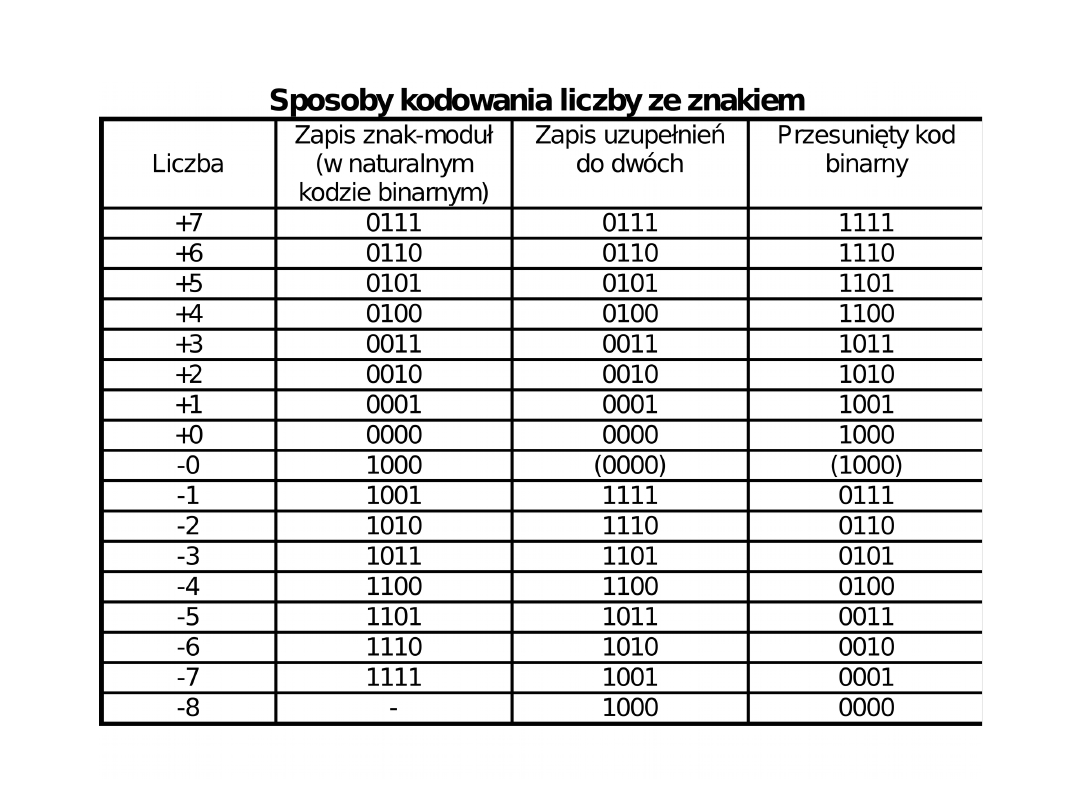

Charakterystyka przejściowa Wejście –

Wyjście

3-bitowego przetwornika A-C

DEFINICJE

1. Rozdzielczość (Resolution) przetwornika DAC jest równa liczbie

bitów zastosowanego słowa cyfrowego.

2. Pełny zakres (Full scale FS) jest różnicą: (Wyjście analogowe, gdy

wszystkie bity są równe 1) minus (Wyjście analogowe, gdy wszystkie

bity są równe 0).

3. Granica pełnego zakresu (Full scale range) jest definiowany jako:

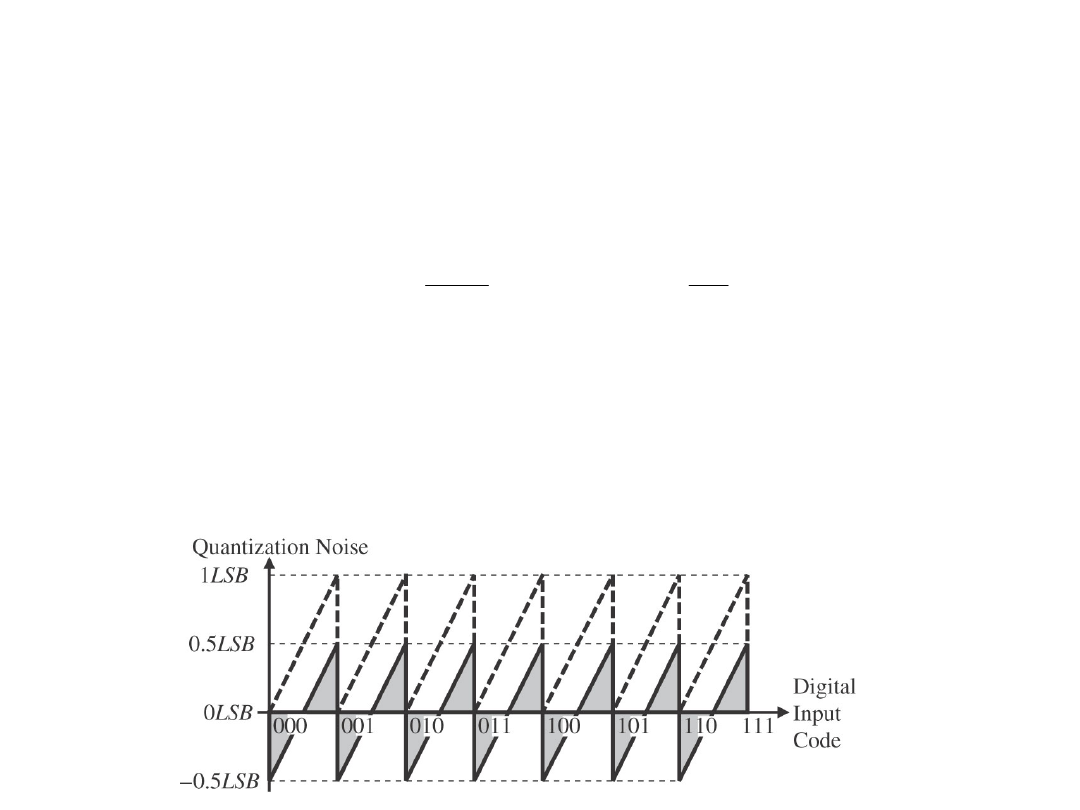

4. Szum kwantyzacji jest naturalną niedokładnością w cyfryzacji

wartości analogowej ze skończoną rozdzielczością przetwornika.

N

REF

N

REF

REF

V

V

V

FS

2

1

1

0

2

REF

N

V

FS

FSR

lim

12

2

12

5

,

0

1

)

i

kwantyzacj

szumu

(

2

0

2

N

T

FSR

LSB

dt

T

t

LSB

T

rms

2

2

6

2

12

2

2

2

12

)

(

max

N

N

N

OUT

FSR

FSR

FSR

rms

v

SNR

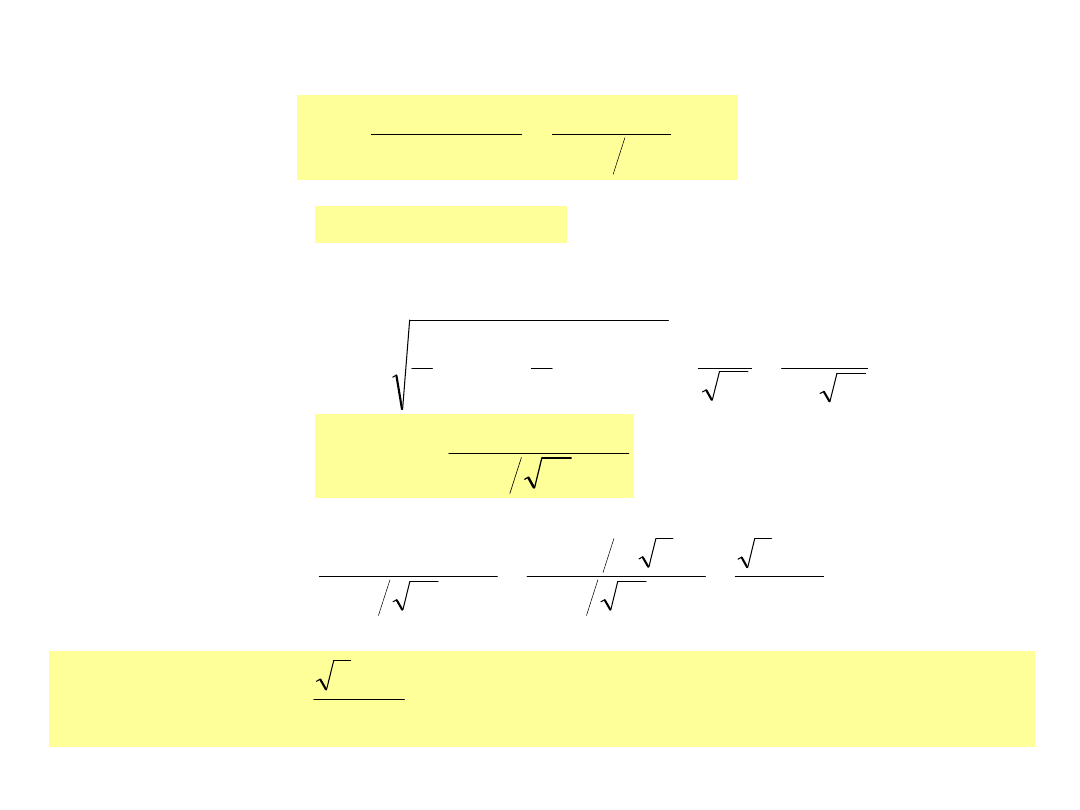

5. Zakres dynamiczny (DR) przetwornika DAC jest stosunkiem FSR do

najmniejszej różnicy, która może być rozróżniona (tj. LSB).

lub wyrażony w dB:

6. Stosunek sygnał – szum (SNR) jest stosunkiem wartości pełnego

zakresu do średniokwadratowej wartości szumu kwantyzacji:

7. Maksymalna wartość SNR (SNR

max

) dla sinusoidy definiowana jest

jako:

8. lub w dB

)

dB

(

02

,

6

)

dB

(

N

DR

N

N

FSR

FSR

LSB

FSR

DR

2

2

)

zakres

(

N

OUT

FSR

rms

v

SNR

2

12

)

(

dB

02

,

6

76

,

1

2

log

20

2

log

20

6

log

10

2

2

6

log

20

)

dB

(

max

N

SNR

N

N

8

8

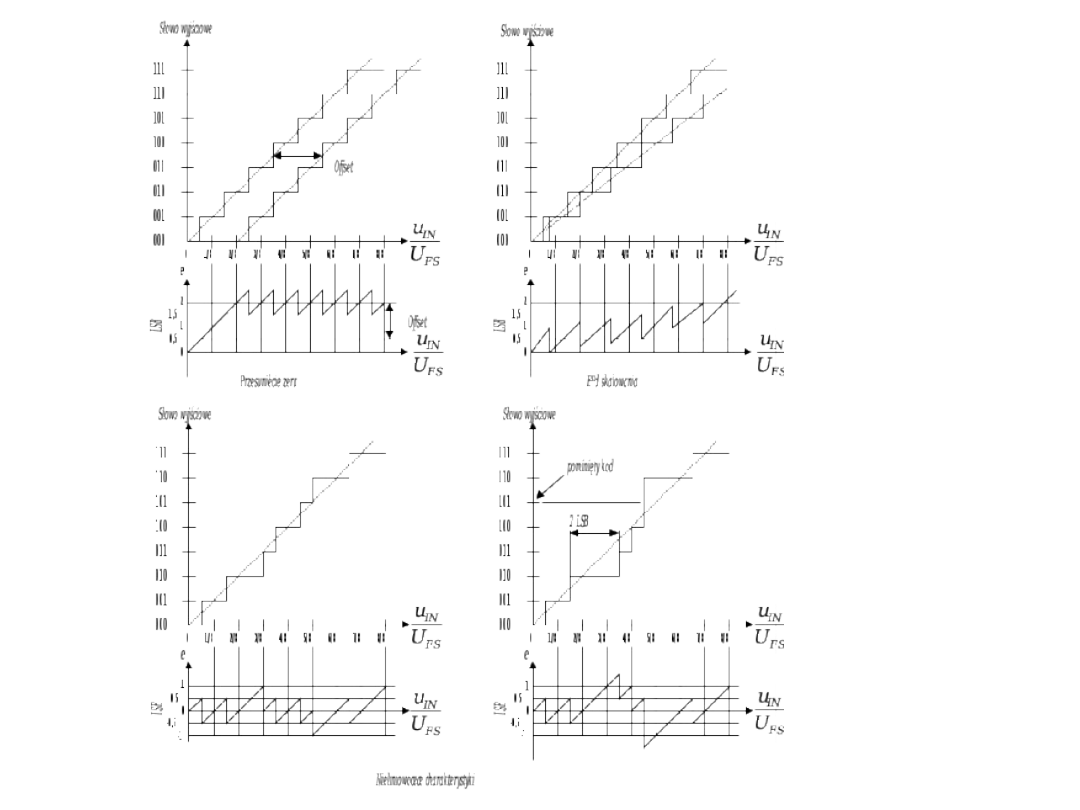

Typowe

błędy

przetwarzan

ia A-C

9

9

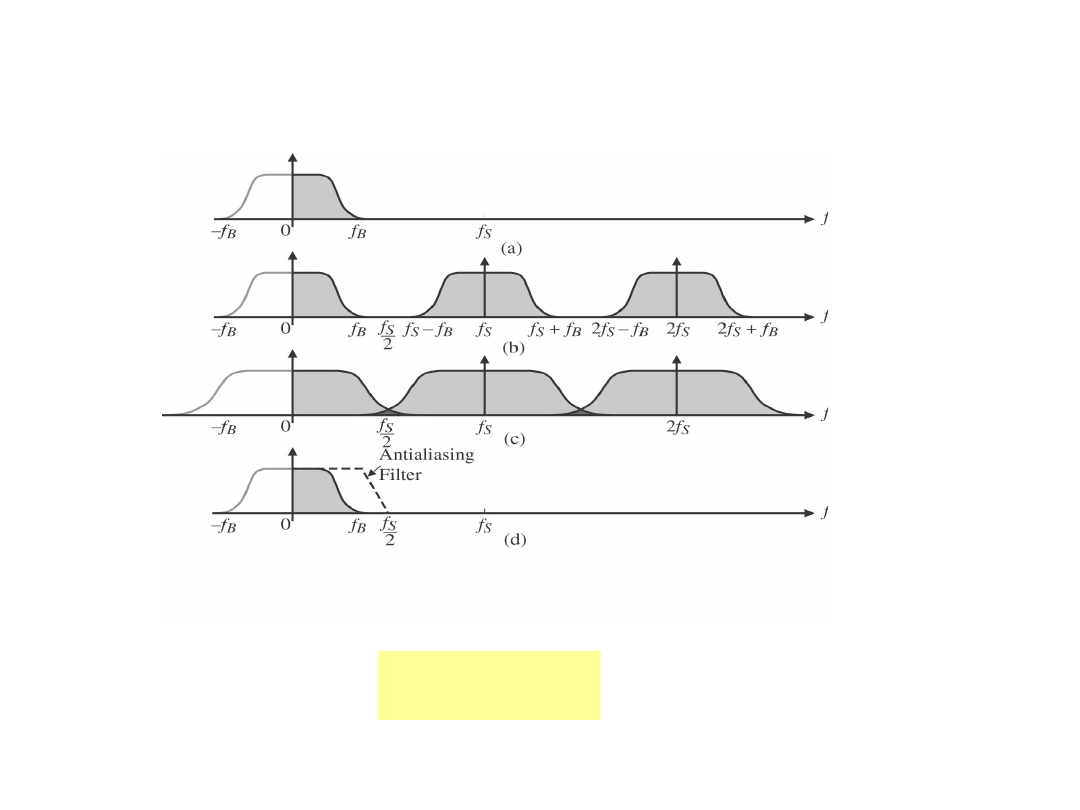

Częstotliwość Nyquista w przetwornikach

A-C

S

B

f

f

5

,

0

10

10

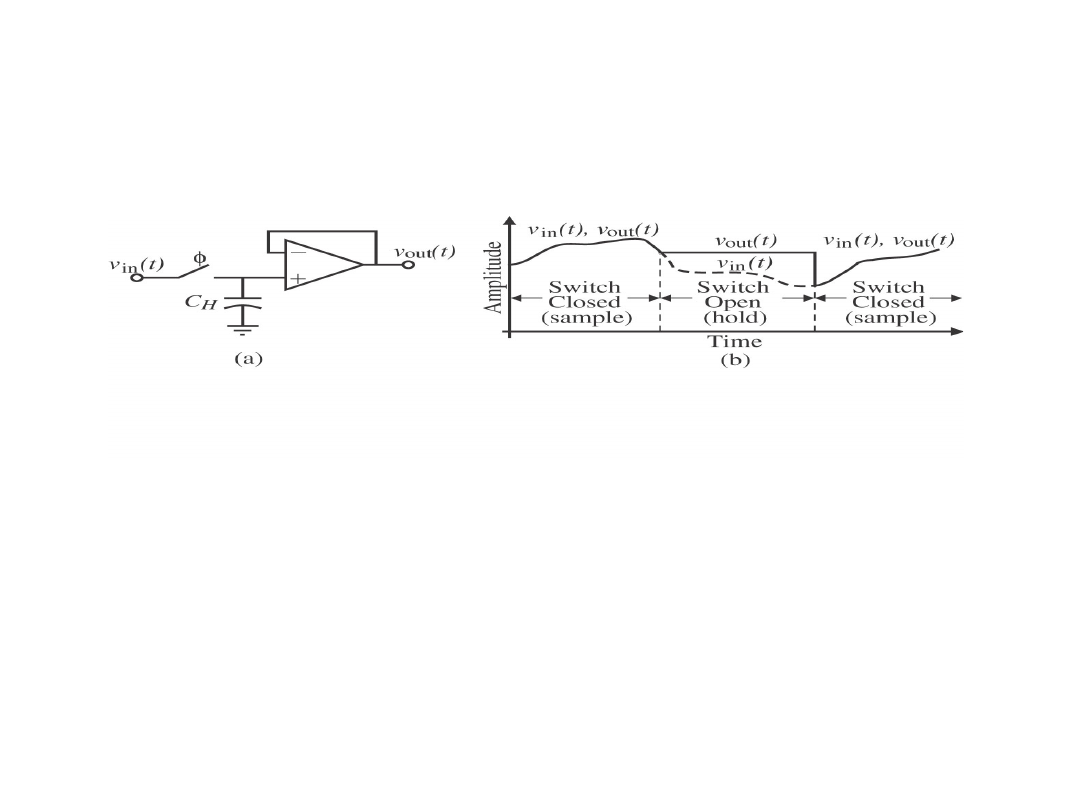

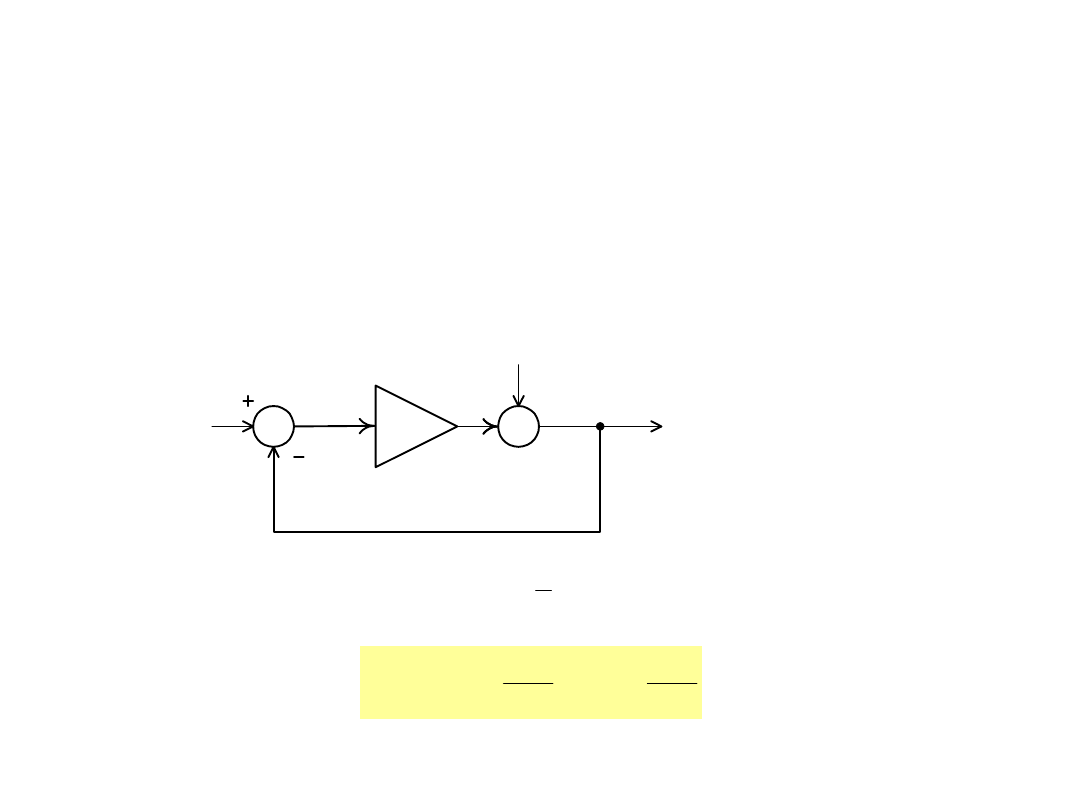

• Fast, open-loop

• Requires current from the input to charge CH

• DC voltage offset of the op amp and the charge feedthrough

of the switch will create dc errors

UKŁAD SAMPLE-AND-HOLD

S-H

11

11

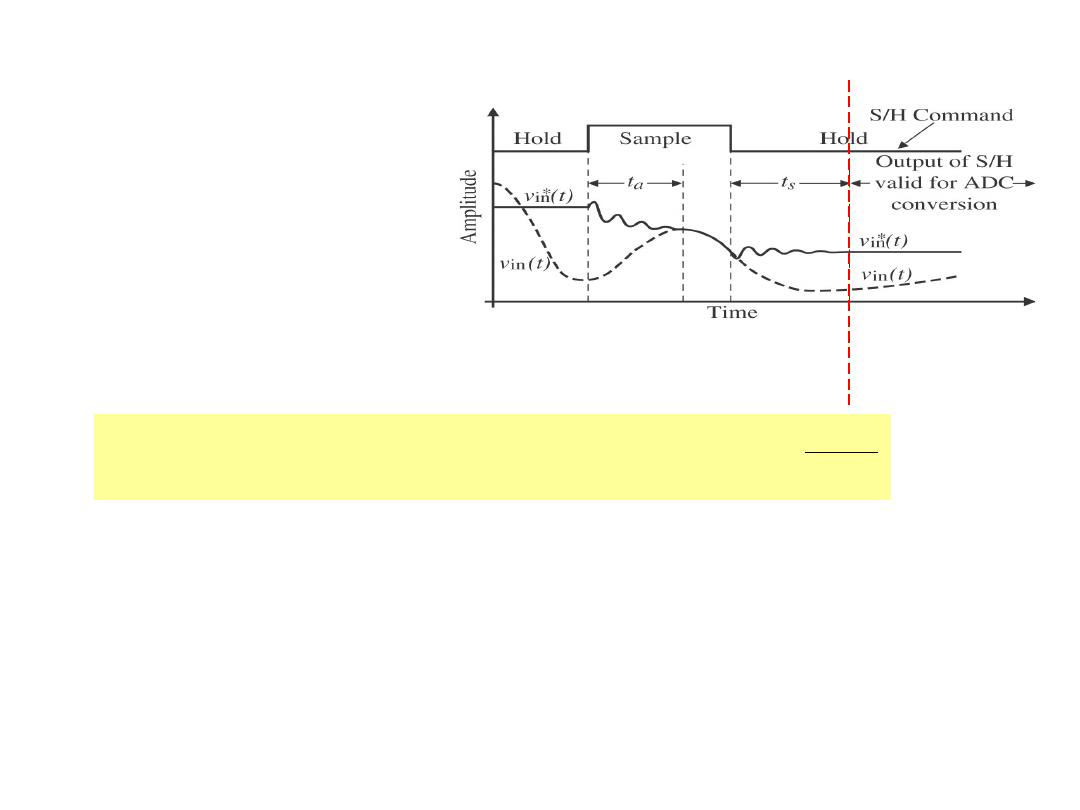

UKŁAD S-H - PROCES

PRÓBKOWANIA

Inne parametry:

•Czas apertury - Aperture time - czas pomiędzy zboczem sygnału

zegarowego wyznaczającego moment próbkowania, a faktycznym momentem

pobrania próbki przez przetwornik A/C (od momentu otwarcia przełącznika S/H

do momentu uruchomienia komendy pobrania próbki).

•Aperture jitter = zmienność czasu apertury, wywołana zmiennością czasu

zegara i szumami (phase noise).

Rodzaje układów S/H:

•Bez sprzężenia zwrotnego - szybsze, mniej dokładne;

•Ze sprzężeniem zwrotnym - wolniejsze, bardziej dokładne.

Definicje:

•Czas odpowiedzi

przetwornika - Acquisition

time (t

a

) = określa czas, jaki

jest wymagany do tego, by stan

wyjściowy przetwornika osiągnął

odpowiednią dokładność po

podaniu na wejściu skoku

jednostkowego zawierającego się

w pełnym zakresie napięciowym

przetwornika.

1

(max)

rate

sample

Maximum

sample

sample

s

a

sample

T

f

t

t

T

12

12

t

s

- Czas odpowiedzi przetwornika (Transient Response lub Settling

Time) – Parametr ten określa czas, jaki jest wymagany do tego, by stan

wyjściowy przetwornika osiągnął odpowiednią dokładność po podaniu na

wejściu skoku jednostkowego zawierającego się w pełnym zakresie

napięciowym przetwornika. Długi czas odpowiedzi przetwornika i

multipleksera może prowadzić

do powstawania przesłuchów międzykanałowych.

Czas opóźnienia apertury (Aperture Delay Time) – Parametr ten bywa

nazywany również krótko czasem apertury. Jest to czas pomiędzy zboczem

sygnału zegarowego wyznaczającego moment próbkowania, a faktycznym

momentem pobrania próbki przez przetwornik A/C.

Jitter apertury (Aperture Jitter)

– Z opisu parametru Aperture Delay Time wiemy już, że faktyczny moment

pobrania próbki przez przetwornik A/C nie musi dokładnie odpowiadać

momentom wyznaczonym przez odpowiednie zbocze sygnału zegarowego.

W praktyce można zaobserwować również dodatkowo wahania (w przód i w

tył) momentów pobrania próbki w stosunku do odpowiedniego zbocza

przebiegu zegarowego. Przyczyną tego zjawiska może być modulacja fazy

przebiegu zegarowego wynikająca z występowania w układzie

szerokopasmowego szumu, zakłóceń pochodzących z zasilania i zakłóceń od

sygnałów cyfrowych. Jitter apertury objawia się jako swego rodzaju szum

zmniejszający całkowity odstęp sygnału od szumu przetwornika A/C.

13

13

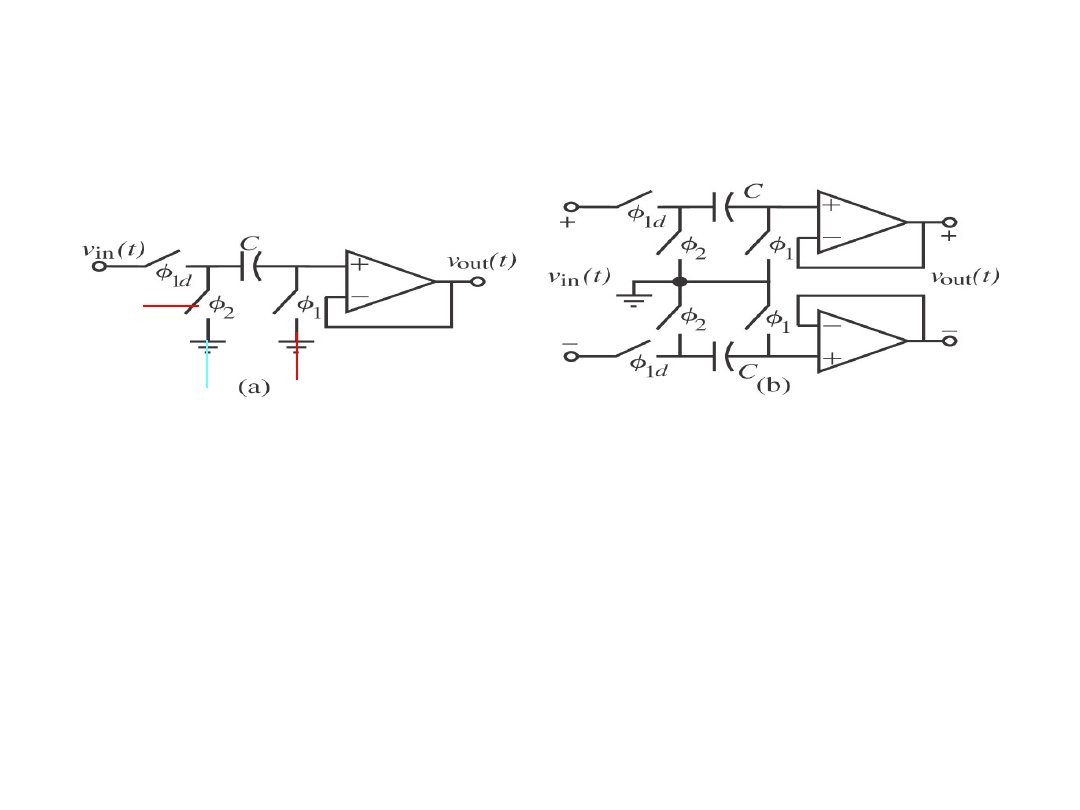

Układy bez sprzężenia zwrotnego w

technice SC

Open-Loop, Switched-Capacitor S/H

Circuit

Switched capacitor S/H circuit. Differential switched-

capacitor S/H

• Delayed clock used to remove input dependent feedthrough.

• Differential version has lower PSRR, cancellation of even

harmonics, and reduction of charge injection and clock

feedthrough.

14

14

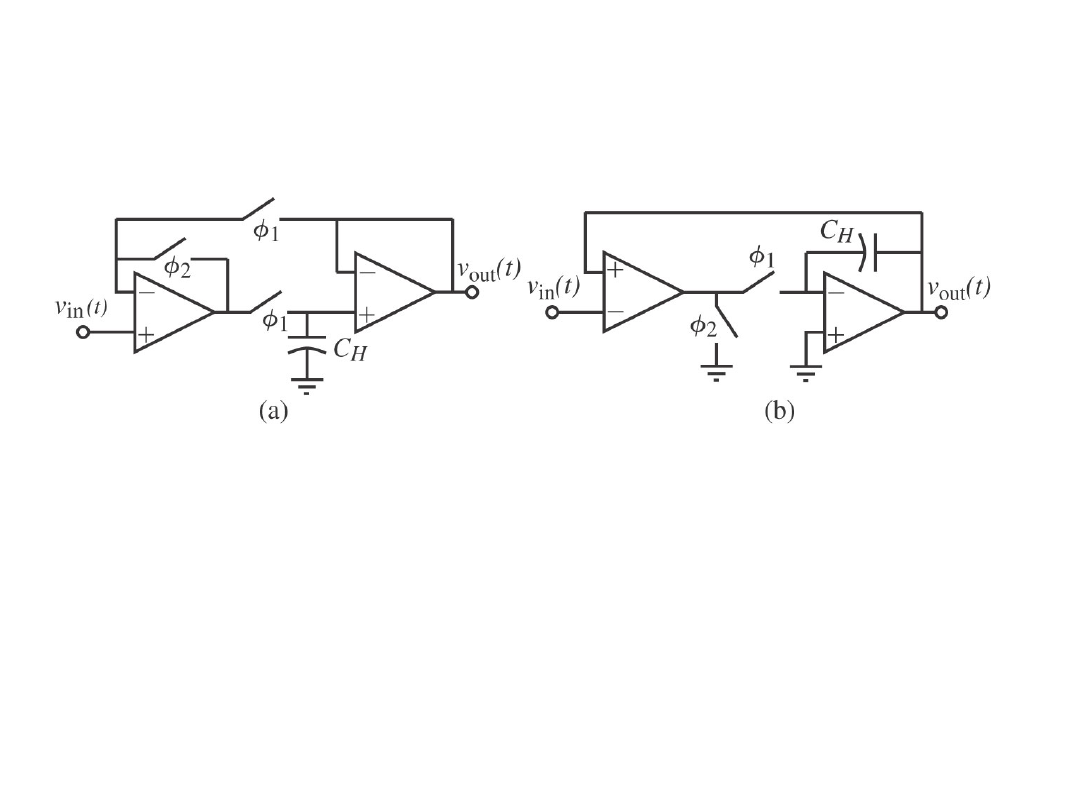

Układ ze sprzężeniam zwrotnym w

technice SC

Closed-Loop , Switched-Capacitor S/H

Circuit

Closed-loop S/H

circuit.

φ1 is the sample

phase,

φ2 is the hold phase.

Attributes:

• Accurate;

• First circuit has signal-dependent feedthrough;

• Slower because of the op amp feedback loop.

Closed-loop S/H

circuit.

An improved version.

15

15

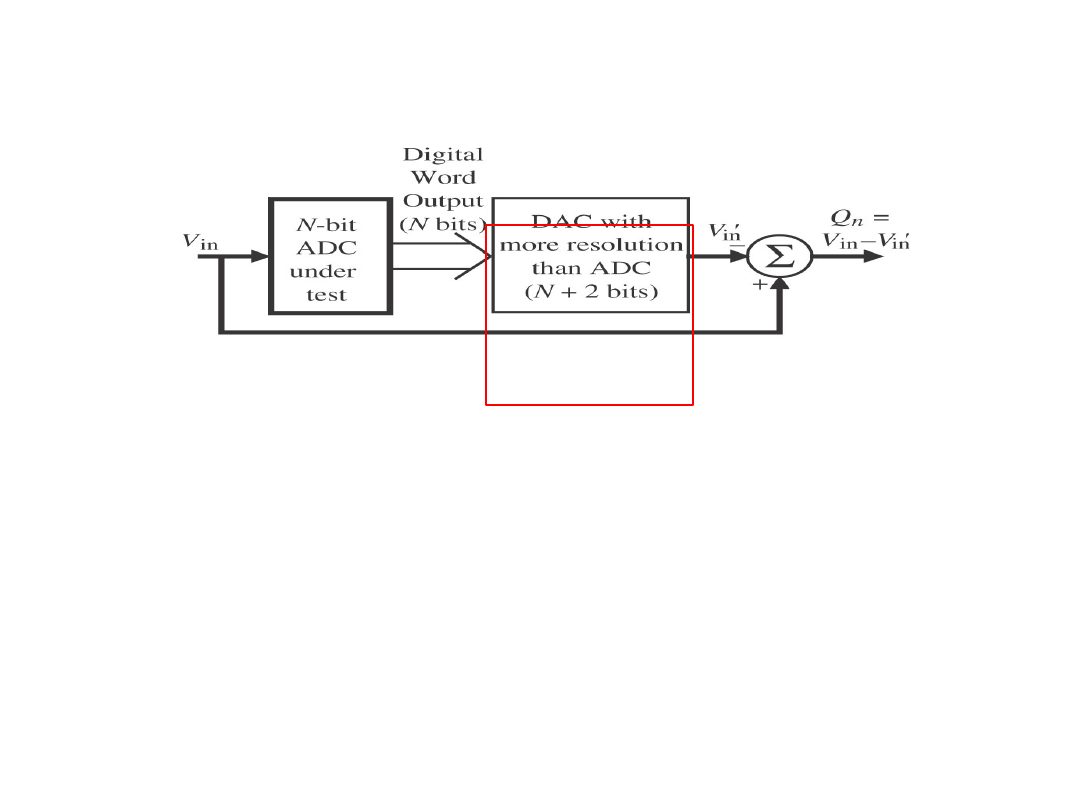

Testowanie przetwornika A-C

• Formowanie cyfrowego słowa wejściowego w zakresie od 000...0 do

111...1.

• Przetwornik ADC powinien mieć przynajmniej o 2 bity większą

rozdzielczość niż błędy wprowadzane przez DAC.

16

16

17

17

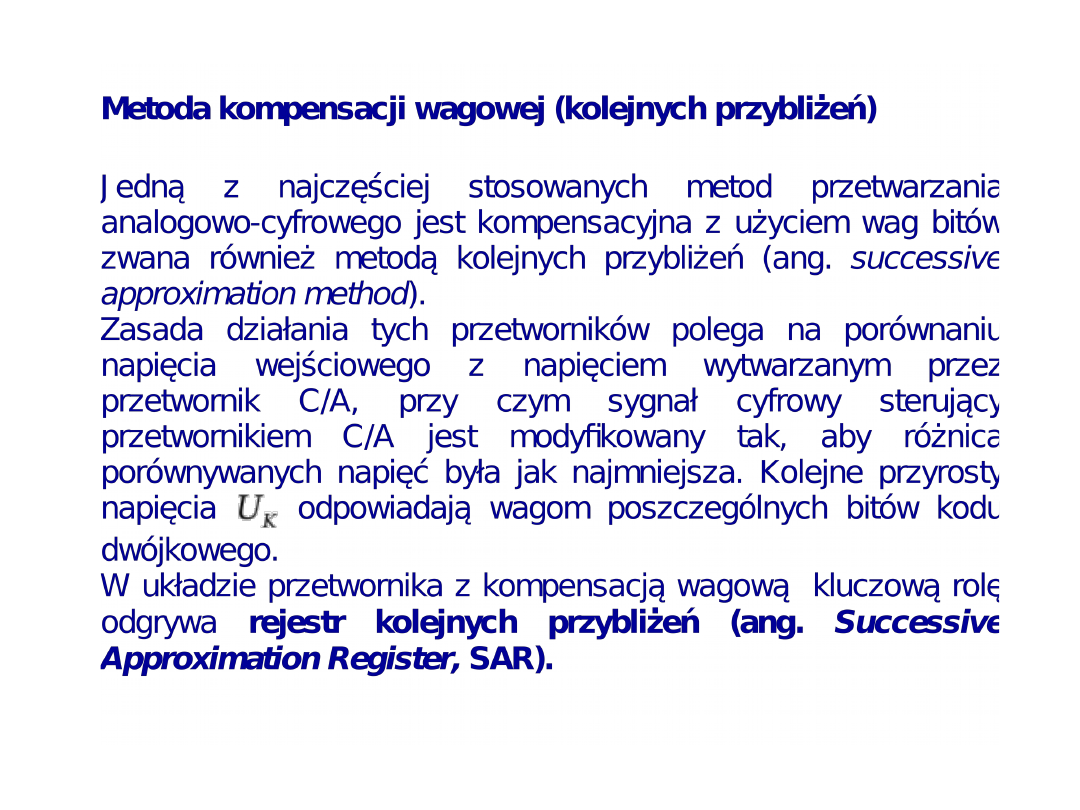

Przetwornik A/C z kompensacją

wagową

18

18

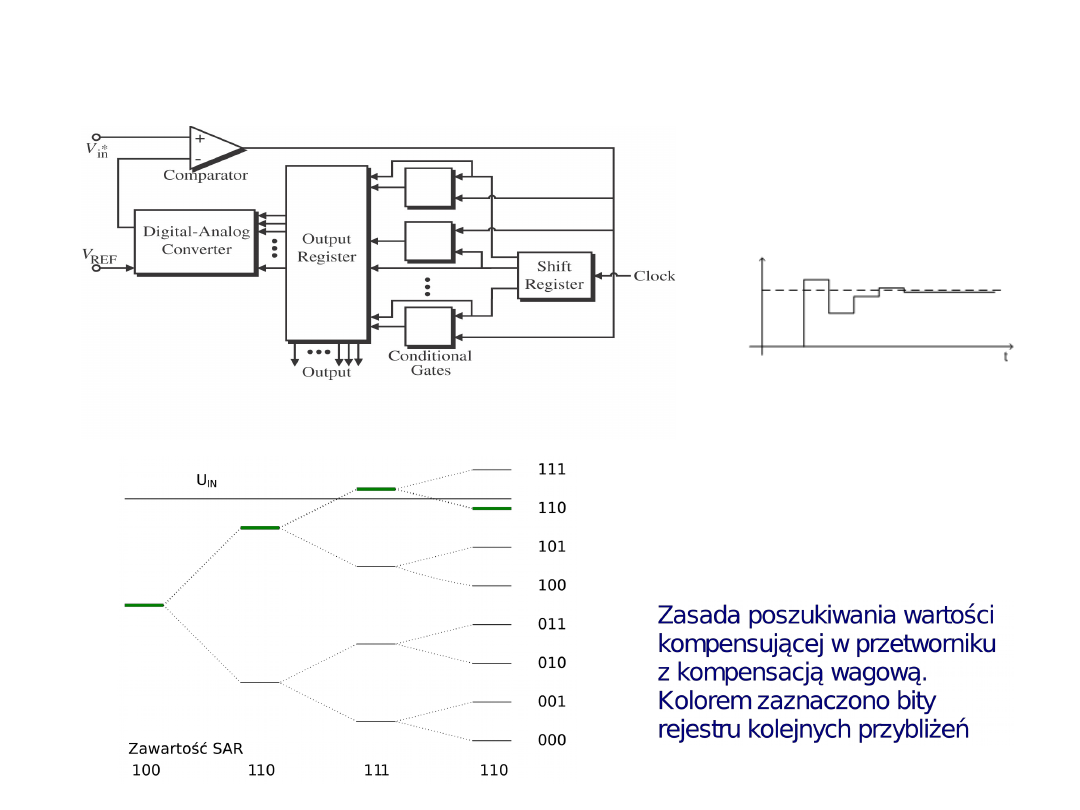

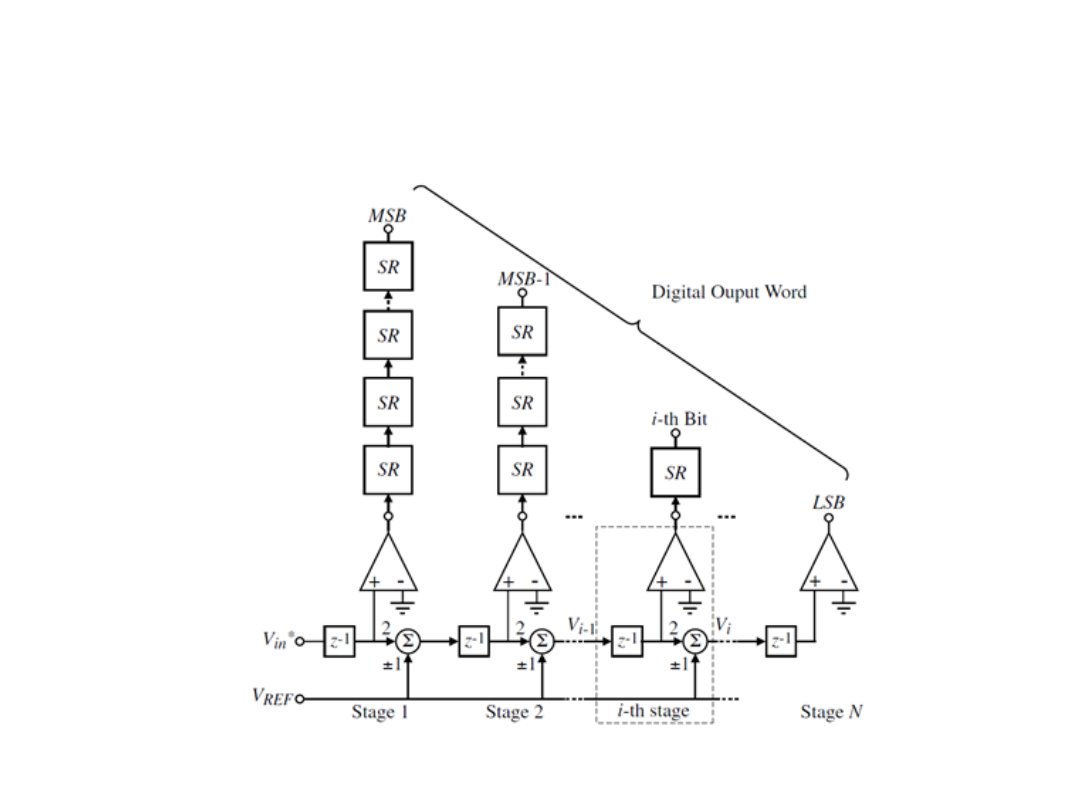

Przetworniki ADC z przetwarzaniem potokowym (pipeline

converters)

Działanie:

• W każdym stopniu sygnał

wejściowy jest mnożony przez 2, a

następnie dodany lub odjęty od

V

REF,

zależnie od znaku sygnału

wejściowego

• w i-tym stopniu:

0

gdy

1

0

gdy

1

m

jest wzore

dane

gdzie

2

1

1

1

i

i

i

i

REF

i

i

i

V

V

b

b

V

b

V

V

19

19

Zastosowanie rejestru przesuwającego w celu zapamiętania bitów

wyjściowych i uporządkowanie ich w czasie, pozwala przetwornikowi

potokowemu generować wartość cyfrową na jego wyjściu w każdym

cyklu zegara z opóźnieniem NT.

20

20

SZYBKIE PRZETWORNIKI ADC

(High Speed ADCs)

Czas przetwarzania tych przetworników jest równy okresowi

zegara T.

Można wyróżnić następujące rodzaje szybkich przetworników

ADC:

• Przetworniki ADC równoległe lub „Flash” (Parallel or Flash

ADCs);

• Przetworniki ADC interpolacyjne (Interpolating ADCs);

• Przetworniki ADC ze składaniem sygnałów (Folding ADCs):

21

21

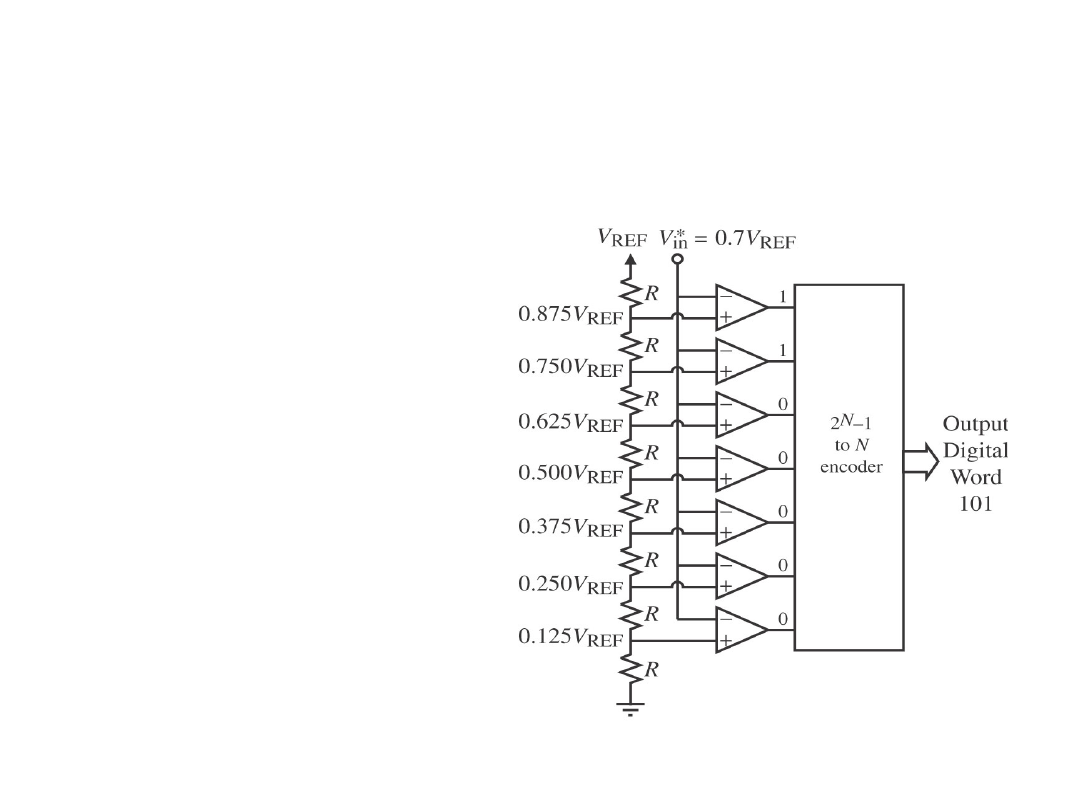

Przetworniki ADC równoległe lub „Flash”

(Parallel or Flash ADCs)

• W pierwszej fazie zegara

analogowy sygnał wejściowy

wprowadzony jest do wejścia

układu S/H. W drugiej fazie

zegara enkoder cyfrowy

określa właściwą wartość

cyfrowego sygnału

wyjściowego.

• Wymagana liczba

komparatorów wynosi 2

N

– 1.

• Można zastosować wejściowy

układ S/H lub synchroniczne

komparatory z zegarem.

• Typowe częstotliwości

próbkowania mogą być 400

MHz dla 6-cio bitowych

przetworników A-C w sub-

mikronowej technologii CMOS.

22

22

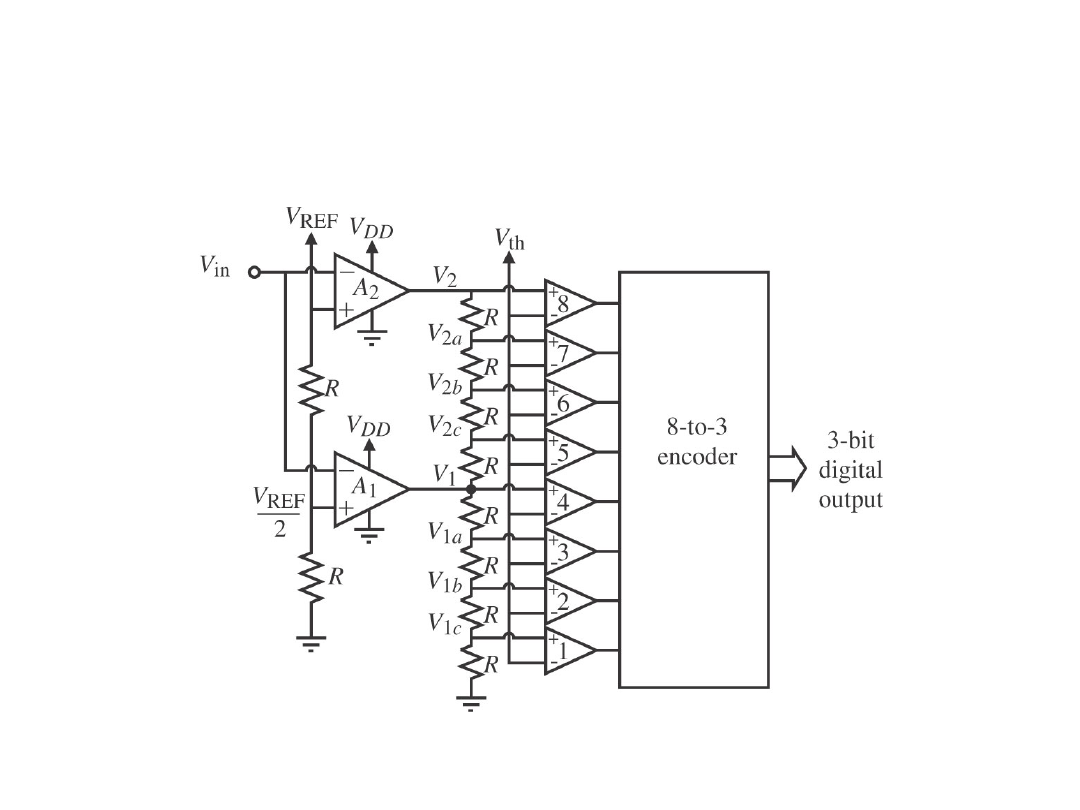

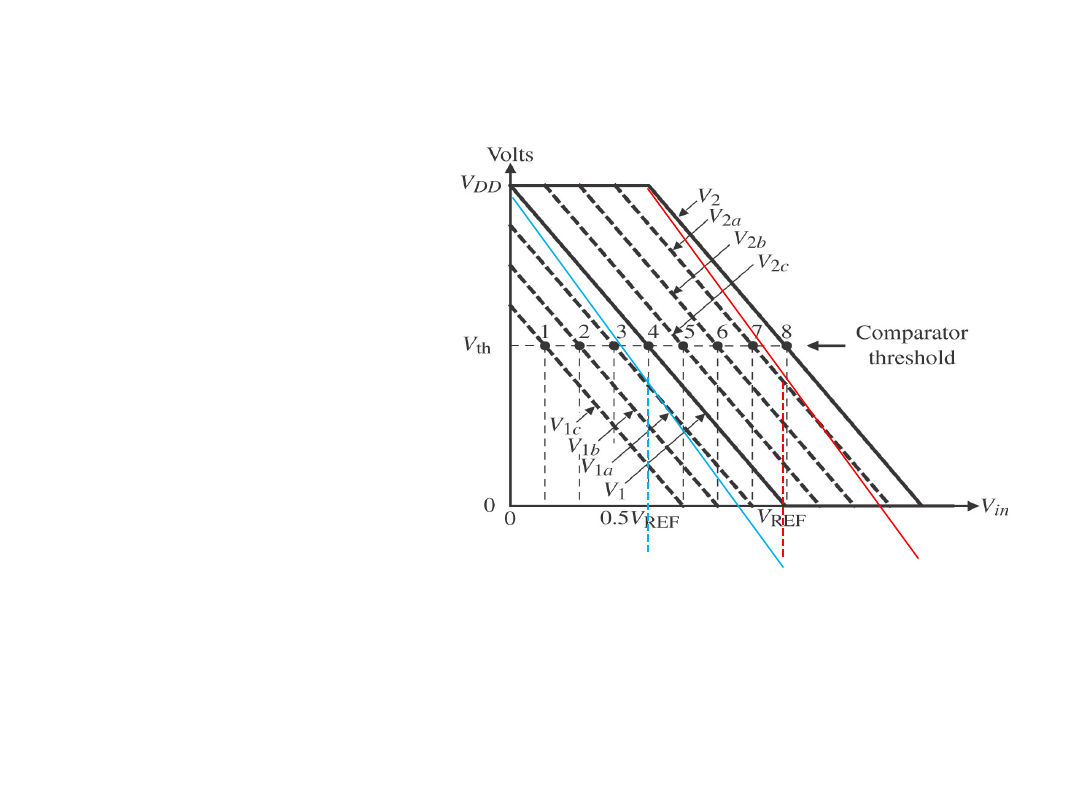

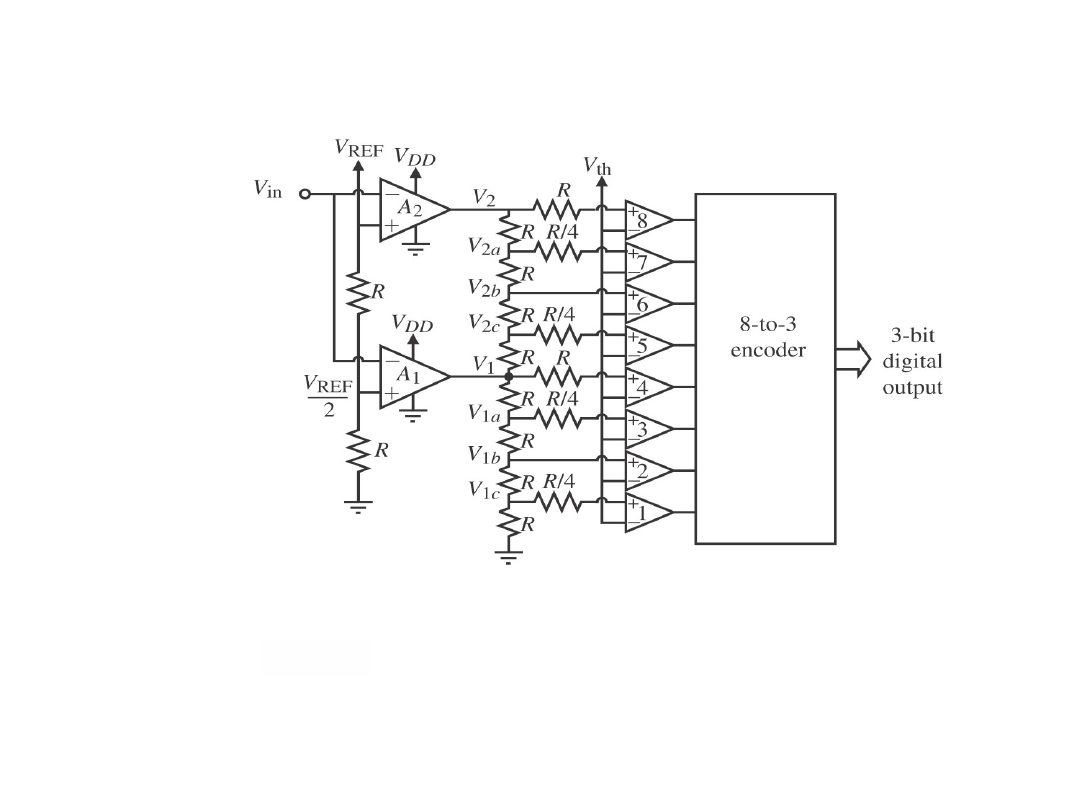

Przetworniki ADC interpolacyjne (Interpolating

ADCs)

3-bitowy przetwornik interpolacyjny ADC, ze współczynnikiem interpolacji

równym 4.

23

23

Przetworniki ADC interpolacyjne (Interpolating

ADCs)

Jeżeli odstępy linii na rysunku nie będą równe, to będzie to

skutkowało w wartościach błędów INL i DNL.

V

REF

i V

REF

/2

stanowią

masy

wirtualne

wzmacniacz

y

operacyjnyc

h

• Obciążenia wejścia jest

zredukowane z 8 wejść

komparatorów do 2 wejść

wzmacniaczy;

• Komparatory nie wymagają

dużych wartości ICMR;

• V

1

i V

2

są interpolowane przez

szereg rezystorów i

zastosowane komparatory;

• Ze względu na wzmocnienie

sygnału wejściowego i jedno

wspólne (takie samo) napięcie

referencyjne, komparatory

mogą być proste i często

stosowane w postaci układów

typu latch.

24

24

3-bitowy przetworniki interpolacyjne

ADC z

wyrównanym opóźnieniem komparatorów

Pewnym problemem interpolacji napięcia, przy stosowaniu elementów

pasywnych (rezystorów), może być to, że opóźnienie sygnału z wyjścia

wzmacniacza do wejścia komparatora może być różne (hazardy). Problem

ten został rozwiązany w przedstawionym na rysunku układzie.

25

25

W przetwornikach z próbkowaniem nadmiarowym (ang.

oversampled converter) dużą rozdzielczość przetwarzania osiąga

się przy użyciu stosunkowo prostych przetworników A/C i C/A i

próbkowaniu sygnału z częstotliwością znacznie przekraczającą

częstotliwość Nyquista. Ze względu na nadpróbkowanie, moc

szumu

kwantyzacji

rozkłada

się

w

szerszym

paśmie

częstotliwości, a zatem przy niezmienionym paśmie użytecznym

stosunek sygnał - szum rośnie. Przykładowo, jeżeli zwiększymy

częstotliwość próbkowania dwukrotnie, to można spodziewać się

dwukrotnego wzrostu SNR, czyli wzrostu o 3 dB, co odpowiada

zwiększeniu rozdzielczości o pół bitu. Efekt ten jest zatem

interesujący, ale niezbyt atrakcyjny –

zwiększenie rozdzielczości

na tej drodze o jeden bit wymaga czterokrotnego wzrostu

częstotliwości próbkowania i rośnie wykładniczo.

Próbkowanie nadmiarowe jest mimo wszystko atrakcyjne, co

wynika z możliwości kształtowania szumu kwantyzacji przez

zamianę charakteru błędu konwersji. Dzięki temu następuje

zamiana widma szumu polegająca na przesunięciu jego

dominujących składowych do zakresu wysokich częstotliwości –

poza

pasmo

sygnału.

Przetworniki

z

próbkowaniem

nadmiarowym są zatem często określane mianem przetworników

z kształtowaniem szumu (ang. noise shaping converters

).

Technika ta pozwala na osiągnięcie rozdzielczości 16-18 bitów

przy użyciu przetwornika jednobitowego, czyli komparatora.

PRZETWORNIKI Z PRÓBKOWANIEM

NADMIAROWYM

26

26

CHARAKTERYSTYCZNE

CECHY

PRZETWORNIKÓW

Z

NADPRÓBKOWANIEM

•Technika ta pozwala na osiągnięcie rozdzielczości 16÷18 bitów przy

paśmie przetwarzanych sygnałów do 50 kHz i 8 ÷10 bitów przy paśmie

przetwarzanych sygnałów do 5 ÷ 10 MHz.

• Współczynnik nadpróbkowania M jest stosunkiem częstotliwości

zegara do częstotliwości Nyquista dla przetwarzanego sygnału.

Współczynnik ten może być w zakresie od 8 do 256.

• Rozdzielczość przetwornika z nadpróbkowaniem jest proporcjonalna

do współczynnika M.

• Pasmo przetwarzanego sygnału jest odwrotnie proporcjonalne do

współczynnika M.

• Przetwarzanie z nadpróbkowaniem jest kompatybilne z techniką

VLSI, ponieważ w większości wykorzystuje układy cyfrowe.

• Charakteryzuje się wysoką rozdzielczością.

• Wykorzystuje jednobitowy kwantyzator, czyli nie zawiera błędów INL i

DNL.

• Pozwala na kompromisy pomiędzy szybkością a dokładnością

przetwarzania.

WADY PRZETWORNIKÓW Z NADPRÓBKOWANIEM

•

Trudności w modelowaniu i symulacji.

•

Ograniczone pasmo przetwarzanych sygnałów do wartości

częstotliwości sygnału dzielonej przez współczynnik nadpróbkowania.

PRZETWORNIKI Z NADPRÓBKOWANIEM

27

27

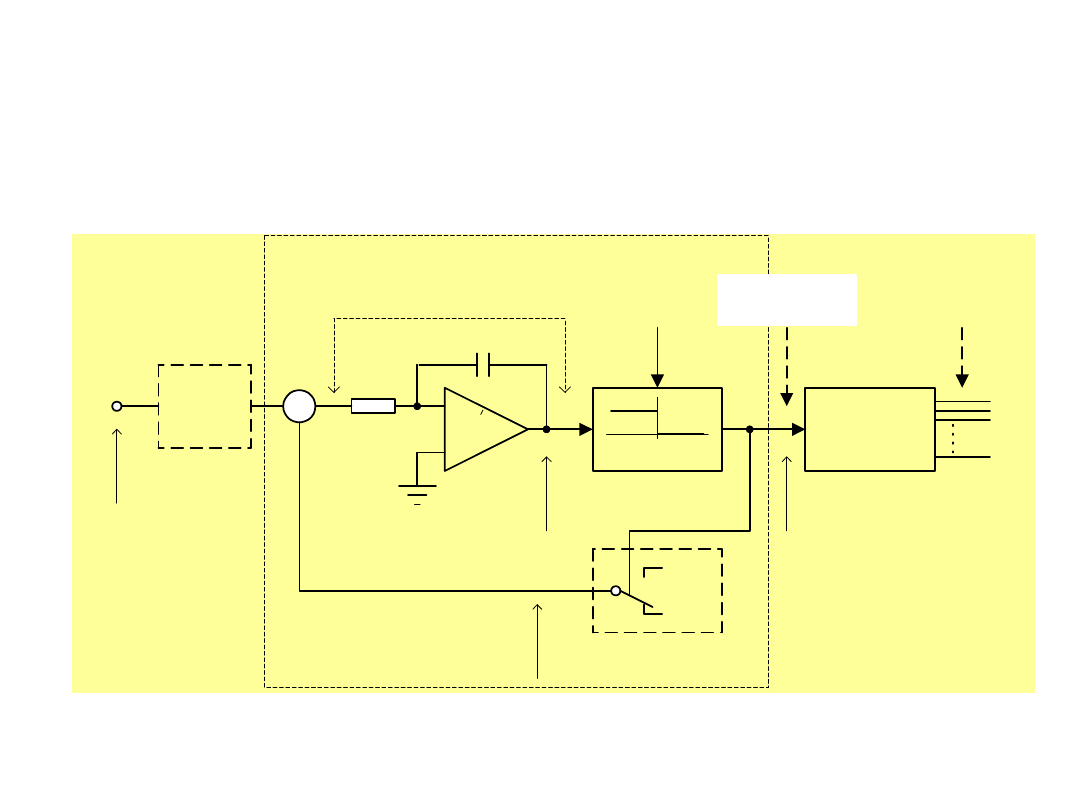

C

A

R

Filtr

cyfrowy

Komparator

1-bitowy

przetwornik A/C

Integrator (filtr DP)

u

INTG

u

AC

U

REF

U

REF

1-bitowy przetwornik C/A

Zegar

f

s

=11,29MHz

u

CA

Modulator sigma - delta

16 bitów

f

so

=44,1kHz

Filtr

antyalia-

singowy

1 bit

f

si

=11,29MHz

u

IN

Prosty układ jednobitowego przetwornika

A/C z próbkowaniem nadmiarowym

28

28

Najprostszy schemat blokowy jednobitowego przetwornika A/C,

zawiera modulator sigma - delta, składający się z integratora,

strobowanego komparatora i jednobitowego przetwornika C/A

sterowanego sygnałem cyfrowym z wyjścia komparatora.

Ponadto przetwornik zawiera filtr cyfrowy, który przekształca

wejściowy sygnał jednobitowy o częstotliwości f

si

na ciąg słów

wielobitowych o znacznie niższej częstotliwości f

so

. Równocześnie

przetwornik filtruje widmo sygnału analogowego reprezentowanego

przez sygnał cyfrowy. Działanie przetwornika można najłatwiej

zilustrować w dziedzinie czasu, a parametry przetwornika łatwiej

wyznacza się w dziedzinie częstotliwości.

Przetwornik jest układem z ujemnym sprzężeniem zwrotnym

dążącym do stanu równowagi, w którym średni ładunek

zgromadzony w kondensatorze C integratora jest zerowy. Gdy

napięcie wyjściowe integratora jest ujemne (u

IN

< 0), to komparator

w każdym okresie zegara znajduje się w stanie wysokim na wyjściu

(bit=1), co powoduje, że klucz w przetworniku C/A jest dołączony do

napięcia U

REF

.

Wywołuje to dopływ ujemnego ładunku do integratora i wzrost

napięcia u

INTG

w kierunku zera.

Im bardziej dodatnie jest napięcie

wejściowe, tym większy jest stosunek jedynek do zer w sygnale

wyjściowym komparatora.

Gdy u

INTG

< 0 , to komparator znajduje się

w stanie niskim na wyjściu (bit=0) i następuje ładowanie

kondensatora C w przeciwnym kierunku. Przy zerowym napięciu

wejściowym

układ

generuje

symetryczny

ciąg

impulsów

prostokątnych o niewielkiej amplitudzie. Cały przetwornik może być

w dziedzinie czasu rozważany jako układ z równoważeniem ładunku,

przekształcającym napięcie wejściowe na ciąg impulsów o

modulowanej gęstości.

29

29

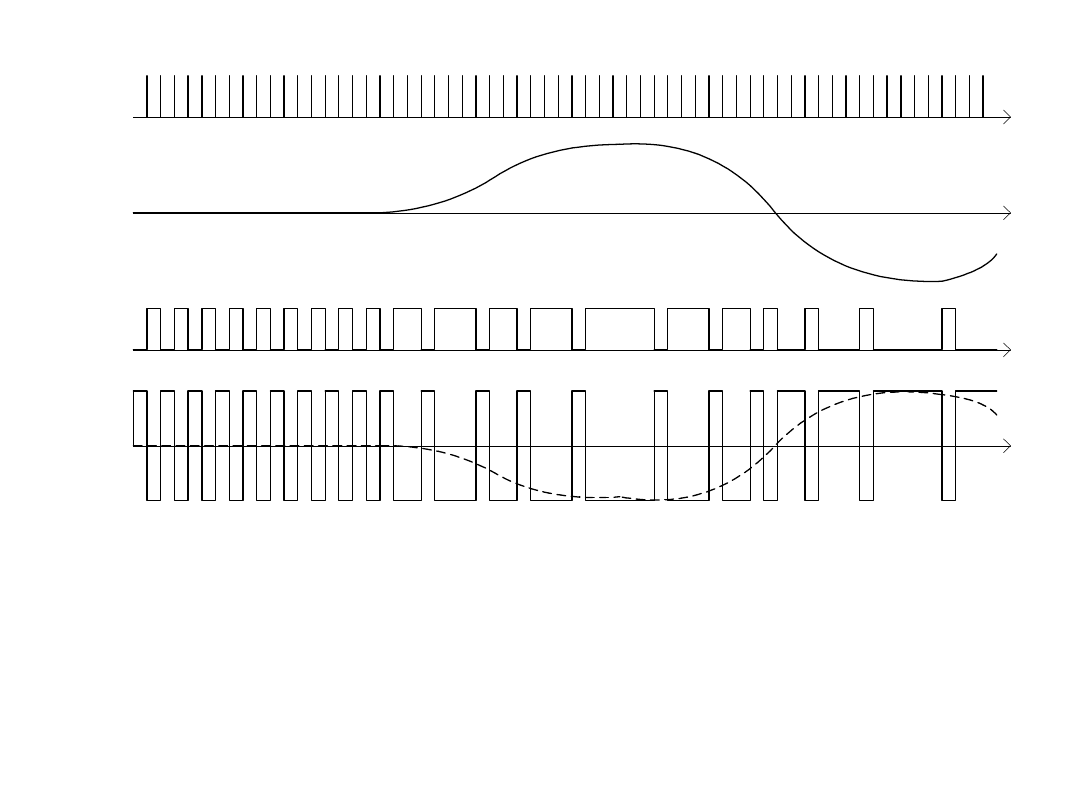

t

t

t

t

Zegar

u

IN

u

AC

u

CA

U

REF

U

REF

Przebiegi czasowe napięć w przetworniku

jednobitowym

Rolą integratora jest całkowanie sygnału błędu będącego różnicą

między aktualnym napięciem wejściowym a szacunkową wartością

tego napięcia, generowaną przez przetwornik C/A na podstawie

poprzednich próbek sygnału. Stała czasowa powinna być większa niż

okres próbkowania T

s

i jednocześnie dostatecznie mała w

porównaniu z okresem T

s

= 1 / ω

g

, odpowiadającym górnej

częstotliwości pasma sygnału wejściowego.

30

30

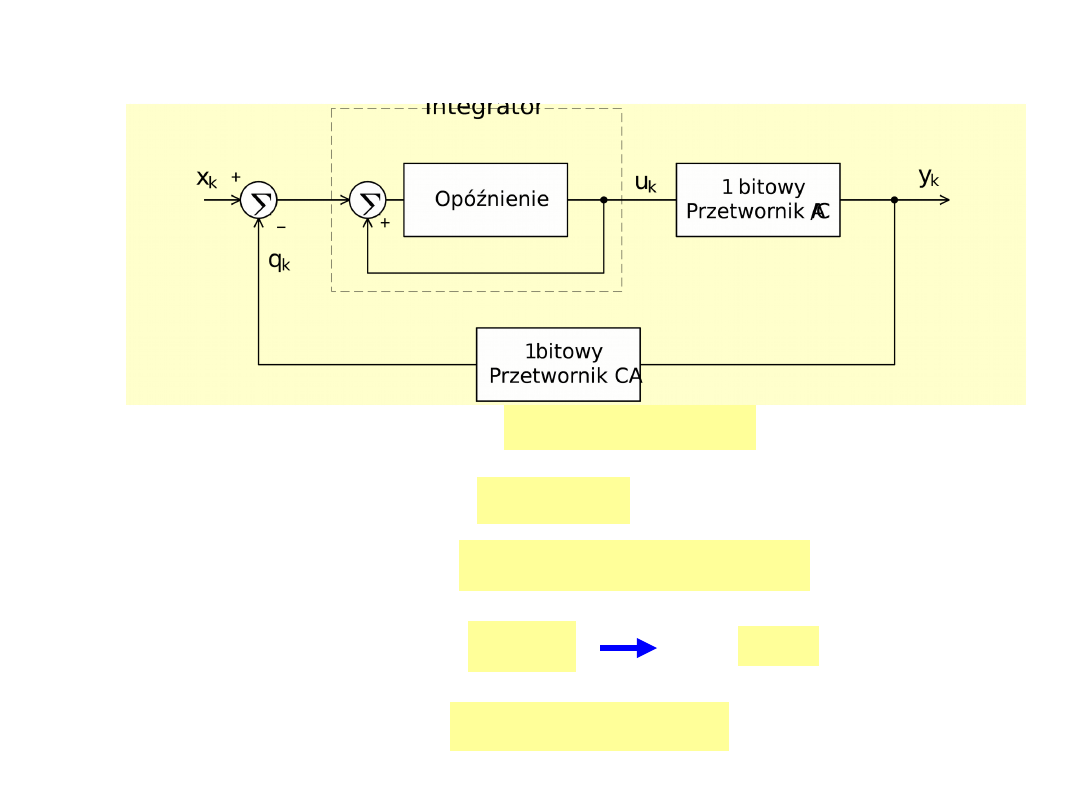

Schemat blokowy modulatora sigma-

delta

1

1

1

k

k

k

k

u

q

x

u

k

k

k

u

y

q

1

1

1

k

k

k

k

k

u

q

x

q

y

k

k

y

q

1

1

k

k

k

k

q

q

x

y

- sygnał na wyjściu

integratora:

- błąd kwantyzacji wnoszony przez przetwornik jednobitowy

- na podstawie powyższych równań, sygnał wyjściowy opisany jest

równaniem

- dla idealnego przetwornika C/A w układzie można zapisać

Na podstawie powyższych równań

otrzymujemy

tzn.

0

k

u

31

31

X(s)

1/s

Y(s)

Q(s)

Model częstotliwościowy modulatora

sigma-delta

s

Y

s

X

s

s

Q

s

Y

1

s

s

X

s

s

s

Q

s

Y

1

1

1

Na wyjściu układu pojawia się z opóźnieniem o jeden cykl skwantowana

wartość sygnału wejściowego powiększona o różnicę błędów kwantyzacji

cyklu bieżącego i poprzedniego. Można więc powiedzieć, że mamy do

czynienia z częściową kompensacją błędu kwantyzacji.

Inne wyjaśnienie zachodzącego zjawiska można przeprowadzić

rozważając model częstotliwościowy układu pracującego w czasie

ciągłym.

Człon opóźniający ma

postać idealnego

integratora, jednobitowy

przetwornik A/C jest

przedstawiony jako

addytywny szum, a

idealny przetwornik C/A

jest bezimpedancyjnym

połączeniem.

32

32

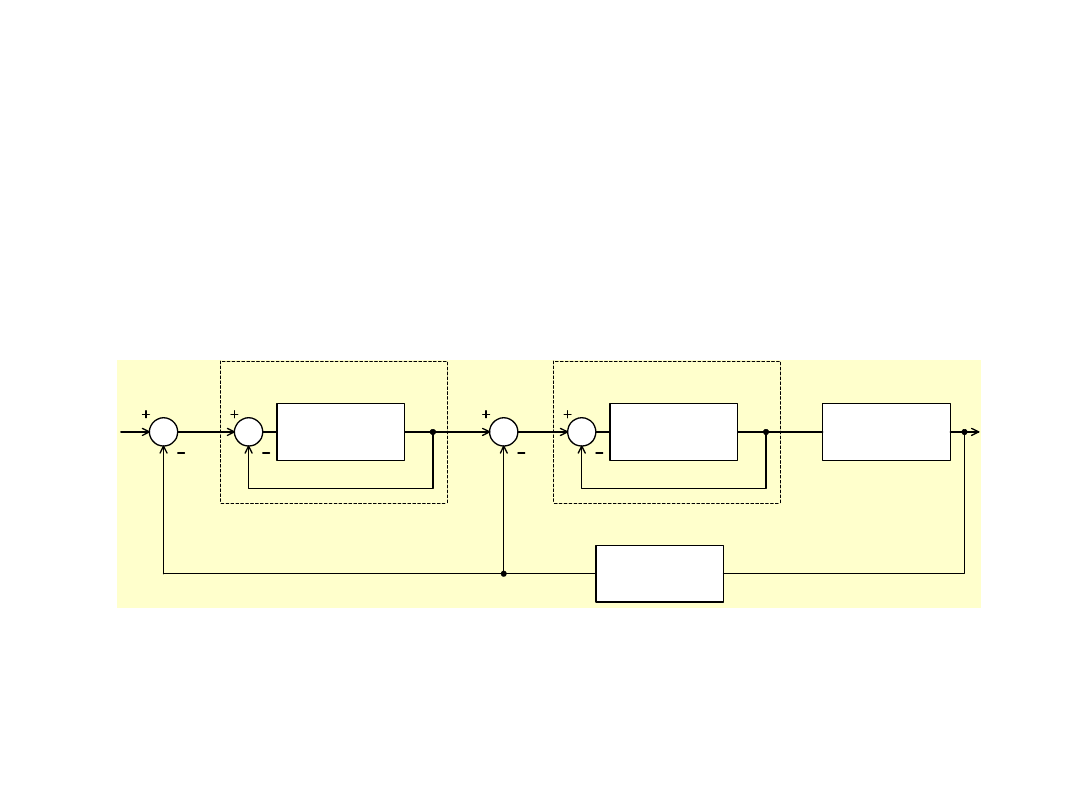

A/C 1 bit

C/A 1 bit

q

k

Opóźnienie

Integrator 1

Opóźnienie

Integrator 2

x

k

y

k

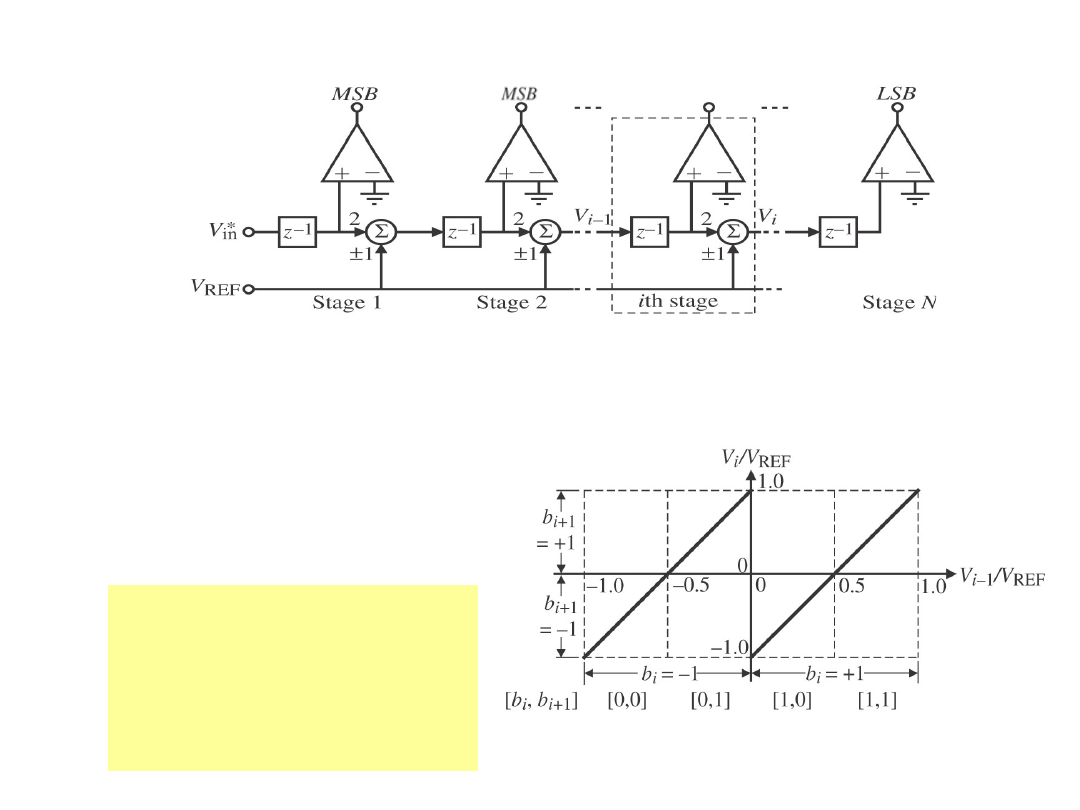

Zauważamy, że o ile sygnał wejściowy jest poddawany filtracji

dolnoprzepustowej, to szum kwantyzacji – górnoprzepustowej. Ten

zabieg jest charakterystyczny dla wszystkich metod kształtowania

widma szumu i skutkuje znaczną redukcją mocy szumu kwantyzacji w

użytecznym paśmie kosztem jej zwiększenia w obszarze górnych

częstotliwości. Łatwo zauważyć, że kluczowym elementem

odpowiedzialnym za ten proces jest integrator. Użycie większej liczby

integratorów jest możliwe i często stosowane praktycznie. Otrzymujemy

wtedy przetworniki wyższych rzędów.

Przetwornik sigma-delta drugiego

rzędu

33

33

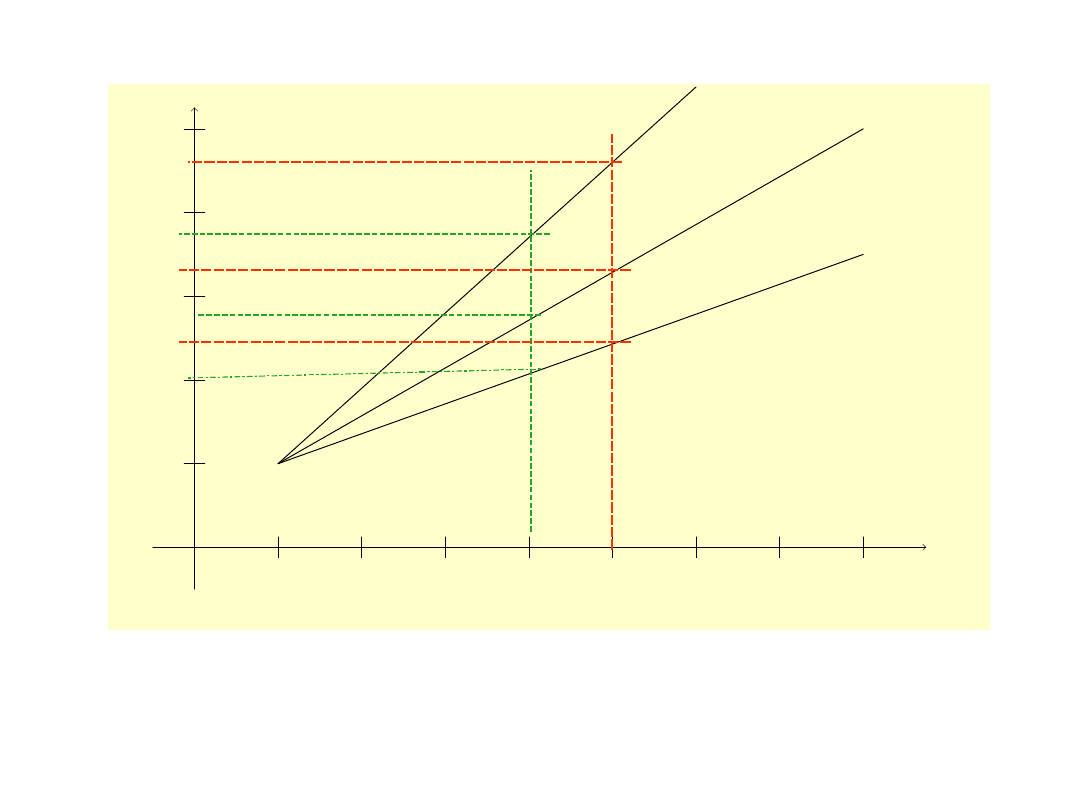

Współczynnik nadpróbkowania

4

8

16

32

64

128

256

512

4

8

12

16

20

Pierwszy rząd

Drugi rząd

Trzeci rząd

Ro

zdz

ielc

zoś

ć w

bit

ach

Zależność efektywnej rozdzielczości przetworników jednobitowych

pierwszego,

drugiego i trzeciego rzędu od współczynnika nadmiarowości

próbkowania

34

34

Budowane są przetworniki jeszcze wyższych rzędów. Nie

można jednak zapominać, że są to mimo wszystko układy z

wielopętlowym sprzężeniem zwrotnym i krytycznym

zagadnieniem staje się stabilność takiego systemu.

Ważnym elementem przetwornika z próbkowaniem

nadmiarowym jest wyjściowy filtr cyfrowy. Spełnia on dwie

bardzo ważne funkcje. Pierwsza to eliminacja szumu

kwantyzacji powyżej pasma sygnału wejściowego, zaś druga

polega na przekształcaniu ciągu jednobitowych liczb

wytwarzanych przez lokalny przetwornik A/C, o dużej

częstotliwości powtarzania , na wielobitowe słowa

wyjściowe wytwarzane z częstotliwością M razy mniejszą.

Proces jednoczesnej filtracji dolnoprzepustowej oraz obniżania

częstotliwości próbkowania nazywany jest filtrowanien

rozrzedzającym (ang. decimating filtering, decimation).

f

s

Document Outline

- Slide 1

- Slide 2

- Slide 3

- Slide 4

- Slide 5

- Slide 6

- Slide 7

- Slide 8

- Slide 9

- Slide 10

- Slide 11

- Slide 12

- Slide 13

- Slide 14

- Slide 15

- Slide 16

- Slide 17

- Slide 18

- Slide 19

- Slide 20

- Slide 21

- Slide 22

- Slide 23

- Slide 24

- Slide 25

- Slide 26

- Slide 27

- Slide 28

- Slide 29

- Slide 30

- Slide 31

- Slide 32

- Slide 33

- Slide 34

Wyszukiwarka

Podobne podstrony:

W10 Przetw A C

przetworniki indukcyjne

Prop aut W9 Ses cyfr Przetworniki fotoelektryczne

Przetworstwo produktow rolniczych

MLEKO I PRZETWORY MLECZNE (2)

Ceny detaliczne i spożycie warzyw i ich przetworów

spoleczna w10

W10

W10

W9 Przetw C A

Filozofia W10 Etyka Zagadnienie norm lepsza wersja2 0bezKanta

W10 Ja Spoleczne

W10 Wpływ różnych metod obróbki wstępnej mięsa

więcej podobnych podstron