W.7. PRZETWORNIKI

C/A

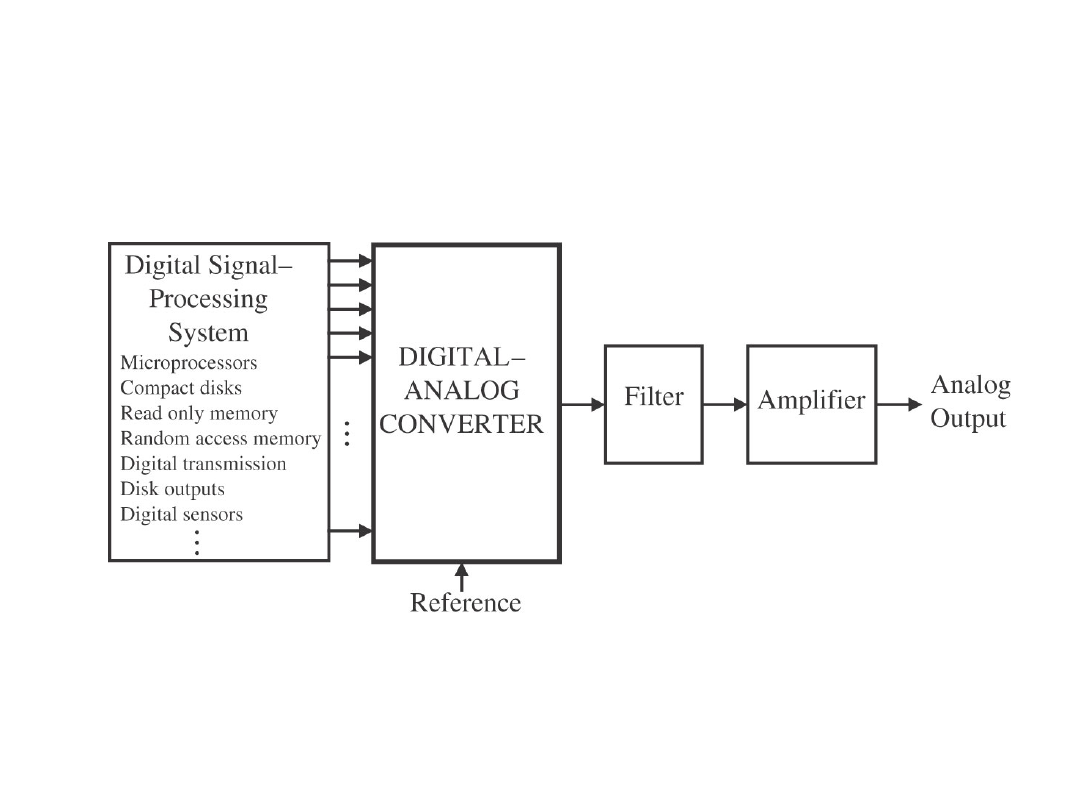

Przetworniki C-A w różnych

zastosowaniach przetwarzania sygnałów

Klasyfikacja przetworników C-A

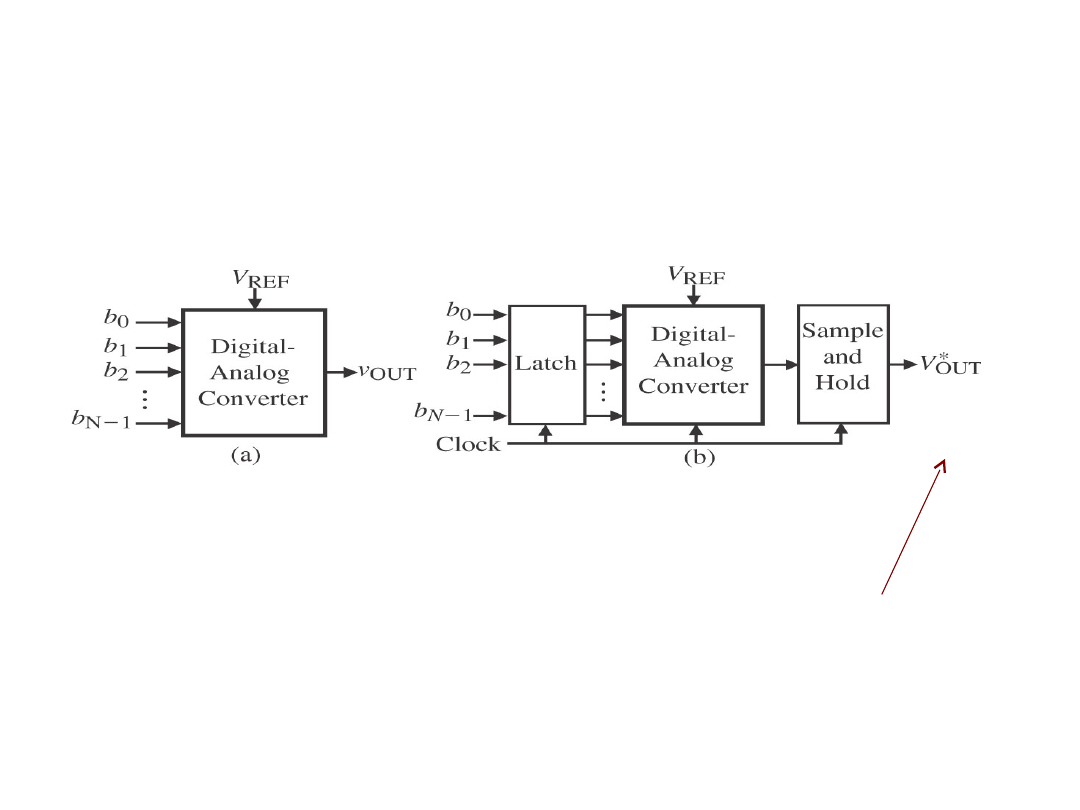

Asynchroniczne (a) i synchroniczne (b)

Gwiazdka oznacza sygnał próbkowany z pamięcią

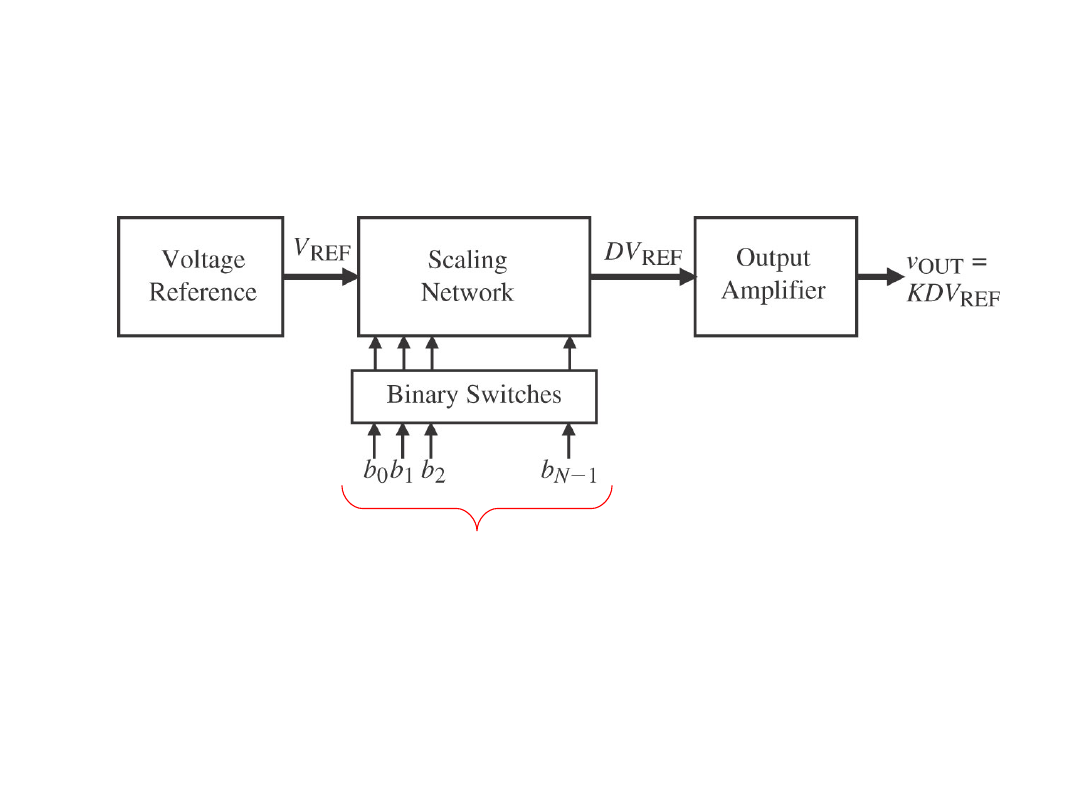

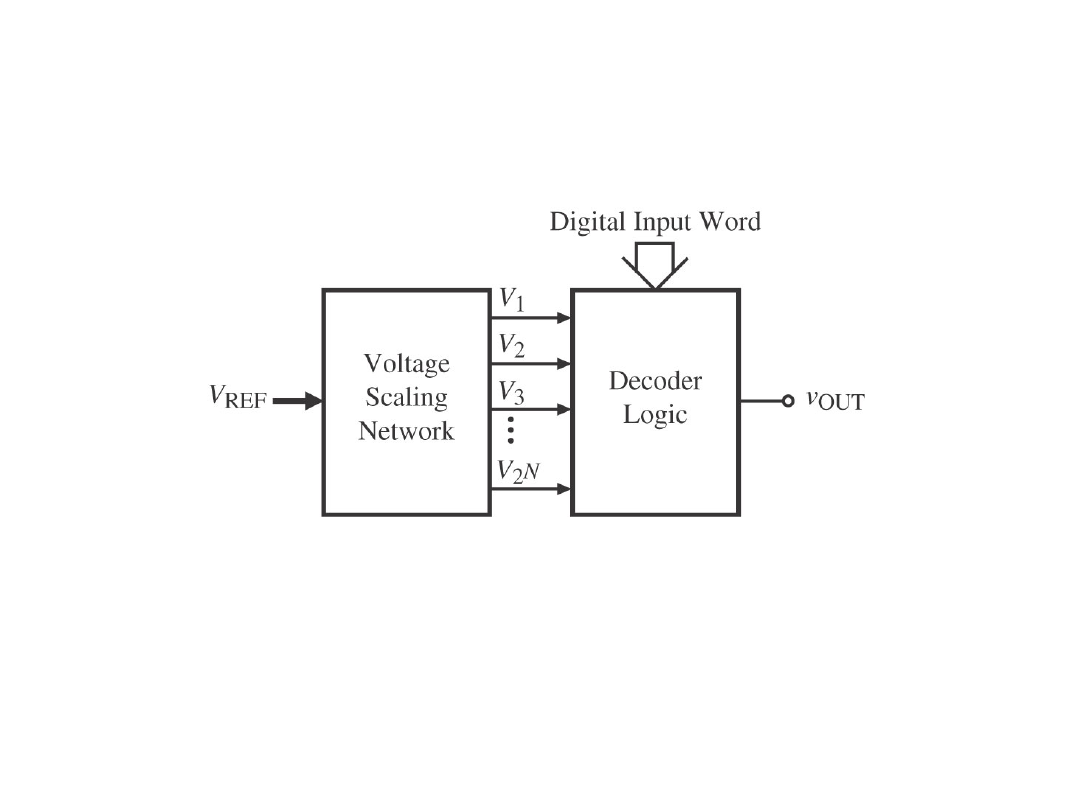

Schemat blokowy przetwornika C-A

b

0

– the most significant bit (MSB) bit najbardziej

znaczący

b

N-1

– the least significant bit (LSB) bit najmniej znaczący

D

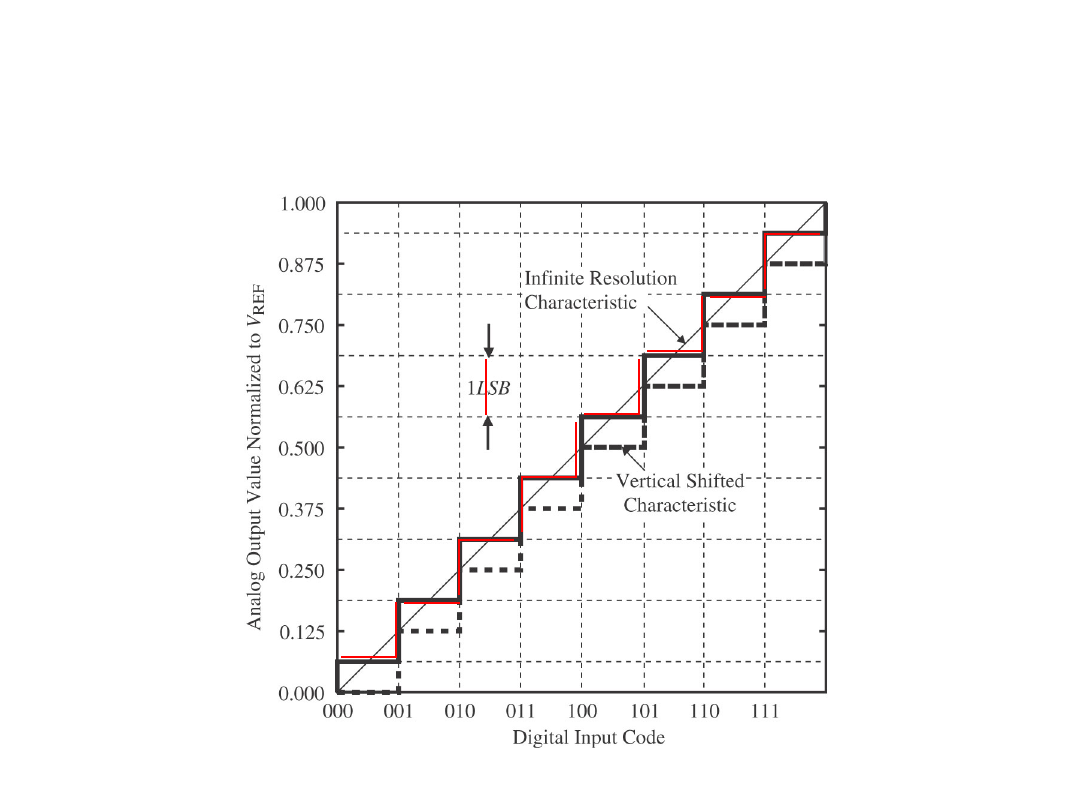

Charakterystyka przejściowa przetwornika

C-A

(3- bitowy)

DEFINICJE

1. Rozdzielczość (Resolution) przetwornika DAC jest równa liczbie

bitów zastosowanego słowa cyfrowego.

2. Pełny zakres (Full scale FS) jest różnicą: (Wyjście analogowe, gdy

wszystkie bity są równe 1) minus (Wyjście analogowe, gdy wszystkie

bity są równe 0).

3. Granica pełnego zakresu (Full scale range) jest definiowanya jako:

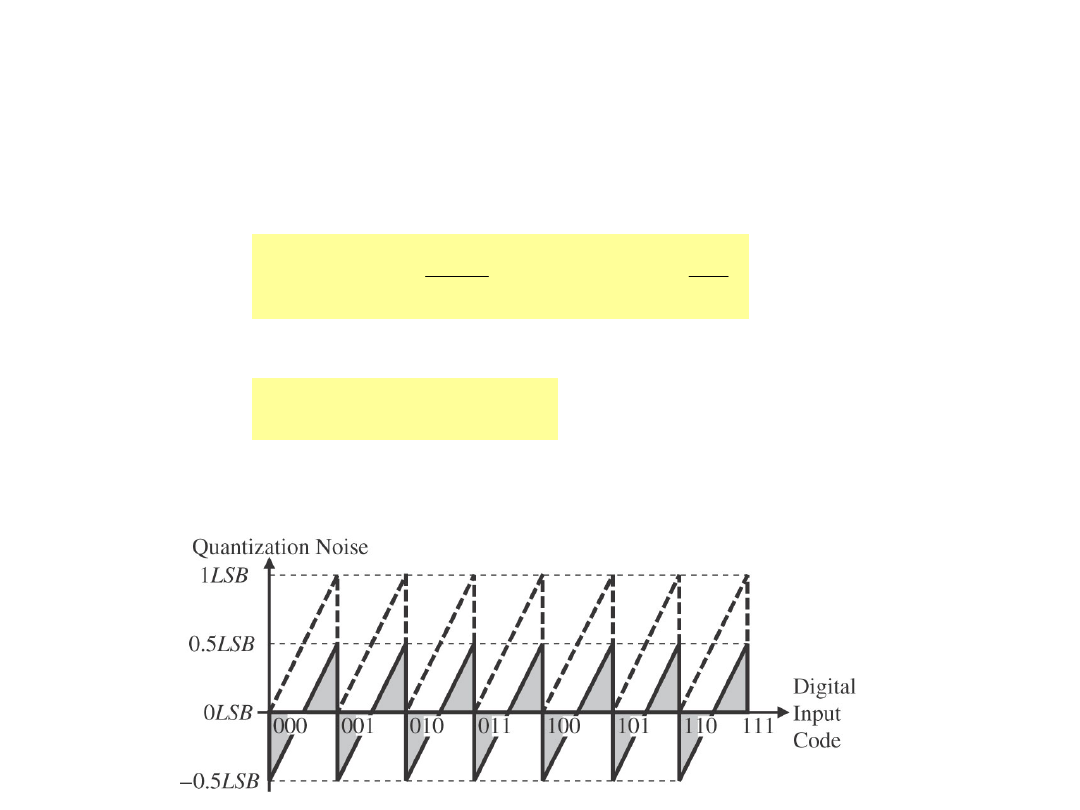

4. Szum kwantyzacji jest naturalną niedokładnością w cyfryzacji

wartości analogowej ze skończoną rozdzielczością przetwornika.

N

REF

N

REF

REF

V

V

V

FS

2

1

1

0

2

REF

N

V

FS

FSR

lim

12

2

12

5

,

0

1

)

i

kwantyzacj

szumu

(

2

0

2

N

T

FSR

LSB

dt

T

t

LSB

T

rms

2

2

6

2

12

2

2

2

12

)

(

max

N

N

N

OUT

FSR

FSR

FSR

rms

v

SNR

5. Zakres dynamiczny (DR) przetwornika DAC jest stosunkiem FSR do

najmniejszej różnicy, która może być rozróżniona (tj. LSB).

lub wyrażony w dB:

6. Stosunek sygnał – szum (SNR) jest stosunkiem wartości pełnego

zakresu do średniokwadratowej wartości szumu kwantyzacji:

7. Maksymalna wartość SNR (SNR

max

) dla sinusoidy definiowana jest

jako:

lub w dB

)

dB

(

02

,

6

)

dB

(

N

DR

N

N

FSR

FSR

LSB

FSR

DR

2

2

)

zakres

(

N

OUT

FSR

rms

v

SNR

2

12

)

(

dB

02

,

6

76

,

1

2

log

20

2

log

20

6

log

10

2

2

6

log

20

)

dB

(

max

N

SNR

N

N

2

2

)

(

max

FSR

rms

v

OUT

8

8

9. Efektywna liczba bitów – ENOB (Effective number of bits ):

Gdzie: SNR

Actual

jest aktualną wartością parametru SNR ADC.

Zakres dynamiczny (DR) jest wymaganym zakresem amplitudy, aby

uzyskać rozdzielczość N bitów amplitudy napięcia wyjściowego.

Jednakowoż, odnosząc zadaną amplitudę analogowego sygnału

wyjściowego do napięcia referencyjnego, wymagany zakres

dynamiczny (DR) musi być zwiększony o 1,76 dB, aby uwzględnić

obecność szumu kwantyzacji.

Tak więc, dla 10-bitowego DAC zakres dynamiczny DR wynosi 60.2 dB

i dla pełnego zakresu średniokwadratowej wartości napięcia

wyjściowego (full-scale, rms output voltage), wartość sygnału musi

być 62 dB powyżej jakiegokolwiek poziomu szumów obecnych na

wyjściu przetwornika DAC (noise floor).

02

,

6

76

,

1

Actual

SNR

ENOB

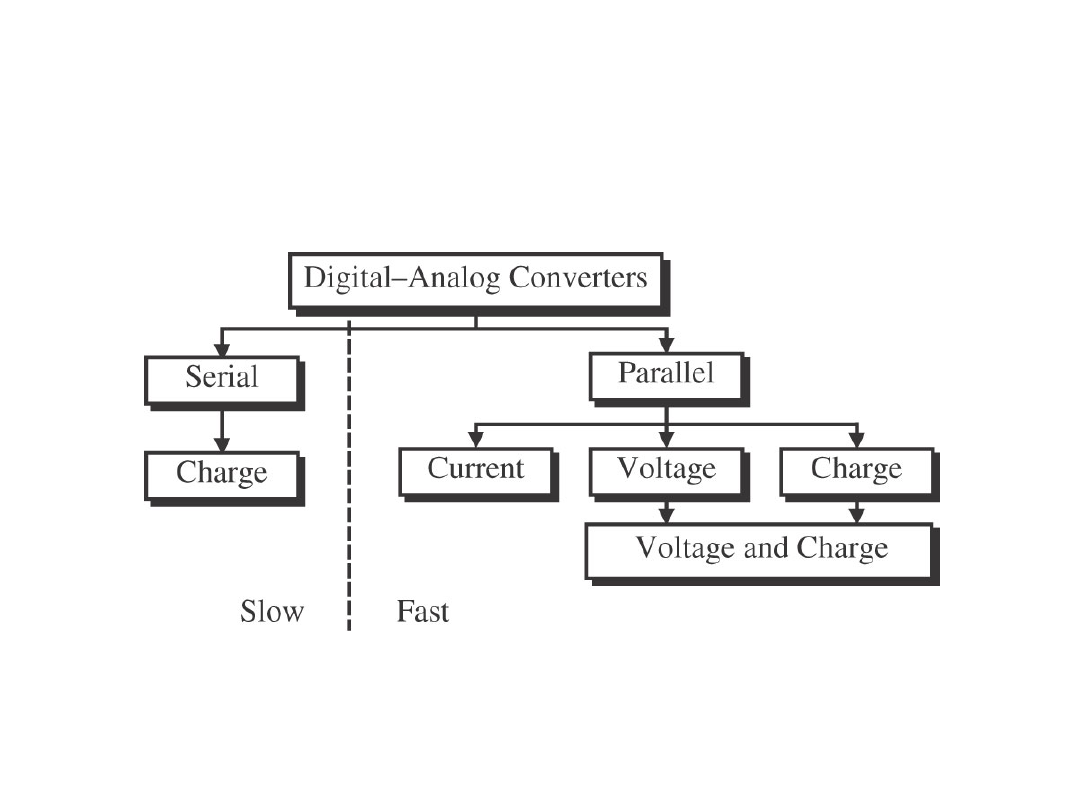

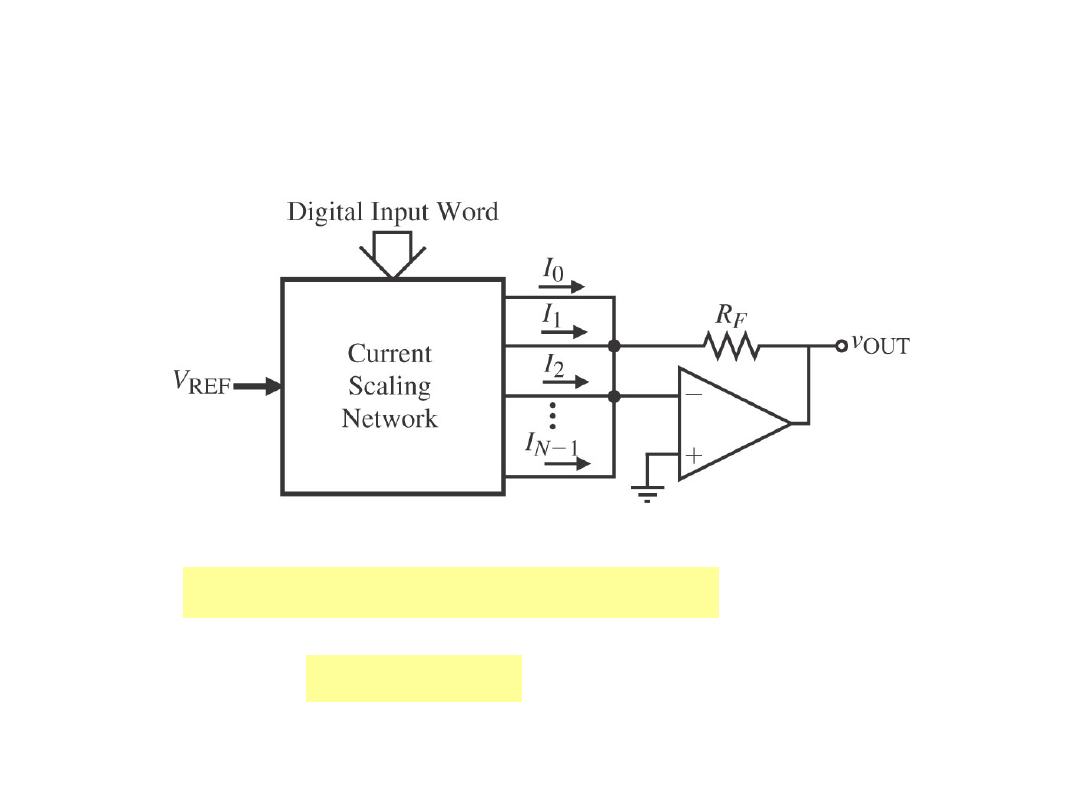

Klasyfikacja przetworników C-A

Przetworniki C-A skalowane prądowo

z binarnie ważonymi prądami

)

......

(

1

2

1

0

N

F

OUT

I

I

I

I

R

v

1

2

1

0

,....,

,

,

N

I

I

I

I

Gdzie: są binarnie ważonymi

prądami

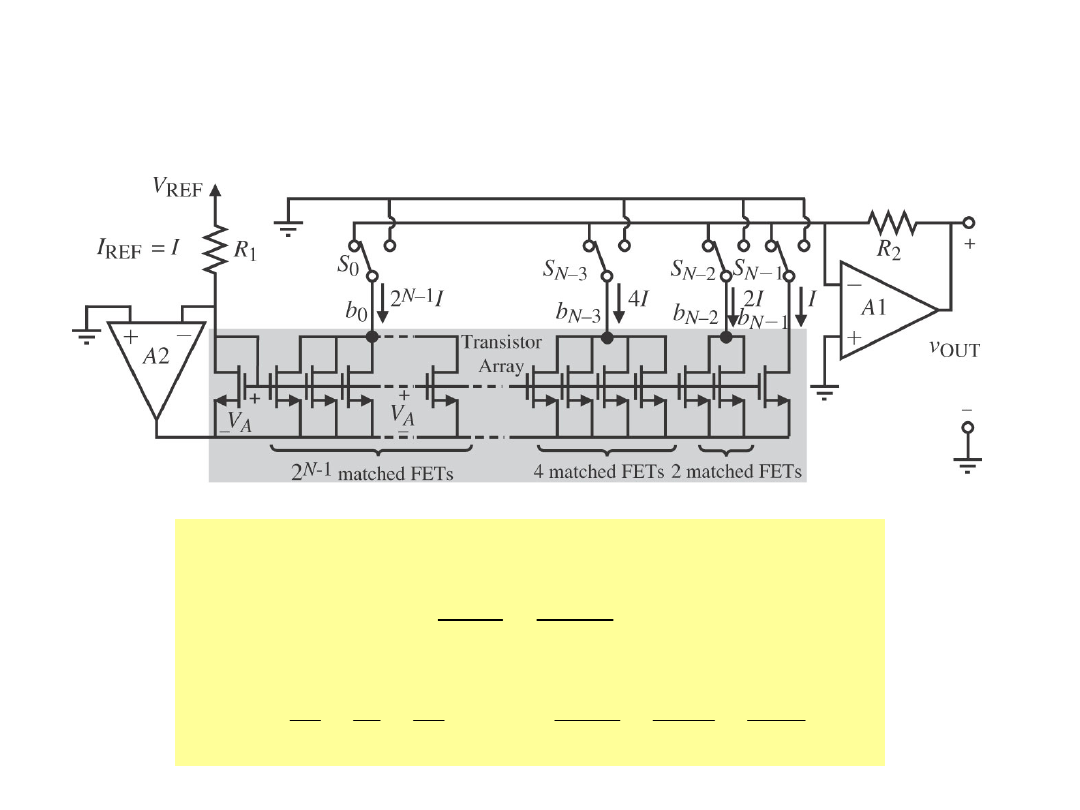

Implementacja przetwornika C-A ze

skalowaniem prądowym z binarnie ważonymi

prądami źródeł prądowych typu absorbcyjnego

(current sinks)

REF

N

N

N

N

N

N

OUT

N

REF

REF

REF

N

N

N

N

OUT

V

b

b

b

b

b

b

v

R

V

R

V

I

I

I

b

I

b

I

b

I

b

R

v

2

2

2

......

8

4

2

2

:

gdy

2

.....

4

2

1

1

2

2

3

2

1

0

2

1

1

0

3

2

1

2

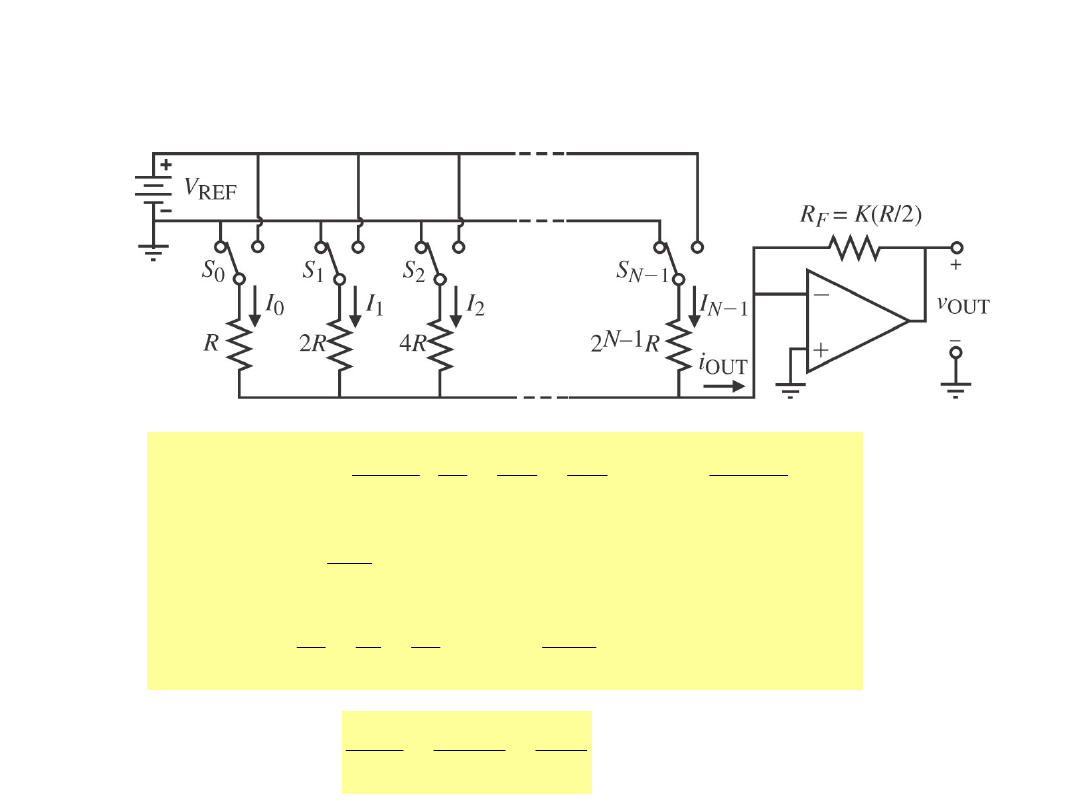

Przetworniki C-A z binarnie ważonymi

rezystorami

REF

N

N

OUT

F

REF

N

N

O

F

OUT

V

b

b

b

b

K

v

KR

R

V

R

b

R

b

R

b

R

b

KR

I

R

v

2

......

8

4

2

2

:

gdy

2

......

4

2

2

1

2

1

0

1

1

2

1

0

1

1

2

1

2

N

N

LSB

MSB

R

R

R

R

2R

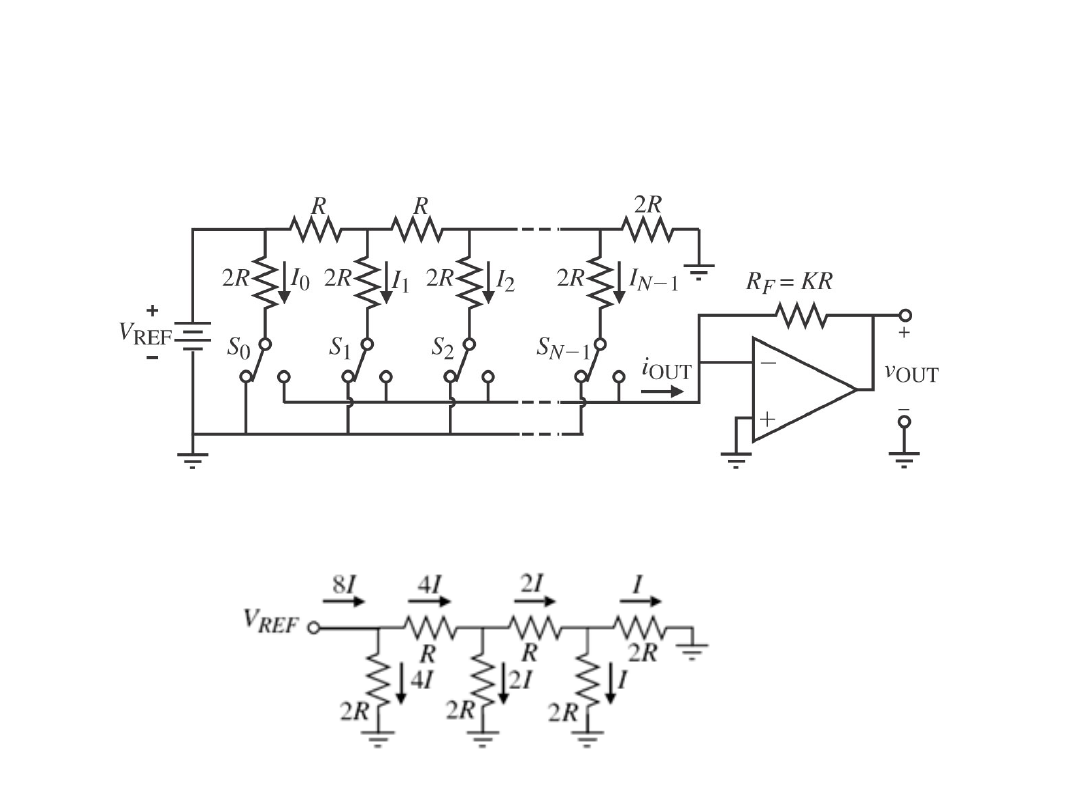

Implementacja przetwornika C-A z binarnie

ważonymi rezystorami za pomocą drabinki

rezystancyjnej R-2R

Zasada działania drabinki rezystancyjnej R-2R

Przetworniki C-A ze skalowanymi

napięciami

Creates all possible values of the analog output then uses a decoding

network to determine which voltage to select - based on the digital

input word.

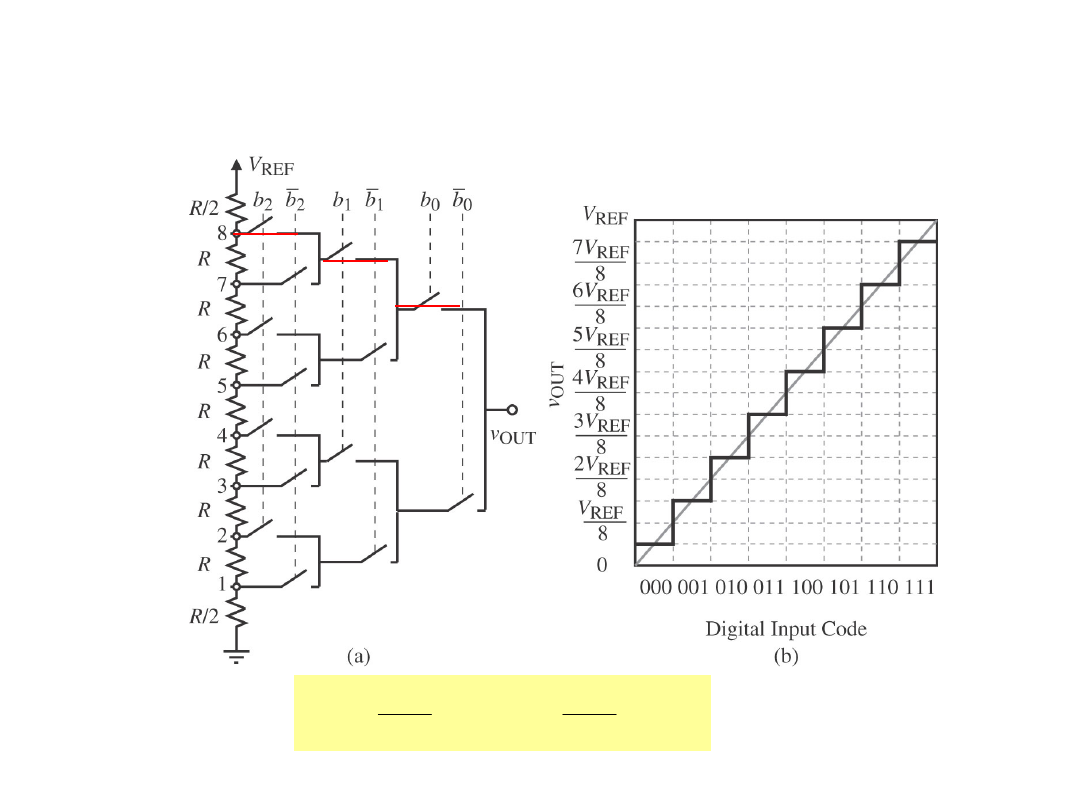

3-bitowy przetworniki C-A skalowany

napięciowo

b

2

= b

1

= b

0

=1

)

1

2

(

16

)

5

,

0

(

8

n

V

n

V

v

REF

REF

OUT

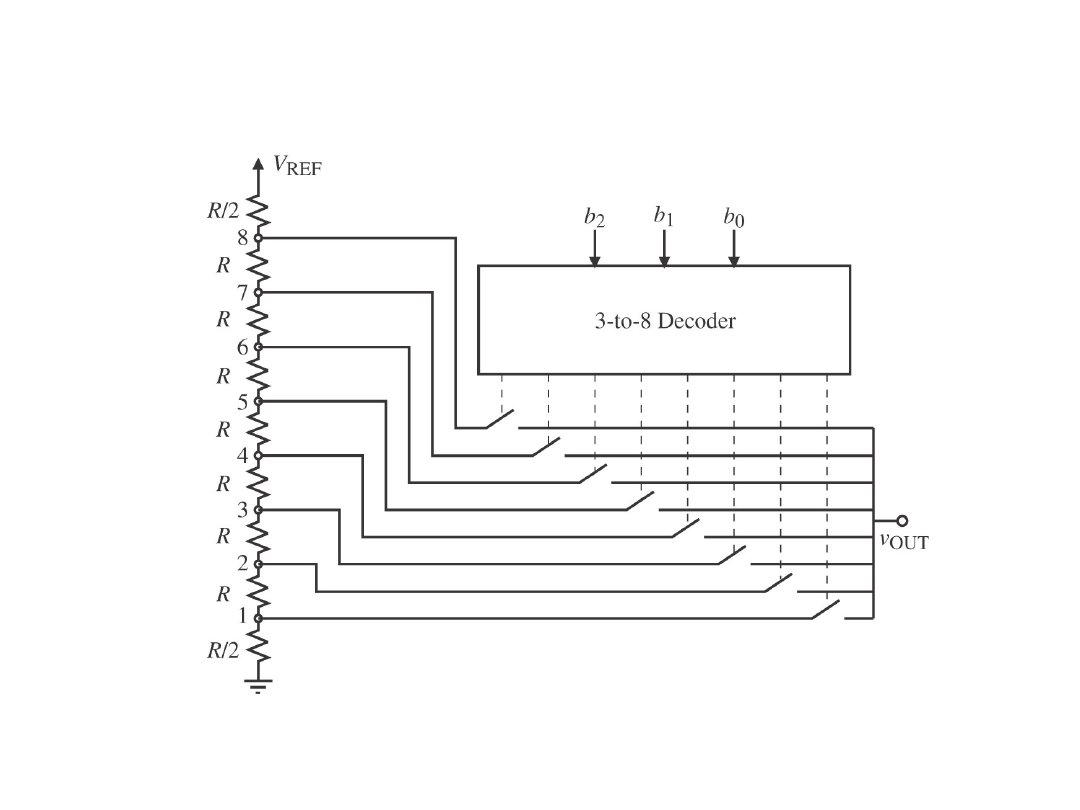

Praktyczna realizacja 3-bitowego

przetworniki C-A ze skalowanymi

napięciami

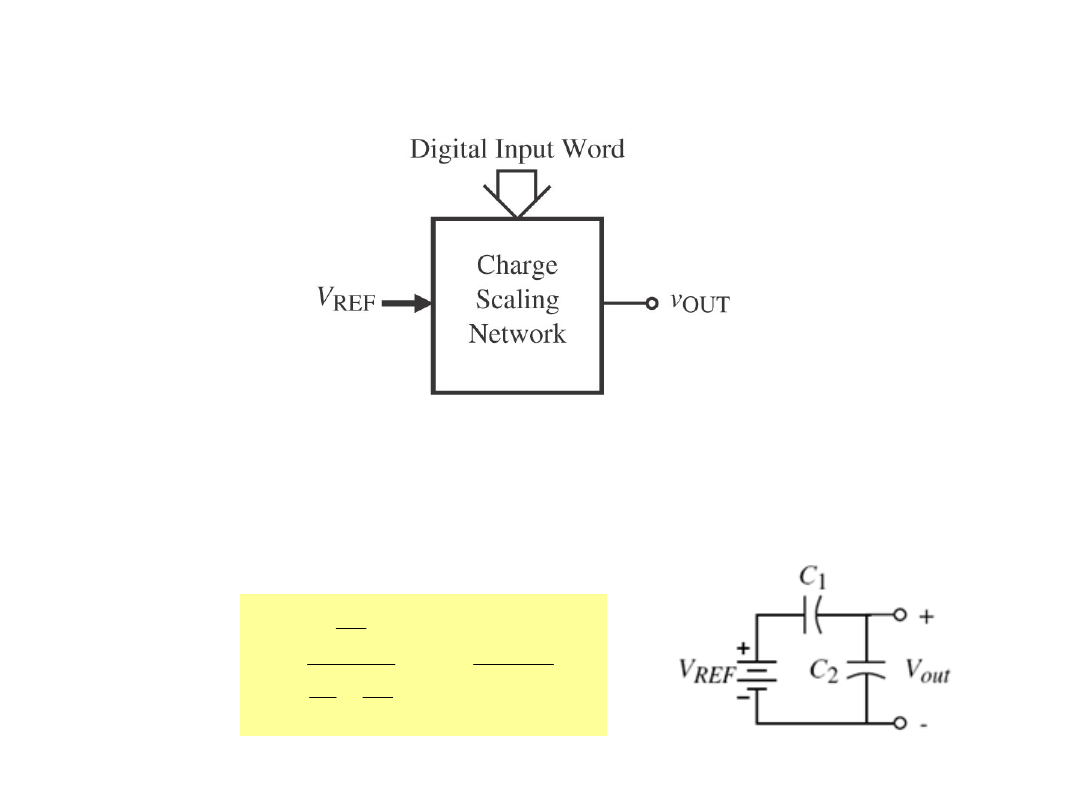

Przetworniki C-A ze skalowanymi ładunkami

Ogólna koncepcja przetwornika C-A ze skalowanymi ładunkami polega na

wykorzystaniu pojemnościowego dzielnika napięcia referencyjnego (w

miejsce rezystancyjnego).

Przykład prostego dzielnika pojemnościowego:

REF

REF

out

V

C

C

C

V

C

C

C

V

2

1

1

2

1

2

1

1

1

1

1

1

0

1

2

2

n

n

C

b

C

b

C

b

C

REF

N

N

REF

REF

O

V

b

b

b

b

V

C

C

V

C

C

C

v

2

....

2

2

2

2

1

3

2

2

1

1

0

1

2

1

1

1

2

2

C

C

C

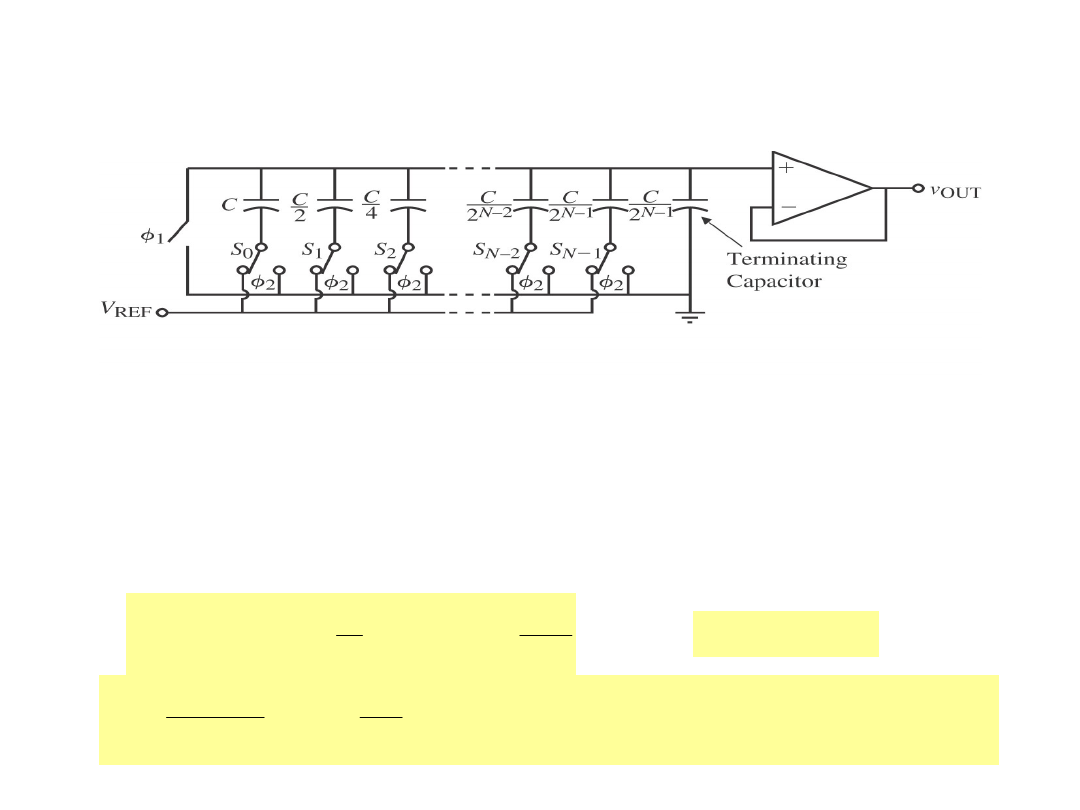

Przetwornik C-A ze skalowanymi ładunkami

ważonymi binarnie

Działanie:

1.) Wszystkie przełączniki dołączone do masy w czasie fazy φ1

(rozładowanie do zera wszystkich pojemności)

.

2). Przełączniki S

i

dołączone do V

REF, jeżeli

b

i

= 1 lub do masy,

gdy b

i

= 0.

Tworzy się zatem dzielnik pojemnościowy, jak na poprzednim

slajdzie, w którym:

19

19

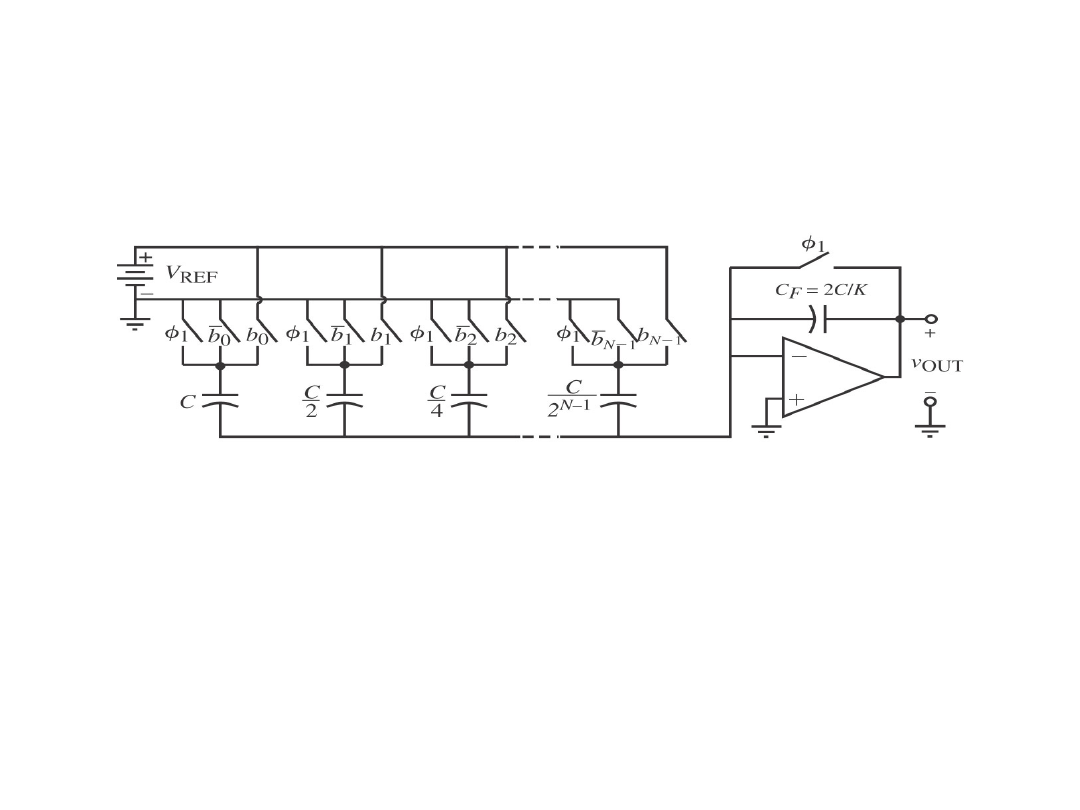

Przetwornik C-A ze wzmacniaczem ładunkowym

ze skalowanymi ładunkami ważonymi binarnie

(Binary Weighted, Charge Amplifier DAC)

Attributes:

• No floating nodes which implies insensitive to parasitics and

fast;

• No terminating capacitor required;

• Can totally eliminate parasitics with parasitic-insensitive

switched capacitor circuitry but not the charge feedthrough

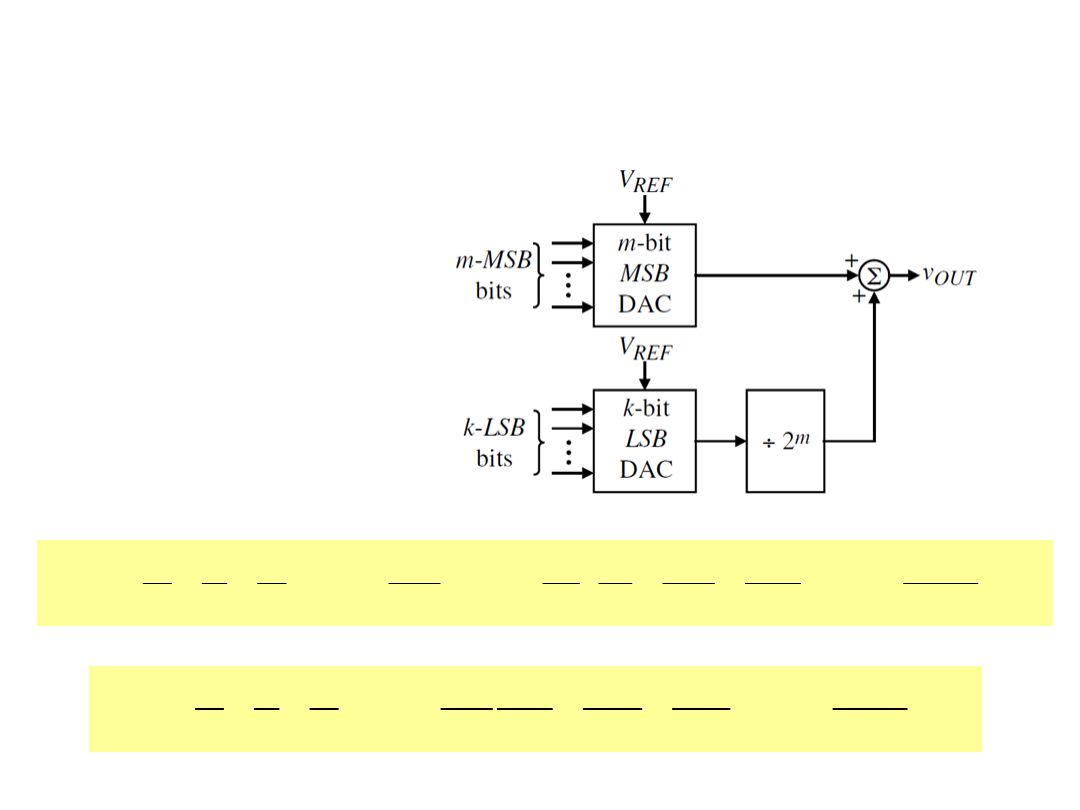

Równoległe przetworniki C-A z rozszerzoną

rozdzielczością

Analog Scaling -

Divider Approach

Example of

combining a m-bit

and k-bit subDAC

to form a (m+k)

-bit DAC.

1

0

2

b

REF

V

REF

k

k

m

m

m

m

m

REF

m

m

OUT

V

b

b

b

b

V

b

b

b

b

v

2

......

8

4

2

2

1

2

......

8

4

2

1

2

1

1

2

1

0

REF

k

m

k

m

m

m

m

m

m

m

m

m

OUT

V

b

b

b

b

b

b

b

b

v

2

......

2

2

2

2

......

8

4

2

1

3

2

2

1

1

1

2

1

0

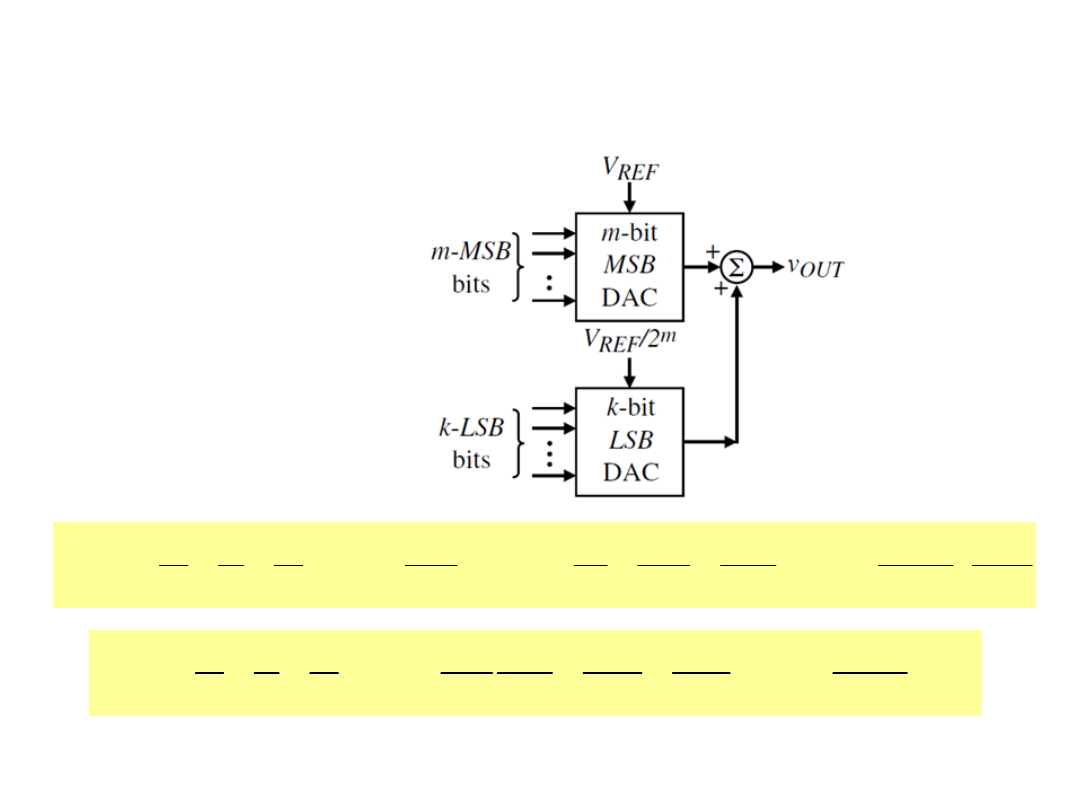

Równoległe przetworniki C-A z rozszerzoną

rozdzielczością

Reference Scaling -

Subranging

Approach

Example of

combining a m-bit

and k-bit subDAC

to form a (m+k)

-bit DAC.

1

0

2

b

REF

V

m

REF

k

k

m

m

m

m

REF

m

m

OUT

V

b

b

b

b

V

b

b

b

b

v

2

2

......

8

4

2

2

......

8

4

2

1

2

1

1

2

1

0

REF

k

m

k

m

m

m

m

m

m

m

m

m

OUT

V

b

b

b

b

b

b

b

b

v

2

......

2

2

2

2

......

8

4

2

1

3

2

2

1

1

1

2

1

0

Accuracy considerations of this method are similar to the analog scaling

approach.

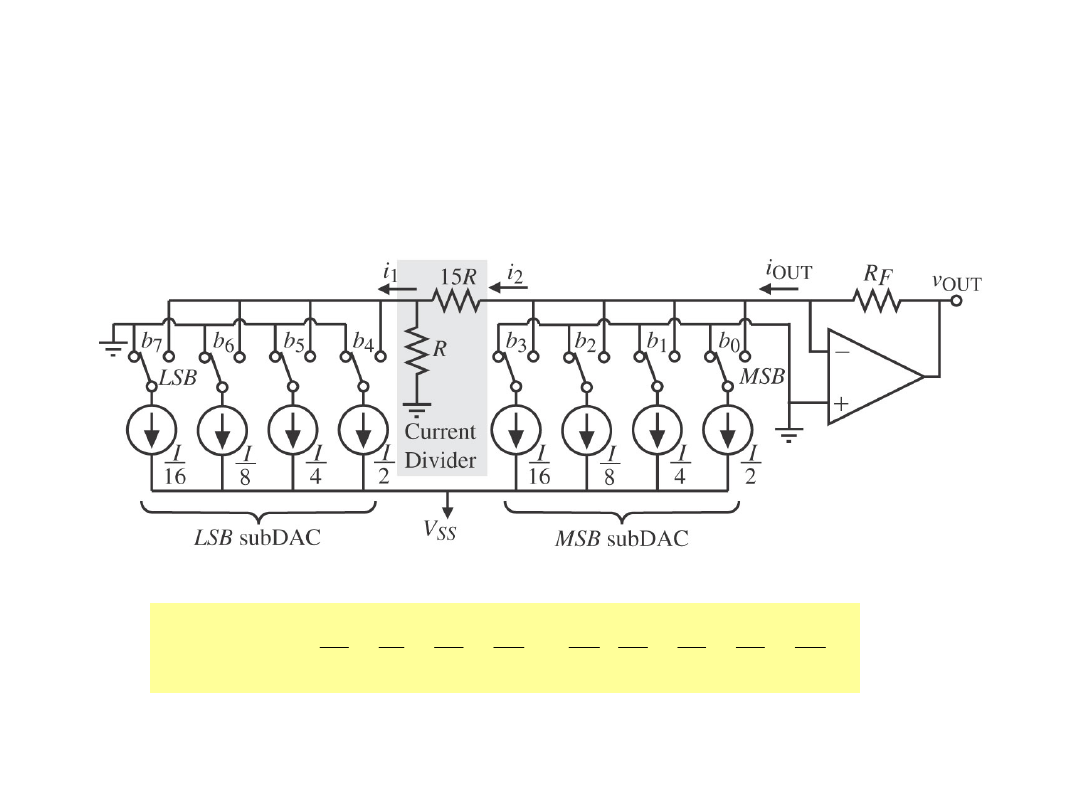

Przetwornik C-A z rozszerzoną rozdzielczością,

wykorzystujący dwa przetworniki C-A skalowane

prądowo

(Current Scaling Dac Using Two SubDACs)

16

8

4

2

16

1

16

8

4

2

7

6

5

4

3

2

1

0

b

b

b

b

b

b

b

b

I

R

v

F

OUT

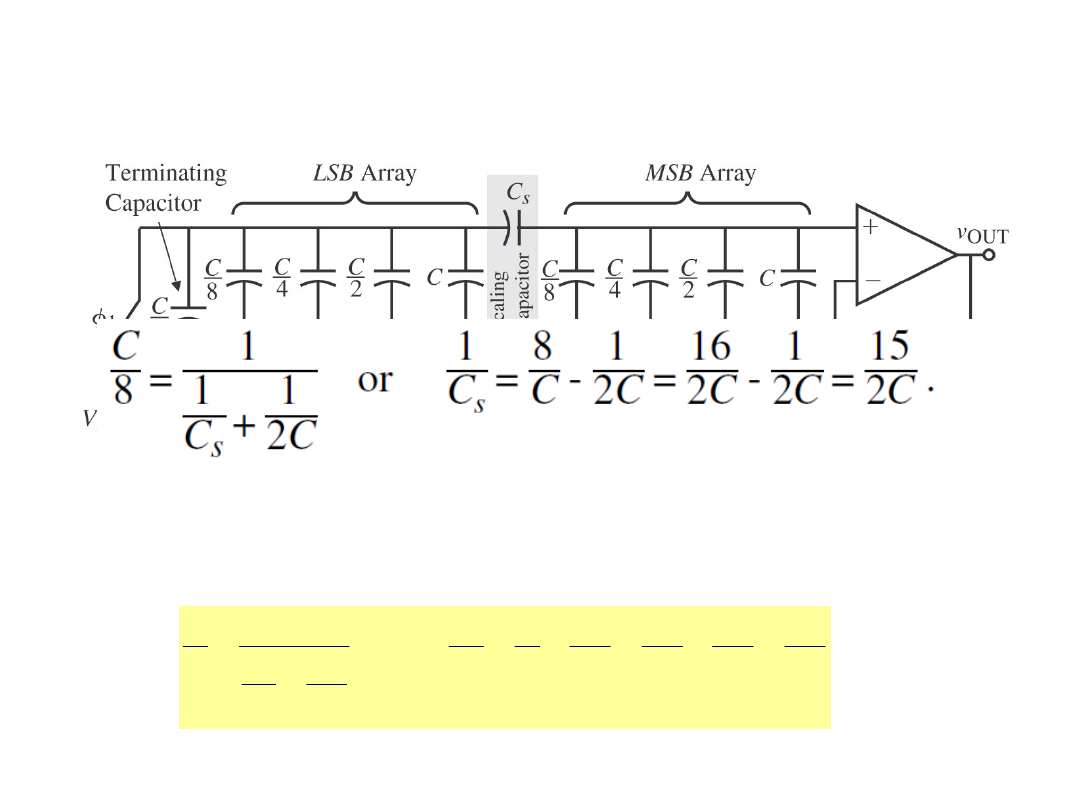

Przetwornik C-A z rozszerzoną rozdzielczością,

wykorzystujący dwa przetworniki C-A ze skalowanym

ładunkiem

(Charge Scaling DAC Using Two SubDACs)

C

C

C

C

C

C

C

C

C

s

s

2

15

2

1

2

16

2

1

8

1

lub

2

1

1

1

8

Projekt pojemności skalującej, C

s

:

Kombinacja szeregowej pojemności C

s

oraz wypadkowej pojemności

matrycy LSB musi zamykać matrycę MSB o pojemności C/8. Dlatego

możemy napisać:

Dziękuję za uwagę!!!

Dziękuję za uwagę!!!

PRZETWORNIKI

C/A

Document Outline

- Slide 1

- Slide 2

- Slide 3

- Slide 4

- Slide 5

- Slide 6

- Slide 7

- Slide 8

- Slide 9

- Slide 10

- Slide 11

- Slide 12

- Slide 13

- Slide 14

- Slide 15

- Slide 16

- Slide 17

- Slide 18

- Slide 19

- Slide 20

- Slide 21

- Slide 22

- Slide 23

- Slide 24

Wyszukiwarka

Podobne podstrony:

W9 Przetwornice DC DC klasy D i DE

Prop aut W9 Ses cyfr Przetworniki fotoelektryczne

Prop aut W9 Ses cyfr Przetworniki fotoelektryczne

Prop aut W9 Ses cyfr Przetworniki fotoelektryczne

przetworniki indukcyjne

w9 aktywna polityka spoleczna

Przetworstwo produktow rolniczych

MLEKO I PRZETWORY MLECZNE (2)

Ceny detaliczne i spożycie warzyw i ich przetworów

W10 Przetw A Cmin

W9 zaocz

SK w9

Kopia W9 Rany krwawiące i postępowanie w krwotoku

przetworniki II opracowane

Przetwarzanie mleka koziego

dupont przetworstwo tworzyw4

Przetwornica buck id 406722 Nieznany

więcej podobnych podstron