1

SEMINARIUM DYPLOMOWE

Pytanie nr 15

„Proces projektowania

cyfrowego układu scalonego

(Design Flow)”

Wykonał: Marcin

Szulc

2

Układ scalony – (ang. intergrated circuit, chip)

(potocznie kość), zminiaturyzowany układ elektroniczny

zawierający w swym wnętrzu od kilku do setek

milionów podstawowych elementów elektronicznych,

takich jak tranzystory, diody, rezystory, kondensatory.

Zwykle jest on zamknięty w hermetycznej obudowie -

szklanej, metalowej, ceramicznej lub wykonanej z

tworzywa sztucznego.

Ze względu na sposób wykonania układy scalone dzieli

się na główne grupy:

monolityczne, w których wszystkie elementy,

elementy czynne wykonane są w monokrystalicznej

strukturze półprzewodnika,

hybrydowe - na płytki wykonane z izolatora

nanoszone są warstwy przewodnika oraz materiału

rezystywnego, które następnie są wytrawiane, tworząc

układ połączeń elektrycznych oraz rezystory. Do tak

utworzonych połączeń dołącza się indywidualne,

miniaturowe elementy elektroniczne (w tym układy

monolityczne).

3

Ze względu na grubość warstw rozróżnia się układy:

cienkowarstwowe (warstwy ok. 2 mikrometrów),

grubowarstwowe (warstwy od 5 do 50 mikrometrów).

Większość stosowanych obecnie układów scalonych jest

wykonana w technologii monolitycznej.

Ze względu na stopień scalenia występuje, w zasadzie

historyczny, podział na układy:

małej skali integracji (SSI – small scale of integration)

poniżej 20 elementów,

średniej skali integracj (MSI – medium scale of integration)

20 – 200 elementów,

dużej skali integracji (LSI – large scale of integration) 200 –

2000 ,

wielkiej skali integracji (VLSI – very large scale of

integration) 2000 – 20000 elementów,

ultrawielkiej skali integracji (ULSI – ultra large scale of

integration) powyżej 20000 elementów.

Ponieważ w układach monolitycznych praktycznie wszystkie elementy

wykonuje się jako tranzystory, odpowiednio tylko przyłączając ich

końcówki, dlatego też często mówi się o gęstości upakowania

tranzystorów na mm

2

.

4

Układ cyfrowy – układ elektroniczny, który realizuje

operacje na wartościach, którym przypisano wartości

liczbowe – w najprostszym przypadku logiczne, którym

odpowiadają wartości 1 lub 0 (Algebra Boole'a). Układy

cyfrowe dzielą się na dwie główne grupy:

układy kombinacyjne,

układy sekwencyjne.

Układ kombinacyjny – charakteryzuje się tym, że stan

wyjść zależy wyłącznie od stanu wejść; stan wyjść opisują

funkcje boolowskie.

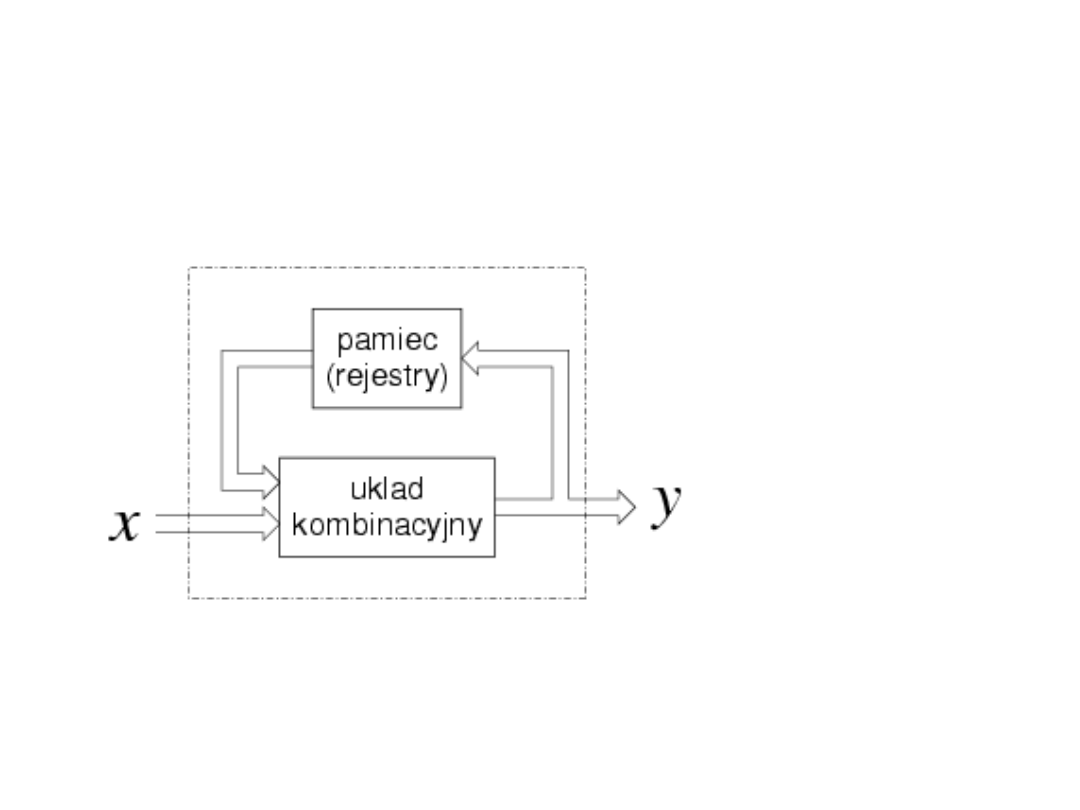

Układ sekwencyjny – charakteryzuje się tym, że stan

wyjść zależy od stanu wejść x oraz od poprzedniego stanu,

zwanym stanem wewnętrznym, pamiętanego w zespole

rejestrów (pamięci).

5

Wśród układów sekwencyjnych zaś wyróżnia się układy

asynchroniczne i synchroniczne.

Przy czym najczęściej układy cyfrowe są synchroniczne,

co oznacza, że zmiany stanów są wyzwalane przez jeden

lub więcej sygnałów zegarowych.

Rys. 1. Schemat budowy układu sekwencyjnego

6

W najczęściej stosowanych układach cyfrowych

określa się dwa stany układu 0 i 1, ze względu na

to, że sygnał z układu może mieć różne wartości

spowodowane

sygnałami

wejściowymi

i

zakłóceniami przyjmuje się zakresy uznawania

sygnału za zero i jedynkę, czasami określa się też

tzw. stan zabroniony, lub nieokreślony.

Często stosuje się też pojęcia stan wysoki H

(high) oraz stan niski L (low).

Zazwyczaj stan wysoki odpowiada wartości 1, a

niski wartości 0, ale spotyka się też realizacje

odwrotne, gdzie brak sygnału lub jego niska

wartość oznacza wartość 1, a wysoka 0.

Układy 0, 1 są najczęściej stosowane w technice,

dlatego często technika cyfrowa jest utożsamiana

z wartościami 0 i 1 oraz z dwójkowym systemem

liczenia, co nie jest do końca prawdą.

7

Przy projektowaniu układów cyfrowych używa się

powszechnie języków opisu sprzętu HDL (Hardware

Description Language). Istnieją dwa zasadnicze sposoby opisu

układów:

behawioralny – projektant definiuje zależności pomiędzy

wyjściami a wejściami układu, natomiast realizacją układu

zajmuje się kompilator;

funkcjonalny – projektant definiuje bloki funkcjonalne

oraz zależności między nimi; przy czym bloki funkcjonalne

mogą być bardzo proste (realizujące np. funkcje

podstawowych bramek logicznych), jak również bardzo

skomplikowane (np. pamięci, rejestry, sumatory itp.).

Środowiska do przetwarzania jęzków HDL mają szerokie

możliwości. Oprócz syntezy układów, umożliwiają różnorakie

optymalizacje (np. minimalizacja funkcji, upraszczanie

obwodów przez użycie „prefabrykantów”), testowanie

zaprojektowanych układów oraz ich funkcjonalną symulację.

Najpopularniejszymi używanymi językami HDL są:

VHDL,

Verilog,

Inne.

8

Pierwsze układy scalone były projektowane ręcznie (za

pomocą ołówka i kartki papieru). Wymagało to od

producenta zatrudnienia na długi okres czasu nie tylko

wielu doświadczonych inżynierów, ale i kreślarzy. W miarę

wzrostu złożoności układów, wydłużał się czas potrzebny

na zrealizowanie projektu, jak również rosły koszty

przygotowania układu do produkcji. W celu dotrzymania

kroku szybko zachodzącym zmianom, urządzenia muszą

być projektowane wyjątkowo szybko, co wymaga

automatyzacji projektowania. Projekty cyfrowe stały się w

dużej mierze uzależnione od stosowanych narzędzi

komputerowego wspomagania projektowania przy pomocy

narzędzi CAD (Computer-Aided Design), znanych jako

systemy automatycznego projektowania DA (Design

automation) lub systemy automatycznego projektowania

układów

elektronicznych

EDA

(Electronic

Design

Automation). Zastosowanie tych narzędzi pozwala na

realizację dwóch zadań:

syntezę – pozwala na translację specyfikacji (opisu) na

implementację projektu,

symulację – pozwala na analizę specyfikację lub

szczegóły implementacji w celu sprawdzenia poprawności

ich działania.

9

Ręczne projektowanie typowego układu VLSI

trwałoby kilka lat i pochłaniałoby ogromne sumy

pieniędzy. Zastosowanie systemów CAD pozwala

znacznie skrócić czas projektowania układów

scalonych i ma ogromne znaczenie ekonomiczne.

Celem zastosowania programów CAD są:

szybkie projektowanie,

wykrywanie błędów w projekcie,

umożliwienie szybkiego wprowadzania zmian,

weryfikacja,

testowanie,

symulacja projektu.

10

Proces projektowania cyfrowego układu scalonego

(Design Flow)

W celu projektowania systemów cyfrowych wykorzystujących bramki

logiczne opracowano formalne metody projektowania:

1. Przygotowanie specyfikacji.

2. W razie konieczności dokonanie podziału systemu na mniejsze części

i przygotowanie specyfikacji dla każdej części.

3. Na podstawie specyfikacji stworzenie grafu automatu stanów, na

którym zaprezentowano wszystkie możliwe stany systemu, kombinacje

sygnałów wejściowych (warunki) określające zmiany stanów oraz

wyjścia dla każdego stanu.

4. Minimalizacja liczby stanów (jest to krok opcjonalny i nie jest

konieczny we wszystkich przypadkach).

5. Wyznaczenie zmiennych boolowskich reprezentujących wszystkie

stany RTL (Register Transfer Level).

6. Wyprowadzenie stanów następnych oraz wyjść.

7. Optymalizacja stanów następnych i wyjść w celu minimalizacji liczby

wymaganych bramek.

8. Wybór odpowiedniego rozmieszenia bramek w konkretnym układzie

scalonym oraz układów scalonych na płytce drukowanej.

9. Wykonanie połączeń pomiędzy układami scalonymi.

11

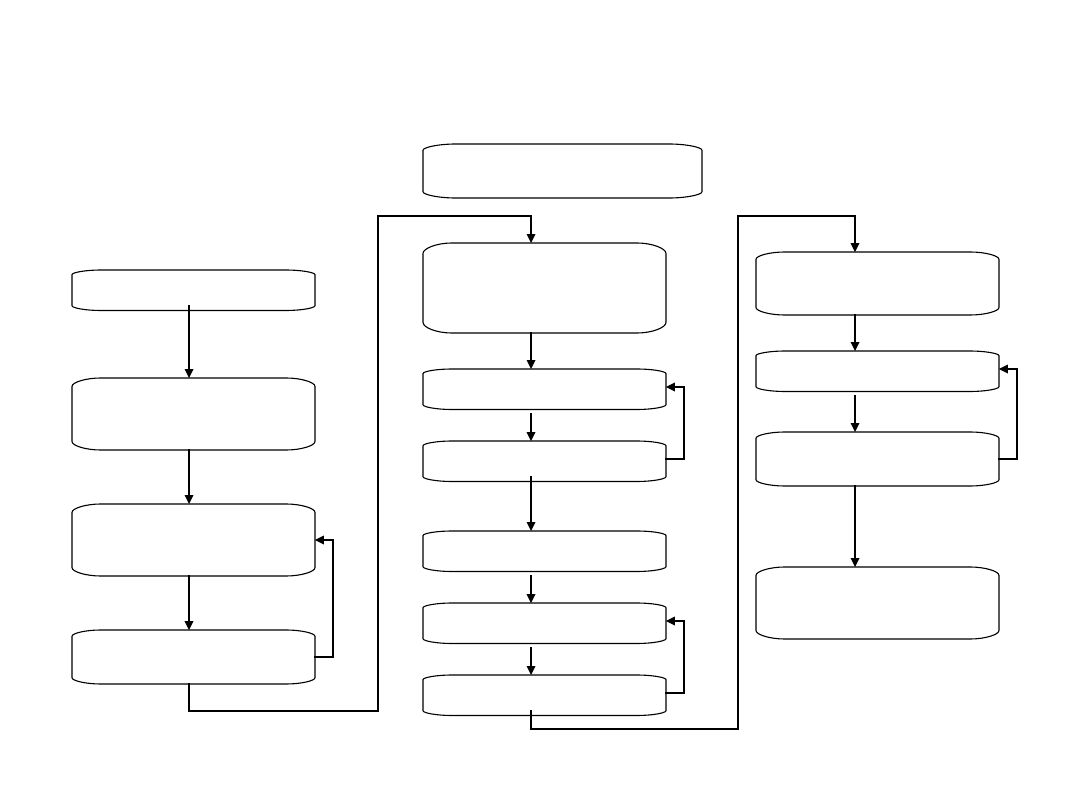

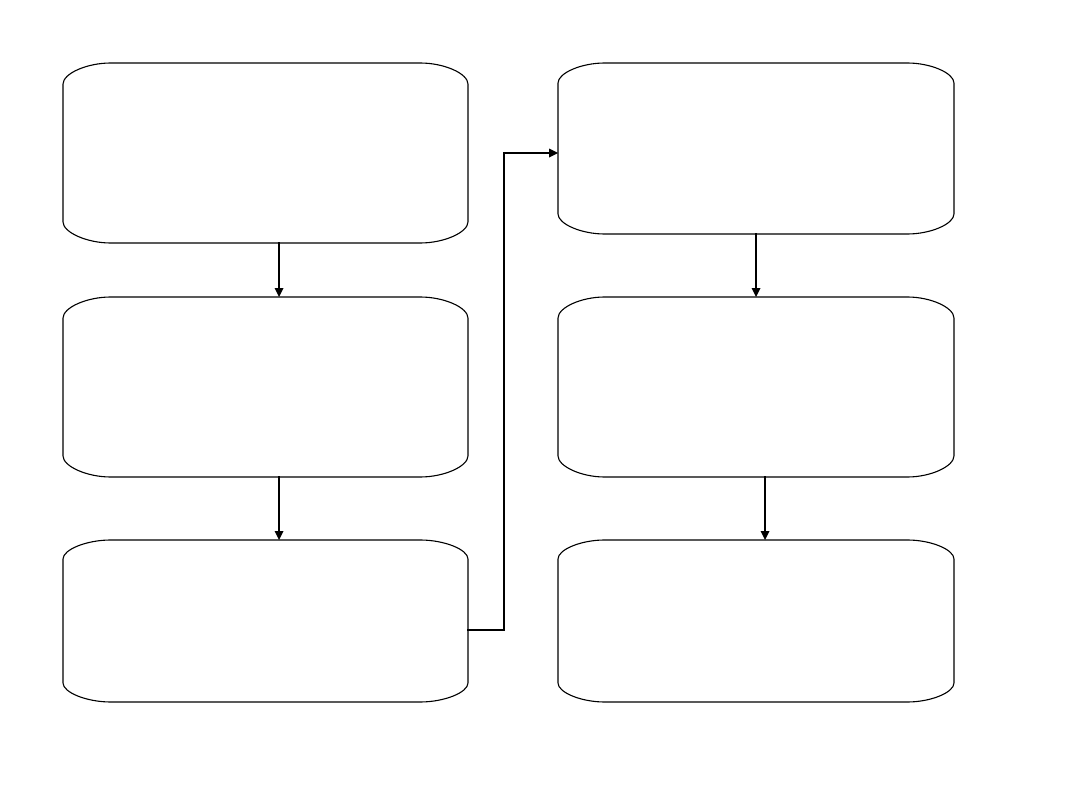

Proces projektowania na każdym poszczególnym poziomie ma

charakter ewolucyjny. Rozpoczyna się od ustalenia określonych

wymagań. Następnie projekt jest rozwijany i testowany na

zgodność z wymaganiami. Jeśli okaże się być z nimi niezgodny,

wówczas musi być ulepszony.

Design Flow

Projekt architektury

funkcjonalnej

Specyfikacja

systemu

Weryfikacja

architektury

Projekt logiki układu

Weryfikacja logiki

układu

Projekt obwodu

Weryfikacja obwodu

Projekt fizyczny

układu

Weryfikacja

rozmieszczenia

elementów

Odwzorowanie

sposobu

zachowania

układu

Stworzenie

logiki układu

(poziom bramek

logicznych)

Tworzenie

obwodu

Rozmieszczanie

elementów

Wytworzenie

oraz testowanie

Rys. 2. Schemat ogólny procesu projektowania cyfrowego układu scalonego

12

Hierarchia projektowania

Hierarchia projektowania jest techniką wymagającą

podzielenia poszczególnych modułów na mniejsze części

(sub-moduły). Proces dzielenia trwa do momentu, w

którym poziom skomplikowania mniejszych elementów

pozwala na łatwe ich opracowanie. Zaprezentowane

wcześniej trzy główne domeny projektowania układów

mogą posiadać hierarchiczną strukturę wyodrębnioną,

dla każdej z nich z osobna. Jednakże warunkiem

koniecznym jest takie uproszczenie projektu tak, aby

hierarchia w różnych domenach odnajdywała w prosty

sposób

swoje

odzwierciedlenie

we

wszystkich

pozostałych.

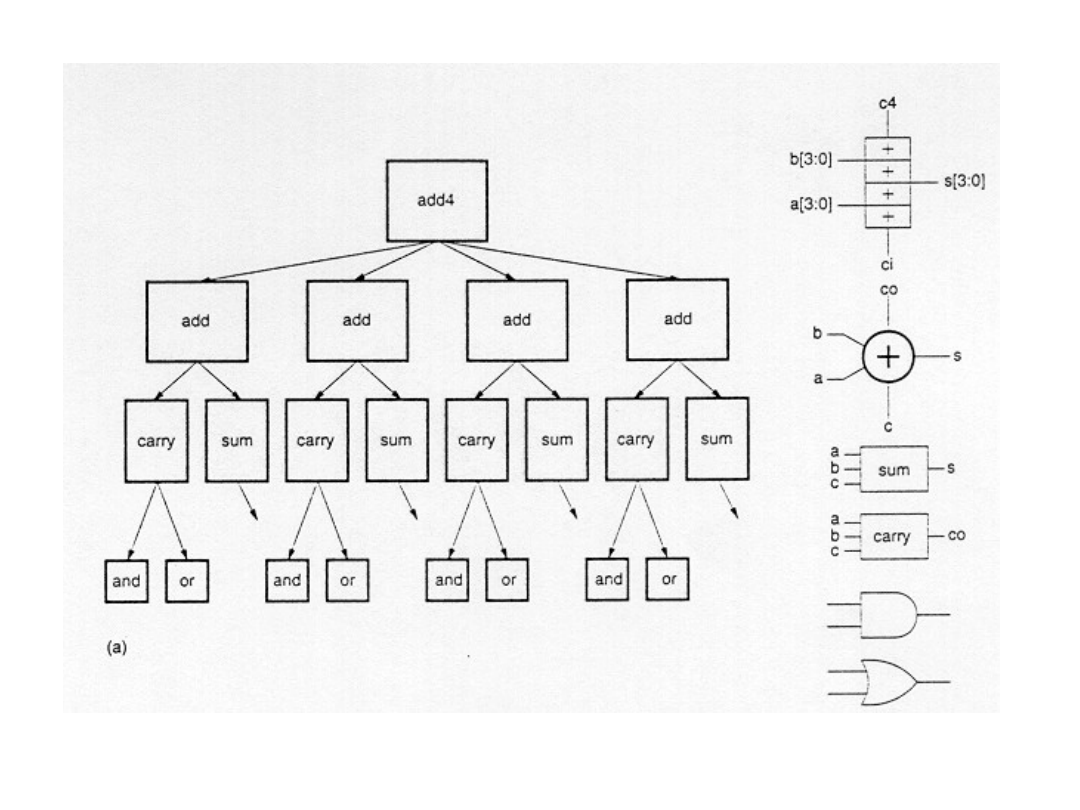

Jako przykład hierarchicznego podziału struktury może

posłużyć 4-bitowy sumator CMOS podzielony na

poszczególne komponenty. Pierwszym krokiem jest

podzielenie go na jedno-bitowy sumatory, które są

następnie dzielone na bity przeniesienia oraz sumy.

Ostatnim krokiem jest podzielenie ich na indywidualne

bramki

logiczne.

Na

tym

poziomie

hierarchii

zaprojektowanie

prostych

obwodów

realizujących

założenia funkcji Boolowskich jest znacznie prostsze niż

w przypadku wyższych poziomów hierarchii.

13

Rys.3. Hierarchiczny podział struktury 4-bitowego sumatora CMOS podzielonego na poszczególne komponenty

14

Regularność

Regularność

oznacza

uproszczenie

systemu

poprzez

stosowanie, w miarę możliwości, identycznych bloków.

Regularność może występować na wszystkich poziomach

projektowania. Dzięki niej możliwe jest zredukowanie liczby

różnych zastosowanych modułów, które muszą zostać

zaprojektowane oraz sprawdzone.

Modułowość

Modułowość w procesie projektowania oznacza, że wszystkie

bloki funkcjonalne tworzące większy system muszą mieć

ściśle zdefiniowane funkcje oraz granice. Zastosowanie tej

reguły pozwala na w miarę niezależne projektowanie modułu

od projektów innych modułów, dzięki temu, że nie ma

dwuznaczności pomiędzy zastosowaniami oraz granicami

dwóch bloków. Dzięki temu wszystkie bloki mogą zostać

połączone w jedną całość na koniec procesu w celu

stworzenia większego systemu. Dzięki modułowości możliwe

są równoległe prace nad poszczególnymi elementami

systemu. Dodatkową zaletą jest możliwość zastosowania

poszczególnych

modułów

w

innych

projektach

(projektowanie plug-and-play).

15

Zlokalizowanie

Określenie granic poszczególnych modułów systemu sprawia,

że “wnętrze” każdego modułu przestaje być istotne dla

innych modułów. Reguła zlokalizowania zapewnia, że

połączenia występują w większości pomiędzy sąsiadującymi

ze sobą modułami przy jednoczesnym unikaniu połączeń

długo-dystansowych. Jest to bardzo istotne w celu unikania

nadmiernych opóźnień. Operacje, które są szczególnie

narażone na opóźnienia powinny być przeprowadzane

lokalnie, bez konieczności dostępu do odległych modułów lub

sygnałów.

16

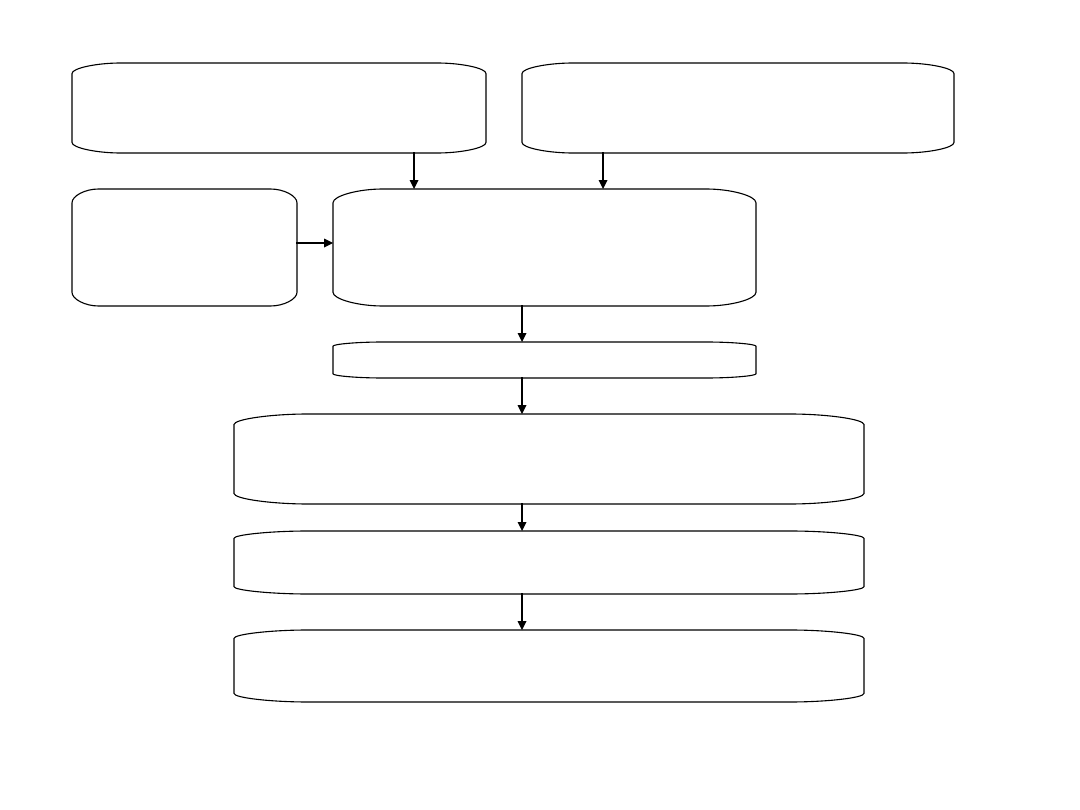

Na poniższym wykresie zaprezentowano główne kroki typowych

przebiegów procesu projektowania cyfrowego układu scalonego

(Design Flow). Wyróżniamy dwie główne metody:

metoda Top-Down,

metoda Bottom-Up.

Podział na mniejsze

bloki funkcjonalne

(opcjonalnie)

Główna idea

systemu

Weryfikacja poziomów

systemu

Metoda Bottom-Up

(Full Custom)

Metoda Top-Down

(Standard Cell)

VLSI Design

Flow

17

Metoda projektowania Bottom-Up (Full

Custom)

Metoda

projektowania

Bottom-Up

bazuje

(głównie)

na

ręcznej

konstrukcji

bloków

obwodów na poziomie tranzystorów oraz

topologii maski. Są one następnie łączone razem

w celu sformowania kompletnej hierarchii

projektu. Dzięki elastyczności na niższych

poziomach

projektowania,

takich

jak

optymalizacja rozmiarów tranzystorów oraz

minimalizacji elementów biernych, metoda

Bottom-Up

jest

bardzo

użyteczna

w

projektowaniu modułów cyfrowych o bardzo

wysokiej gęstości oraz osiągach, jak również

zintegrowanych obwodach analogowych oraz

mieszanych.

18

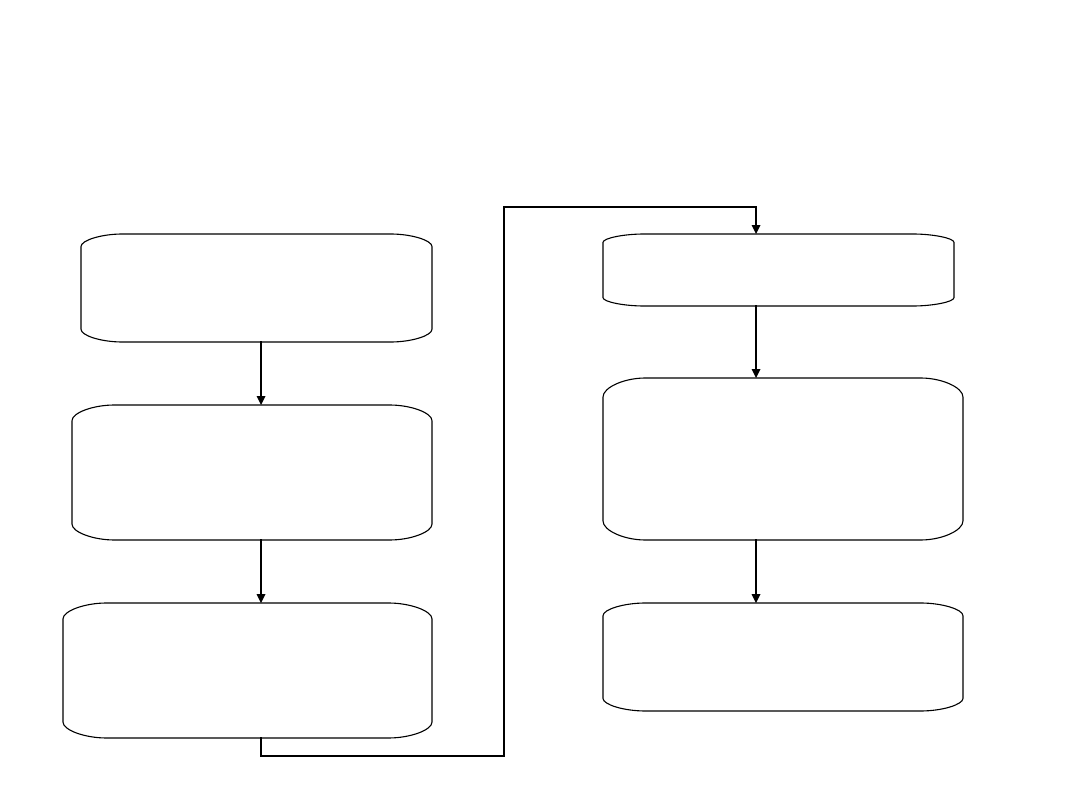

Symulacja

Końcowa symulacja bloków

obwodu przeprowadzona

przy pomocy SPICE

Sprawdzenie zgodności

maski rozmieszczenia

elementów ze schematem

obwodu

Ekstrakcja (maskowanie)

Rzeczywiste wymiary

urządzenia oraz parametry

pasożytnicze są zależne od

rozplanowania maski

Rozmieszczenie

elementów

Rozmieszczenie

poszczególnych bloków

obwodów wykonane w

edytorze rozmieszczenia

Symulacja połączeń

tranzystorów

Symulacja bloków obwodu w

celu sprawdzenia ich

funkcjonalności np. przy

pomocy programu SPICE lub

innego

Schematy poszczególnych

bloków funkcjonalnych

Schemat połączeń

tranzystorów obwodu

wykonane przy pomocy

edytora schematów

Rys.5. Schemat przebiegu procesu projektowania metodą Bottom-Up (Full Custom)

19

Metoda projektowania Top-Down (Standard

Cell)

Metoda projektowania Top-Down odgrywa

podstawową

rolę

przy

automatycznej,

wspomaganej komputerowo syntezie bramek

przy użyciu języków programowania HDL.

Syntetyzowana

logika

jest

następnie

przekształcana

na

standardowe

komórki

biblioteki lub na FPGA. Metoda Top-Down

stosowana jest tylko do projektów cyfrowych

posiadających

stosunkowo

krótkie

cykle

produkcyjne oraz umiarkowane wymagania

względem efektywności układu.

20

Biblioteki

Zawierają

dostępne

elementy oraz

funkcje

Synteza logiczna oraz

odwzorowanie bibliotek

Stworzenie opisu poziomu bramek

przy użyciu biblioteki komórek

Kod struktury (HDL)

Szczegółowy kod opisujący

strukturę poziomu bramek

Kod RTL (HDL)

Wyznaczenie zmiennych

boolowskich reprezentujących

wszystkie stany

Symulacja końcowa

Zasymulowanie końcowego układu logicznego w

celu zweryfikowania rzeczywistych opóźnień oraz

możliwości układu

Rozmieszczenie elementów oraz ścieżek

Stworzenie struktury obwodu przy użyciu

odpowiednich narzędzi

Symulacja cyfrowa

Weryfikacja logicznej funkcjonalności obwodu

Poziom opisu sieci bramek

Rys.6. Schemat przebiegu procesu projektowania metodą Top-Down (Standard Cell)

21

Etap produkcji od projektu rozmieszczenia elementów oraz

ścieżek do wyprodukowania gotowego chipu

Etap ten zazwyczaj wymaga wielu modyfikacji projektu

rozmieszczenia w celu spełnienia wymagań projektowych,

wyprodukowania prototypu oraz wielokrotnego testowania w celu

skorygowania ewentualnych wad projektu.

Wytwarzanie

Masowa produkcja

zaprojektowanego

układu

Testowanie

Weryfikacja osiągów

układu oraz

zidentyfikowanie

możliwości

wprowadzenia

ewentualnych poprawek

Prototyp

Wyprodukowanie próbek

układu

Stworzenie pliku w

formacie

umożliwiającym opis

kolejnych etapów

produkcji układu dla

wytwórcy (Tape-out)

Weryfikacja

rozmieszczenia

Symulacje mające na

celu zbadanie

funkcjonalności i osiągów

całego układu

Rozmieszczenie

elementów oraz

ścieżek całego układu

(Top Level)

Document Outline

- Slide 1

- Slide 2

- Slide 3

- Slide 4

- Slide 5

- Slide 6

- Slide 7

- Slide 8

- Slide 9

- Slide 10

- Slide 11

- Slide 12

- Slide 13

- Slide 14

- Slide 15

- Slide 16

- Slide 17

- Slide 18

- Slide 19

- Slide 20

- Slide 21

Wyszukiwarka

Podobne podstrony:

15 Proces projektowania cyfrowego układu scalonego

Wykorzystanie modelu procesow w projektowaniu systemow informatycznych

1 PROCES PROJEKTOWO KONSTRUKCYJNY

Projektowanie analogowych układów scalonych

15 PROCESY NAUCZANIA

Projekt rzeczywistego układu hydraulicznego

EKONOMIKA BUDOWNICTWA, PROCES PROJEKTOWY, Budownictwo stalowe obejmuje zasadniczo budowle i konstruk

Cyfrowe Układy Scalone Serii MCY74 N

14 Proces projektowo konstrukcyjny

Model procesu projektowania, Uczelnia, PKM

15 sygnał analogowy i cyfrowy

1 Proces projektowaniaid 9643 Nieznany

Projekt rzeczywistego ukladu hydraulicznego

8 procesów w projektach zarządzanych według PRINCE2, Chrzest966, MAP

Od lampy do układu scalonego 2009

wykład2 (cz1) Proces projektowania

więcej podobnych podstron