Rozdział 3.

Mikroprocesor i jednostka centralna

Jednostka centralna jest podstawową częścią każdego mikrokomputera. Zawiera ona mikroprocesor oraz najczęściej pewne układy wspomagające, jak np.:

bufory magistral,

układ generowania sygnałów zegarowych,

układ zerowania,

układ pracy krokowej.

Dodatkowo jednostka centralna może być wyposażona także w inne układy, charakterystyczne dla użytego typu mikroprocesora.

Jednostka centralna Z-80

Z-80 należy do grupy mikroprocesorów 8-bitowych. Został on skonstruowany w roku 1976 przez firmę Zilog, zawiera około 8 [Author ID1: at Fri Dec 14 16:20:00 2001 ]500 tranzystorów i wykonuje 158 rozkazów. Z-80 można traktować jako rozwinięcie mikroprocesora Intel 8080, niemal w pełni z nim zgodne na poziomie kodu wynikowego.

Mikroprocesor charakteryzuje się m. [Author ID1: at Fri Dec 14 16:21:00 2001

]in. rozdzieloną przestrzenią adresową pamięci i wejścia-wyjścia. Adres pamięci jest zawsze 16-bitowy, natomiast wejścia-wyjścia 8- lub 16-bitowy zależnie od sposobu adresowania.

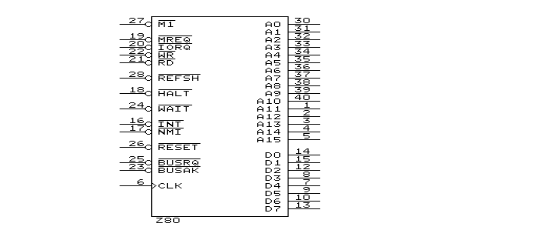

Opis wyprowadzeń Z-80

Wśród wyprowadzeń mikroprocesora Z-80 można wyróżnić 16-bitową magistralę adresową A, 8-bitową magistralę danych D oraz liczne sygnały sterujące (rysunek 3.1[Author ID1: at Fri Dec 14 16:23:00 2001

][Author ID1: at Fri Dec 14 16:23:00 2001

][Author ID1: at Fri Dec 14 16:23:00 2001

][Author ID1: at Fri Dec 14 16:23:00 2001

][Author ID1: at Fri Dec 14 16:23:00 2001

]Rysunek [Author ID1: at Fri Dec 14 16:23:00 2001

]1[Author ID1: at Fri Dec 14 16:23:00 2001

][Author ID1: at Fri Dec 14 16:23:00 2001

]). Stan aktywny wszystkich sygnałów sterujących to „0”, a ich[Author ID1: at Sat Dec 15 23:18:00 2001

] znaczenie tych sygnałów [Author ID1: at Sat Dec 15 23:18:00 2001

]jest następujące:

—[Author ID1: at Fri Dec 14 16:24:00 2001 ]-[Author ID1: at Fri Dec 14 16:24:00 2001 ] wyjście informujące, że mikroprocesor realizuje cykl pobrania kodu rozkazu;[Author ID1: at Fri Dec 14 16:26:00 2001 ],[Author ID1: at Fri Dec 14 16:26:00 2001 ]

—[Author ID1: at Fri Dec 14 16:24:00 2001 ]-[Author ID1: at Fri Dec 14 16:24:00 2001 ] wyjście żądania dostępu do przestrzeni adresowej pamięci;[Author ID1: at Fri Dec 14 16:27:00 2001 ],[Author ID1: at Fri Dec 14 16:26:00 2001 ]

—[Author ID1: at Fri Dec 14 16:24:00 2001 ]-[Author ID1: at Fri Dec 14 16:24:00 2001 ] wyjście żądania dostępu do przestrzeni adresowej wejścia-wyjścia;[Author ID1: at Fri Dec 14 16:27:00 2001 ],[Author ID1: at Fri Dec 14 16:27:00 2001 ]

—[Author ID1: at Fri Dec 14 16:25:00 2001 ]-[Author ID1: at Fri Dec 14 16:25:00 2001 ] wejście żądania przejęcia magistrali, np. przez sterownik bezpośredniego dostępu do pamięci;[Author ID1: at Fri Dec 14 16:27:00 2001 ],[Author ID1: at Fri Dec 14 16:27:00 2001 ]

—[Author ID1: at Fri Dec 14 16:25:00 2001 ]-[Author ID1: at Fri Dec 14 16:25:00 2001 ] wyjście potwierdzenia zwolnienia magistrali przez procesor wskutek wystąpienia sygnału

;[Author ID1: at Fri Dec 14 16:27:00 2001 ],[Author ID1: at Fri Dec 14 16:27:00 2001 ]

—[Author ID1: at Fri Dec 14 16:25:00 2001 ]-[Author ID1: at Fri Dec 14 16:25:00 2001 ] wejście żądania wydłużenia cyklu maszynowego, używane m.,[Author ID1: at Fri Dec 14 16:28:00 2001 ]

—[Author ID1: at Fri Dec 14 16:25:00 2001 ]-[Author ID1: at Fri Dec 14 16:25:00 2001 ] wyjście informujące o tym, że mikroprocesor znajduje się w stanie zatrzymania (wykonuje rozkaz HLT);[Author ID1: at Fri Dec 14 16:28:00 2001 ],[Author ID1: at Fri Dec 14 16:28:00 2001 ]

—[Author ID1: at Fri Dec 14 16:26:00 2001 ]-[Author ID1: at Fri Dec 14 16:26:00 2001 ] wyjście informujące, że na liniach A7 - [Author ID1: at Fri Dec 14 16:28:00 2001 ]-[Author ID1: at Fri Dec 14 16:28:00 2001 ]A0 znajduje się adres odświeżanego wiersza pamięci dynamicznej;[Author ID1: at Fri Dec 14 16:28:00 2001 ],[Author ID1: at Fri Dec 14 16:28:00 2001 ]CLK —[Author ID1: at Fri Dec 14 16:25:00 2001 ]

-[Author ID1: at Fri Dec 14 16:25:00 2001 ] wejście zegarowe.

Rysunek 3.1. [Author ID1: at Fri Dec 14 16:29:00 2001

][Author ID1: at Fri Dec 14 16:29:00 2001

][Author ID1: at Fri Dec 14 16:29:00 2001

][Author ID1: at Fri Dec 14 16:29:00 2001

]1[Author ID1: at Fri Dec 14 16:29:00 2001

][Author ID1: at Fri Dec 14 16:29:00 2001

]. [Author ID1: at Fri Dec 14 16:29:00 2001

]Wyprowadzenia mikroprocesora Z-80

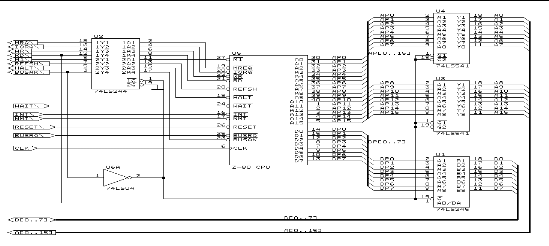

Buforowanie wyprowadzeń

Z-80 charakteryzuje się niską obciążalnością wyprowadzeń —[Author ID1: at Fri Dec 14 16:30:00 2001

]-[Author ID1: at Fri Dec 14 16:30:00 2001

] do każdego wyjścia można podłączyć tylko jedno wejście TTL. Z tego powodu w większości zastosowań konieczne jest „otoczenie” mikroprocesora buforami. Rozpatrywany przykład (rysunek 3.2[Author ID1: at Fri Dec 14 16:30:00 2001

][Author ID1: at Fri Dec 14 16:30:00 2001

][Author ID1: at Fri Dec 14 16:30:00 2001

][Author ID1: at Fri Dec 14 16:30:00 2001

][Author ID1: at Fri Dec 14 16:30:00 2001

]Rysunek [Author ID1: at Fri Dec 14 16:30:00 2001

]2[Author ID1: at Fri Dec 14 16:30:00 2001

][Author ID1: at Fri Dec 14 16:30:00 2001

]) umożliwia zastosowanie jednostki centralnej w układach wykorzystujących mechanizm bezpośredniego dostępu do pamięci (DMA).

Rysunek 3.2. [Author ID1: at Fri Dec 14 16:32:00 2001

][Author ID1: at Fri Dec 14 16:32:00 2001

][Author ID1: at Fri Dec 14 16:32:00 2001

][Author ID1: at Fri Dec 14 16:32:00 2001

]2[Author ID1: at Fri Dec 14 16:32:00 2001

][Author ID1: at Fri Dec 14 16:32:00 2001

]. [Author ID1: at Fri Dec 14 16:32:00 2001

]Buforowanie wyprowadzeń mikroprocesora Z-80

Magistralę adresową można buforować przez dwa 8-bitowe bufory jednokierunkowe, np. 74244 lub 74541. W praktycznych zastosowaniach lepszy jest układ 74541, ponieważ jego wejścia znajdują się po jednej stronie obudowy, a wyjścia —[Author ID1: at Fri Dec 14 16:33:00 2001

]-[Author ID1: at Fri Dec 14 16:33:00 2001

] po drugiej.

Również sygnały sterujące można wzmocnić za pomocą takich buforów. Część sygnałów powinna być blokowana podczas realizacji cykli DMA, natomiast pozostałe mogą lub powinny być stale aktywne. Do grupy sygnałów blokowanych należą ![]()

,![]()

, ![]()

i ![]()

, ponieważ są one wykorzystywane przez sterownik DMA do adresowania urządzeń, między którymi wymieniane są dane. Pozostałe sygnały, tj. ![]()

, ![]()

i ![]()

nie są potrzebne do realizacji cyklu DMA, natomiast ![]()

informuje sterownik DMA o możliwości przejęcia magistrali i w związku z tym musi zawsze być dostępny na zewnątrz mikroprocesora. Z tych rozważań wynika, że najodpowiedniejszym układem buforującym będzie 74244.

Bufor magistrali danych musi umożliwiać przesył danych w obie strony, zatem odpowiednim[Author ID1: at Fri Dec 14 16:34:00 2001

] układem jest tu 74245. Przyjmijmy, że od strony procesora znajdzie się strona „A” bufora. Podczas odczytu dane będą więc przesyłane w kierunku B [Author ID1: at Fri Dec 14 16:34:00 2001

]→ [Author ID1: at Fri Dec 14 16:34:00 2001

]A, zatem wejście określające kierunek przesyłu powinno przyjąć wtedy stan niski. Warunek ten można spełnić przez dołączenie tego wejścia do sygnału ![]()

.

Podczas realizacji cyklu DMA wyjścia buforów powinny przejść w stan wysokiej impedancji, a więc ich wejścia bramkujące powinny być w stanie logicznym „1”. Ponieważ przez cały czas trwania cyklu DMA aktywny jest sygnał ![]()

(ma wówczas wartość „0”), może on posłużyć do blokowania buforów, konieczna jest jednak zmiana jego stanu logicznego na przeciwny.

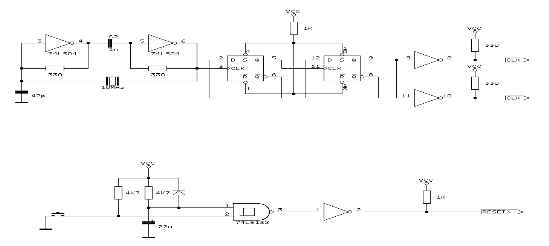

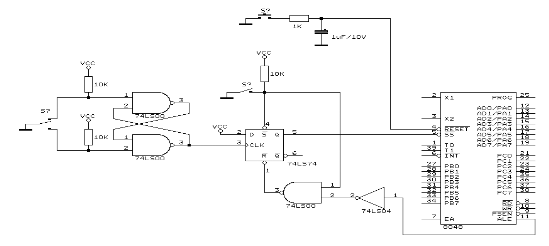

Generator sygnału zegarowego i układ zerowania

Mikroprocesor Z-80 wymaga sygnału zegarowego, którego maksymalna częstotliwość wynosi od 2,5 do 8 MHz. Przykładowy układ (rysunek 3.3[Author ID1: at Fri Dec 14 16:36:00 2001

][Author ID1: at Fri Dec 14 16:36:00 2001

][Author ID1: at Fri Dec 14 16:36:00 2001

][Author ID1: at Fri Dec 14 16:36:00 2001

][Author ID1: at Fri Dec 14 16:36:00 2001

]Rysunek [Author ID1: at Fri Dec 14 16:36:00 2001

]3[Author ID1: at Fri Dec 14 16:36:00 2001

][Author ID1: at Fri Dec 14 16:36:00 2001

]) wykorzystuje oscylator 10 MHz. Do wygenerowania podstawowego przebiegu wykorzystamy generator oparty na[Author ID1: at Fri Dec 14 19:02:00 2001

]o[Author ID1: at Fri Dec 14 19:02:00 2001

] dwóch[Author ID1: at Fri Dec 14 19:02:00 2001

]ie[Author ID1: at Fri Dec 14 19:02:00 2001

] tzw. bramkach[Author ID1: at Fri Dec 14 19:02:00 2001

]i[Author ID1: at Fri Dec 14 19:02:00 2001

] zlinearyzowanych[Author ID1: at Fri Dec 14 19:02:00 2001

]e[Author ID1: at Fri Dec 14 19:02:00 2001

], w których wejście jest połączone z wyjściem poprzez rezystor 330 Ω. Generator taki zapewnia dużą stabilność częstotliwości. Ponieważ częstotliwość oscylatora wynosi 10 MHz, konieczne jest podzielenie jej przez 4. Podział ten realizowany jest w dwóch przerzutnikach synchronicznych typu D —[Author ID1: at Fri Dec 14 16:37:00 2001

]-[Author ID1: at Fri Dec 14 16:37:00 2001

] uzyskujemy w ten sposób częstotliwość 2,5 MHz. Podział częstotliwości można uzyskać także przez wykorzystanie licznika.

Mikroprocesor Z-80 wymaga, aby sygnał zegarowy na wejściu CLK miał nieco inne poziomy napięć niż standardowy przebieg TTL. Wymaganie to można spełnić przez dołączenie bramki wraz z rezystorem podciągającym o wartości 330 Ω.

Rysunek 3.3. [Author ID1: at Fri Dec 14 16:38:00 2001

][Author ID1: at Fri Dec 14 16:38:00 2001

][Author ID1: at Fri Dec 14 16:38:00 2001

][Author ID1: at Fri Dec 14 16:38:00 2001

]3[Author ID1: at Fri Dec 14 16:38:00 2001

][Author ID1: at Fri Dec 14 16:38:00 2001

]. [Author ID1: at Fri Dec 14 16:38:00 2001

]Generator sygnału zegarowego i zerowania dla mikroprocesora Z-80

Procesor powinien być wyzerowany w dwóch przypadkach:

po włączeniu zasilania,

na s[Author ID1: at Fri Dec 14 16:39:00 2001 ]

ws[Author ID1: at Fri Dec 14 16:39:00 2001 ]kutek interwencji użytkownika (np. po [Author ID1: at Fri Dec 14 16:40:00 2001 ]naciśnięciu[Author ID1: at Fri Dec 14 16:40:00 2001 ]e[Author ID1: at Fri Dec 14 16:40:00 2001 ] przycisku).

Przykładowy układ (rysunek 3.3[Author ID1: at Fri Dec 14 16:43:00 2001

][Author ID1: at Fri Dec 14 16:43:00 2001

][Author ID1: at Fri Dec 14 16:43:00 2001

][Author ID1: at Fri Dec 14 16:43:00 2001

][Author ID1: at Fri Dec 14 16:43:00 2001

]Rysunek [Author ID1: at Fri Dec 14 16:43:00 2001

]3[Author ID1: at Fri Dec 14 16:43:00 2001

][Author ID1: at Fri Dec 14 16:43:00 2001

]) realizuje obie funkcje. Po włączeniu zasilania następuje ładowanie kondensatora Cx poprzez rezystor Rx. Dopóki kondensator nie będzie odpowiednio naładowany, na wejściu bramki będzie znajdował się stan niski, a więc sygnał ![]()

będzie miał wartość logiczną „0”. Po naładowaniu kondensatora sygnał ![]()

przejdzie w stan nieaktywny i zerowanie zakończy się.

Ręczne zerowanie jest możliwe przez wciśnięcie przycisku Kx, w następstwie czego następuje[Author ID1: at Fri Dec 14 16:46:00 2001

]które powoduje[Author ID1: at Fri Dec 14 16:46:00 2001

] podanie „0” logicznego na wejście bramki i w konsekwencji wygenerowanie sygnału ![]()

.

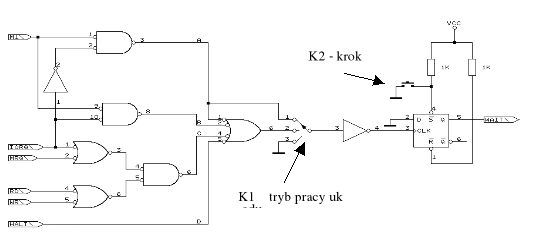

Układ pracy krokowej

W początkowym okresie konstrukcji układu mikroprocesorowego przydatny może być mechanizm pracy krokowej. W przypadku mikroprocesora Z-80 umożliwia on bowiem zatrzymywanie realizacji programu nawet w trakcie każdego cyklu maszynowego. Dzięki takiemu rozwiązaniu można dowolnie długo obserwować stany poszczególnych sygnałów w układzie.

W zaprezentowanym układzie (rysunek 3.4[Author ID1: at Fri Dec 14 16:48:00 2001

][Author ID1: at Fri Dec 14 16:48:00 2001

][Author ID1: at Fri Dec 14 16:48:00 2001

][Author ID1: at Fri Dec 14 16:48:00 2001

][Author ID1: at Fri Dec 14 16:48:00 2001

]Rysunek [Author ID1: at Fri Dec 14 16:48:00 2001

]4[Author ID1: at Fri Dec 14 16:48:00 2001

][Author ID1: at Fri Dec 14 16:48:00 2001

]) przyczyną zatrzymania procesora może być dowolny cykl maszynowy (przełącznik K1 w położeniu 2.[Author ID1: at Fri Dec 14 16:50:00 2001

]) lub tylko cykl pobrania kodu rozkazu. Położenie 3.[Author ID1: at Fri Dec 14 16:50:00 2001

] przełącznika oznacza wyłączenie pracy krokowej.

-->

Rysunek[Author:EK]

[Author ID1: at Fri Dec 14 16:51:00 2001

] 3.4. [Author ID1: at Fri Dec 14 16:49:00 2001

][Author ID1: at Fri Dec 14 16:49:00 2001

][Author ID1: at Fri Dec 14 16:49:00 2001

][Author ID1: at Fri Dec 14 16:49:00 2001

]4[Author ID1: at Fri Dec 14 16:49:00 2001

][Author ID1: at Fri Dec 14 16:49:00 2001

]. [Author ID1: at Fri Dec 14 16:49:00 2001

]Układ pracy krokowej dla mikroprocesora Z-80

Stan „0” sygnału A oznacza, że realizowany jest cykl pobrania kodu rozkazu. Podczas tego cyklu aktywne są sygnały ![]()

i ![]()

mikroprocesora Z-80.

Stan „0” sygnału B oznacza, że realizowany jest cykl przyjęcia przerwania. Podczas tego cyklu aktywne są sygnały ![]()

i ![]()

mikroprocesora Z-80.

Stan „0” sygnału C oznacza, że realizowany jest cykl odczytu lub zapisu pamięci lub układów wejścia-wyjścia. Podczas tego cyklu aktywne są sygnały ![]()

lub ![]()

oraz ![]()

lub ![]()

mikroprocesora Z-80.

Stan „0” sygnału D oznacza, że realizowany jest cykl zatrzymania (HALT), podczas którego aktywny jest sygnał ![]()

mikroprocesora.

Wystąpienie zbocza narastającego na wejściu C przerzutnika powoduje wpisanie do niego „0” logicznego, wygenerowanie sygnału ![]()

i w konsekwencji zatrzymanie realizacji programu. Wykonanie kroku jest możliwe przez naciśnięcie przycisku K2. Ponieważ wejście ![]()

przerzutnika jest asynchroniczne, konieczne jest zastosowanie układu czasowego.

Jednostka centralna 8048

8048 należy do grupy 8-bitowych mikrokomputerów jednoukładowych. Jest to pierwszy układ tego typu, zaprojektowany w roku 1976 w firmie Intel. Jest on w stanie zaadresować do 4 KB pamięci programu (adres 12-bitowy) oraz 256 B wewnętrznej lub zewnętrznej pamięci danych (adres 8-bitowy). Układ ten zawiera:

8-bitową jednostkę centralną,

wewnętrzną pamięć programu o pojemności 1 - [Author ID1: at Fri Dec 14 17:29:00 2001 ]

-[Author ID1: at Fri Dec 14 17:29:00 2001 ]4 KB,wewnętrzną pamięć danych o pojemności 64 B,

trzy uniwersalne porty wejścia-wyjścia,

układ czasowo-licznikowy w postaci[Author ID1: at Fri Dec 14 17:30:00 2001 ]

-[Author ID1: at Fri Dec 14 17:30:00 2001 ] programowalnego[Author ID1: at Fri Dec 14 17:30:00 2001 ]y[Author ID1: at Fri Dec 14 17:30:00 2001 ] licznika[Author ID1: at Fri Dec 14 17:30:00 2001 ] 8-bitowego[Author ID1: at Fri Dec 14 17:30:00 2001 ]y[Author ID1: at Fri Dec 14 17:30:00 2001 ],jednopoziomowy układ przerwań.

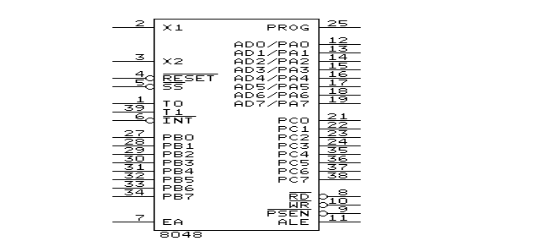

Opis wyprowadzeń 8048

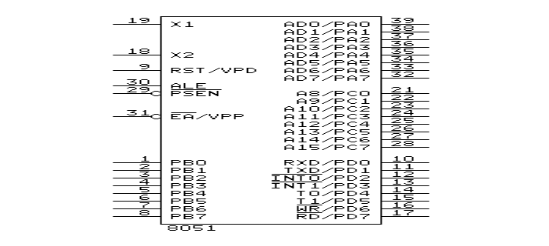

Wśród wyprowadzeń mikrokomputera 8048 (rysunek 3.5[Author ID1: at Fri Dec 14 17:32:00 2001

][Author ID1: at Fri Dec 14 17:32:00 2001

][Author ID1: at Fri Dec 14 17:32:00 2001

][Author ID1: at Fri Dec 14 17:32:00 2001

][Author ID1: at Fri Dec 14 17:32:00 2001

]Rysunek [Author ID1: at Fri Dec 14 17:32:00 2001

]5[Author ID1: at Fri Dec 14 17:32:00 2001

][Author ID1: at Fri Dec 14 17:32:00 2001

]) można wyróżnić porty wejścia-wyjścia oraz sygnały sterujące. Niektóre porty są wykorzystywane do realizacji magistrali adresowej i danych przy współpracy z zewnętrznymi układami pamięci i wejścia-[Author ID1: at Fri Dec 14 17:33:00 2001

] [Author ID1: at Fri Dec 14 17:33:00 2001

]wyjścia. Znaczenie sygnałów jest następujące:

PA —[Author ID1: at Fri Dec 14 17:34:00 2001 ]

-[Author ID1: at Fri Dec 14 17:34:00 2001 ] dwukierunkowy, 8-bitowy port wejścia-wyjścia, który może także pełnić funkcję młodszej części magistrali adresowej (bity A0 - [Author ID1: at Fri Dec 14 17:36:00 2001 ]-[Author ID1: at Fri Dec 14 17:36:00 2001 ]A7) multipleksowanej z magistralą danych;[Author ID1: at Fri Dec 14 17:36:00 2001 ],[Author ID1: at Fri Dec 14 17:36:00 2001 ]PB —[Author ID1: at Fri Dec 14 17:34:00 2001 ]

-[Author ID1: at Fri Dec 14 17:34:00 2001 ] dwukierunkowy, 8-bitowy port wejścia wyjścia;[Author ID1: at Fri Dec 14 17:37:00 2001 ],[Author ID1: at Fri Dec 14 17:37:00 2001 ]PC —[Author ID1: at Fri Dec 14 17:34:00 2001 ]

-[Author ID1: at Fri Dec 14 17:34:00 2001 ] dwukierunkowy, 8-bitowy port wejścia-[Author ID1: at Fri Dec 14 17:38:00 2001 ]-[Author ID1: at Fri Dec 14 17:38:00 2001 ]A12) oraz funkcję [Author ID1: at Fri Dec 14 17:39:00 2001 ]specjalnej magistrali,[Author ID1: at Fri Dec 14 17:40:00 2001 ] służącej do dołączenia ekspandera 8243;[Author ID1: at Fri Dec 14 17:38:00 2001 ],[Author ID1: at Fri Dec 14 17:38:00 2001 ]T0 —[Author ID1: at Fri Dec 14 17:34:00 2001 ]

-[Author ID1: at Fri Dec 14 17:34:00 2001 ] wejście testowane w niektórych rozkazach skoków warunkowych lub wyjście sygnału zegarowego;[Author ID1: at Fri Dec 14 17:40:00 2001 ],[Author ID1: at Fri Dec 14 17:40:00 2001 ]T1 —[Author ID1: at Fri Dec 14 17:34:00 2001 ]

-[Author ID1: at Fri Dec 14 17:34:00 2001 ] wejście testowane w niektórych rozkazach skoków warunkowych lub wejście sygnału zegarowego dla wewnętrznego układu czasowo-licznikowego;[Author ID1: at Fri Dec 14 17:41:00 2001 ],[Author ID1: at Fri Dec 14 17:41:00 2001 ]ALE —[Author ID1: at Fri Dec 14 17:34:00 2001 ]

-[Author ID1: at Fri Dec 14 17:34:00 2001 ] wyjście sygnału zegarowego o częstotliwości fXTAL/15 oraz wyjście strobujące adres przy współpracy z zewnętrznymi układami pamięci i wejścia-wyjścia;[Author ID1: at Fri Dec 14 17:41:00 2001 ],[Author ID1: at Fri Dec 14 17:41:00 2001 ]PROG —[Author ID1: at Fri Dec 14 17:35:00 2001 ]

-[Author ID1: at Fri Dec 14 17:35:00 2001 ] wyjście sterujące do współpracy z ekspanderem 8243;[Author ID1: at Fri Dec 14 17:41:00 2001 ],[Author ID1: at Fri Dec 14 17:41:00 2001 ]

[Author ID1: at Fri Dec 14 17:37:00 2001 ]—[Author ID1: at Fri Dec 14 17:35:00 2001 ]-[Author ID1: at Fri Dec 14 17:35:00 2001 ] wejście przerwania lub wejście [Author ID1: at Fri Dec 14 17:42:00 2001 ]testowane w niektórych rozkazach skoków warunkowych;[Author ID1: at Fri Dec 14 17:42:00 2001 ],[Author ID1: at Fri Dec 14 17:42:00 2001 ]

[Author ID1: at Fri Dec 14 17:37:00 2001 ]—[Author ID1: at Fri Dec 14 17:35:00 2001 ]-[Author ID1: at Fri Dec 14 17:35:00 2001 ] wyjście żądania odczytu z przestrzeni adresowej zewnętrznej pamięci danych;[Author ID1: at Fri Dec 14 17:43:00 2001 ],[Author ID1: at Fri Dec 14 17:43:00 2001 ]

[Author ID1: at Fri Dec 14 17:37:00 2001 ]—[Author ID1: at Fri Dec 14 17:35:00 2001 ]-[Author ID1: at Fri Dec 14 17:35:00 2001 ] wyjście żądania zapisu do przestrzeni adresowej zewnętrznej pamięci danych;[Author ID1: at Fri Dec 14 17:43:00 2001 ],[Author ID1: at Fri Dec 14 17:43:00 2001 ]

[Author ID1: at Fri Dec 14 17:37:00 2001 ]—[Author ID1: at Fri Dec 14 17:35:00 2001 ]-[Author ID1: at Fri Dec 14 17:35:00 2001 ] wyjście żądania odczytu z przestrzeni adresowej zewnętrznej pamięci programu;[Author ID1: at Fri Dec 14 17:43:00 2001 ],[Author ID1: at Fri Dec 14 17:43:00 2001 ]EA —[Author ID1: at Fri Dec 14 17:35:00 2001 ]

-[Author ID1: at Fri Dec 14 17:35:00 2001 ] wejście wymuszające pobieranie kodu rozkazów wyłącznie z zewnętrznej pamięci programu;[Author ID1: at Fri Dec 14 17:43:00 2001 ],[Author ID1: at Fri Dec 14 17:43:00 2001 ]XTAL1, XTAL2 —[Author ID1: at Fri Dec 14 17:35:00 2001 ]

-[Author ID1: at Fri Dec 14 17:35:00 2001 ] wejścia służące do podłączenia oscylatora kwarcowego; XTAL1 może być też[Author ID1: at Fri Dec 14 17:43:00 2001 ]z[Author ID1: at Fri Dec 14 17:43:00 2001 ] wejściem zewnętrznego sygnału taktującego.

Rysunek 3.5. [Author ID1: at Fri Dec 14 17:43:00 2001

][Author ID1: at Fri Dec 14 17:43:00 2001

][Author ID1: at Fri Dec 14 17:43:00 2001

][Author ID1: at Fri Dec 14 17:43:00 2001

]5[Author ID1: at Fri Dec 14 17:43:00 2001

][Author ID1: at Fri Dec 14 17:43:00 2001

]. [Author ID1: at Fri Dec 14 17:43:00 2001

]Wyprowadzenia mikroprocesora 8048

Buforowanie wyprowadzeń

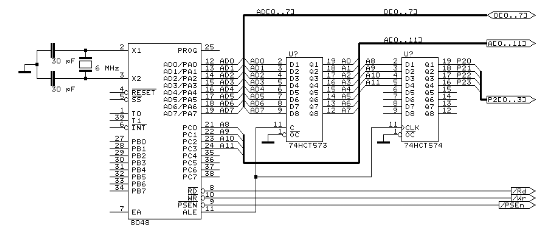

Mikroprocesory rodziny 8048 można rozbudować o [Author ID1: at Fri Dec 14 16:16:00 2001

] [Author ID1: at Fri Dec 14 16:16:00 2001

]zewnętrzne pamięci i [Author ID1: at Fri Dec 14 16:17:00 2001

] [Author ID1: at Fri Dec 14 16:17:00 2001

]układy peryferyjne. W najprostszych przypadkach nie jest konieczne budowanie magistrali. Dołączenie zewnętrznej pamięci — [Author ID1: at Fri Dec 14 17:46:00 2001

]- [Author ID1: at Fri Dec 14 17:46:00 2001

]zarówno programu, jak i danych —[Author ID1: at Fri Dec 14 17:46:00 2001

]-[Author ID1: at Fri Dec 14 17:46:00 2001

] wymusza jednak zbudowanie magistrali, a dokładniej —[Author ID1: at Fri Dec 14 17:47:00 2001

]-[Author ID1: at Fri Dec 14 17:47:00 2001

] wydzielenie z wyprowadzeń portów sygnałów adresowych (rysunek 3.6[Author ID1: at Fri Dec 14 17:47:00 2001

][Author ID1: at Fri Dec 14 17:47:00 2001

][Author ID1: at Fri Dec 14 17:47:00 2001

][Author ID1: at Fri Dec 14 17:47:00 2001

][Author ID1: at Fri Dec 14 17:47:00 2001

][Author ID1: at Fri Dec 14 17:47:00 2001

]Rysunek [Author ID1: at Fri Dec 14 17:47:00 2001

]6[Author ID1: at Fri Dec 14 17:47:00 2001

][Author ID1: at Fri Dec 14 17:47:00 2001

]).

Rysunek 3.6. [Author ID1: at Fri Dec 14 17:47:00 2001

][Author ID1: at Fri Dec 14 17:47:00 2001

][Author ID1: at Fri Dec 14 17:47:00 2001

][Author ID1: at Fri Dec 14 17:47:00 2001

]6[Author ID1: at Fri Dec 14 17:47:00 2001

][Author ID1: at Fri Dec 14 17:47:00 2001

]. [Author ID1: at Fri Dec 14 17:47:00 2001

]Buforowanie wyprowadzeń mikroprocesora 8048

Młodsza część adresu znajduje się na wyprowadzeniach AD0 - [Author ID1: at Fri Dec 14 17:48:00 2001

]-[Author ID1: at Fri Dec 14 17:48:00 2001

]AD7, starsza natomiast —[Author ID1: at Fri Dec 14 17:48:00 2001

]-[Author ID1: at Fri Dec 14 17:48:00 2001

] na liniach PC0 - [Author ID1: at Fri Dec 14 17:48:00 2001

]-[Author ID1: at Fri Dec 14 17:48:00 2001

]PC3. Pojawieniu się młodszej części adresu towarzyszy stan „1” sygnału ALE, natomiast gdy ALE ma wartość „0”, linie DB przyjmują funkcję magistrali danych. Z tego powodu adres musi być zapamiętany w zewnętrznym rejestrze. Może nim być 74373 lub 74573 —[Author ID1: at Fri Dec 14 17:49:00 2001

]-[Author ID1: at Fri Dec 14 17:49:00 2001

] do obu tych układów informacja jest wpisywana podczas stanu „1” na wejściu C. W zastosowaniach praktycznych 74573 jest wygodniejszy ze względu na korzystniejsze rozmieszczenie wyprowadzeń.

Starsza część adresu nie musi być zapamiętywana. Może się jednak zdarzyć, [Author ID1: at Fri Dec 14 16:16:00 2001

] [Author ID1: at Fri Dec 14 16:16:00 2001

]że port P2 zawiera informacje, które muszą być cały czas dostępne dla systemu, nawet wtedy, gdy mikroprocesor odwołuje się do pamięci. Można wówczas zastosować dodatkowy rejestr, w którym informacja zostanie zapamiętana, gdy stan sygnału ALE będzie się zmieniał z „0” na „1”. Rejestrem takim może być 74374 lub 74574.

Przy dużych obciążeniach magistrali można także zbuforować linie danych oraz linie sterujące, na ogół jednak nie jest to konieczne. Rozwiązanie takie pokazane jest przy okazji jednostki centralnej z mikroprocesorem 8051.

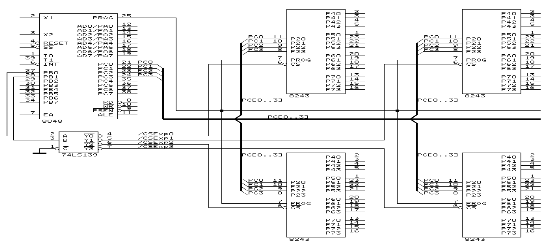

Do --> [Author:BZ] łączenie ekspanderów

W pewnych zastosowaniach liczba linii portów w mikrokomputerze jednoukładowym 8048 może być niewystarczająca. Z sytuacją taką mamy do czynienia na przykład wówczas, gdy stosujemy zewnętrzne pamięci —[Author ID1: at Fri Dec 14 17:51:00 2001

]-[Author ID1: at Fri Dec 14 17:51:00 2001

] duża część linii portów jest wykorzystana do utworzenia magistrali. Dlatego też do mikrokomputera 8048 można dołączyć jeden lub więcej ekspander 8243 (rysunek 3.7[Author ID1: at Fri Dec 14 17:52:00 2001

][Author ID1: at Fri Dec 14 17:51:00 2001

][Author ID1: at Fri Dec 14 17:51:00 2001

][Author ID1: at Fri Dec 14 17:51:00 2001

][Author ID1: at Fri Dec 14 17:51:00 2001

]Rysunek [Author ID1: at Fri Dec 14 17:51:00 2001

]7[Author ID1: at Fri Dec 14 17:51:00 2001

][Author ID1: at Fri Dec 14 17:51:00 2001

]). Jest to układ zaprojektowany specjalnie dla 8048. Jego podłączenie wymaga czterech linii portu (PC0 - [Author ID1: at Fri Dec 14 17:52:00 2001

]-[Author ID1: at Fri Dec 14 17:52:00 2001

]PC3) oraz sygnału PROG. Ekspander jest także wyposażony w wejście![]()

, które umożliwia wybór jednego z wielu układów. Z drugiej strony ekspander posiada cztery 4-bitowe porty wejścia-wyjścia. Transmisja informacji między 8048 a 8243 jest wspomagana przez specjalne rozkazy. Zasady tej transmisji są następujące:

podczas zbocza opadającego sygnału PROG do ekspandera przesyłany jest 2-bitowy kod rozkazu (zapis, odczyt, suma logiczna lub iloczyn logiczny) oraz numer portu ekspandera;[Author ID1: at Fri Dec 14 17:53:00 2001 ]

,[Author ID1: at Fri Dec 14 17:53:00 2001 ]podczas zbocza narastającego sygnału PROG przesyłane są 4-bitowe dane —[Author ID1: at Fri Dec 14 17:53:00 2001 ]

-[Author ID1: at Fri Dec 14 17:53:00 2001 ] kierunek tego przesyłu zależy od wykonywanego rozkazu.

Ponieważ wymiana danych z ekspanderem zachodzi w innym czasie,[Author ID1: at Fri Dec 14 17:53:00 2001

]kiedy indziej[Author ID1: at Fri Dec 14 17:53:00 2001

] niż pobieranie kodu rozkazu, możliwe jest bezkonfliktowe użycie tych samych linii portu P2 do realizacji obu czynności.

Rysunek 3.7. [Author ID1: at Fri Dec 14 17:54:00 2001

][Author ID1: at Fri Dec 14 17:54:00 2001

][Author ID1: at Fri Dec 14 17:54:00 2001

][Author ID1: at Fri Dec 14 17:54:00 2001

]7[Author ID1: at Fri Dec 14 17:54:00 2001

][Author ID1: at Fri Dec 14 17:54:00 2001

]. [Author ID1: at Fri Dec 14 17:54:00 2001

]Współpraca mikroprocesora 8048 z ekspanderami 8243

W przypadku konieczności dołączenia większej liczby ekspanderów należy wykorzystać ich wejścia ![]()

. Mogą one być podłączone do portu albo bezpośrednio,[Author ID1: at Fri Dec 14 17:54:00 2001

] albo poprzez dekoder. W obu przypadkach odwołanie do ekspandera musi być poprzedzone programowym ustawieniem linii portu w taki sposób, aby wejście ![]()

adresowanego układu było aktywne (stan logiczny „0”), natomiast [Author ID1: at Fri Dec 14 17:57:00 2001

]pozostałe wejścia[Author ID1: at Fri Dec 14 17:57:00 2001

]zaś[Author ID1: at Fri Dec 14 17:57:00 2001

] —[Author ID1: at Fri Dec 14 17:57:00 2001

]-[Author ID1: at Fri Dec 14 17:57:00 2001

] nieaktywne (stan logiczny „1”).

Zwiększenie liczby przerwań

Mikrokomputer jednoukładowy 8048 wyposażony jest w tylko jedno wejście przerwania zewnętrznego. W wielu zastosowaniach jest to zbyt mało jak na potrzeby systemu mikroprocesorowego. Można zwiększyć liczbę przerwań przez wykorzystanie liczników (wejścia T0 i T1), metoda ta jednak nie może być zastosowana, jeśli w systemie używa się licznika[Author ID1: at Fri Dec 14 17:59:00 2001

] wewnętrznego[Author ID1: at Fri Dec 14 17:59:00 2001

]y[Author ID1: at Fri Dec 14 17:59:00 2001

] mikrokomputera 8048.

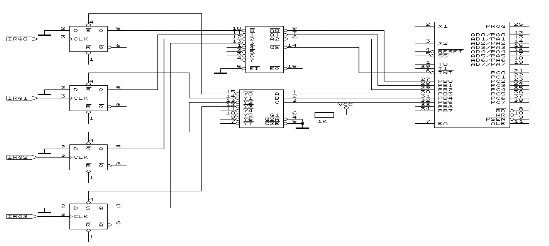

Przykład zwiększenia liczby przerwań zewnętrznych ilustruje rysunek 3.8[Author ID1: at Fri Dec 14 18:00:00 2001

] [Author ID1: at Fri Dec 14 17:59:00 2001

][Author ID1: at Fri Dec 14 17:59:00 2001

][Author ID1: at Fri Dec 14 17:59:00 2001

][Author ID1: at Fri Dec 14 17:59:00 2001

][Author ID1: at Fri Dec 14 17:59:00 2001

]Rysunek [Author ID1: at Fri Dec 14 17:59:00 2001

]8[Author ID1: at Fri Dec 14 17:59:00 2001

][Author ID1: at Fri Dec 14 17:59:00 2001

]. Przyjście przerwania [Author ID1: at Fri Dec 14 18:01:00 2001

]z dowolnego źródła powoduje wpisanie do przerzutnika wartości „0”, a to z kolei jest przyczyną[Author ID1: at Fri Dec 14 18:05:00 2001

]co powoduje[Author ID1: at Fri Dec 14 18:06:00 2001

] pojawienia[Author ID1: at Fri Dec 14 18:00:00 2001

]a[Author ID1: at Fri Dec 14 18:00:00 2001

] się stanu „0” na jednym z wejść kodera priorytetowego 74148. Zakodowany numer tego wejścia podaje się następnie na wejścia portu P1, czemu towarzyszy stan „0” wyjścia ![]()

kodera. Sygnał ten można zatem wykorzystać jako sygnał zgłoszenia przerwania (aktywny w [Author ID1: at Fri Dec 14 18:07:00 2001

]poziomi[Author ID1: at Fri Dec 14 18:07:00 2001

]em[Author ID1: at Fri Dec 14 18:07:00 2001

] niskim).

Rysunek 3.8. [Author ID1: at Fri Dec 14 18:08:00 2001

][Author ID1: at Fri Dec 14 18:08:00 2001

][Author ID1: at Fri Dec 14 18:08:00 2001

][Author ID1: at Fri Dec 14 18:08:00 2001

]8[Author ID1: at Fri Dec 14 18:08:00 2001

][Author ID1: at Fri Dec 14 18:08:00 2001

]. [Author ID1: at Fri Dec 14 18:08:00 2001

]Zwiększenie liczby przerwań zewnętrznych mikroprocesora 8048

Jeżeli w danej chwili będzie zgłoszonych więcej przerwań, na wejściach kodera pojawi się więcej stanów „0”. W takiej sytuacji koder wybiera wejście o najwyższym priorytecie (najniższym numerze).

Procedura obsługi przerwania zewnętrznego powinna rozpocząć się od znalezienia przyczyny przerwania. Jest to [Author ID1: at Fri Dec 14 18:11:00 2001

]możliwe przez odczyt zawartości bitów 0 - [Author ID1: at Fri Dec 14 18:10:00 2001

]-[Author ID1: at Fri Dec 14 18:10:00 2001

]3 portu P1. Następnie mikrokomputer wykonuje odpowiedni fragment programu zależnie od przyczyny przerwania. W procedurze obsługi przerwania powinien także znaleźć się fragment odpowiedzialny za skasowanie przerzutnika przyjętego przerwania. W omawianym przykładzie wystarczy w tym celu uaktywnić dekoder 74138 przez [Author ID1: at Fri Dec 14 16:16:00 2001

] [Author ID1: at Fri Dec 14 16:16:00 2001

]podanie „1” na jego wejście G1 —[Author ID1: at Fri Dec 14 18:12:00 2001

], a[Author ID1: at Fri Dec 14 18:12:00 2001

] numer kasowanego przerwania jest przecież równy numerowi przerwania obsłużonego.

Jeżeli po skasowaniu przerzutnika obsłużonego przerwania są aktywne jeszcze jakieś inne zgłoszenia, zostaną one obsłużone zgodnie z ich priorytetem według podanego powyżej algorytmu.

Układ pracy krokowej

W mikrokomputerze jednoukładowym 8048 możliwe jest stosowanie pracy krokowej na nieco odmiennych zasadach niż w mikroprocesorze Z-80. Nie jest tu bowiem możliwe zatrzymywanie pracy programu na dowolnym cyklu maszynowym, a tylko na cyklach pobrania kodu rozkazu. Zasady pracy krokowej są następujące:

jeżeli na wejściu

mikrokomputera 8048 jest stan „0”, przechodzi on w tryb pracy krokowej;[Author ID1: at Fri Dec 14 18:14:00 2001 ],[Author ID1: at Fri Dec 14 18:14:00 2001 ]w trybie tym następuje wstrzymanie realizacji programu w chwili rozpoczęcia pobierania kodu kolejnego rozkazu;[Author ID1: at Fri Dec 14 18:14:00 2001 ]

,[Author ID1: at Fri Dec 14 18:14:00 2001 ]podczas wstrzymania sygnał ALE jest w stanie „1”, a na magistrali adresowej (linie DB0-7 i P20-3) znajduje się adres pobieranego rozkazu; stan taki może trwać dowolnie długo;[Author ID1: at Fri Dec 14 18:16:00 2001 ]

,[Author ID1: at Fri Dec 14 18:16:00 2001 ]zakończenie stanu wstrzymania następuje wskutek podania stanu „1” na wejście

mikrokomputera 8048;[Author ID1: at Fri Dec 14 18:16:00 2001 ],[Author ID1: at Fri Dec 14 18:16:00 2001 ]wstrzymanie realizacji kolejnego rozkazu jest możliwe, jeżeli na wejście

podamy stan „0” tuż po przejściu sygnału ALE w stan „0”.

Przykładowy układ pracy krokowej ilustruje rysunek 3.9[Author ID1: at Fri Dec 14 18:16:00 2001

] [Author ID1: at Fri Dec 14 18:16:00 2001

][Author ID1: at Fri Dec 14 18:16:00 2001

][Author ID1: at Fri Dec 14 18:16:00 2001

][Author ID1: at Fri Dec 14 18:16:00 2001

][Author ID1: at Fri Dec 14 18:16:00 2001

]Rysunek [Author ID1: at Fri Dec 14 18:16:00 2001

]9[Author ID1: at Fri Dec 14 18:16:00 2001

][Author ID1: at Fri Dec 14 18:16:00 2001

]. Włączenie pracy krokowej następuje po rozwarciu przełącznika S1. Pierwsze pojawienie się stanu „0” sygnału ALE powoduje wówczas wyzerowanie przerzutnika 7474, a co za tym idzie —[Author ID1: at Fri Dec 14 18:17:00 2001

]-[Author ID1: at Fri Dec 14 18:17:00 2001

] podanie stanu „0” na wejście ![]()

mikrokomputera. Mikrokomputer przechodzi do stanu wstrzymania i pozostaje w nim do chwili naciśnięcia klawisza S2, kiedy to następuje[Author ID1: at Fri Dec 14 18:18:00 2001

]tóre powoduje[Author ID1: at Fri Dec 14 18:18:00 2001

] wpisanie do przerzutnika „1” logicznej i kontynuacja[Author ID1: at Fri Dec 14 18:19:00 2001

]ę[Author ID1: at Fri Dec 14 18:19:00 2001

] wykonywania programu.

Rysunek 3.9. [Author ID1: at Fri Dec 14 18:20:00 2001

][Author ID1: at Fri Dec 14 18:20:00 2001

][Author ID1: at Fri Dec 14 18:20:00 2001

][Author ID1: at Fri Dec 14 18:20:00 2001

]9[Author ID1: at Fri Dec 14 18:20:00 2001

][Author ID1: at Fri Dec 14 18:20:00 2001

]. [Author ID1: at Fri Dec 14 18:20:00 2001

]Układ pracy krokowej dla mikroprocesora 8048

Jednostka centralna 8051

8051 należy do grupy 8-bitowych mikrokomputerów jednoukładowych i jest to najpopularniejszy obecnie układ tej klasy. Zawiera on:

8-bitową jednostkę centralną;[Author ID1: at Fri Dec 14 18:22:00 2001 ]

,[Author ID1: at Fri Dec 14 18:22:00 2001 ]wewnętrzną pamięć programu o pojemności 4 - [Author ID1: at Fri Dec 14 18:20:00 2001 ]

-[Author ID1: at Fri Dec 14 18:20:00 2001 ]16 KB;[Author ID1: at Fri Dec 14 18:22:00 2001 ],[Author ID1: at Fri Dec 14 18:22:00 2001 ]wewnętrzną pamięć danych o pojemności 128 - [Author ID1: at Fri Dec 14 18:20:00 2001 ]

-[Author ID1: at Fri Dec 14 18:20:00 2001 ]256 B;[Author ID1: at Fri Dec 14 18:22:00 2001 ],[Author ID1: at Fri Dec 14 18:22:00 2001 ]cztery uniwersalne porty wejścia-wyjścia;[Author ID1: at Fri Dec 14 18:22:00 2001 ]

,[Author ID1: at Fri Dec 14 18:22:00 2001 ]układ czasowo-licznikowy, zawierający dwa programowalne liczniki 16-bitowe;[Author ID1: at Fri Dec 14 18:22:00 2001 ]

,[Author ID1: at Fri Dec 14 18:22:00 2001 ]port transmisji szeregowej;[Author ID1: at Fri Dec 14 18:22:00 2001 ]

,[Author ID1: at Fri Dec 14 18:22:00 2001 ]dwupoziomowy układ przerwań.

Warto zauważyć, że każdy producent ma w ofercie procesory rozszerzone o różne układy wewnętrzne, jak np.:

dodatkowe porty wejścia-wyjścia, często posiadające[Author ID1: at Fri Dec 14 18:23:00 2001 ]

wyposażone w[Author ID1: at Fri Dec 14 18:23:00 2001 ] dodatkowe funkcje;[Author ID1: at Fri Dec 14 18:24:00 2001 ],[Author ID1: at Fri Dec 14 18:24:00 2001 ]rozszerzone układy czasowo-licznikowe i układy przerwań;[Author ID1: at Fri Dec 14 18:24:00 2001 ]

,[Author ID1: at Fri Dec 14 18:24:00 2001 ]dodatkowe interfejsy szeregowe, m.

,[Author ID1: at Fri Dec 14 18:24:00 2001 ]przetworniki analogowo-cyfrowe i komparatory analogowe;[Author ID1: at Fri Dec 14 18:24:00 2001 ]

,[Author ID1: at Fri Dec 14 18:24:00 2001 ]zegary czasu rzeczywistego i układy nadzorujące.

W dalszej części książki będziemy zajmować się wyłącznie wersją podstawową 8051, a dokładniej —[Author ID1: at Fri Dec 14 18:24:00 2001

]-[Author ID1: at Fri Dec 14 18:24:00 2001

] układem 8031, pozbawionym wewnętrznej pamięci programu. Układ ten może zaadresować 64 KB pamięci programu (wewnętrznej lub zewnętrznej), 256 B wewnętrznej pamięci danych oraz 64 KB zewnętrznej pamięci danych.

Opis wyprowadzeń 8051

Wśród wyprowadzeń układu 8051 można wyróżnić cztery porty wejścia-wyjścia,[Author ID1: at Fri Dec 14 18:25:00 2001

] ([Author ID1: at Fri Dec 14 18:25:00 2001

]w których większość wyprowadzeń pełni dodatkowe funkcje)[Author ID1: at Fri Dec 14 18:26:00 2001

], a także sygnały sterujące (rysunek 3.10[Author ID1: at Fri Dec 14 18:26:00 2001

][Author ID1: at Fri Dec 14 18:26:00 2001

][Author ID1: at Fri Dec 14 18:26:00 2001

][Author ID1: at Fri Dec 14 18:26:00 2001

][Author ID1: at Fri Dec 14 18:26:00 2001

]Rysunek [Author ID1: at Fri Dec 14 18:26:00 2001

]10[Author ID1: at Fri Dec 14 18:26:00 2001

][Author ID1: at Fri Dec 14 18:26:00 2001

]). Znaczenie sygnałów jest następujące:

PA —[Author ID1: at Fri Dec 14 18:27:00 2001 ]

-[Author ID1: at Fri Dec 14 18:27:00 2001 ] 8-bitowy, dwukierunkowy port wejścia-wyjścia, który może także pełnić funkcję młodszej połowy magistrali adresowej (A0 - [Author ID1: at Fri Dec 14 18:29:00 2001 ]-[Author ID1: at Fri Dec 14 18:29:00 2001 ]A7) oraz magistrali danych przy odwołaniach do zewnętrznych układów pamięci lub wejścia-wyjścia;[Author ID1: at Fri Dec 14 18:29:00 2001 ],[Author ID1: at Fri Dec 14 18:29:00 2001 ]PB —[Author ID1: at Fri Dec 14 18:27:00 2001 ]

-[Author ID1: at Fri Dec 14 18:27:00 2001 ] 8-bitowy, dwukierunkowy port wejścia-wyjścia;[Author ID1: at Fri Dec 14 18:30:00 2001 ],[Author ID1: at Fri Dec 14 18:30:00 2001 ]PC —[Author ID1: at Fri Dec 14 18:27:00 2001 ]

-[Author ID1: at Fri Dec 14 18:27:00 2001 ] 8-bitowy, dwukierunkowy port wejścia-wyjścia, który może także pełnić funkcję starszej połowy magistrali adresowej (bity A8 - [Author ID1: at Fri Dec 14 18:30:00 2001 ]-[Author ID1: at Fri Dec 14 18:30:00 2001 ]A15) przy odwołaniach do zewnętrznych układów pamięci lub wejścia-wyjścia;[Author ID1: at Fri Dec 14 18:30:00 2001 ],[Author ID1: at Fri Dec 14 18:30:00 2001 ]PD —[Author ID1: at Fri Dec 14 18:27:00 2001 ]

-[Author ID1: at Fri Dec 14 18:27:00 2001 ] 8-bitowy, dwukierunkowy port wejścia-wyjścia, którego poszczególne wyprowadzenia mogą także pełnić funkcje sygnałów sterujących:

RXD —[Author ID1: at Fri Dec 14 18:27:00 2001 ]

-[Author ID1: at Fri Dec 14 18:27:00 2001 ] wejście odbiornika portu transmisji szeregowej,TXD —[Author ID1: at Fri Dec 14 18:27:00 2001 ]

-[Author ID1: at Fri Dec 14 18:27:00 2001 ] wyjście nadajnika portu transmisji szeregowej,

,

[Author ID1: at Fri Dec 14 18:28:00 2001 ]—[Author ID1: at Fri Dec 14 18:27:00 2001 ]-[Author ID1: at Fri Dec 14 18:27:00 2001 ] wejścia przerwań zewnętrznych,T0, T1 —[Author ID1: at Fri Dec 14 18:27:00 2001 ]

-[Author ID1: at Fri Dec 14 18:27:00 2001 ] wejścia zewnętrzne do układu czasowo-licznikowego,

[Author ID1: at Fri Dec 14 18:28:00 2001 ]—[Author ID1: at Fri Dec 14 18:27:00 2001 ]-[Author ID1: at Fri Dec 14 18:27:00 2001 ] wyjście żądania odczytu z przestrzeni adresowej zewnętrznej pamięci danych,

[Author ID1: at Fri Dec 14 18:28:00 2001 ]—[Author ID1: at Fri Dec 14 18:27:00 2001 ]-[Author ID1: at Fri Dec 14 18:27:00 2001 ] wyjście żądania zapisu do przestrzeni adresowej zewnętrznej pamięci danych;[Author ID1: at Fri Dec 14 18:31:00 2001 ],[Author ID1: at Fri Dec 14 18:31:00 2001 ]

[Author ID1: at Fri Dec 14 18:28:00 2001 ]—[Author ID1: at Fri Dec 14 18:27:00 2001 ]-[Author ID1: at Fri Dec 14 18:27:00 2001 ] wyjście żądania odczytu z przestrzeni adresowej zewnętrznej pamięci programu;[Author ID1: at Fri Dec 14 18:31:00 2001 ],[Author ID1: at Fri Dec 14 18:31:00 2001 ]ALE —[Author ID1: at Fri Dec 14 18:27:00 2001 ]

-[Author ID1: at Fri Dec 14 18:27:00 2001 ] wyjście sygnału zegarowego o częstotliwości fXTAL/6, używane także jako wyjście strobujące adres podczas współpracy z zewnętrznymi układami pamięci lub wejścia-wyjścia;[Author ID1: at Fri Dec 14 18:31:00 2001 ],[Author ID1: at Fri Dec 14 18:31:00 2001 ]

—[Author ID1: at Fri Dec 14 18:27:00 2001 ]-[Author ID1: at Fri Dec 14 18:27:00 2001 ] wejście wymuszające pobieranie kodu rozkazów wyłącznie z zewnętrznej pamięci programu;[Author ID1: at Fri Dec 14 18:32:00 2001 ],[Author ID1: at Fri Dec 14 18:32:00 2001 ]XTAL1, XTAL2 —[Author ID1: at Fri Dec 14 18:28:00 2001 ]

-[Author ID1: at Fri Dec 14 18:28:00 2001 ] wejścia służące do podłączenia oscylatora kwarcowego, które mogą być też wejściami zewnętrznego sygnału taktującego (zależnie od wersji procesora jest to wejście XTAL1 lub XTAL2).

Rysunek 3.10. [Author ID1: at Fri Dec 14 18:32:00 2001

][Author ID1: at Fri Dec 14 18:32:00 2001

][Author ID1: at Fri Dec 14 18:32:00 2001

][Author ID1: at Fri Dec 14 18:32:00 2001

]10[Author ID1: at Fri Dec 14 18:32:00 2001

][Author ID1: at Fri Dec 14 18:32:00 2001

]. [Author ID1: at Fri Dec 14 18:32:00 2001

]Wyprowadzenia mikroprocesora 8051

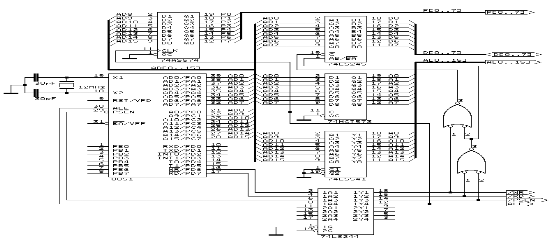

Buforowanie wyprowadzeń

Mikroprocesory rodziny 8051 —[Author ID1: at Fri Dec 14 18:33:00 2001

]-[Author ID1: at Fri Dec 14 18:33:00 2001

] podobnie jak i 8048 —[Author ID1: at Fri Dec 14 18:33:00 2001

]-[Author ID1: at Fri Dec 14 18:33:00 2001

] można rozbudować o [Author ID1: at Fri Dec 14 16:16:00 2001

] [Author ID1: at Fri Dec 14 16:16:00 2001

]zewnętrzne pamięci i [Author ID1: at Fri Dec 14 16:16:00 2001

] [Author ID1: at Fri Dec 14 16:16:00 2001

]układy peryferyjne. W najprostszych przypadkach nie jest konieczne budowanie magistrali. Dołączenie zewnętrznej pamięci —[Author ID1: at Fri Dec 14 18:33:00 2001

]-[Author ID1: at Fri Dec 14 18:33:00 2001

] zarówno programu, jak i danych —[Author ID1: at Fri Dec 14 18:33:00 2001

]-[Author ID1: at Fri Dec 14 18:33:00 2001

] wymusza jednak zbudowanie magistrali, a dokładniej —[Author ID1: at Fri Dec 14 18:34:00 2001

]-[Author ID1: at Fri Dec 14 18:34:00 2001

] wydzielenie z wyprowadzeń portów sygnałów adresowych (rysunek 3.11[Author ID1: at Fri Dec 14 18:34:00 2001

][Author ID1: at Fri Dec 14 18:34:00 2001

][Author ID1: at Fri Dec 14 18:34:00 2001

][Author ID1: at Fri Dec 14 18:34:00 2001

][Author ID1: at Fri Dec 14 18:34:00 2001

]Rysunek [Author ID1: at Fri Dec 14 18:34:00 2001

]11[Author ID1: at Fri Dec 14 18:34:00 2001

][Author ID1: at Fri Dec 14 18:34:00 2001

]).

Młodsza część adresu znajduje się na wyprowadzeniach AD0 - [Author ID1: at Fri Dec 14 18:35:00 2001

]-[Author ID1: at Fri Dec 14 18:35:00 2001

]AD7, starsza natomiast —[Author ID1: at Fri Dec 14 18:35:00 2001

]-[Author ID1: at Fri Dec 14 18:35:00 2001

] na liniach P20 - [Author ID1: at Fri Dec 14 18:35:00 2001

]-[Author ID1: at Fri Dec 14 18:35:00 2001

]P27. Pojawieniu się młodszej części adresu towarzyszy stan „1” sygnału ALE, natomiast gdy ALE ma wartość „0”, linie AD przyjmują funkcję magistrali danych. Z tego powodu adres musi być zapamiętany w zewnętrznym rejestrze. Może nim być 74373 lub 74573 —[Author ID1: at Fri Dec 14 18:36:00 2001

]-[Author ID1: at Fri Dec 14 18:36:00 2001

] do obu tych układów informacja jest wpisywana w czasie trwania stanu „1” na wejściu wpisującym C. W zastosowaniach praktycznych 74573 jest wygodniejszy ze względu na korzystniejsze rozmieszczenie wyprowadzeń.

Starsza część adresu nie musi być zapamiętywana. Może się jednak zdarzyć, [Author ID1: at Fri Dec 14 16:16:00 2001

] [Author ID1: at Fri Dec 14 16:16:00 2001

]że port P2 zawiera informacje, które muszą być cały czas dostępne dla systemu, nawet wtedy, gdy mikroprocesor odwołuje się do pamięci. Można wówczas zastosować dodatkowy rejestr, w którym informacja zostanie zapamiętana, gdy stan sygnału ALE będzie się zmieniał z „0” na „1”. Rejestrem takim może być 74374 lub 74574.

Przy wyjątkowo dużych obciążeniach magistrali można także zbuforować linie danych oraz linie sterujące, na ogół jednak nie jest to konieczne. W rozpatrywanym przypadku bufor danych 74245 jest włączany tylko wtedy, gdy mikrokomputer odwołuje się do zewnętrznej pamięci programu (aktywny sygnał ![]()

) lub danych (aktywny sygnał ![]()

lub ![]()

). Kierunek przesyłu danych określany jest na podstawie stanu sygnałów ![]()

i ![]()

—[Author ID1: at Fri Dec 14 18:37:00 2001

]-[Author ID1: at Fri Dec 14 18:37:00 2001

] aktywność któregokolwiek z nich oznacza przesył z otoczenia do mikrokomputera. Można też włączyć bufor danych na stałe, podłączając na jego wejście ![]()

stan „0”.

Rysunek 3.11. [Author ID1: at Fri Dec 14 18:38:00 2001

][Author ID1: at Fri Dec 14 18:38:00 2001

][Author ID1: at Fri Dec 14 18:38:00 2001

][Author ID1: at Fri Dec 14 18:38:00 2001

]11[Author ID1: at Fri Dec 14 18:38:00 2001

][Author ID1: at Fri Dec 14 18:38:00 2001

]. [Author ID1: at Fri Dec 14 18:38:00 2001

]Buforowanie wyprowadzeń mikroprocesora 8051

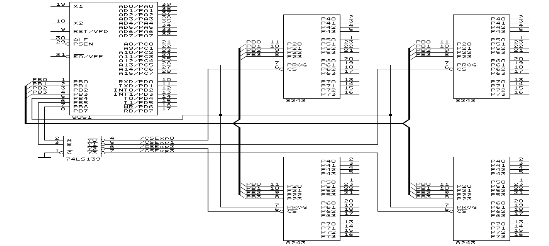

Dołączenie ekspanderów

W mikrokomputerze 8051 zrezygnowano ze sprzętowego wspomagania współpracy z ekspanderami. W razie potrzeby można jednak programowo emulować protokół komunikacji 8048 z ekspanderami. Przykład dołączenia czterech układów 8243 do mikrokomputera 8051 przedstawia rysunek 3.12[Author ID1: at Fri Dec 14 18:39:00 2001

] [Author ID1: at Fri Dec 14 18:39:00 2001

][Author ID1: at Fri Dec 14 18:39:00 2001

][Author ID1: at Fri Dec 14 18:39:00 2001

][Author ID1: at Fri Dec 14 18:39:00 2001

][Author ID1: at Fri Dec 14 18:39:00 2001

]Rysunek [Author ID1: at Fri Dec 14 18:39:00 2001

]12[Author ID1: at Fri Dec 14 18:39:00 2001

][Author ID1: at Fri Dec 14 18:39:00 2001

]. W układzie tym port [Author ID1: at Fri Dec 14 18:42:00 2001

]linie portu PA0-3 służą wymianie rozkazów i danych między mikrokomputerem a ekspanderem, natomiast linia PA4 emuluje sygnału[Author ID1: at Fri Dec 14 18:42:00 2001

] PROG mikrokomputera 8048. Wyprowadzenia PA5-7 umożliwiają wybór ekspandera, przy czym jeżeli liczba ich nie przekracza 3, dekoder nie jest potrzebny. Jego zastosowanie pozwala jednak zwiększyć liczbę ekspanderów do ośmiu. Liczba ta może być jeszcze większa, jeżeli do wyboru ekspandera zastosuje się dodatkowe linie portów.

Rysunek 3.12. [Author ID1: at Fri Dec 14 18:43:00 2001

][Author ID1: at Fri Dec 14 18:43:00 2001

][Author ID1: at Fri Dec 14 18:43:00 2001

][Author ID1: at Fri Dec 14 18:43:00 2001

][Author ID1: at Fri Dec 14 18:43:00 2001

]12[Author ID1: at Fri Dec 14 18:43:00 2001

][Author ID1: at Fri Dec 14 18:43:00 2001

]. [Author ID1: at Fri Dec 14 18:43:00 2001

]Dołączenie ekspanderów 8243 do mikroprocesora 8051

Zwiększenie liczby przerwań

Mikrokomputer jednoukładowy 8051 wyposażony jest w dwa wejścia przerwania zewnętrznego. W wielu zastosowaniach jest to zbyt mało jak na potrzeby systemu mikroprocesorowego. Można zwiększyć liczbę przerwań przez wykorzystanie liczników (wejścia T0 i T1). Metoda ta jednak nie może być zastosowana, jeśli w systemie używa się liczników[Author ID1: at Fri Dec 14 18:46:00 2001

]i[Author ID1: at Fri Dec 14 18:46:00 2001

] wewnętrznych[Author ID1: at Fri Dec 14 18:46:00 2001

]e[Author ID1: at Fri Dec 14 18:46:00 2001

] mikrokomputera 8051. Wówczas można zwiększyć liczbę przerwań,[Author ID1: at Fri Dec 14 18:46:00 2001

] podobnie,[Author ID1: at Fri Dec 14 18:46:00 2001

] jak w przypadku mikroprocesora 8048, wykorzystując przerzutniki typu D oraz opcjonalnie demultiplekser i koder priorytetowy.

Układ pracy krokowej

W mikrokomputerze jednoukładowym 8051 w ogóle nie występuje mechanizm pracy krokowej. Można go jednak zastąpić przez [Author ID1: at Fri Dec 14 18:53:00 2001

]Możliwe jest jednak [Author ID1: at Fri Dec 14 18:54:00 2001

]wykorzystanie w tym celu [Author ID1: at Fri Dec 14 18:54:00 2001

]układu przerwań. Do realizacji prostej pracy krokowej wystarczy przerwanie zewnętrzne, np. ![]()

. Powinno ono być zaprogramowane jako aktywne w [Author ID1: at Fri Dec 14 18:50:00 2001

]poziomi[Author ID1: at Fri Dec 14 18:50:00 2001

]em[Author ID1: at Fri Dec 14 18:50:00 2001

] niskim. Jeżeli wejście ![]()

ma wartość „0”, wywołuje się program obsługi tego przerwania. Program ten powinien się kończyć sekwencją rozkazów sprawdzającą, czy ![]()

[Author ID1: at Fri Dec 14 18:48:00 2001

]= [Author ID1: at Fri Dec 14 18:48:00 2001

]„1”, a następnie ![]()

[Author ID1: at Fri Dec 14 18:48:00 2001

]= [Author ID1: at Fri Dec 14 18:48:00 2001

]„0”. Wówczas wyjście z procedury obsługi przerwania jest możliwe, [Author ID1: at Fri Dec 14 18:56:00 2001

]J[Author ID1: at Fri Dec 14 18:55:00 2001

]j[Author ID1: at Fri Dec 14 18:55:00 2001

]eżeli na wejściu ![]()

pojawi się sekwencja zmian 0 [Author ID1: at Fri Dec 14 18:49:00 2001

]→ [Author ID1: at Fri Dec 14 18:49:00 2001

]1 [Author ID1: at Fri Dec 14 18:49:00 2001

]→ [Author ID1: at Fri Dec 14 18:49:00 2001

]0, wówczas wyjście z procedury obsługi przerwania jest możliwe[Author ID1: at Fri Dec 14 18:55:00 2001

]. Sekwencja ta pozwa[Author ID1: at Fri Dec 14 18:58:00 2001

]o[Author ID1: at Fri Dec 14 18:58:00 2001

]la[Author ID1: at Fri Dec 14 18:57:00 2001

]i[Author ID1: at Fri Dec 14 18:57:00 2001

] na wykonanie jednego rozkazu.[Author ID1: at Fri Dec 14 18:58:00 2001

],[Author ID1: at Fri Dec 14 18:58:00 2001

] P[Author ID1: at Fri Dec 14 18:58:00 2001

]p[Author ID1: at Fri Dec 14 18:58:00 2001

]o jego [Author ID1: at Fri Dec 14 18:58:00 2001

]realizacji k[Author ID1: at Fri Dec 14 18:58:00 2001

]tórego [Author ID1: at Fri Dec 14 18:58:00 2001

]mikroprocesor ponownie rozpocznie obsługę przerwania ![]()

.

2 Część I ♦ Podstawy obsługi systemu WhizBang (Nagłówek strony)

2 C:\Moje dokumenty\Korekta\Uklady mikro\1 Od autora\r3-1.doc

[Author ID1: at Fri Dec 14 16:51:00 2001 ][Author ID1: at Fri Dec 14 16:51:00 2001 ][Author ID1: at Fri Dec 14 16:51:00 2001 ][Author ID1: at Fri Dec 14 16:51:00 2001 ][Author ID1: at Fri Dec 14 16:51:00 2001 ] Na rysunku w napisach „K2 [Author ID1: at Fri Dec 14 16:52:00 2001 ]— krok” i „K1 — tryb pracy układu” powinny być naniesione myślniki, a także spacje przed [Author ID1: at Fri Dec 14 16:53:00 2001 ]nimi [Author ID1: at Fri Dec 14 16:54:00 2001 ]i po nich[Author ID1: at Fri Dec 14 16:53:00 2001 ].[Author ID1: at Fri Dec 14 16:54:00 2001 ]

[Author ID1: at Fri Dec 14 18:01:00 2001 ][Author ID1: at Fri Dec 14 18:01:00 2001 ][Author ID1: at Fri Dec 14 18:01:00 2001 ][Author ID1: at Fri Dec 14 18:01:00 2001 ][Author ID1: at Fri Dec 14 18:01:00 2001 ] Może po prostu: Przerwanie z dowolnego źródła powoduje ...[Author ID1: at Fri Dec 14 18:01:00 2001 ]

Wyszukiwarka

Podobne podstrony:

9012

9012

9012

9012

BN 62 9012 01 ?GLY I BLOKI?ME NTOWO GLINIANE Z WYPELNIACZAMI

9012

9012

14 С 9012А хар2

2sc9014 9012 wzmacniacz

13 С 9012А хар1

12 С 9012А коор

49 С 9012В хар

48 С 9012В коор

więcej podobnych podstron