|

|

Ćw. nr: 1 |

|

Temat:

|

|

|

Data wykonania ćwiczenia :

|

Ocena: |

SPRAWOZDANIE

Cel ćwiczenia :

Celem ćwiczenia jest pomiar oraz porównanie wartości parametrów statycznych układów wykonanych w technice TTL z wartościami parametrów układów wykonanych w technice unipolarnej CMOS.

Badanie bramki TTL: UCY 7400

Tabela prawdy

Pomiar napięcia wyjściowego w stanie wysokim UOH

Schemat pomiarowy i wynik

Schemat pomiarowy i wynik

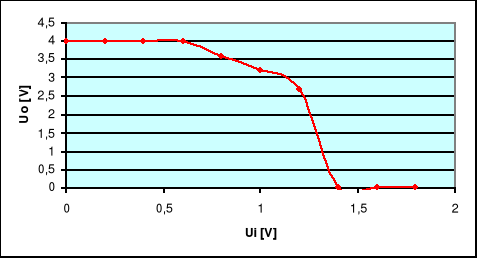

Schemat pomiarowy i wynikWyznaczanie charakterystyki przejściowej

Schemat pomiarowyTabelka pomiarowa

Charakterystyka

Pomiar zwarciowego prądu wyjściowego w stanie wysokim IOS

Schemat pomiarowy i wynik

Obciążalność wyjściowa bramki TTL

Schemat pomiarowy i wynikiObliczenia

Schemat pomiarowy i wynikiObliczenia

Badanie bramki CMOS: 7404Tabela prawdy

A

Pomiar napięcia wyjściowego w stanie wysokim UOH

Schemat pomiarowy i wynikPomiar napięcia wyjściowego w stanie niskim UOL

Schemat pomiarowy i wynik

Schemat pomiarowy i wynik

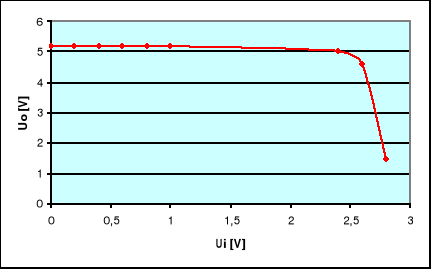

Schemat pomiarowy i wynikWyznaczanie charakterystyki przejściowej

Schemat pomiarowyCharakterystyka

Pomiar zwarciowego prądu wyjściowego w stanie wysokim IOS

Schemat pomiarowy i wynikObciążalność wyjściowa bramki TTL

Schemat pomiarowy i wyniki

Obliczenia

Schemat pomiarowy i wynikiObliczenia

Uwagi i wnioski

A |

B |

Y |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

UOH= 3 V

1.3 Pomiar napięcia wyjściowego w stanie niskim UOL

1.3.1 Schemat pomiarowy i wynik

UOL= 0 V

1.4 Pomiar wejściowego prądu w stanie niskim IIL

IIL= 1,1 mA

1.5 Pomiar wejściowego prądu w stanie wysokim IIH

IIH= 14 A

Ui [V] |

0 |

0,2 |

0,4 |

0,6 |

0,8 |

1 |

1,2 |

1,4 |

1,6 |

1,8 |

Uo [V] |

4 |

4 |

4 |

4 |

3,6 |

3,2 |

2,7 |

0,04 |

0,04 |

0,03 |

IOS= 32 mA

a). dla stanu wysokiego

UOH

= 3V

R= 620

IOH= 4,8 mA

![]()

b). dla stanu niskiego

UOL= 0,5 V

R= 100

IOL= 42,5 mA

![]()

Y |

|

0 |

1 |

1 |

0 |

UOH= 4,5 V

UOL= 0 V

2.4. Pomiar wejściowego prądu w stanie niskim IIL

IIL= 1,1 mA

2.5. Pomiar wejściowego prądu w stanie wysokim IIH

IIH= 40 A

2.6.2. Tabelka pomiarowa

Ui [V] |

0 |

0,2 |

0,4 |

0,6 |

0,8 |

1 |

2,4 |

2,6 |

2,8 |

Uo [V] |

5,2 |

5,2 |

5,2 |

5,2 |

5,2 |

5,2 |

5 |

4,6 |

1,5 |

IOS= 5 mA

a). dla stanu wysokiego

UOH= 2,5 V

R= 1 k

IOH= 2,5 mA

![]()

b). dla stanu niskiego

UOL= 0,4 V

R= 2,4 k

IOL= 166 A

![]()

W ćwiczeniu zauważamy, że wartość napięcia wyjściowego i prądu wejściowego w stanie wysokim na bramce CMOS jest większa niż na bramce TTL. Natomiast wartość napięcia wyjściowego i prądu wejściowego w stanie niskim na bramce CMOS i bramce TTL jest taka sama. Zwarciowy prąd wyjściowy w stanie wysokim przy bramce CMOS jest ponad sześciokrotnie mniejsze. Wyjściowy prąd w stanie wysokim na bramce TTL jest pawie dwa razy większy niż na bramce CMOS, a prąd wyjściowy w stanie niskim na bramce TTL jest rzędu pięćdziesięciu miliamperów, natomiast na bramce CMOS jest prawie nieznaczny (rzędu stu mikroamperów). Obciążalność bramki CMOS w stanie wysokim jest kilka razy mniejsza niż bramki TTL. Obciążalność bramki TTL w stanie niskim jest dużo większa niż bramki CMOS.

9

Wyszukiwarka

Podobne podstrony:

Pomiary wielkosci elektrycznych Badanie bramek logicznych id 37

Pomiary wielkości elektrycznych Instrukcja do ćw 09 Badanie bramek logicznych

Cw 1 Badanie bramek logicznych

Badanie cyfrowych bramek logicznych1, Nr. ?wiczenia: Temat:

BADANIE CYFROWYCH BRAMEK LOGICZNYCH, WSI

Badanie cyfrowych bramek logicznych2, Laboratorium układów elektronicznych

Badanie cyfrowych bramek logicznych6, Politechnika Opolska

Elektronika - Badanie cyfrowych bramek logicznych, Politechnika Opolska, sprawozdania, zachomikowane

Badanie funktorów logicznych., Klasa

Badanie funktorów logicznych., Klasa

Badanie funktorów logicznych TTL

Badanie Funkcji Logicznych

Wszystkie możliwe kombinacje bramek logicznych na zestykach przekażników, Wszystkie możliwe kombinac

więcej podobnych podstron