Politechnika Wrocławska Wydział Elektryczny

|

Skład grupy :

|

Rok studiów III Grupa Semestr VI Rok akadem. |

|||

Laboratorium Podstaw Automatyki

|

|||||

Data wyk.ćwicz.

|

Nr ćw .

|

Temat : Badanie i synteza kombinacyjnych i sekwencyjnych układów logicznych |

Ocena : |

||

I. Cel ćwiczenia

Celem ćwiczenia jest poznanie toku postępowania podczas syntezy i analizy układów kombinacyjnych ,zaznajomienie się z metodami minimalizacji funkcji oraz realizacja układów z wykorzystaniem bezstykowych elementów logicznych.

II. Synteza układów kombinacyjnych

Tablica zależności stanów

Postać dziesiętna |

Postać binarna |

||||

|

X3 |

X2 |

X1 |

X0 |

Y |

0 |

0 |

0 |

0 |

0 |

- |

1 |

0 |

0 |

0 |

1 |

1 |

2 |

0 |

0 |

1 |

0 |

0 |

3 |

0 |

0 |

1 |

1 |

0 |

4 |

0 |

1 |

0 |

0 |

- |

5 |

0 |

1 |

0 |

1 |

- |

6 |

0 |

1 |

1 |

0 |

1 |

7 |

0 |

1 |

1 |

1 |

1 |

8 |

1 |

0 |

0 |

0 |

0 |

9 |

1 |

0 |

0 |

1 |

1 |

10 |

1 |

0 |

1 |

0 |

- |

11 |

1 |

0 |

1 |

1 |

0 |

12 |

1 |

1 |

0 |

0 |

- |

13 |

1 |

1 |

0 |

1 |

1 |

14 |

1 |

1 |

1 |

0 |

0 |

15 |

1 |

1 |

1 |

1 |

- |

Dla 1,6,7,9,13 należy uzyskać „1” ; dla 2,3,8,11,14 należy uzyskać „0” ; pozostałe stany obojętne .

Tablica Karnougha dla funkcji czterech zmiennych z zaznaczonymi maksymalnymi konturami dla grupy jedynek

x3,x2 |

00 |

01 |

11 |

10 |

|

- |

1 |

0 |

0 |

|

- |

- |

1 |

1 |

11 |

- |

1 |

- |

1 |

|

0 |

1 |

0 |

- |

Po utworzeniu maksymalnych grup otrzymano normalną postać minimalną sumy w postaci :

![]()

Daną funkcję należy zrealizować na bramkach NAND.

Aby zrealizować funkcję na bramkach NAND ,funkcję podaną powyżej należy przedstawić w postaci iloczynów i negacji (wyeliminować operacje sumowania ):

![]()

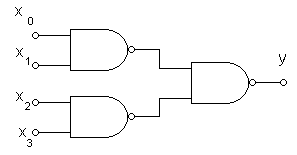

Schemat układu logicznego złożonego z bramek NAND :

Sprawdzenie poprawności działania układu logicznego przeprowadzono na makiecie pomiarowej ,na której znajdowały się bramki NAND oraz lampki sygnalizacyjne. Świecenie lampek sygnalizowało stan na wyjściu układu logicznego(,,1”-lamka świeci , ,,0”-lampka zgaszona) .W wyniku obserwacji stwierdzono ,że układ działał poprawnie .

III. Synteza układu sekwencyjnego metodą tablic kolejności łączeń

Wyznaczanie taktów działania i niedziałania elementów wyjściowych ( Y1 , Y2 ) sporządzono w tablicy kolejności łączeń

Takty |

0 |

1 |

2 |

3 |

4 |

5 |

6 |

|

20 |

x1 |

- |

+ |

|

|

|

|

|

21 |

x2 |

- |

|

|

|

+ |

|

|

|

y1 |

- |

|

+ |

|

|

- |

|

|

y2 |

- |

|

|

+ |

|

|

- |

St.łącz. |

0 |

1 |

5 |

13 |

15 |

11 |

3 |

|

Sporządzanie tablic Karnoughta dla wyjść y1 , y2

Dla y1 :

y2,y1 |

00 |

01 |

11 |

10 |

|

0 |

1 |

0 |

- |

01 |

- |

1 |

- |

- |

11 |

- |

1 |

0 |

- |

|

- |

- |

0 |

- |

Dla zakreślonych w tablicy maksymalnych konturów jedynkowych otrzymano następujące wyrażenie strukturalne :

![]()

Dla y2 :

y2,y1 |

00 |

01 |

11 |

10 |

|

0 |

0 |

0 |

- |

|

- |

1 |

- |

- |

|

- |

1 |

1 |

- |

10 |

- |

- |

0 |

- |

Dla zakreślonych w tablicy maksymalnych konturów jedynkowych otrzymano następujące wyrażenie strukturalne :

y2 = y1

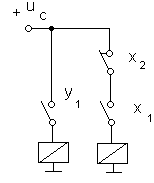

Realizacja układu za pomocą elementów stykowych :

Sprawdzenie poprawności działania układu logicznego przeprowadzono na makiecie pomiarowej ,w której wykorzystano przekaźniki oraz lampki sygnalizacyjne. W wyniku obserwacji stwierdzono ,że układ działał poprawnie .

1

Wyszukiwarka