POLITECHNIKA WARSZAWSKA Zakład Sterowania Ruchem Kolejowym |

LABORATORIUM PODSTAW AUTOMATYKI |

SPRAWOZDANIE Z ĆWICZENIA NR 2

ELEMENTY LOGICZNE

SKŁAD ZESPOŁU

|

GRUPA TwT |

SEMESTR V |

|

|

|||

Data wykonania ćwiczenia 19-10-2003 |

Data oddania sprawozdania 26-10-2003 |

||

1) Realizacja diodowa funkcji logicznych

Na początku ćwiczenia zapoznaliśmy się z budową stanowiska i dostępnymi elementami. Następnie po analizie schematów wybraliśmy elementy - dwie diody oraz dwa oporniki o skrajnych wartościach

R1 = 470Ω i R2 = 220kΩ. Rezystancje zostały wybrane tak abyśmy w wyniku pomiarów otrzymali możliwie skrajne wartości potencjałów. Jako napięcie zasilania układu przyjęliśmy potencjał -6[V].

Po połączeniu pierwszego układu wykonaliśmy pomiary dla dwóch rezystancji.

R1 = 470Ω |

|

R2 = 220kΩ |

|||||||||

UA [V] |

UB [V] |

UR1 [V] |

UZ [V] |

|

UA [V] |

UB [V] |

UR2 [V] |

UZ [V] |

|||

0 |

0 |

0 |

-5,26 |

|

0 |

0 |

0 |

-5,27 |

|||

0 |

-3,40 |

-2,67 |

-3,40 |

|

0 |

-5,27 |

-4,83 |

-5,27 |

|||

-3,26 |

0 |

-2,88 |

-3,26 |

|

-5,27 |

0 |

-5,13 |

-5,27 |

|||

-3,26 |

-3,26 |

-2,88 |

-3,26 |

|

-5,27 |

-5,27 |

-5,13 |

-5,27 |

|||

A |

B |

X |

|||||||||

0 |

0 |

0 |

|||||||||

0 |

1 |

1 |

|||||||||

1 |

0 |

1 |

|||||||||

1 |

1 |

1 |

|||||||||

Przy wartości rezystancji 470Ω następuje spadek potencjału zasilania, który nie występuje przy rezystancji 220kΩ. Wynika to z tego, że przy mniejszej rezystancji przepływa przez układ większy prąd.

Po założeniu, że stan logiczny 0 odpowiada potencjałowi o wartości 0[V], a stan logiczny 1 potencjałowi mniejszemu od zera. Przyjęcie, że 0 odpowiada dokładnie potencjałowi 0[V] jest możliwe ze względu na konstrukcję układu.

Na podstawie wyników utworzyliśmy tabelę prawdy, z której wynika, iż układ realizuje funkcję sumy logicznej („LUB”, „OR”).

Realizowana przez układ funkcja jest zależna od przyjętej konwencji napięciowo logicznej. Po zmianie konwencji na odwrotną układ realizowałby funkcję iloczynu logicznego („I”, „AND”).

Następnie połączyliśmy drugi układ wykorzystując te same elementy i wykonaliśmy pomiary dla dwóch rezystancji. Jako napięcie zasilania układu przyjęliśmy potencjał -3[V].

R1 = 470Ω |

|

R2 = 220kΩ |

|||||||||

UA [V] |

UB [V] |

UR1 [V] |

UZ [V] |

|

UA [V] |

UB [V] |

UR2 [V] |

UZ [V] |

|||

0 |

0 |

-0,37 |

-3,07 |

|

0 |

0 |

-0,12 |

-3,80 |

|||

0 |

-3,07 |

-0,37 |

-3,07 |

|

0 |

-3,80 |

-0,12 |

-3,80 |

|||

-3,10 |

0 |

-0,70 |

-3,10 |

|

-3,80 |

0 |

-0,40 |

-3,80 |

|||

-3,80 |

-3,80 |

-3,80 |

-3,80 |

|

-3,80 |

-3,80 |

-3,79 |

-3,80 |

|||

A |

B |

X |

|||||||||

0 |

0 |

0 |

|||||||||

0 |

1 |

0 |

|||||||||

1 |

0 |

0 |

|||||||||

1 |

1 |

1 |

|||||||||

Po założeniu, że stan logiczny 0 odpowiada potencjałowi z zakresu 0÷-1[V], a stan logiczny 1 potencjałowi mniejszemu od -1. W tym układzie nie można przyjąć, że 0 odpowiada dokładnie potencjałowi 0[V] z uwagi na spadek napięcia na złączach diod (na wyjściu nigdy nie wystąpi potencjał 0[V]).

Na podstawie wyników utworzyliśmy tabelę prawdy, z której wynika, iż układ realizuje funkcję iloczynu logicznego („I”, „AND”).

Realizowana przez układ funkcja jest zależna od przyjętej konwencji napięciowo logicznej. Po zmianie konwencji na odwrotną układ realizowałby funkcję sumy logicznej („LUB”, „OR”).

2) Realizacja tranzystorowa funkcji logicznych

2.1) Badanie funktora NOT

Podobnie jak poprzednio po przeanalizowaniu problemu i schematu układu przystąpiliśmy do wyboru elementów. Jako napięcie zasilania układu przyjęliśmy potencjał -9[V]. Na początek przyjęliśmy oporników RA, RB, RC wartość rezystancji równą 12kΩ. Wybór był podyktowany tym, iż jest to wartość znajdująca się mniej więcej w połowie dostępnych rezystancji, co umożliwia późniejszą zmianę wartości oporników zarówno w górę jak i w dół.

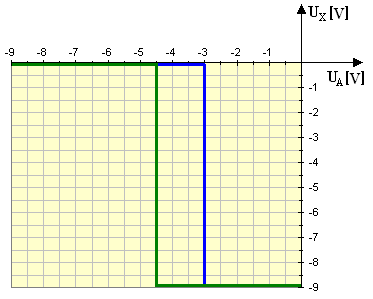

Kolejnym krokiem było wyznaczenie żądanej charakterystyki UX = f(UA).

Idealną charakterystyką jest taka, w której stan z 0 na 1 zmienia się w połowie zakresu napięciowego (linia zielona). W praktyce, co można zaobserwować po przeanalizowaniu wyników poprzedniego ćwiczenia im bardziej obciążamy wyjście układu, tym bardziej zmniejsza się potencjał na wyjściu układu. Wynika z tego, że przesunięcie charakterystyki w kierunku zera (linia niebieska) będzie korzystne. Poprawia to obciążalność układu - zwiększa, tolerancję sprzętową, powoduje też, iż układ staje się bardziej odporny na zakłócenia.

Następnie przystąpiliśmy do dokonania pomiarów:

Lp. |

UA[V] |

-0 |

-0,5 |

-1 |

-1,5 |

-2 |

-2,5 |

-3 |

-3,5 |

-4 |

-4,5 |

-5 |

RA |

RB |

RC |

1 |

UX[V] |

-9,03 |

-9,03 |

-8,98 |

-0,30 |

-0,03 |

-0,02 |

|

|

|

|

|

12k |

12k |

12k |

2 |

UX[V] |

-9,04 |

-9,04 |

-9,04 |

-9,04 |

-9,01 |

-8,57 |

-5,19 |

-0,13 |

0,06 |

|

|

39k |

12k |

12k |

3 |

UX[V] |

-9,04 |

-9,04 |

-9,04 |

-9,04 |

-9,00 |

-8,02 |

-0,07 |

-0,03 |

|

|

|

12k |

3,7k |

12k |

4 |

UX[V] |

-9,05 |

-9,05 |

-9,05 |

-9,05 |

-9,05 |

-8,94 |

-7,68 |

-5,30 |

-2,03 |

-0,18 |

-0,10 |

12k |

3,7k |

1k |

5 |

UX[V] |

-9,06 |

-9,06 |

-9,06 |

-9,06 |

-8,77 |

-6,89 |

-3,7 |

-0,8 |

-0,1 |

|

|

12k |

5,7k |

1k |

Otrzymane przebiegi wyglądają następująco:

Analiza poszczególnych przypadków:

Przełączenie następuje w strefie od -2 do -1[V], co nastąpiło przy potencjale mniejszym od założonego.

Zwiększenie rezystancji opornika RA. Przełączenie nastąpiło w strefie od -3,5 do -2,5[V], czyli przy oczekiwanym potencjale. Z analizy układu wynika, iż zwiększenie rezystancji opornika RA jest niekorzystne, gdyż powoduje, że spadek napięcia jest na nim większy, co dla odmiany zmniejsza tolerancję układu na zmniejszenie potencjału na wejściu układu. Zmniejszenie potencjału występuje na wyjściach układów przy dołączaniu do nich wejść kolejnych układów.

Powrót do poprzedniej wartości rezystancji opornika RA i zmniejszenie rezystancji opornika RB. Przełączenie nastąpiło w strefie od -3 do -2,5[V], czyli przy oczekiwanym potencjale.

Po uzyskaniu oczekiwanej charakterystyki mieliśmy poprawić układ w kierunku zwiększenia jego obciążalności na wyjściu poprzez zmniejszenie wartości rezystancji opornika RC. W efekcie przełączenie nastąpiło w strefie od -4,5 do -2,5[V], co zdecydowanie pogorszyło charakterystykę układu, poprzez poszerzenie strefy przejścia i przesunięcie punktu przełączania.

W celu dalszej poprawy układu zwiększyliśmy wartość rezystancji opornika RB. Przełączenie nastąpiło w strefie od -3,5 do -2[V], czyli przy oczekiwanym potencjale.

Dzielnik złożony z rezystancji RA i RB steruje prądem bazy, a więc decyduje o punkcie przełączania tranzystora. Ze względu na konieczność łączenia ze sobą podobnych układów dobrze jest, aby spadek napięcia na oporniku RA był jak najmniejszy, co za tym idzie, aby wartość jego rezystancji nie była duża. Dlatego lepszy efekt uzyskaliśmy zmniejszając rezystancję opornika RB.

Wartość rezystancji opornika RC decyduje o obciążalności wyjścia układu. Im większa będzie wartość jego rezystancji tym większy będzie na nim spadek potencjał, a więc tym niższy będzie potencjał na wyjściu, który będzie malał przy dołączaniu kolejnych stopni.

W celu uzyskania odpowiednich parametrów, musimy liczyć się z przyjęciem pewnych kompromisów, np.: pomiędzy obciążalnością układów, a szerokością strefy przejścia.

2.2) Badanie funktorów NOR (negacji sumy) i NAND (negacji iloczynu)

A |

B |

C |

UX |

X |

0 |

0 |

0 |

-9,06 |

1 |

0 |

0 |

1 |

-0,05 |

0 |

0 |

1 |

0 |

-0,05 |

0 |

0 |

1 |

1 |

-0,05 |

0 |

1 |

0 |

0 |

-0,05 |

0 |

1 |

0 |

1 |

-0,03 |

0 |

1 |

1 |

0 |

-0,03 |

0 |

1 |

1 |

1 |

-0,02 |

0 |

Funktor NOR (negacja sumy logicznej)

Układ funktora NOR zbudowaliśmy w oparciu o poprzedni układ.

Dla oporników na wejściach A, B i C układu przyjęliśmy wartość rezystancji równą 12kΩ, było to podyktowane koniecznością zachowania zgodności z poprzednim układem. Pozostałe wartości rezystancji pozostały bez zmian. Po dokonaniu pomiarów otrzymaliśmy wyniki świadczące o tym, iż układ spełnia funkcję trzywejściowej bramki NOR. Układ pracował zgodnie z naszymi oczekiwaniami.

A |

B |

C |

UX |

X |

0 |

0 |

0 |

-9,10 |

1 |

0 |

0 |

1 |

-9,10 |

1 |

0 |

1 |

0 |

-9,10 |

1 |

0 |

1 |

1 |

-9,10 |

1 |

1 |

0 |

0 |

-9,10 |

1 |

1 |

0 |

1 |

-9,10 |

1 |

1 |

1 |

0 |

-9,10 |

1 |

1 |

1 |

1 |

-8,77 |

0 |

Funktor NAND (negacja iloczynu logicznego)

Po przeanalizowaniu schematu ostatniego układu przystąpiliśmy do wyboru elementów. Ze względu na konieczność zachowania zgodności z poprzednimi układami przyjęliśmy taką jak poprzednio wartość rezystancji oporników na wejściach A, B i C układu i na jego wyjściu.

Ze względu na brak możliwości przyjęcia dla oporników łączących bazy tranzystorów z potencjałem masy układu (zerowym) przyjęliśmy dla nich wartość rezystancji równą 1kΩ.

Uzyskane wyniki są niezadawalające, ponieważ na wyjściu układu dla wartości, która powinna reprezentować 0 logiczne potencjał wyniósł -8,77[V], a więc różniący się nieznacznie od potencjału logicznej 1.

W celu poprawienia układu zmierzyliśmy potencjały na kolektorach poszczególnych układów, a następnie poprawialiśmy układ zmieniając wartości rezystancji oporników łączących bazy tranzystorów z potencjałem masy układu (RBx).

Lp. |

TA |

TB |

TC |

RBA |

RBB |

RBC |

1 |

-8,77 |

-0,07 |

-0,04 |

1k |

1k |

1k |

2 |

-8,66 |

-1,01 |

-0,03 |

2k7 |

1k |

1k |

3 |

-7,78 |

-0,96 |

-0,54 |

2k7 |

2k |

1k |

4 |

-0,26 |

-0,19 |

-0,10 |

2k7 |

2k |

1k47 |

5 |

-0,91 |

-0,13 |

-0,05 |

1k47 |

2k |

2k7 |

Z powyższego wynika, iż zmieniając rezystancje poszczególnych tranzystorów można poprawić układ. Dobrze jest, gdy wartości rezystancji w dla kolejnych tranzystorów są coraz większe, z tego wynika, iż ilość wejść w układzie jest ograniczona.

Wyszukiwarka