Chipsety i magistrale komputera

Chipset

Na początku komputery PC składały się z procesora oraz dużej ilości układów scalonych. W miarę rozwoju technologii mikroelektronicznej funkcje bloków były wchłaniane przez układy scalone wyższej generacji. W chwili obecnej na płycie głównej montuje się nie więcej niż dwa układy scalone bardzo wysokiej skali integracji oraz najwyżej kilka chipów pomocniczych.

Już od dawna można umieścić cały komputer w jednym układnie scalonym (z punktu widzenia technologii wykonania). W ten sposób buduje się wiele układów automatyki i komputery przemysłowe. Systemy takie mają wiele zalet np.: są tanie i odporne na wiele czynników zakłócających. Niestety takie rozwiązanie ma bardzo sztywną architekturę. Trudno wyobrazić sobie układ scalony, do którego można by podłączyć procesor i wszystkie obecne na płycie gniazda: PCI, ISA, AGP itp.

Chipset spełnia następujące funkcje:

· Sprzężenie z procesorem poprzez magistralę FSB (Front Side Bus).

· Realizacja kontrolera pamięci operacyjnej i obsługa magistrali pamięciowej.

· Sterowanie pamięci podręcznej L2 (lub L3)

· Implementacja magistral PCI, AGP i ewentualnie ISA.

· Integracja większości bloków klasycznej architektury PC: kontrolera przerwań, układów DMA, złączy szeregowych i równoległych, złącza Game-Port, magistrali EIDE, kontrolera klawiatury, kontrolera dysków elastycznych oraz kolejnych rozszerzeń, takich jak USB, IrDA.

Punktem centralnym jest układ, do którego przyłącza się procesor. Najczęściej określa się go jako: North Bridge, Host Bridge, MCH-Memory Hub lub CPU Bridge.

Pamięć L1 wielu wcześniejszych oraz aktualnie wytwarzanych procesorów, zawarta jest

w strukturze półprzewodnikowej CPU i taktowana z pełną częstotliwością zegara.

Lokalizacja pamięci podręcznej L2 zależy od typu CPU. W procesorach Intel Pentium II/III lub AMD K6-III najczęściej osadzona jest na module lub strukturze. Pamięć L2 współczesnych procesorów Athlon i Pentium 4 zlokalizowana jest

na strukturze półprzewodnikowej CPU i taktowana z jego pełną częstotliwością zegarową.

Drugi człon chipsetu realizuje większość funkcji pomocniczych i nazywany jest najczęściej South Bridge. Intel posługiwał się do niedawna nazwą PIIX (PCI to ISA/IDE Xcelerator), a obecnie stosuje określenie ICH (I/O Controller Hub). Człon ten zawierał początkowo jedynie punkty przyłączeniowe dla magistral PCI i ISA. Układy scalone ostatniej generacji pozwoliły na integrację większości złączy I/O (równoległych, szeregowych, USB, Fire Wire, IrDA itd.).

Magistrala FSB

FSB - (z ang. Front Side Bus) inaczej magistrala lub szyna danych, poprzez którą odbywa się komunikacja między chipsetem, procesorem a pamięcią. Od jej taktowania zależy szybkość i efektywność przekazywania danych między procesorem a pamięcią. Jej wielokrotność (określana przez mnożniki) określa taktowanie procesora oraz PCI i dysków . Domyślna częstotliwość taktowania FSB to 100 MHz

Mnożnik CPU określa wewnętrzną częstotliwość pracy procesora, wyrażaną jako wielokrotność częstotliwości FSB.

Nowoczesne chipsety obsługują mnożniki od 3,0x do 10,0 i więcej razy.

Na przykład procesor Pentium III 1,2 GHz, współpracujący z magistralą FSB 133,33 MHz, ma mnożnik równy 9,0, ponieważ 9,0 x 133,33 = 1200,0.

W przypadku procesorów Pentium 4 mnożnik odnosi się do faktycznej częstotliwości FSB (100, 133 lub 200 MHz), a nie do częstotliwości po zwielokrotnieniu (400, 533, lub 800 MHz).

Na przykład procesor Pentium 4 2,4 GHz, przystosowany do pracy z FSB 100/400 MHz, ma mnożnik równy 24x, procesor Pentium 4 2,4 GHz, przystosowany do pracy z FSB 133/533 MHz, ma mnożnik równy 18x, zaś mnożnik Pentium 4 2,4 GHz dla FSB 200/800 MHz wynosi 12x.

Firma AMD nadaje swoim procesorom Athlon XP własne oznaczenia, które nie mówią nic o faktycznej częstotliwości, z jaką one pracują, ale i w tym przypadku obowiązują te same zasady. Na przykład Athlon XP 3000+, który pracuje z częstotliwością 2,16 GHz i jest przystosowany do pracy z FSB 166 MHz, ma mnożnik równy 13.

Manipulacje zegarem FSB znajdowały jednak swe odbicie nie tylko w prędkości samego CPU. Częstotliwość ta stanowiła bazę dla przebiegów sterujących magistrale PCI i AGP. Wszystkie układy Intela dla podstawki Socket 7 pracowały oficjalnie do częstotliwości 66 MHz. Odpowiednio do tego skonstruowane chipsety, w tym również sztandarowy przedstawiciel klasy Slot-1, czyli 440BX. Zegar magistrali PCI pozyskiwany był z dzielenia FSB:2, a magistrala PCI pracowała zawsze synchronicznie z FSB, z wszelkimi tego skutkami. Przy FSB 50 MHz otrzymywano 25 MHz na PCI.

Zegar PCI stanowił źródło odniesienia również dla interfejsu EIDE, a nie wszystkie dyski twarde tolerowały skracanie czasu cykli I/O. Ten sam problem odnosił się do zegara magistrali AGP, który w przypadku chipsetów Intela pozyskiwany był z magistrali FSB w stosunku 1:1.

Chipsety konkurencyjne (np. ViA Apollo Pro133A) były bardziej elastyczne

i umożliwiały manipulacje częstotliwościami magistral w dosyć szerokim zakresie przy utrzymaniu reżimów na szynach PCI i AGP. Chipset ViA dopuszczał wprowadzanie przesunięcia ±33 MHz pomiędzy magistralami FSB i pamięciową oraz wybór jednego z trzech współczynników podziału pomiędzy AGP i FSB: 1:1, 2:3 lub 1:2.

Bardziej eleganckie wyjście z tego dylematu oferowały chipsety, które potrafiły formować sygnały sterujące dla magistral PCI i AGP w sposób niezależny od FSB.

W tych przypadkach posługiwano się metodą asynchroniczną

Stosowana była w chipsetach SiS, gdzie przebieg zegarowy dla magistrali AGP generowano w odrębnym układzie. Z sygnału tego (po podzieleniu przez 2) wyprowadzany był zegar PCI. Rozwiązanie takie nie było pozbawione wad.

Na skutek rozbieżności fazowej dostęp do magistrali PCI odbywał się z opóźnieniem jednego do dwóch taktów, przez co pracowała ona zdecydowanie wolniej.

Przepustowość magistrali FSB w warunkach rzeczywistych odbiega znacznie od szczytowych wartości teoretycznych wynikających z pomnożenia jej szerokości przez częstotliwość taktująca. Pasmo FSB odpowiadało również za transfer na odcinku L1/L2 w architekturach, których pamięć L2 leżała poza procesorem [2].

Obsługa pamięci operacyjnej i magistrali pamięciowej

Jednym z głównych zadań chipsetu jest pośredniczenie w wymianie danych między procesorem a główną pamięcią komputera. Kontroler pamięci, będący częścią chipsetu, ma dwa istotne obowiązki. Po pierwsze, zmniejsza on obciążenie procesora, samodzielnie wykonując pewne operacje na pamięci, takie jak odświeżanie jej zawartości czy zarządzanie transferami w trybie DMA. Po drugie, gdy procesor odczytuje lub zapisuje dane do pamięci, nie robi tego bezpośrednio, lecz właśnie za pomocą kontrolera pamięci.

Podobnie jak główna magistrala systemowa (FSB) łączy chipset z procesorem, magistrala pamięci łączy chipset z główną pamięcią komputera. Od szybkości

i szerokości magistrali pamięci zależy to, z jaką prędkością można przesyłać dane między tymi dwoma podzespołami. Jeżeli magistrala pamięci nie jest w stanie przesyłać danych przynajmniej tak szybko jak FSB, istnieje niebezpieczeństwo, że procesor będzie musiał bezczynnie czekać na nadejście potrzebnych mu informacji. Właśnie dlatego nowoczesne chipsety są optymalizowane w taki sposób, aby magistrala pamięci mogła być jak najszybsza. Jej przepustowość zależy od dwóch powiązanych ze sobą czynników:

· Szybkości - magistrala pamięci determinuje to, jak szybkie układy pamięci można instalować w komputerze. Jeżeli na przykład na płycie głównej znajduje się chipset zaprojektowany z myślą o obsłudze pamięci DDR-SDRAM

i magistrali pamięci o maksymalnej prędkości 333 MHz, to w komputerze warto instalować co najwyżej moduły DDR333 MHz (PC2700). Z kolei jakiś inny chipset może współpracować z magistralą pamięci o częstotliwości 400 MHz,

co oznacza, że idealnym rozwiązaniem dla komputera będą kości DDR400 (PC3200). Szybkie magistrale pamięci potrafią obsługiwać wolniejsze moduły. Na przykład chipset przystosowany do pracy z modułami PC3200 zazwyczaj będzie też działał prawidłowo z kośćmi PC2700. Podobnie w komputerach

z wolnymi magistralami pamięci można instalować szybkie moduły, tyle że ich wydajność będzie ograniczana przez częstotliwość taktowania magistrali.

Na przykład w komputerze, którego chipset obsługuje jedynie pamięci PC2700 można instalować moduły PC3200, ale będą one działały tak samo jak kości PC2700. Chipsety szóstej i siódmej generacji obsługują magistrale pamięci

o częstotliwościach od 66 MHz do 400 MHz.

· Szerokości - standardowe chipsety współpracujące z pamięciami SDR-SDRAM

i DDR-SDRAM przesyłają dane po 64-bitowych (8-bajtowych) ścieżkach.

Po przemnożeniu szerokości magistrali pamięci przez częstotliwość jej taktowania uzyskuje się jej maksymalną możliwą przepustowość. Na przykład 64-bitowa magistrala pamięci pracująca z częstotliwością 400 MHz może przesyłać maksymalnie 8 bajtów x 400 MHz, czyli 3200 MB na sekundę. Niektóre chipsety szóstej i siódmej generacji obsługują dwukanałowe, a więc dwukrotnie szersze magistrale pamięci, co pozwala przesyłać w jednym cyklu zegara dwukrotnie więcej danych. Na przykład chipsety nVIDIA nForce2

i Intel 875P obsługują dwukanałowe magistrale DDR-SDRAM taktowane częstotliwością 400 MHz, pozwalające przesyłać za jednym razem aż 16 bajtów. Przy 400 MHz daje to 6400 MB na sekundę.

Magistrale układów pamięci

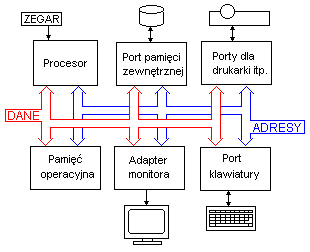

Wszystkie części składowe komputera są połączone centralnym ciągiem komunikacyjnym - magistralami, czyli szynami. Kolejowa symbolika jest jak najbardziej na miejscu, ponieważ magistrala to nie tylko przewody; obejmuje ona między innymi układy komutacyjne - swoiste zwrotnice, umożliwiające procesorowi dostęp do konkretnych bloków funkcjonalnych. Urządzenia te mogą same żądać dostępu do procesora. Na przykład wtedy gdy w porcie klawiatury pojawi się informacja, co oznacza że operator się obudził i czegoś chce. Urządzenia w których coś sie dzieje wysyłają wtedy sygnał żądania obsługi, a procesor utworzy połączenie na magistrali, po czym rozpocznie pobieranie danych i dekodowanie ich.

Właściwie są dwie główne szyny systemowe: szyna danych i szyna adresowa. W komputerze wszystko ma swój "adres zamieszkania". Na szynie adresowej ustawia się adres komórki pamięci, urządzenia lub portu, z którym ma zostać połączona szyna danych. Dla porządku trzeba wspomnieć o trzeciej, szynie sterowań, służącej do wymiany sygnałów sterujących i kontrolnych.

Magistrale komputera są w większości równoległe; mają tyle przewodów, ile bitów mają porcje informacji nimi przesyłane. Szerokość szyny danych zwykle odpowiada ilości bitów w słowie maszynowym. Mówiąc, że nasz komputer jest np. 32-bitowy określamy długość słowa maszynowego, a co za tym idzie wewnętrzną przepustowość systemu

Magistrale te są zsynchronizowane z FSB

Wyszukiwarka

Podobne podstrony:

Magistrale i sygnały sterujące mikroprocesora, Szkoła, Systemy Operacyjnie i sieci komputerowe, utk,

format[1], Szkoła, Systemy Operacyjnie i sieci komputerowe, systemy, semestr I

Pamięci dynamiczne RAM, Szkoła, Systemy Operacyjnie i sieci komputerowe, utk, semestr I

bramki logiczne, Szkoła, Systemy Operacyjnie i sieci komputerowe, utk, semestr I

router, Szkoła, Systemy Operacyjnie i sieci komputerowe, sieci

Dyski twarde-woluminy, Szkoła, Systemy Operacyjnie i sieci komputerowe, systemy, semestr II

Konsola odzyskiwania systemu, Szkoła, Systemy Operacyjnie i sieci komputerowe, systemy, semestr II

Rejestry, Szkoła, Systemy Operacyjnie i sieci komputerowe, utk, semestr I

Podstawy architektury komputera, Szkoła, Systemy Operacyjnie i sieci komputerowe, utk, semestr II

Teoria informatyki, Szkoła, Systemy Operacyjnie i sieci komputerowe, utk, semestr II

instalacja win 2003, Szkoła, Systemy Operacyjnie i sieci komputerowe, systemy, semestr II

Sieci radiowe typu Wireless LAN, Szkoła, Systemy Operacyjnie i sieci komputerowe, sieci

Komunikaty konsoli-Posłaniec, Szkoła, Systemy Operacyjnie i sieci komputerowe, systemy, semestr II

Zasady bezpieczeństwa w Windows, Szkoła, Systemy Operacyjnie i sieci komputerowe, systemy, semestr I

Dyski twarde-konspekt, Szkoła, Systemy Operacyjnie i sieci komputerowe, utk, semestr II

DOS, Szkoła, Systemy Operacyjnie i sieci komputerowe, systemy, semestr I

ghost, Szkoła, Systemy Operacyjnie i sieci komputerowe, systemy, semestr I

więcej podobnych podstron