PRZERZUTNIKI I REJESTRY

Opis stanowiska laboratoryjnego

Budowa stanowiska

Stanowisko składa się ze sterownika połączonego z klawiaturą oraz z dwóch plansz. Pierwsza z plansz umożliwia sprawdzenie działania podstawowych typów przerzutników. Druga plansza zawiera różne rodzaje rejestrów, zrealizo-wanych z wykorzystaniem wcześniej badanych przerzutników i umożliwia obserwację ich działania w trybie równoległego i szeregowego wpisu lub odczytu danych.

Plansza przerzutników

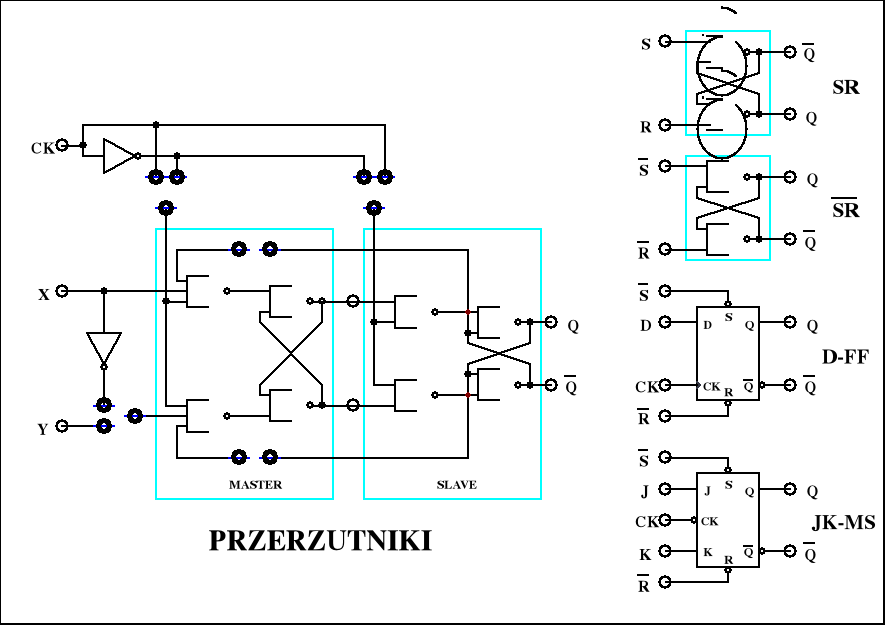

Widok planszy przerzutników przedstawia rysunek 1. Po lewej stronie planszy umieszczono dwa proste przerzutniki: nadrzędny (master) i podpo-rządkowany (slave). Przy pomocy zworek, możliwe jest wprowadzanie zewnętrznych połączeń i zamodelowanie kilku podstawowych przerzutników: asynchronicznego i synchronicznego przerzutnika SR, przerzutników D LATCH i D FLIP-FLOP oraz przerzutnika JK MASTER-SLAVE.

Rys. 1. Widok planszy przerzutników

Po prawej stronie planszy umieszczono cztery typy, w pełni połączonych i gotowych do działania przerzutników, zrealizowanych w oparciu o popularne układy scalone: SN74HC02 (bramki NOR), SN74HC00 (bramki NAND), SN74HC74 (przerzutnik D-FF) i SN74HC76 (przerzutnik JK-MS).

Zmianę stanu logicznego, z jedynki na zero lub z zera na jedynkę, na wybranym wejściu badanego przerzutnika, można uzyskać przez jednokrotne naciśnięcie odpowiedniego klawisza klawiatury. Wyjątek stanowi klawisz spacji, generujący na wejściach synchronizujących CK krótki impuls dodatni, czyli sekwencję „0-1-0”. Obserwację stanów logicznych na wyjściach badanych przerzutników umożliwiają dwukolorowe, zielono-czerwone diody LED. Zgodnie z konwencją przyjętą w laboratorium, świecenie diody LED na zielono sygnalizuje stan niski (0), świecenie na czerwono natomiast sygnalizuje stan wysoki (1). Aby uczynić wszelkie przeprowadzane badania bardziej czytelne możliwe jest selektywne włączanie i wyłączanie diod sygnalizujących stany logiczne na wejściach i wyjściach każdego z przerzutników. Zmianę aktywności diod sygnalizacyjnych realizują klawisze numeryczne: „1” (przerzutnik o struk-turze programowalnej zworkami), „2” - asynchroniczny przerzutnik SR z wejściami prostymi, „3” - asynchroniczny przerzutnik SR z wejściami zanego-wanymi, „4” - przerzutnik D - FF oraz „5” - przerzutnik JK-MS.

Zadania laboratoryjne

Połączyć asynchroniczny przerzutnik SR z wejściami prostymi zgodnie z rysunkiem 2. (cały przerzutnik zamyka się w części „master”). Sprawdzić wszystkie możliwe ustawienia wejść z uwzględnieniem stanów poprzednich. Opracować tabelę stanów przerzutnika. Porównać działanie wykonanego modelu przerzutnika z przerzutnikiem zrealizowanym na bramkach NOR.

Rys. 2. Asynchroniczny przerzutnik SR z wejściami prostymi

Połączyć synchroniczny przerzutnik SR z wejściami prostymi zgodnie z rysunkiem 3. (cały przerzutnik zamyka się w części „master”). Sprawdzić wszystkie możliwe ustawienia wejść z uwzględnieniem stanów poprzednich. Opracować tabelę stanów przerzutnika.

Rys. 3. Synchroniczny przerzutnik SR z wejściami prostymi

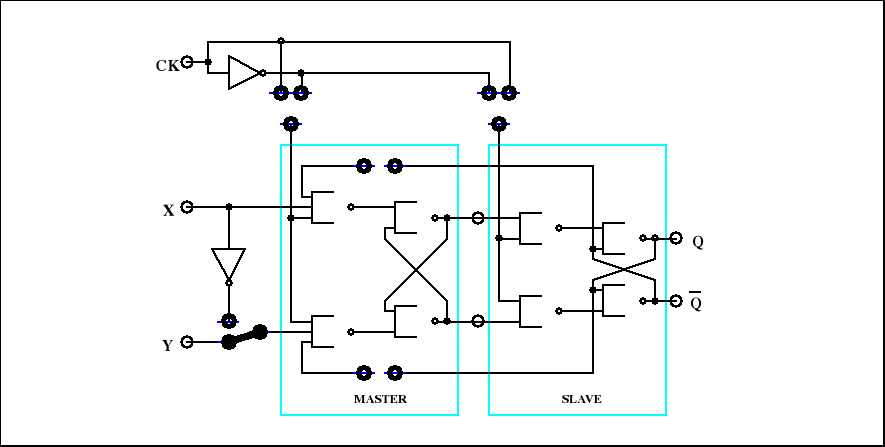

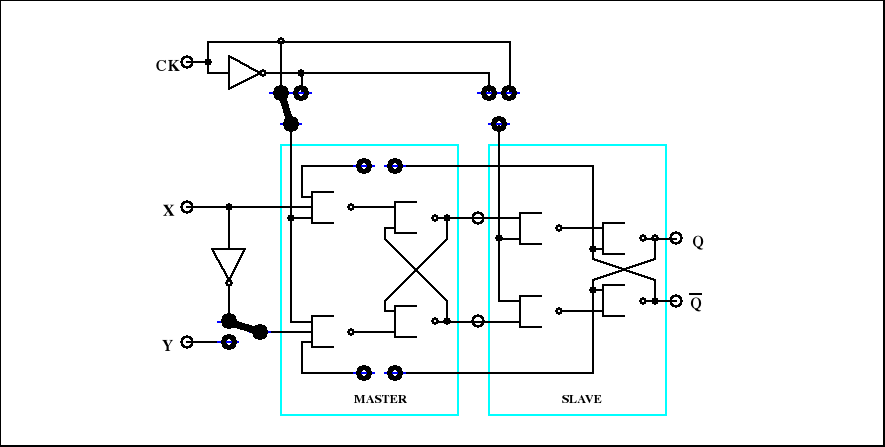

Połączyć synchroniczny przerzutnik SR-MS zgodnie z rysunkiem 4. Sprawdzić wszystkie możliwe ustawienia wejść z uwzględnieniem stanów poprzednich. Opracować tabelę stanów przerzutnika oraz tabelę wzbudzeń. Narysować wykresy czasowe.

Rys. 4. Synchroniczny przerzutnik SR-MS

Połączyć synchroniczny przerzutnik D-LATCH zgodnie z rysunkiem 5. (cały przerzutnik zamyka się w części „master”). Sprawdzić wszystkie możliwe ustawienia wejść z uwzględnieniem stanów poprzednich. Opracować tabelę stanów przerzutnika i tabelę wzbudzeń. Narysować wykresy czasowe.

Rysunek 5. Synchroniczny przerzutnik D-LATCH

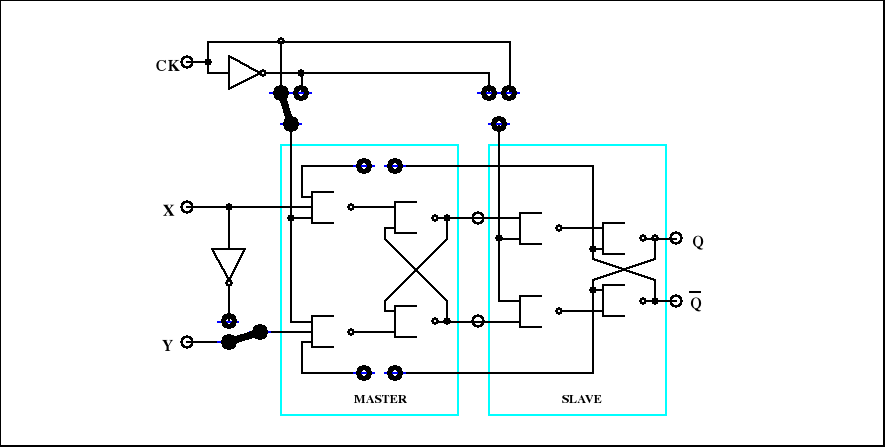

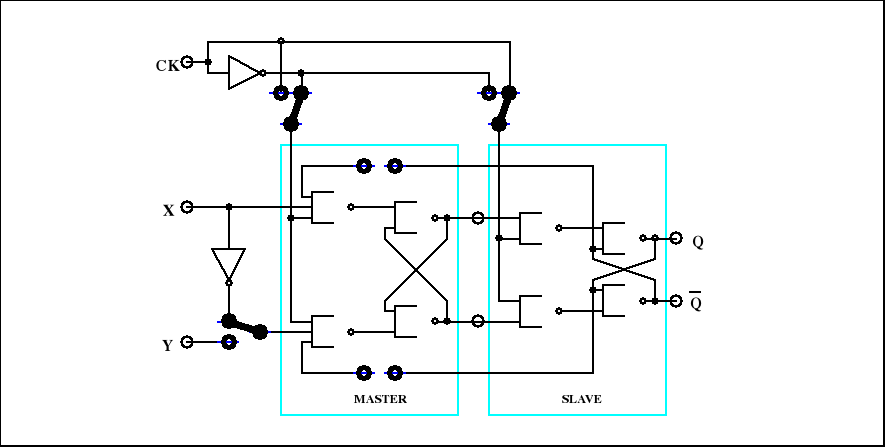

Połączyć synchroniczny przerzutnik D-FF zgodnie z rysunkiem 6. Sprawdzić wszystkie możliwe ustawienia wejść z uwzględnieniem stanów poprzednich. Opracować tabelę stanów przerzutnika i tabelę wzbudzeń. Narysować wykresy czasowe. Porównać działanie wykonanego modelu przerzutnika z przerzutnikiem D-FF z układu scalonego SN74HC74.

Rysunek 6. Synchroniczny przerzutnik D-FF

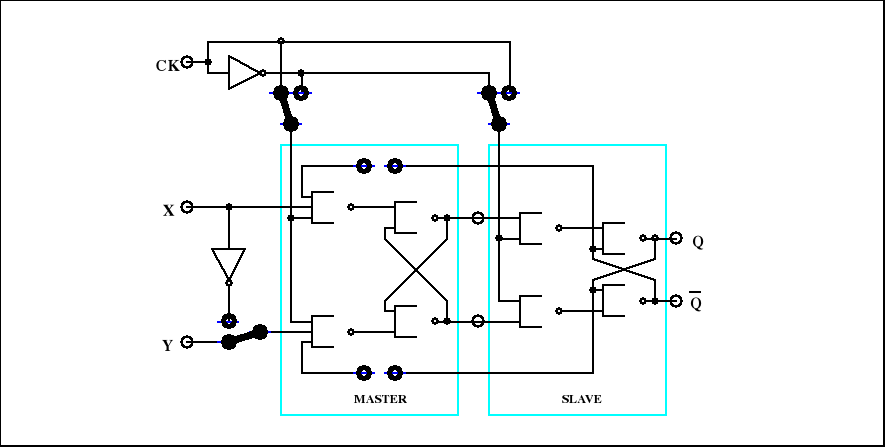

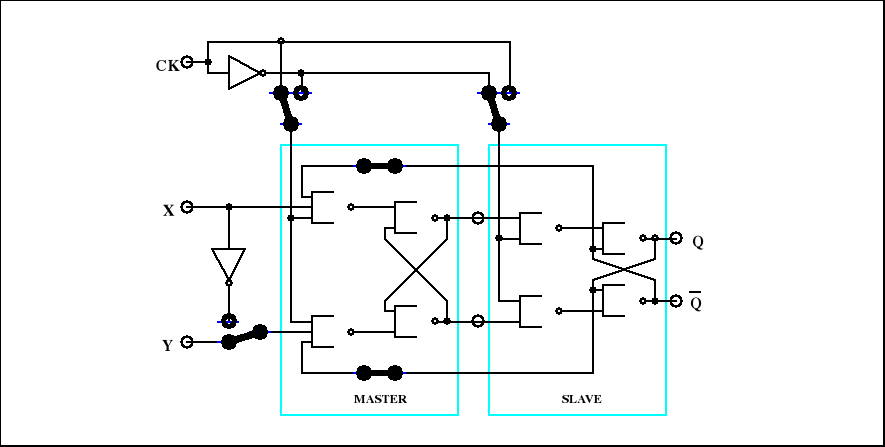

Połączyć synchroniczny przerzutnik JK-MS zgodnie z rysunkiem 7. Sprawdzić wszystkie możliwe ustawienia wejść z uwzględnieniem stanów poprzednich. Opracować tabelę stanów przerzutnika i tabelę wzbudzeń. Narysować wykresy czasowe. Porównać działanie wykonanego modelu przerzutnika z przerzutnikiem z układu scalonego SN74HC76.

Rysunek 7. Synchroniczny przerzutnik JK-MS

Wykaz klawiszy do obsługi planszy przerzutników zawiera tabela 1.

Tabela 1. Opis klawiszy do obsługi planszy przerzutników

klawisz |

opis |

C |

sygnał synchronizujący CK (tylko jedno zbocze) |

SPACJA |

sygnał synchronizujący CK ( pełny cykl - „0-1-0”) |

D |

wejście informacyjne D |

S |

wejście ustawiające S |

R |

wejście zerujące R |

J, X |

wejścia informacyjne J i X |

K, Y |

wejścia informacyjne K i Y |

Plansza rejestrów

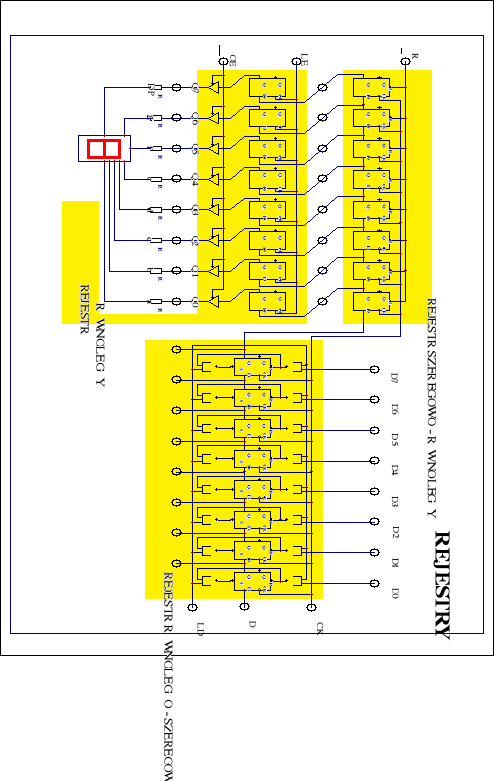

Widok planszy rejestrów przedstawiono na rys. 8. Na planszy umieszczono wszystkie podstawowe rodzaje rejestrów: równoległo-szeregowy, szeregowy, szeregowo-równoległy i równoległy. Rejestry umieszczone na planszy połączo-ne są w sposób symulujący szeregową linię transmisji danych, z równoległym wejściem (rejestr równoległo-szeregowy) i równoległym wyjściem (rejestr szeregowo-równoległy). Dodatkowy rejestr równoległy umożliwia zapamiętanie na wyjściu przesłanych danych w czasie przesyłania kolejnych porcji informacji.

Rys.8. Widok planszy rejestrów

REJESTR RÓWNOLEGŁO-SZEREGOWY - z wejściem równoległym (D0, D1, .... D7) i wyjściem szeregowym. Składa się z ośmiu przerzutników D-FF. Dane z wejścia równoległego wprowadzane są jednocześnie do rejestru stanem wysokim sygnału wpisu LD. Stan wysoki tego sygnału powoduje ustawienie przerzutników rejestru zgodnie ze stanem sygnałów wejściowych. Zmiana na jakimkolwiek wejściu, wywołuje natychmiastową zmianę stanu rejestru. Rejestr jest „przeźroczysty”. Wyłączenie aktywności sygnału LD powoduje zatrzymanie w rejestrze ostatnio zapisanej informacji. Rejestr jest wtedy w stanie pamiętania i nie reaguje na zmiany sygnałów na wejściu równoległym. Zapisane w rejestrze dane, wyprowadzane są z rejestru zboczami narastającymi sygnału synchronizu-jącego CK szeregowo, czyli „bit po bicie”. Wejście wpisu równoległego LD jest asynchroniczne i ma wyższy priorytet od wejścia synchronizującego CK. W efekcie aktywny stan LD blokuje wejście zegarowe i dlatego w czasie szeregowego wyprowadzania danych z rejestru, wejście LD musi być nieaktywne (stan niski). Stan wyjścia każdego z przerzutników rejestru monitorowany jest na bieżąco diodami LED.

REJESTR SZEREGOWY (SZEREGOWO-SZEREGOWY) - ponieważ rejestr równoległo-szeregowy ma dodatkowe wejście szeregowe D, może pełnić również rolę rejestru szeregowego z szeregowym wejściem i wyjściem. Dane z wejścia D wprowadzane są do rejestru narastającym zboczem sygnału synchronizującego CK, przy czym ze względu na niższy priorytet tego sygnału, wejście wpisu równoległego LD musi być w stanie nieaktywnym (niskim). Szeregowe wprowadzanie nowych danych do rejestru powoduje przesuwanie całej zawartości rejestru z lewej strony na prawą i jednoczesne wyprowadzanie poprzedniej zawartości rejestru, poprzez wyjście ostatniego w szeregu przerzutnika.

REJESTR SZEREGOWO-RÓWNOLEGŁY - z wejściem szeregowym i równoległym wyjściem. Składa się z ośmiu przerzutników D-FF. Dane wejściowe tego rejestru pochodzą z wyjścia rejestru równoległo-szeregowego. Dane są wprowadzane szeregowo do rejestru narastającymi zboczami sygnału synchronizującego CK i są stale dostępne na wyjściach równoległych, monitorowanych diodami LED. Dodatkowym wyposażeniem rejestru jest asynchroniczne wejście R, zerujące wszystkie przerzutniki rejestru. Stanem aktywnym tego wejścia jest poziom niski. Ze względu na wyższy priorytet wejścia zerującego R, musi ono pozostawać w stanie nieaktywnym (poziom wysoki) w trakcie szeregowego wprowadzania danych do rejestru.

REJESTR RÓWNOLEGŁY (RÓWNOLEGŁO-RÓWNOLEGŁY) - z równoległym wejściem i równoległym wyjściem (Q0, Q1, ..... Q7). Składa się z ośmiu przerzutników D-LATCH. Dane wejściowe tego rejestru w postaci równoległej podawane są z wyjścia równoległego rejestru szeregowo-równoległego. Sygnałem wpisującym dane do rejestru jest sygnał LE. Stan aktywny tego sygnału (wysoki) powoduje ustawienie przerzutników rejestru zgodnie ze stanem sygnałów wejściowych. Zmiana na jakimkolwiek wejściu wywołuje natychmiastową, odpowiednią zmianę stanu rejestru. Rejestr jest w tym stanie „przeźroczysty”. Wyłączenie aktywności sygnału LE powoduje zatrzymanie w rejestrze ostatnio zapisanej informacji. Rejestr jest wtedy w stanie pamiętania i nie reaguje na zmiany sygnałów na wejściu równoległym. Dodatkowym elementem rejestru równoległego jest bufor trójstanowy, otwierany sygnałem OE, aktywnym w stanie niskim. Wyjścia bufora na bieżąco monitorowane są diodami LED. Do wyjść bufora trójstanowego podłączono siedmiosegmentowy wyświetlacz LED, umożliwiający ekspozycję zawartości rejestru w postaci znaku alfanumerycznego.

Zmianę stanu logicznego, z jedynki na zero lub z zera na jedynkę, na wybranym wejściu sterującym (LD, CK, OE, LE i R), można uzyskać przez jednokrotne naciśnięcie odpowiedniego klawisza klawiatury. Zmianę stanu logicznego danych wejściowych (D, D0, D1, ... D7), można uzyskać przez jednokrotne naciśnięcie odpowiedniego klawisza klawiatury lub jednoczesny wpis całego bajtu. Klawisz spacji generuje na wejściu synchronizującym CK krótki impuls dodatni, czyli sekwencję „0-1-0”. Obserwację stanów logicznych na wyjściach badanych przerzutników umożliwiają dwukolorowe, zielono-czerwone diody LED. Zgodnie z przyjętą w laboratorium konwencją, świecenie diody LED na zielono sygnalizuje stan niski (0), świecenie na czerwono sygnalizuje stan wysoki (1), brak świecenia sygnalizuje stan wysokiej impedancji (HiZ). Wykaz klawiszy do obsługi planszy rejestrów zawiera tabela 2.

Tabela 2. Opis klawiszy do obsługi planszy rejestrów

klawisz |

opis |

C |

sygnał synchronizujący CK ( tylko jedno zbocze) |

SPACJA |

sygnał synchronizujący CK ( pełny cykl - „0-1-0”) |

D |

wejście szeregowe D |

L |

sygnał wpisu równoległego LD (wejście asynchroniczne, stan wysoki) |

R |

wejście zerujące R (wejście asynchroniczne, stan niski) |

E |

sygnał wpisu równoległego LE (wejście asynchroniczne, stan wysoki) |

O |

sygnał sterujący buforem trójstanowym OE (stan niski) |

0,1..7 |

zmiana stanu pojedynczego bitu wejścia równoległego D0, D1, .. D7 |

H, x y |

wpis całego bajtu wejścia równoległego (x, y = 0, 1 .. 9, A, .. F) |

Zadania laboratoryjne

Prześledzić proces wprowadzania i wyprowadzania danych do i z rejestru równoległo-szeregowego. Narysować przebiegi czasowe, ze szczególnym uwzględnieniem sygnału wpisu równoległego LD i sygnału synchronizują-cego CK.

Prześledzić proces wprowadzania i wyprowadzania danych do i z rejestru szeregowego. Narysować przebiegi czasowe, ze szczególnym uwzględnie-niem sygnału synchronizującego CK.

Prześledzić proces wprowadzania i wyprowadzania danych do i z rejestru szeregowo-równoległego. Narysować przebiegi czasowe, ze szczególnym uwzględnieniem sygnału zerującego R i sygnału synchronizującego CK.

Prześledzić proces wprowadzania i wyprowadzania danych do i z rejestru równoległego. Narysować przebiegi czasowe, ze szczególnym uwzględnie-niem sygnału wpisu równoległego LE i sygnału kontrolującego aktywność bufora trójstanowego OE.

Przeprowadzić transmisję szeregową kilku znaków alfanumerycznych z wejść równoległych D0, D1, .... D7, na siedmiosegmentowy wyświetlacz LED, w sposób eliminujący miganie wyświetlacza w czasie transmisji.

Przeprowadzić transmisję szeregową kilku znaków alfanumerycznych z wejścia szeregowego D, na siedmiosegmentowy wyświetlacz LED, w sposób eliminujący miganie wyświetlacza w czasie transmisji.

5

Wyszukiwarka

Podobne podstrony:

oscyloskop, IB PWr, Podstawy elektroniki i elektrotechniki 2

pierwsza, IB PWr, Podstawy elektroniki i elektrotechniki 2

cw12 sprawozdanie elektro w, IB PWr, Podstawy elektroniki i elektrotechniki 2

cw10 elektronika, IB PWr, Podstawy elektroniki i elektrotechniki 2

ćw 12, IB PWr, Podstawy elektroniki i elektrotechniki 2

Badanie Wzmacniaczy Operacyjnych, PWr, Podstawy elektroniki 2

ćw 5, IB PWr, Podstawy elektroniki i elektrotechniki 2

ćw.8, IB PWr, Podstawy elektroniki i elektrotechniki 2

ćw 2, IB PWr, Podstawy elektroniki i elektrotechniki 2

ćw 8, IB PWr, Podstawy elektroniki i elektrotechniki 2

cw8 elektro, IB PWr, Podstawy elektroniki i elektrotechniki 2

ćw 3, IB PWr, Podstawy elektroniki i elektrotechniki 2

Zagad NE09, Politechnika Wrocławska, PWR - W10- Automatyka i Robotyka, Sem3, Elektro, Podstawy elekt

sc5 druk, Politechnika Wrocławska, PWR - W10- Automatyka i Robotyka, Sem3, Elektro, Podstawy elektro

matrialy, PWR [w9], W9, 5 semestr, Podstawy elektrotechniki Lab, MATERIAŁY, podst ele lab - swistak,

SC3, Politechnika Wrocławska, PWR - W10- Automatyka i Robotyka, Sem3, Elektro, Podstawy elektrotechn

fazowe, Studia PWr [IŚ i BLiW], Podstawy Elektrotechniki

więcej podobnych podstron