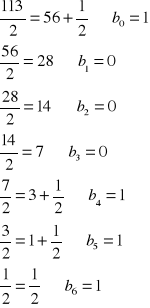

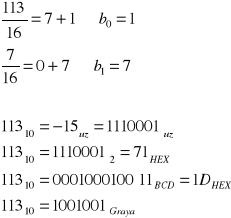

1.Zapisać liczbę 113 w kodzie binarnym, BCD i Graya oraz liczbę 113 w zapisie uzupełnień do 113. Wszystkie kody przedstawić w zapisie zero-jedynkowym i heksadecymalnym.

2.Omówić właściwości tranzystora bipolarnego bipolarnego zakresie odcięcia i nasycenia.

W stanie nasycenia oba złącza tranzystora są spolaryzowane w kierunku przewodzenia. Złącze kolektor-baza zaczyna przewodzić (przy przewodzącym drugim złączu), gdy napięcie C-E osiągnie wartość napięcia nasycenia ![]()

. ![]()

wynosi od ok. 0,20 do kilku V. Stan nasycenia odpowiada zwarciu na zaciskach C-E. Charakteryzuje go duża wartość ![]()

przy bardzo małym ![]()

. Rezystancja wyjścia ![]()

jest mała (w nasyceniu). Wynosi od ułamka ![]()

do kilkuset ![]()

.

W stanie nieprzewodzenia (odcięcia) obydwa złącza tranzystora są spolaryzowane w kierunku wstecznym. Odpowiada to rozwarciu na zaciskach kolektor-emiter. Płynący prąd jest mały. Granicę między zakresami aktywnymi i odcięcia stanowi prąd zerowy ![]()

.

![]()

-nap. Progowe (dla krzem. 0,5-0,8V)

Transformator nasycony: ![]()

Transformator odcięty ![]()

-duże, ![]()

-duże

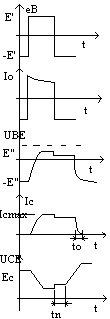

3.Narysować i omówić przebieg napięć wyjścia klucza z tranzystorem bipolarnym npn w układzie WE, sterowanego napięciem prostokątnym.

Klucz tranzystora dostarcza energię odpowiedniej częstotliwości do obciążenia przy możliwie najmniejszych stratach.

Napięcie wyjściowe jest opóźnione względm napięcia sterującego. Czas opadania ![]()

wynika z rozkładu pojemności złącza B i CB. W tym czasie ![]()

maleje od![]()

do ![]()

; następuje narastanie napięcia.

W czasie narastania I napięcie wyjściowe maleje. Czas wzrostu prądu wynika z czasu przejścia nośników przez obszar bazy.

tn- czas magazynowania (wyjścia ze stanu nasycenia)

4.Narysować i omówić przebieg napięcia wyjściowego klucza z tranzyt. MOSFET indukowanym kanałem n w ukł. wspólnego źródła sterowanego napięciem prostokątnym:

Tranzystor unipolarny MOSFET kanałem n indukowanym:

S-źródło D- dren G- bramka B- podłoże K- kanał indukowany

Gdy do bramki doprowadzone jest napięcie ujemne w stosunku do podłoża B, wówczas źródło zostaje oddzielone od D drenu przeciwnie spolaryzowanego zł. PN- stan komutacji. Prąd SD stanowi wówczas pr. Wsteczny jednego ze złączy ma znikomą wartość. Znikomy prąd płynie też przy UGS =0.

Gdy do bramki dopr. napięcie + w stosunku do podłoża wtedy po przekroczeniu napięcia progowego UT=-5V powstaje przy powierzchni warstwa inwersyjna- indukowany kanał, który po doprowadzeniu napięcia polaryzacyjnego SD umożliwia przepływ prądu od S do D. Ze wzrostem UGS prą d drenu wzrasta

Stała czasowa decyduje o czasie włączenia lub wyłączenia kanału . Po ustaleniu się UG następuje etap przełączania tranzystora- ustalenie się UD. Kondensator rozładowuje się przez zmienną rezystancję kanału.

5.Omówić przebieg charakt. wyjściowych tranzystora MOSFET (dlaczego raz strome raz płaskie)

Tranzystor MOSFET jest to unipolarny tranzystor z izolowaną bramką (najczęściej SiO2)

Charakterystyka wyjściowa:

Zależnie od relacji między napięciami Ut, Uas, Uds tranzystory mogą pracować w dwóch trybach:

nasycenie (płaskie), gdy

nienasycone (strome), gdy

Charakterystyki w zakresie liniowym (nienasycenia), gdy S jest uziemione (Us=0) to ![]()

. W zakresie nasycenia ![]()

β- współczynnik transkonduktancji, zależny od struktury tranzystora, β=µ*Ci*z gdzie: µ-ruchliwość nośników w krzemie; Ci- pojemność warstwy izolatora przypadająca na jednostkę powierzchni z-szerokość kanału

l-długość kanału Ut- napięcie progowe wyznaczone praktycznie jako Usg, przy którym prąd drenu ma określoną wartość

wzmocnienie = transkonduktancja ![]()

-tryb nienasycenia ![]()

-tryb nasycenia ![]()

Konduktancja wyjściowa jest to przewodność kanału, czyli nasycenie ch-ki wyjściowej w określonym punkcie pracy![]()

-tryb nienasycenia ![]()

-tryb nasycenia z def. ![]()

=0, ale ze względu na zjawisko skracania elektrycznej długości kanału ![]()

>0

6.Wyjaśnić pojęcie obciążalności bramek logicznych:

Obciążalność bramek logicznych jest to maksymalna liczba wejść innych układów, które można dołączyć do 1 wyjścia danego układu. Liczba ta zależy od maksym. wartości prądów wyjściowych i wejściowych danego układu i np. dla TTL=10

7.Narysować schemat bramki NAND (NOR) w techn.. CMOS, omówić jej działanie.

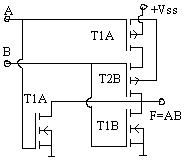

Bramka NAND w ukł. CMOS (pary komplementarne tr MOS).

Gdy na obu wejściach A i B jest stan jedynki logicznej (napięcie bliskie Vss). Oba dolne tranzystory są przewodzące, o górne odcięte i na wyjściu F jest stan „0”. Gdy choć na jednym wejściu jest 0 logiczne powoduje to odcięcie odpowiedniego szeregowego dolnego tranzystora, a przewodzenie górnego. Prowadzi to do pojawienia się stanu „1” na wyjściu.

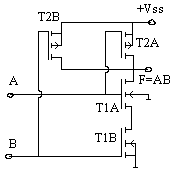

Bramka NOR w układzie CMOS.

Gdy na obu wejściach A i B jest poziom napięcia odpowiadający „0” logicznemu oba górne tranzystory ![]()

i ![]()

są przewodzące, a dolne odcięte. Na wyjściu F mamy „1” logiczną. Gdy choć na jednym wejściu jest „1” logiczna powoduje to przewodzenie jednego z dolnych szeregowych tranzystorów, a odcięcie górnego, co prowadzi do pojawienia się stanu „0” na wyjściu F.

8.Zasada budowy bramek CMOS, właściwości:

Ukł. CMOS zbudowane są par tranzystorów unipolarnych przeciwstawnych kanałem p i n. Ukł. inwertora CMOS jest ukł. wejściowym dla podstawowych bramek logicznych. Gdy na wej, jest 0 to T1 jest zablokowany, a T2 przewodzi na wyj. b panuje nap. Ed, czyli „1” logiczne. Gdy na wej. Jest 1 to T1 przewodzi, a T2 jest zatkany i na wyj. b panuje napięcie 0V. Czyli stan „0” logicznego. Układ CMOS w odróżnieniu od bramek z kanałem jednego typu odznaczają się znacznie krótszymi czasami przełączania (50ns). Stroma ch-ka przejściowa zapewnia znacznie większe marginesy zakłóceń. Bramki CMOS charakteryzują się znacznie większym wzmocnieniem logicznym i większą możliwością realizacji ukł. wielowejściowych, zapewniają poziomy logiczne niezależne od liczby wejść i obciążenia. Podstawową zaletą ukł. CMOS jest znikomy pobór mocy. W obu stanach logicznych przez bramkę nie płynie prąd, gdyż bądź dolne bądź górne tranzystory są odcięte.

Wyszukiwarka