Magistrala ISA (ang. Integrated System Architecture) to historycznie najstarsza magistrala zewnętrzna stosowana w komputerach typu PC. W swojej 8-bitowej wersji była przystosowana do współpracy z procesorem 8088. Wraz z pojawieniem się procesorów 286 opracowano jej wersję 16-bitową, która bez zmian przetrwała do dzisiaj i jest wbudowana w najnowszych nawet płytach głównych do obsługi kart rozszerzających typu ISA. Magistrala ta jest taktowana zegarem o częstotliwości ok. 8MHz, co przy 16-bitowej szerokości daje teoretyczną maksymalną prędkość transmisji ok. 8MB/S. W praktyce prędkość ta jest jeszcze ograniczona protokołami transmisji i wynosi ok. 4MB/S. Złącza magistrali ISA są zawsze w kolorze czarnym. Magistrala ta jest obecnie stosowana do podłączania kart rozszerzeń nie wymagających dużych prędkości transmisji, jak np. karty dźwiękowe, wolniejsze karty sieciowe, itp. Standard ISA posiada 16-bitową, dwukierunkową szynę danych (SD0...SD7, SD8...SD15) i 24-bitową szynę adresową (SA0...SA19, LA17...LA23). Złącze ISA składa się z dwóch sekcji: 62-stkowej, z 8-bitową szyną danych i 36-stykowej, umożliwiającej rozszerzenie szyn danych do 16 bitów. Szyna adresowa (SA0...SA19) umieszczona na 62-stykowej (8 linii danych i 20 linii adresowych) sekcji złącza ISA pozwala zaadresować 1 MB (zwany inaczej zerowym megabajtem) pamięci. Sygnał SMEMW jest aktywny tylko w przypadku zapisu danych do pamięci zawartej w tym obszarze, a sygnał SMEMR - aktywny dla odczytu danych tylko z tego obszaru. Sygnały te mogą być generowane przez mikroprocesor lub przez układy obsługujące transmisję DMA. Linie adresowe SA0...SA19 wraz z liniami LA17...LA23 umożliwiają adresowanie pamięci do 16 MB. Linie L17...L23 wykorzystywane są jako sygnały wyjściowe dekoderów pamięci; sygnały te nie są zapamiętywane w rejestrach. Zapis danych do całego 16-megabajtowego obszaru pamięci możliwy jest przy aktywnym sygnale MEMW, odczyt przy aktywnym sygnale MEMR. Maksymalna przestrzeń adresowa przeznaczona dla portów wejścia/wyjścia magistrali ISA wynosi 64 KB (16 linii adresowych SA). Pierwszych 256 adresów zarezerwowanych jest dla układów znajdujących się z reguły na płycie głównej (rejestry kontrolerów DMA, kontrolerów przerwań, zegara czasu rzeczywistego, itd.). Zapis danych do portu odbywa się przy aktywnym sygnale IOW (Input/Output Write), natomiast odczyt - przy aktywnym sygnale IOR (Input/Output Read). Lina MASTER umożliwia przejecie sterowania zasobami systemu przez urządzenie zewnętrzne. Realizowane to jest poprzez zgłoszenie żądania cyklu DMA linią DRQ, a po akceptacji zgłoszenia (DACK), ustawienie linii MASTER w stan niski. Stan ten powoduje odłączenie od szyn danych, adresowych oraz linii sterujących mikroprocesorem i układów DMA. Sterowanie tymi szynami może być przejęte przez urządzenie zewnętrzne. Sygnał MASTER nie może trwać dłużej niż 15 mikrosekund, gdyż po tym czasie procesor musi wykonać rutynowe odświeżania pamięci DRAM. Sygnał RESET zeruje układy zewnętrzne w trakcie załączania napięć zasilających lub w trakcie zerowania systemu klawiszem RESET. Do złącza ISA doprowadzone są napięcia +5V, -5V, +12V, -12V umożliwiające zasilanie zainstalowanych tam kart. Transmisję w trybie bezpośredniego dostępu do pamięci (DMA) zrealizowano w oparciu o dwa kontrolery 8237A (jak na rysunku) połączone kaskadowo. Jeden kontroler obsługuje transmisje 8-bitowe (kanały 0...3), drugi zaś transmisje 16-bitowe (kanały 5...7). Za pomocą linii DRQ, urządzenie żąda transmisji w trybie DMA. Kontroler DMA akceptuje zgłoszenie transmisji za pomocą linii DACK. Sygnał AEN (generowany przez mikroprocesor) informuje wszystkie urządzenia dołączone do szyn ISA o przejęciu kontroli przez DMA nad szyną adresową. System przerwań zawiera dwa kontrolery 8259 połączone kaskadowo. Układ 1 obsługuje przerwania o numerach od 0 do 7, przy czym przerwanie o numerze 2 (IRQ2) pochodzi od drugiego kontrolera 8259. Układ drugi obsługuje przerwania o numerach od 8 do 15. Sygnały żądania przerwania IRQ0, IRQ1, IRQ8 i IRQ13 generowane są przez układy znajdujące się standardowo na płycie głównej. Poniższa tabela ilustruje priorytety poziomów przerwań wykorzystywanych przez układy znajdujące się na płycie głównej oraz przez urządzenia zewnętrzne.

|

Poszczególne linie tego złącza mają następujące znaczenie:

AEN (ADDRESS ENABLE) - sygnał (generowany przez HLDA mikroprocesora 80286) umożliwia przejęcie kontroli przez sterownik DMA nad szyną adresową.

MAGISTRALA EISA

Standard EISA (ang. Enhanced ISA) powstał jako 32-bitowe rozszerzenie magistrali. Karty rozszerzające EISA mają do dyspozycji oprócz wielu sygnałów sterujących 32 bity systemowej szyny adresowej i 32 bity systemowej szyny danych. Na magistralę zewnętrzną EISA składa się 98 sygnałów ISA oraz 90 nowych linii. Nie wszystkie nowe sygnały są jednoznacznie zdefiniowane, pozostawiono tu miejsce dla specyficznych rozwiązań producentów wysoce wyspecjalizowanych kart. Aby zachować wymóg zgodności z kartami ISA, gniazda EISA mają szczególną konstrukcję, styki gniazd ułożone są na dwóch poziomach. Poziom górny dostarcza wszystkich sygnałów ISA, natomiast poziom dolny położony w głębi EISA. Normalna karta ISA nie może być wsunięta tak głęboko by sięgać nimi dodatkowych styków, uniemożliwiają to poprzeczne zapory. Nie są one jednak przeszkodą dla kart EISA posiadających w odpowiednich miejscach wycięcia. System EISA dysponuje podobnie jak ISA 15 kanałami IRQ. Nowością jest zmiana sposobu wyzwalania przerwań. Standard ISA używał zbocza impulsów co jest metodą bardzo podatną na zakłócenia. EISA wymaga od zgłaszającego przerwanie urządzenia utrzymania aktywnego poziomu sygnału, przekroczenia określonego poziomu napięcia a nie tylko jego wzrostu. 64 bajty pamięci konfiguracji z architektury AT zastąpione zostały 4kB w standardzie EISA. Pamięć ta przechowuje nie tylko informację o konfiguracji płyty głównej ale i o zainstalowanych kartach. W kartach EISA nie ma żadnych przełączników konfiguracyjnych, ani zwór. Konfigurowanie systemu odbywa się programowo. Magistrala pracuje z częstotliwością 8MHz, co daje maksymalną teoretyczną prędkość ok. 32MB/S. W praktyce jednak szybkość ta nie przekracza 5 MB/S. Rozwiązanie to zdobyło sobie pewne uznanie i było stosowane, jednak obecnie jest prawie nie używane. Szyna ta jest zgodna ze standardem ISA, można więc wprowadzać karty wyposażone w szynę ISA do gniazd EISA, co nie oznacza oczywiście że karty ISA będą pracować szybciej w złączu EISA.

MAGISTRALA PCI

Magistrala lokalna PCI (ang. Peripheral Component Interconnent - standard połączeń układów peryferyjnych) została opracowana przez firmę INTEL w roku 1992, z myślą o obsłudze kart wymagających dużych szybkości transmisji (np. kontroler dysków twardych, kart sieciowych, graficznych itd.). Koncepcja PCI polegała na umieszczeniu magistrali pomiędzy magistralą lokalna procesora a magistrala zewnętrzną, zrealizowano to za pomocą tzw. Mostów. Opracowano nowy układ kontrolera magistrali, co pokazuje poniższy rysunek: Magistrala PCI taktowana zegarem o częstotliwości 33 MHz, przesyła dane całą szerokości 32-bitowej szyny, osiągając tym samym maksymalną szybkość transmisji 132 MB/s. Wszystkie współczesne płyty główne wyposażone są w kilka gniazd PCI. Magistrala PCI wyposażona jest w 32-bitową multipleksowaną szynę adresową/danych AD[31:0], taktowaną zegarem CLK o częstotliwości 33 MHz. Procesor transmisji danych wykonany jest w trybie przesyłania seryjnego (ang. Burst). W pierwszym cyklu inicjującym transmisję wystawiany jest adres początkowy, zaś w następnych cyklach przesyłane są dane, przy czym ich ilość nie jest limitowana. Standard PCI wyróżnia dwa rodzaje współpracujących ze sobą urządzeń: urządzenia inicjujące transmisję (inicjatory) i urządzenia docelowe. Transmisję danych rozpoczyna inicjator, który na szynie AD [31:0] wystawia adres urządzenia docelowego, a na liniach C/BE [3:0] - kod rodzaju operacji (przykładowe kody operacji we/wy: 0010 - odczyt danych, 0011 - zapis danych). Inicjator uaktywnia również sygnał FRAME (początek wysyłania ramki). Wybrane urządzenie docelowe odpowiada uaktywnieniem sygnału DEVSEL. W ciągu kolejnych taktów zegara przesyłane są dane, oczywiście tylko wtedy, gdy aktywne będą linie: IRDY - inicjator gotowy, TRDY - urządzenie docelowe gotowe. Jeśli jeden z tych dwóch sygnałów jest nieaktywny, następuje stan oczekiwania. Magistrala PCI została zaprojektowana dla kart zasilanych napięciem 5V i 3.3V. Różnice pomiędzy złączani tych kart przedstawione są na rysunku. Istniej również możliwość zainstalowania w gnieździe PCI karty "uniwersalnej" zasilanej napięciem 5V lub 3.3V - karta taka posiada złącze z dwoma wycięciami. Magistrala PCI wyposażona jest w automatyczną konfigurację - procedury BIOS automatycznie konfigurują każde nowe urządzenie dołączone do magistrali, uwzględniają przy tym parametry konfiguracyjne innych kart dołączonych wcześniej do magistrali.

Specyfikacja PCI2.2 dopuszcza przyspieszenie zegara szyny do 66 MHz i zwiększenie jej szerokości do 64 bitów. Z 64-bitową szyną PCI taktowaną zegarem 66 MHz spotykamy się obecnie często w płytach głównych o przeznaczeniu serwerowym. W serwerowych zastosowaniach kariere robi obecnie PCI-X, zgodne wstecz rozwinięcie standardu PCI, pozwalające na zastosowanie 64 i 32 bitowych kart w szynie taktowanej zegarem do 133 MHz. Jednak jest to rozwiązanie zbyt kosztowne. |

DMA Gdy urządzenie I/O zgłasza potrzebę transmisji, zadaniem kontrolera DMA jest zapewnienie mu wolnej magistrali i możliwości komunikacji po niej z pamięcią. Uaktywnienie linii DREQ na pewnym kanale stanowi zgłoszenie urządzenia I/O dołączonego do tego kanału. Gdy kontroler DMA jest gotowy (nie zajmuje akurat magistrali), zgłasza procesorowi sygnał HRQ żądania zawieszenia się, czyli odłączenia od magistral. Gdy procesor zawiesi się, potwierdza to sygnałem HLDA, a wówczas na tym samym kanale pojawia się potwierdzenie gotowości DMA na linii DACK. Następuje transmisja. Po jej zakończeniu DMA wyłącza sygnał HRQ, procesor wychodzi z zawieszenia i wyłącza HLDA, a wówczas DMA wyłącza DACK. Teraz może zostać przyjęte nowe zgłoszenie sygnałem DREQ. Żądanie transmisji na pewnym kanale DMA może być zgłoszone także programowo, jeżeli jej inicjatorem jest procesor. Do tego celu służy port o nazwie rejestr żądań DMA. Na kilku bitach zapisuje się w nim numer kanału transmisjiora z na jednym bicie ustawia żądanie. Ustawienie żądania wstawia układ I/O w kolejkę DMA. Jest ona realizowana według priorytetu kanałów. W czasie pracy kontroler DMA musi wskazać pamięci adres początku zwartego obszaru, gdzie transmitowane dane będą zapisywane lub odczytywane. Transmisja ta odbywa się w trybie seryjnym pracy magistral (ang. burst). Ponadto kontroler DMA musi wystawiać sygnały sterujące zapisem lub odczytem pamięci (MEMW, MEMR) i urządzenia I/O (IOW, IOR). Tc sygnały będą decydowały o kierunku transmisji, ustawienie MEMR i IOW da transmisję z pamięci do urządzenia I/O, zaś ustawienie MEMW i IOR spowoduje transmisję z urządzenia l/O do pamięci. Wstępnym etapem pracy DMA jest programowanie go, czyli ustawienie trybu i wielkości transmisji oraz ew. rejestru żądań. W czasie transmisji układ DMA zlicza dane przesyłane i przerywa pracę, jeśli liczba ta osiągnie wcześniej zaprogramowaną wartość. Po zakończeniu pracy kontroler DMA sygnalizuje koniec pracy sygnałem EOP. DMA zapewnia cztery podstawowe tryby pracy: spoczynkowy, pojedynczy, blokowy i na żądanie. W trybie spoczynkowym DMA oczekuje na zgłoszenia sygnałów DREQ lub sygnału programowania CS#. W trybie pojedynczym DMA realizuje transmisję pojedynczego słowa i wówczas wyłącza sygnały sterujące pamięcią, urządzeniem I/O, sygnał HRQ i zgłasza koniec operacji (EOP). Nowa transmisja wymaga ponownego zgłoszenia DREQ. W trybie blokowym DMA zlicza transmitowane słowa i wyłącza sygnały sterujące oraz HRQ po odliczeniu ustalonej z góry liczby słów lub pojawieniu się sygnału przerwania transmisji EOP. W trybie na żądanie DMA transmituje tak jak w trybie blokowym (według licznika lub do pojawienia się EOP), tyle że możliwe jest chwilowe wstrzymanie transmisji. Następuje to, gdy sygnał DREQ zostanie wyłączony lub pojawi się DREQ na kanale o wyższym priorytecie (o niższym numerze kanału). Wówczas nastąpi czasowe wstrzymanie transmisji.

Praca układu DMA składa się z faz inicjacji operacji DMA, realizacji operacji i zakończenia operacji. Pracę tę przedstawimy na przykładzie transmisji bloku 20 KB z. bufora w pamięci RAM zaczynającego się pod adresem 1234H:12345678H na port równoległy LPT1 dołączony do kanału nr 1 DMA. Niech procesor wykonuje aplikację, w której pojawia się potrzeba transmisji bloku danych z pamięci na port LPT1. Wówczas: 1. Inicjacja operacji DMA przez procesor w trybie przerwania programowego procesor programuje kontroler DMA -zapisując w rejestrach stanu i sterowania:tryb pracy DMA (tu blokowy), - liczbę bajtów lub słów do transmisji (tu licznik bajtów zostaje zainicjalizowany na 20 K), -adres początku w pamięci DRAM (tu 1234H:12345678H), - kierunek transmisji (tu odczyt pamięci, zapis urządzenia I/O), ? następnie wstawia żądanie transmisji na kanale DMA nr 1 do rejestru żądań. Jest to równoważne uaktywnieniu linii DREQ1. 2. Realizacja operacji I/O przez DMA ? DMA wystawia procesorowi sygnał HRQ, ? procesor zawiesza się i potwierdza ten fakt sygnałem HLDA, ? DMA przejmuje kontrolę nad magistralami i potwierdza to sygnałem DACK1, ? DMA wystawia na magistralę adres początkowy bloku w pamięci, ? DMA wystawia sygnał odczytu pamięci MEMR i inne sygnały sterujące magistralą pamięci, ? pamięć wystawia daną na szynę danych, ? DMA wystawia sygnał IOW zapisu kontrolera I/O i inne sygnały sterujące magistralą I/O. Jednocześnie zmniejsza licznik transmisji o 1, ? kontroler I/O zapisuje dane z szyny danych do bufora, ? DMA wystawia sygnały sterujące odczytem kolejnych słów pamięci w trybie stronicowania lub seryjnym, ? pamięć wystawia kolejne słowa danych na szynę danych, ? DMA wystawia kolejne sygnały IOW zapisu kontrolera I/O. Jednocześnie za każdym razem zmniejsza licznik transmisji o 1, ? kontroler I/O zapisuje kolejne dane do swego bufora. 3. Zakończenie transmisji Gdy licznik transmisji osiąga wartość 0, przetransmitowana jest zaprogramowana liczba bajtów. Wówczas kontroler DMA: ? wystawia aktywny poziom sygnału EOP, ? zgłasza przerwanie sprzętowe w celu poinformowania procesora (programu użytkowego) o zakończeniu transmisji. Warto podkreślić, że w przedstawionym przykładzie żądanie transmisji nic wyszło od sygnału DREQ, ale zostało zrealizowane programowo przez ustawienie rejestru żądań.

OBSŁUGA UKŁADÓW WEJŚCIA-WYJŚCIA W TRYBIK PROGRAMOWYM Obsługa programowa polega na wykonywaniu programu, który w tak zwanej pętli przepytywania cyklicznie sprawdza zapotrzebowanie kontrolerów l/O na obsługę (odczytując pewien bit statusu, np. RDY w jakimś rejestrze stanu kontrolera l/O). Napotkanie RDY = I oznacza, że kontroler jest gotowy do obsługi (np. jego bufor został już opróżniony), Wówczas wykonywane jest przerwanie programowe obsługi lego kontrolera, który realizuje np. napełnianie bufora nowymi danymi. Taki system obsługi programowej warto stosować, jeżeli urządzenia zewnętrzne są stosunkowo szybkie. Jest on jednak mało efektywny, jeżeli żądania obsługi pojawiają się rzadko. Program przepytujący musi bowiem być wykonywany regularnie, co pewien czas. niezależnie od tego, czy pojawiają się zgłoszenia obsługi, czy leż nic.

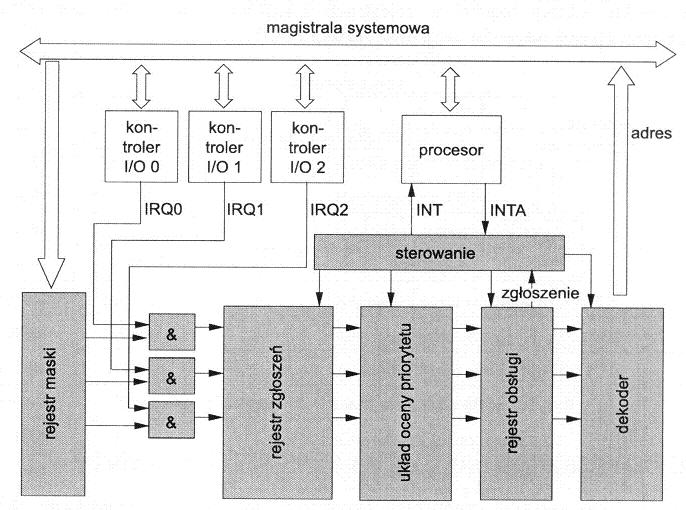

OBSŁUGA UKŁADÓW WEJŚCIA-WYJŚCIA W TRYBIE PRZERWAŃ SPRZĘTOWYCH 1. Na liniach zgłoszenia przerwań IRQO, IRQ1, IRQ2,... utrzymują się zgłoszenia od wszystkich układów I/O, które aktualnie żądają obsługi lub są obsługi- 2. Zgłoszenia mogą zostać zamaskowane bitami rejestru maski (rejestr może być ustawiany z magistrali I/O rozkazami procesora). Jeżeli odpowiedni bit maski jest 0, to zgłoszenie przerwania nie przejdzie przez bramkę AND i nic zostanie zarejestrowane w rejestrze zgłoszeń. 3. Wszystkie niezamaskowane zgłoszenia są w każdym takcie zegara zapisywane w rejestrze zgłoszeń. 4. Spośród nich układ oceny priorytetu wybiera jedno zgłoszenie o najwyższym priorytecie (tj. najniższym numerze linii). Zostaje ono zapisane na odpowiedniej pozycji rejestru obsługi. Koder przekodowuje numer linii rejestru obsługi na numer sytuacji wyjątkowej, czyli adres adr w tablicy przerwań i wystawia ten adres na szynę adresową. 5. Gdy w rejestrze obsługi pojawia się sygnał lub następuje zmiana pozycji z niższego priorytetu na wyższy, układ sterowania otrzymuje sygnał zgłoszenie i wystawia procesorowi sygnał zgłoszenia przerwania INT. 6. Procesor zapamiętuje swój stan na stosie, pobiera z szyny adres adr, w jednym cyklu pamięci odczytuje adres ISR: adr_podpr = Pamięć(adr), ładuje adr_podpr do PC, wystawia potwierdzenie INTA i rozpoczyna wykonanie ISR. Z chwilą nadejścia INTA sterowanie układu przerwań wyłącza INT. 7. Obsługa urządzenia I/O kończy się ostatnim rozkazem podprogramu obsługi przerwań IRET. Wtedy obsłużone urządzenie wyłącza swój sygnał IRQ. Procesor odczytuje ze stosu poprzedni stan i kontynuuje przerwany program (jeżeli był nim podprogram obsługi innego układu I/O o niższym priorytecie, na liniach IRQ będzie aktywne zgłoszenie tego układu i nastąpi zmiana w rejestrze obsługi nie powodująca przerwania).

|

|

|

Wyszukiwarka

Podobne podstrony:

Sprawozdanie(1), Studia, WAT Informatyka 2, semestr IV, systemy wejścia-wyjścia

klawiatury monitory drukarki myszki, Studia, WAT Informatyka 2, semestr IV, systemy wejścia-wyjścia

Zad1, Studia, WAT Informatyka 2, semestr III, Statystyka matematyczna

sprawko z T3, Studia, WAT Informatyka 2, semestr I, Podstawy technologii komputerowych

Zad3, Studia, WAT Informatyka 2, semestr III, Statystyka matematyczna

Zad8, Studia, WAT Informatyka 2, semestr III, Statystyka matematyczna

Zad6, Studia, WAT Informatyka 2, semestr III, Statystyka matematyczna

Zad10, Studia, WAT Informatyka 2, semestr III, Statystyka matematyczna

Zad7, Studia, WAT Informatyka 2, semestr III, Statystyka matematyczna

Zad12, Studia, WAT Informatyka 2, semestr III, Statystyka matematyczna

Zad5, Studia, WAT Informatyka 2, semestr III, Statystyka matematyczna

Zad4, Studia, WAT Informatyka 2, semestr III, Statystyka matematyczna

Spraw-1, Studia, WAT Informatyka 2, semestr II, podstawy elektroniki i elektroniki

Zad9, Studia, WAT Informatyka 2, semestr III, Statystyka matematyczna

Zad2, Studia, WAT Informatyka 2, semestr III, Statystyka matematyczna

Swb-sciaga, Studia, WAT Informatyka, s4 - Swb - systemy wbudowane

sciaga uz2, Studia, WAT Informatyka, s4 - Swk - systemy we-wy komputerów

sciaga uz, Studia, WAT Informatyka, s4 - Swk - systemy we-wy komputerów

sciaga uz3, Studia, WAT Informatyka, s4 - Swk - systemy we-wy komputerów

więcej podobnych podstron