Wykonanie ćwiczenia

Realizacja diodowa funkcji logicznych

A. Realizacja diodowa sumy logicznej (OR)

Przebieg ćwiczenia.

Po zapoznaniu się z budową stanowiska i analizie schematu określono:

do budowy układu należy wybrać oporności o skrajnych wartościach co pozwoli nam na uzyskanie rozbieżności w działaniu układu, przyjęto R1 = 470 Ώ 220 kΏ i R2 = 220 kΏ .

w celu poprawnego działania układu, z uwagi na przepływ prądu w diodach (kierunek przewodzenia) należy użyć napięcia o potencjale ujemnym.

po połączeniu układu wg schematu dokonano pomiarów napięcia na wyjściu w różnych jego stanach jego wejść, wyniki pomiaru wpisano do tabeli,

zmieniono wartość oporności i ponownie dokonano pomiary

dokonano pomiaru napięć zasilających,

wszystkie wyniki wpisano do tabel

przyjęto następującą konwencję napięciowo logiczną 0V - 0; -6V - 1

Dokonano następujących zapisów logicznych :

Układ A |

|

Układ B |

||||||||||||||

A |

B |

X |

|

A |

B |

X |

||||||||||

0 |

0 |

0 |

|

0 |

0 |

0 |

||||||||||

0 |

1 |

1 |

|

0 |

1 |

0 |

||||||||||

1 |

0 |

1 |

|

1 |

0 |

0 |

||||||||||

1 |

1 |

1 |

|

1 |

1 |

1 |

||||||||||

UA [V] |

UB [V] |

UR1 [V] |

UR2 [ V] |

|

A |

B |

X |

470 |

220k |

|||||||

0 |

0 |

0 |

0 |

|

0 |

0 |

0 |

5,3 |

5,3 |

|||||||

0 |

-6 |

2,7 |

4,8 |

|

0 |

1 |

1 |

|

||||||||

-6 |

0 |

2,9 |

5,1 |

|

1 |

0 |

1 |

|

||||||||

Układ A realizuje funkcję sumy logicznej OR. Układ B realizuje funkcję iloczynu logicznego AND.

Analizując wyniki pomiarów tych samych układów z opornikami o różnych wartościach można stwierdzić, że przy realizacji sumy i iloczynu logicznego lepsze są oporności o dużych wartościach.

Po zmianie polaryzacji napięć w układzie będzie występował prąd o bardzo małym napięciu (kierunek zaporowy diody) . Układ będzie miał tylko jeden stan logiczny - 0.

Po zmianie konwencji napięciowo logicznej na przeciwną układ A będzie realizował funkcje iloczynu logicznego a układ B sumy logicznej.

Realizacja tranzystorowa funkcji logicznych

2.1 Realizacja tranzystorowa negacji logicznej (NOT)

Funktor NOT, ma za zadanie podawać na wyjściu zanegowane wartości sygnału wejściowego (np.: wej=0 to wyj=1). Zakłada się, że układ jest stabilny logicznie, jeżeli szerokość stanu „0” ma się do szerokości stanu „1” jak 1:2 (gdzie szerokość oznacza wartość napięcia), w przypadku żądanej charakterystyki, gdy napięcie maksymalne na wyjściu wynosi 9V, szerokość przedziału stanu „0” powinna być od <0-3)V a „1” od (3-9>V. Żądaną charakterystykę naszkicowano na rys. instr.

- zestawiono układ według schematu.

- y a wyniki wpisano do tabel

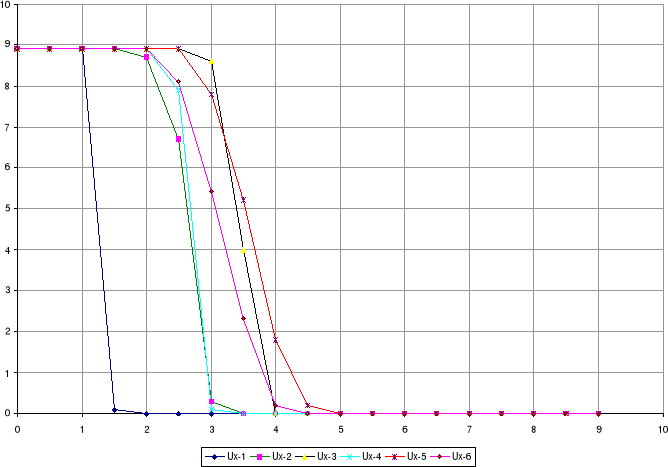

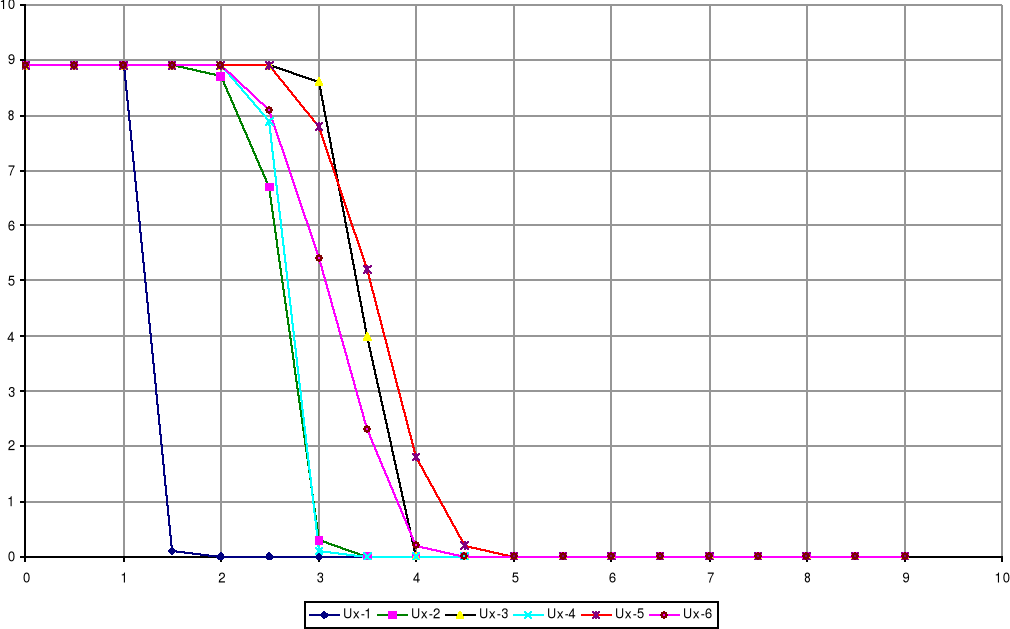

Ustalono początkowe wartości oporników Ra=Rb=Rc=12 [kΏ] i wykonano pomiary wartości Ux dla zmienianych (po jednym) wartości Ra,Rb,Rc .Zdjęto pięć pozostałych charakterystyk. Wyniki zapisano w tabeli. Uzyskane charakterystyki przedstawiono na wykresie.

Analiza wyników

- zestaw 1, nie spełnia warunku gdyż „0” jest tylko do 1.5V . Układ jest przesterowany. Aby to zmienić, należy zmniejszyć napięcie między bazą i emiterem co można uzyskać, zwiększając Ra lub zmniejszając Rb.

- zestaw 2, Ra zwiększono, pozostałe oporniki bez zmian

charakterystyka odpowiada przewidywaniom, strefa „0” przesunęła się w kierunku większych wartości (3V ) i poszerzyła się strefa zmiany sygnału (2 V)

- zestaw 3, Ra jak w zestawie 1, Rb- zmniejszono.

charakterystyka przesunęła się w stronę większych wartości napięcia (do około 4V), strefa zmiany sygnału (2 V)

- zestaw 4- Ra jak w zestawie 1, Rb- zwiększono do 1/3 wartości Ra

Strefa „O” zawęziła się do 3V, strefa zmiany sygnału zwęziła się do 1,5 V.

Zestaw 5: Ra jak w zestawie 1,Rb jak w zestawie 4, Rc zmniejszono

Strefa „O” rozszerzyła się do 4,5 V

zestaw 6: Ra jak w zestawie 1,Rb zwiększono o 1kΏ, Rc jak w zestawie 5

Strefa „O” zawęziła się do 4,5V.

Optymalnym zestawem jest zestaw nr 4 .Zmiana sygnału następuje w pobliżu ustalonej wartości 3V a strefa zmiany sygnału jest najwęższa ze wszystkich i wynosi 1.5 V.

2.2 Badanie funktorów NOR (negacja sumy) i NAND (negacja iloczynu)

Po połączeniu układów według schematu przeprowadzono pomiary napięcia wyjściowego przy różnych stanach wejść badanych układów. Wyniki realizacji funkcji logicznych przedstawiono w tabeli.

Układ 1 |

|

Układ 2 |

||||||

A |

B |

C |

X |

|

A |

B |

C |

X |

0 |

0 |

0 |

1 |

|

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

|

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

|

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

|

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

|

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

|

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

|

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

|

1 |

1 |

1 |

0 |

Układ 1 realizuje negację sumy NOR a układ 2 negację iloczynu NAND.

Wyszukiwarka