Image141

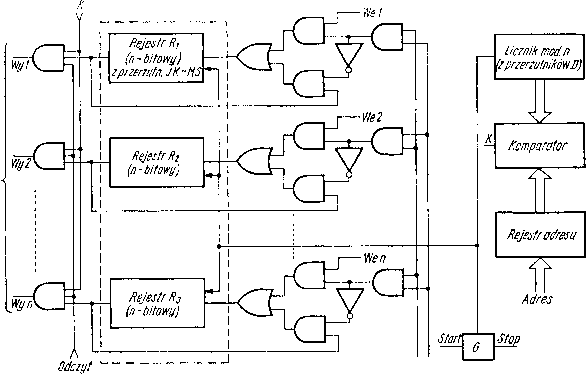

Na rysunku 4.88 przedstawiono schemat ideowy pamięci szeregowej, zbudowanej z rejestrów przesuwających. W stanie początkowym rejestry przesuwające i licznik modulo n są wyzerowane. Zapis informacji wejściowej pod wskazany adres następuje wówczas, gdy K = 1 i na szynę „Wpis” podany jest sygnał 1. Odczyt informacji wystąpi wówczas, gdy K = 1 i na szynę „Odczyt” podany jest sygnał 1. Tego typu pamięci są wolne w działaniu, ale wymagają małej liczby elementów do ich budowy.

JL RWplsK

Rys. 4.88. Pamięć zbudowana z rejestrów szeregowych

Schemat ideowy pamięci o pojemności 8 słów 8-bitowych, z możliwością równoległego wprowadzenia i szeregowego wyprowadzania danych przedstawiono na rys. 4.89. Zapis informacji pod wskazany adres nastąpi wówczas, gdy na wejście 0 dekodera 1 podany zostanie sygnał 0. Podanie sygnału 0 na wejście D dekodera II powoduje uruchomienie generatora grupy 8 impulsów, powodujących szeregowe wyprowadzenie informacji z rejestru o żądanym adresie. Informacja nie może być jednocześnie zapisywana i odczytywana.

Na rysunku 4.90 przedstawiono układ, który umożliwia szeregowe wprowadzenie 16-bitowych słów w ten sposób, że pierwsze słowo zostaje wprowadzone do rejestru R, następne zaś pojawia się na wyjściu Wy2, przy czym kolejne bity tego słowa pojawiają się jednocześnie z bitami słowa pierwszego, wyprowadzanego teraz z rejestru R (IPyi). Układ może być wykorzystywany przy dwukrotnym przesyłaniu informacji i następnie kontrolowaniu, czy są one identyczne.

151

Wyszukiwarka

Podobne podstrony:

Image100 Na rysunku 4.22 przedstawiono schemat ideowy bramki I-LUB-NIE realizującej funkcję: F= AB+C

Image145 Na rysunku 4.95 przedstawiono schemat ideowy wykorzystania rejestru 198 jako licznika pierś

Image146 Wyjścia Na rysunku 4.98 przedstawiono schemat ideowy układu licznika Johnsona mod. 16 zbudo

Image125 Na rysunku 4.68 przedstawiono schemat logiczny czterobitowego rejestru przesuwającego, zbud

Image136 Na rysunku 4.82 przedstawiono przykład rozwiązania pamięci typu RAM, zbudowanej z rejestrów

Image257 Na rysunku 4.280 przedstawiono schemat ideowy układu, umożliwiającego realizację operacji X

Image274 Na rysunku 4.305 przedstawiono schemat ideowy kaskadowego połączenia trzech programowanych

Image517 Na rysunku 4.658 przedstawiono schemat ideowy translatora sygnałów, w którym czasy narastan

Image159 Na rysunku 4.115 przedstawiono organizację pamięci o pojemności 16 słów czterobitowych. Jeś

Image150 Na rysunku 4.102 przedstawiono dwa przykłady rejestrów liniowych zawierających cztery przer

więcej podobnych podstron