Image152

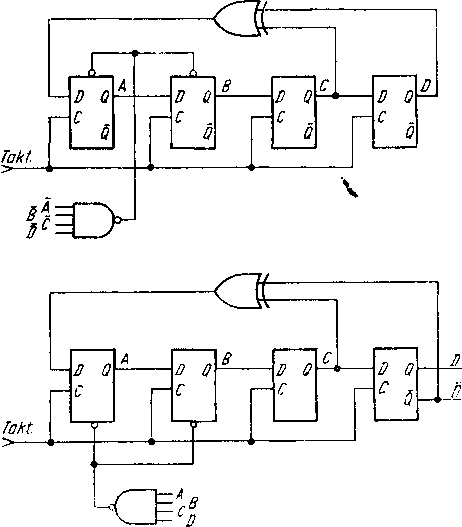

Rys. 4.104. Rejestr generujący ciągi pseudolosowe z samoczynnym likwidowaniem stanów zabronionych

Takt >

B C B

|

n Q |

X |

D G |

X |

b a |

X |

B 0 | |

|

c |

C |

c |

C | ||||

A B C B

|

B Q |

X |

D 0 |

X |

B Q |

X |

B | ||

|

C |

C |

C |

r |

C | ||||

|

—i |

X |

______L |

! | |||||

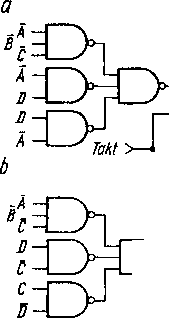

Rys. 4.105. Rejestry liniowe z samoczynnym likwidowaniem stanów zabronionych

162

Wyszukiwarka

Podobne podstrony:

Image122 a Rys. 4.62 Układ służący do równoległego wprowadzania informacji z czterech źródeł do reje

Image124 Rys. 4.66. Układ służący do równoległego wyprowadzania informacji z rejestru Q

Image133 c> ~v~ We C Wg __t- We Rys. 4.79. Rejestry równoległe a) z dwu układów

Image137 Rys. 4.83 Zespół rejestrów buforowych o pojemności 8 słów 8-bitowych 2 rozdzielacza Rys. 4.

Image140 Rys. 4.87. Pamięć składająca się z zespołu rejestrów równoległych150

Image143 rys. 4.91. Impuls „start” powoduje wpisanie informacji do rejestru i odblokowanie bramki B.

Image112 Rys. 4.49. Ilustracja definicji czasów propagacji sygnałów od wejść synchronizujących do wy

Image134 Rys. Zmienne stanu — droga X0— prędkość X7— przyspieszenie w wyróżnionych chwilach czasu: 1

Image147 U(t) Rys. Schemat blokowy układu opisanego równaniem stanu i równaniem wyjścia

Image148 Rys. Schemat blokowy układu gdy wektory U(t)=u(t) i Y(t)=y(t) są jednowymiarowe

Image156 Rys. Schemat blokowy układu gdy sygnały sterujące oddziały wuj ą także na sygnały wyjściowe

Image171 Rys. 4.131. Schemat ideowy generatora 8 słów 32 bitowych Rys. 4.132. Schemat ideowy generat

więcej podobnych podstron