uklady logiczne 3

♦5V

♦5V

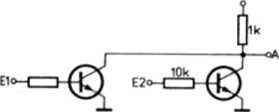

Rys. 3

Bramka NOR z dwóch tranzystorów. Punkt A przejdzie w stan niski tylko wtedy, gdy E1 lub E2 (albo obydwa jednocześnie) beda w stanie wysokim

Wyszukiwarka

Podobne podstrony:

uklady logiczne 2 Rys. 2 Bramka NAND zbudowana z dwóch tranzystorów. Wyjście A przechodzi

uklady logiczne 10 o»5V Rys. 10 Wieloemiterowy tranzystor wejściowy w bramce NAND można przedst

uklady logiczne 8 o*5V Rys. 8 W bramkach z serii 74L zastosowano rezystory o większej rezystanc

099 2 Stabilność 99 2) jeśli pierwiastki były zespolone1, to badane układy były stabilne wtedy i tyl

uklady logiczne 18 Bramko TTl z otwartym kolektorem Bramka CMOS lfco=5V!) =o— Bramka CMOS Bramk

uklady logiczne 1 Rys. 1A Realizacja funkcji OR za pomocą dwóch wyłączników i żarówki. Żarówka A zaś

uklady logiczne 9 Rys. 9 Niskie napięcie nasycenia diod Schottkyego zapobiega w bramkach TTL-S i TTL

Slajd35 (104) -4- + * pOtQC2«rv tt proęromov*orvfr * potoczni %*Qk9 Programowalne układy logiczne:

układy Parametry układów scalonych z bramkami CMOS i TTL Nazwa Liczba wejść Liczba

DSC00025 (25) Aktualnie laboratoryjne układy logiczne piacuya przy szybkościach większych od tOóGH/t

więcej podobnych podstron