Pamięć (część 1)

1

Przedmioty prowadzone w ramach

Programu Rozwoju WSFiZ w Białymstoku realizowane są w ramach

Programu Operacyjnego Kapitał Ludzki, Priorytet IV Szkolnictwo wyższe i nauka, Poddziałanie 4.1.1

Wzmocnienie potencjału dydaktycznego uczelni, współfinansowanego ze środków

Europejskiego Funduszu Społecznego (POKL.04.01.01-00-030/08)

9.

Pamięć (część 1)

Spis treści

Klasyfikacja ze względu na technologię wytwarzania ........................................... 7

9.1 Podstawowe typy i parametry

Zgodnie z założeniami sformułowanymi przez von Neumanna pamięć systemu

komputerowego służy do przechowywania rozkazów i danych. Jeżeli potraktować ją jako czarne

pudełko realizujące określone funkcje, to najważniejszymi parametrami charakteryzującymi

pamięć są:

1. Pojemność;

2. Szybkość;

3. Koszt;

4. Pobór mocy.

Pojemność (ang. capacity) określa ilość informacji, która może być w niej przechowywana.

Mierzona jest najczęściej w bajtach lub słowach. Niezależnie od jednostek, w których wyraża się

pojemność pamięć dzieli się na fragmenty o stałej długości, którym przyporządkowuje się

kolejne liczby całkowite nazywane adresami. W zależności od typu pamięci (patrz dalej)

fragmenty te mogą mieć różną wielkość. W pamięci głównej (tzw. operacyjnej) komputera

fragmenty te mają zazwyczaj długość słowa i nazywane są komórkami. Długość słowa zawiera

się pomiędzy bajtem (dla mikrokomputerów) a ośmioma bajtami (dla dużych instalacji). W

związku z tym wyrażając pojemność pamięci w słowach zwyczajowo podaje się liczbę słów i

wielkość słowa, przy czym liczbę słów poprzedza się mnożnikiem lub jego skrótem, np. Kilo-

(K, mnożnik = 2

10

), Mega- (M, mnożnik = 2

20

), Giga- (G, mnożnik = 2

30

) czy Tera- (T, mnożnik

= 2

40

).

W pamięciach masowych, które są zazwyczaj większe od pamięci operacyjnych, adresuje się

fragmenty o długości od kilkuset do kilku tysięcy bajtów. Dobrym przykładem są tu dyski

magnetyczne, dla których takim fragmentem jest tzw. sektor (patrz rozdział 9.3 Pamięci

Pamięć (część 1)

2

dyskowe). Istotną cechą opisywanego fragmentu jest to, że jest on najmniejszą porcją, którą

można zapisać do lub odczytać z pamięci.

Szybkość pamięci określa jak często można z niej korzystać. Na tą okoliczność podawane są

różne parametry, np. takie jak:

Czas dostępu (ang. access time);

Czas cyklu (ang. cycle time);

Szybkość transmisji (ang. transfer speed).

Czas dostępu jest czasem pomiędzy momentem zażądania dostępu do informacji a chwilą, w

której ta informacja pojawi się na wyjściu pamięci. Dla pamięci operacyjnej wartości czasu

dostępu zawierają się pomiędzy 10 ns a 100 ns.

Czas cyklu jest najkrótszym czasem, jaki musi upłynąć pomiędzy dwoma kolejnymi żądaniami

dostępu do pamięci. W istocie jest to opóźnienie wnoszone przez układy elektroniczne, z których

zrobiona jest pamięć. Zazwyczaj jest to czas nieco dłuższy od czasu dostępu.

Szybkość transmisji wyraża się liczbą bajtów, jaką można przesłać w jednostce czasu

pomiędzy pamięcią a innym urządzeniem. Zazwyczaj jest on stosowany do urządzeń, dla których

fragment jest dużo większy niż słowo. Wynika to z faktu, że w takich urządzeniach najmniejszą

adresowalną jednostką jest wspomniany fragment, czyli zapisuje się go lub odczytuje w całości, a

w takiej sytuacji czas dostępu do pojedynczego słowa jest mniej istotny.

Co do kosztów, to światowy trend wskazuje jednoznacznie, że jednostkowa cena pamięci

nieustannie spada. Najwyraźniej widać to na pamięciach półprzewodnikowych. Rynek jest

jednak mocno zróżnicowany. Z jednej strony występują na nim tanie, ale niezbyt szybkie układy

scalone pamięci półprzewodnikowych o dużych pojemnościach. Z drugiej – szybkie układy

pamięciowe mające niewielkie pojemności i na dodatek wysoką cenę. Stąd w praktyce pamięci

operacyjne realizuje sie przede wszystkim na dużych, tanich ale wolnych układach

półprzewodnikowych. Jednocześnie w celu przyśpieszenia wykonywania programów używa się

jako pomocniczą, współpracującą z główną, niewielką, drogą ale szybką tzw. pamięć

kieszeniową (ang. cache memory). Zagadnienia organizacji współpracy obu rodzajów pamięci

będą omówione w dalszej części tego rozdziału (patrz rozdział 9.2.4 Pamięć kieszeniowa).

Każdy pracujący układ scalony pobiera moc i wydziela ciepło. O ile budowanie odpowiednio

wydajnych zasilaczy nie stanowi (poza kosztami) jakiegoś szczególnego problemu, to szybkie

odprowadzenie ciepła tak, aby utrzymać nominalną temperaturę pracy układu już nim jest.

Problem wielkości poboru mocy, do pominięcia w niewielkich pamięciach, staje się istotnym

problemem dla bardzo dużych pamięci. Łączonych jest wtedy ze sobą dużo układów scalonych i

ilości wytworzonego ciepła mogą być trudne do odprowadzenia. Innym obszarem, gdzie

zagadnienie minimalizacji poboru mocy musi być traktowane jako pierwszoplanowe jest świat

laptopów i komputerów kieszonkowych. Zagadnienie staje się szczególnie krytyczne, jeżeli

rośnie zapotrzebowanie na moc ze strony innych części systemu komputerowego, np. procesora.

Konstruktorzy zmuszeni są do instalowania w systemie komputerowym wielu rodzajów

pamięci. Różne rodzaje pamięci półprzewodnikowych są niezbędne, gdyż jako jedyne dorównują

swoją szybkością procesorowi, a w związku z tym mogą z nim efektywnie współpracować;

szybkie pamięci magnetyczne (głównie dyski) – ponieważ są pojemnymi pamięciami

nieulotnymi (zachowują informację po wyłączeniu napięcia), na których można zrealizować

system plików i przechowywać oprogramowanie (w tym kod systemu operacyjnego) oraz różne

istotne informacje użytkownika; dyski optyczne i pamięci taśmowe – bo są wygodnym

Pamięć (część 1)

3

(pojemnym, przenośnym) narzędziem do sporządzania kopii bezpieczeństwa (ang. backup) oraz

dystrybuowania oprogramowania. Wszystkie one tworzą tzw. hierarchię pamięci. Można

wyróżnić 5 jej poziomów:

1. Pamięć rejestrowa;

2. Pamięć kieszeniowa;

3. Pamięć operacyjna;

4. Pamięć masowa;

5. Pamięć zewnętrzna.

nazwa

pojemność

Czas dostępu

rejestrowa

<1Kb

<1 ns

kieszeniowa

≤144MB

1÷10 ns

operacyjna

512MB÷16GB

10÷100 ns

masowa

>100GB

<10 ms

zewnętrzna

nieograniczona

sekundy÷minuty

Tabela 9.1. Zestawienie parametrów różnych typów pamięci

Pamięć rejestrową tworzą wszystkie rejestry znajdujące się w procesorze. Ponieważ jest ich od

kilku do kilkudziesięciu to jest pamięć o najmniejszej pojemności, ale za to o najkrótszym czasie

dostępu. Poza tym niektóre z rejestrów są dostępne jedynie dla układu sterowania, inne (tzw.

rejestry ogólnego przeznaczenia) są dostępne dla programisty.

Pamięć kieszeniowa jest niezbyt dużą (poniżej 144MB) pamięcią o czasie dostępu rzędu 1÷10

ns. Pełni rolę bufora na podręczne, często używane informacje. Może być umiejscowiona w

procesorze (ang. internal cache; L1, L2) albo poza nim (ang. external cache; L3). Ze względu na

mały czas dostępu istotnie przyśpiesza ona działanie procesora. Wybrane problemy jej

organizacji będą omówione później w tym rozdziale.

Pamięć operacyjna jest główną pamięcią komputera. Jej pojemność może sięgać kilkunastu

Giga bajtów. Ponieważ tendencja jest wzrostowa to można spodziewać się, że granice te mogą

być w bliskiej przyszłości przesunięte w górę. Czas dostępu zależy mocno od zastosowanej

technologii, ale najczęściej jest to 10÷100 ns.

Pamięć masowa jest zwykle realizowana na dyskach magnetycznych. Jej pojemność jest rzędu

setek Mega bajtów dla mikrokomputerów do Tera bajtów dla dużych instalacji. Czas dostępu

zazwyczaj nie przekracza 10 ms. Dyski są przedstawicielami tzw. pamięci nieulotnych, tzn.

takich, w których zapisane informacje nie giną po zaniku napięcia zasilającego.

Odnośnie pamięci zewnętrznych trudno operować parametrami liczbowymi, gdyż te są mocno

zależne od konkretnego typu pamięci. Nawiasem mówiąc ten rodzaj pamięci, w odróżnieniu od

pozostałych, jest wyjątkowo niejednorodny technologicznie. Są tu i streamery, gdzie nośnikiem

jest taśma magnetyczna, ale również dyski optyczne (oba są pamięciami nieulotnymi). Można

tylko powiedzieć, że ich kluczowym parametrem jest czas transmisji. Ich najważniejszą cechą

jest możliwość wymiany nośnika. Ponieważ rozbudowane systemy informacyjne (np. bazy

danych) mogą być przechowywane na wielu nośnikach to daje to tą korzyść, że w danej chwili

używa się tylko potrzebnego nośnika.

Pamięć (część 1)

4

Zestawienie rodzajów i parametrów pamięci znajduje sie w tabeli 9.1 (patrz wyżej)

Ze względu na sposób dostępu do informacji pamięci można podzielić na cztery następujące

klasy:

1. Pamięci z dostępem bezpośrednim;

2. Pamięci z dostępem cyklicznym;

3. Pamięci z dostępem sekwencyjnym;

4. Pamięci z dostępem asocjacyjnym.

Nazwa „dostęp bezpośredni” albo inaczej „swobodny” (ang. RAM – random access memory)

wzięła się stąd, że czas dostępu w tych pamięciach nie zależy od adresu komórki. Nośnikami

informacji w tych pamięciach są tzw. matryce elementów. Zasada działania matryc jest taka, że

każdy element matrycy pamięta jeden bit. Dla n-bitowego adresu i m-bitowego słowa matryca

realizuje 2

n

słów m-bitowych, czyli jest pamięcią o pojemności 2

n

×m. Schemat działania takiej

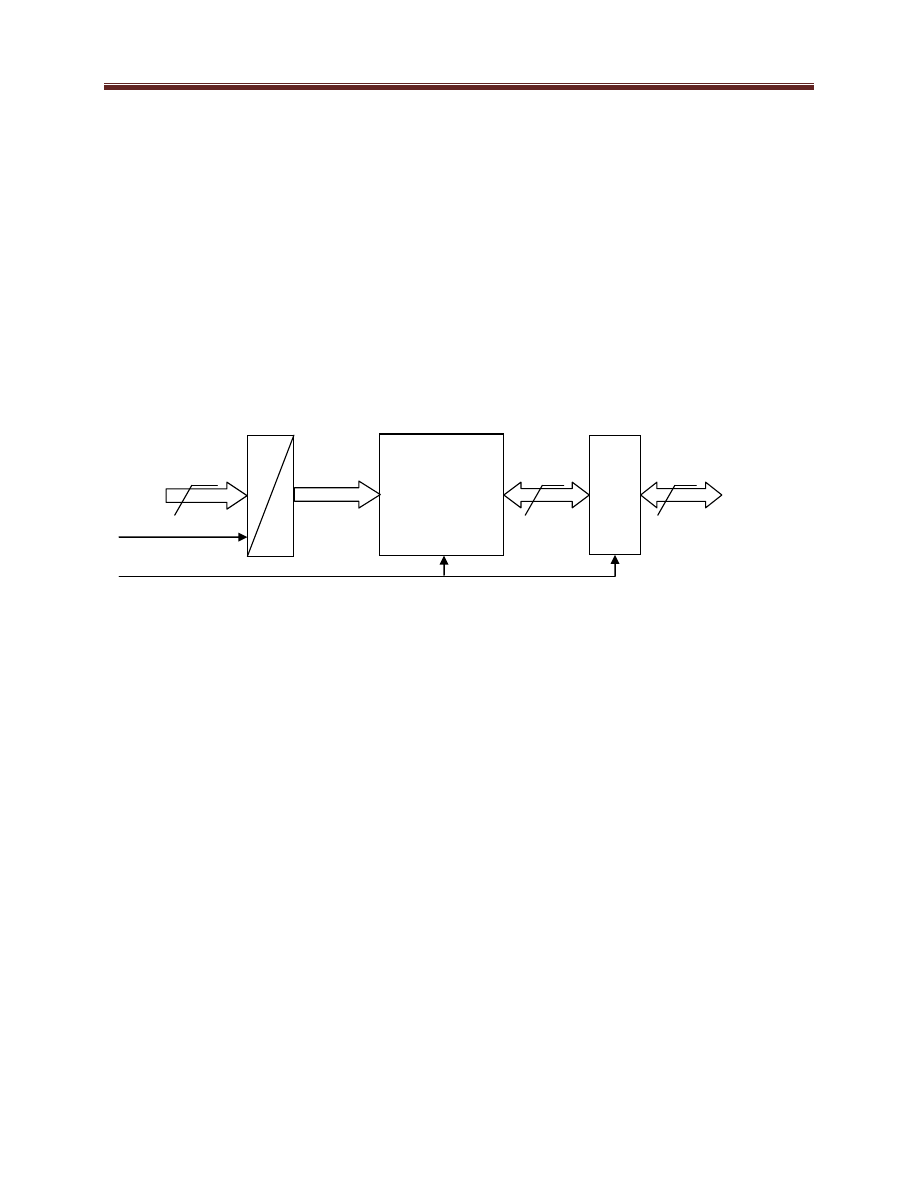

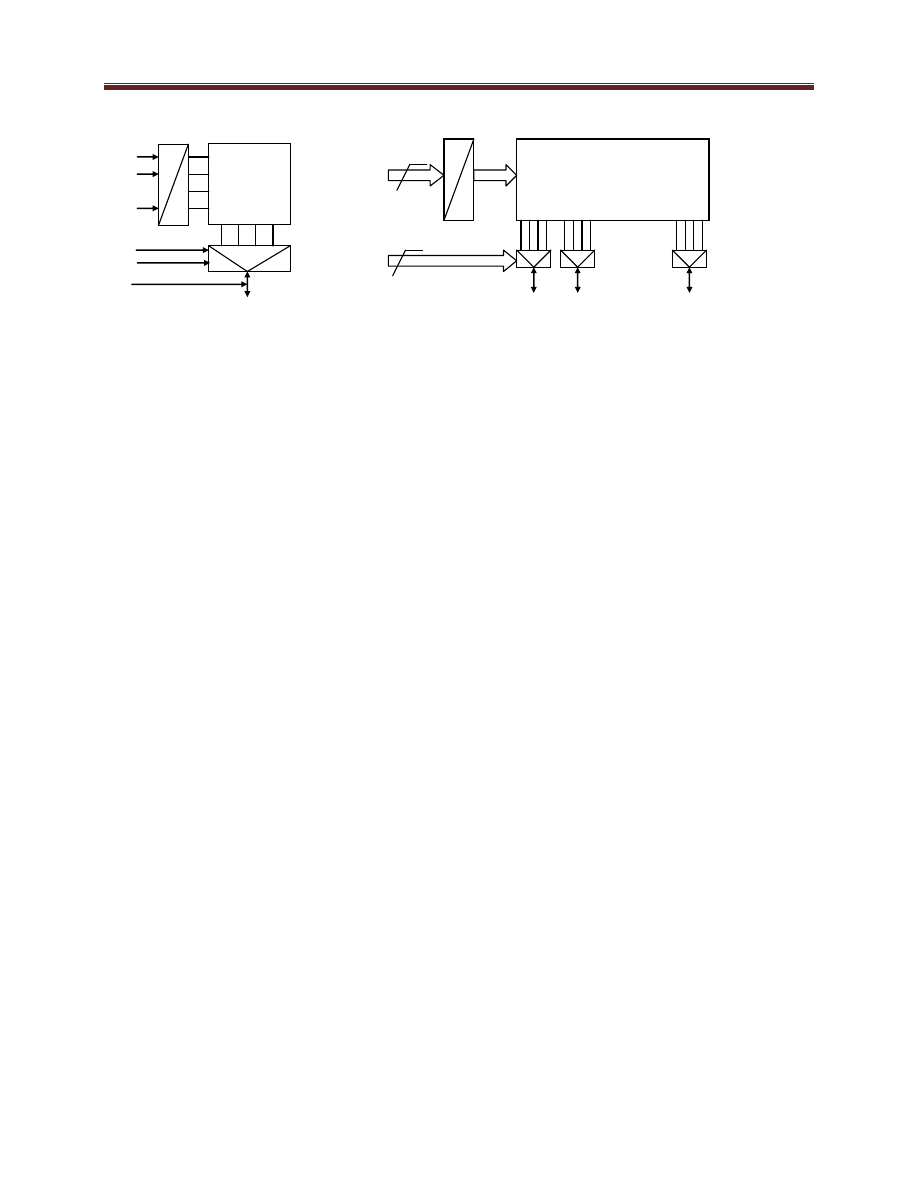

pamięci pokazany jest na rysunku 9.1.

n

Matryca

m

m

Adres

2

n

×m

Bufor

E

R/W

Rysunek 9.1. Schemat pamięci RAM

Jak wynika z rysunku procesor wysyła n-bitowy adres i sygnał E, który uaktywnia wejściowy

dekoder (na rysunku oznaczony jako prostokąt przekreślony ukośną linią). Przekształca on adres

w numer słowa. Linią R/W wysyłany jest sygnał rodzaju pracy: odczyt/zapis (ang. read/write). W

rezultacie, na koniec cyklu odczytu w wyjściowym buforze pojawia się m-bitowe słowo, a na

koniec cyklu zapisu słowo z bufora zostaje zapamiętane pod podanym adresem. Proszę zwrócić

uwagę na sposób określania z ilu bitów składa się szyna. Obu-kierunkowe strzałki między

matrycą a buforem oraz ta na wyjściu są niezbędne, gdyż przy zapisie i odczycie m-bitowego

słowa kierunek przepływu informacji jest przeciwny.

Specjalnym rodzajem pamięci o dostępie swobodnym są pamięci ROM (ang. read only

memory). Są to pamięci jednokrotnie zapisywane i wielokrotnie odczytywane (patrz niżej). Przy

okazji: pamięci RAM są wielokrotnie zapisywane i wielokrotnie odczytywane.

Pamięci z dostępem cyklicznym to przede wszystkim dyski będące przedstawicielem grupy

pamięci z ruchomym nośnikiem. Grupę drugą: pamięci cyklicznych z nośnikiem nieruchomym

tworzą pamięci zbudowane na rejestrach przesuwnych, w których informacja krąży w zamkniętej

pętli sprzężenia zwrotnego. Zasada działania pamięci cyklicznych jest taka, że co pewien

ustalony czas umożliwia ona odczyt lub zapis informacji pod pewien adres nazywany adresem

bieżącym. Porównując ten adres z adresem wejściowym można wychwycić moment zgodności i

wykonać akcję zapisu lub odczytu.

Pamięci z dostępem sekwencyjnym są pamięciami realizowanymi na taśmach magnetycznych

w urządzeniach nazywanych streamerami. Informacja zapisywana jest w kolejności jej

przychodzenia w porcjach nazywanych blokami lub rekordami. Aby odczytać informację należy

Pamięć (część 1)

5

podać numer bloku liczony od początku nośnika, a urządzenie przewinie taśmę do bloku o

wskazanym numerze.

Pamięci asocjacyjne (ang. associative memory) nazywane są również pamięciami

adresowanymi zawartością (ang. content addressable memory) albo pamięciami

skojarzeniowymi. Pamięci takie składają się z pamięci RAM oraz dodatkowej elektroniki

przeszukującej jej zawartość. Przykłady takiej pamięci zostaną opisane dalej w tym rozdziale.

9.2

Pamięć operacyjna

9.2.1

Rodzaje pamięci operacyjnych

Zostaną omówione dwie klasyfikacje pamięci operacyjnych: pierwsza bazuje na różnicach w

sposobie wybierania elementów z matryc, druga – na różnicach w technologii wytwarzania.

Zaczniemy od tej pierwszej.

9.2.1.1 Organizacja matryc

Nośnikami informacji w pamięci operacyjnej są tzw. matryce elementów. Ich ogólna definicja i

sposób działania został opisany wyżej.

Matryca może być tak skonstruowana, że w każdym jej wierszu znajduje się dokładnie jedno

słowo. Wejściowy dekoder zamienia adres na numer słowa, które przy odczycie pojawia się na

liniach wyjściowych, a przy zapisie, korzystając z tych samych linii ustawia wartości bitów w

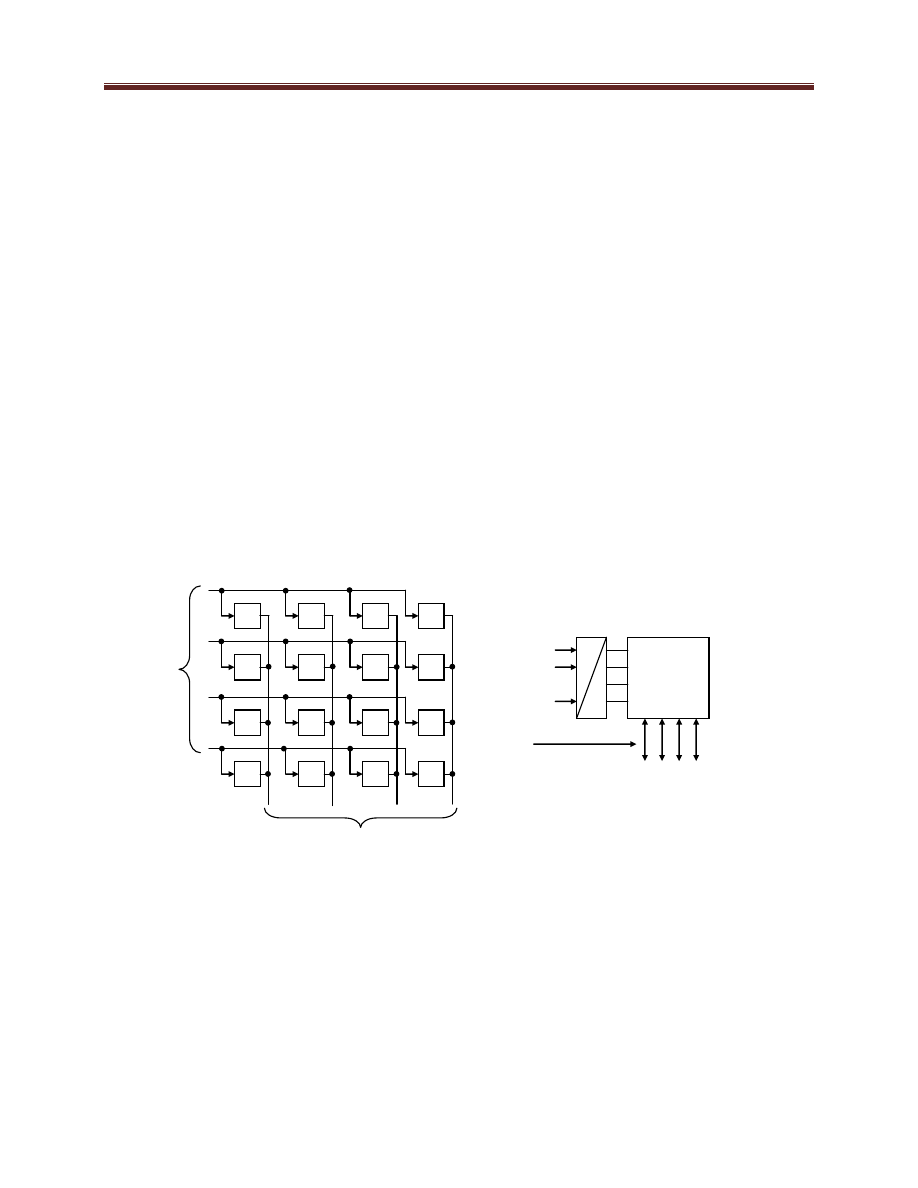

wybranym słowie zgodnie z podanymi na nich wartościami. Na rysunku 9.2a pokazana jest

przykładowa pamięć o takiej organizacji.

a)

b)

a

0

wejścia

a

1

Matryca

wybierające

E

R/W

linie danych

Rysunek 9.2. Pamięć typu 2D: a) matryca; b) układ współpracujący

Jej pojemność wynosi 16 bitów ułożonych w matrycę 4×4 (4 słowa 4-ro bitowe). Wystarczy

określić jedną linię (podać na nią jedynkę) aby wybrać całe słowo. Na rysunku 9.2b pokazany

jest schemat układu współpracującego z opisaną matrycą. W związku z przyjętą organizacją

dekoder wejściowy przekształca 2-bitowy adres (2 bity a

1

a

2

wystarczą, aby ponumerować każde

z 4 słów) w sygnał na dokładnie jednym z 4 swoich wyjść, a mianowicie tym, którego numer jest

zakodowanym binarnie adresem (taki sposób kodowania nazywa się kodowaniem 1 z n, w

naszym przykładzie 1 z 4). Kierunek przepływu informacji na wyjściach układu

współpracującego wynika z realizowanej operacji: odczytu lub zapisu.

Pamięć (część 1)

6

Pamięć z matrycą wyposażoną w jedno wejście wybierające nazywana jest pamięcią z

wybieraniem liniowym lub pamięcią typu 2D. Jej podstawową wadą jest konieczność używania

dekodera o liczbie wyjść równej pojemności pamięci (liczonej w słowach). Przy rozmiarach

pamięci np. 64K daje to dekoder o 16 wejściach i 2

16

wyjściach. Skonstruowanie takiego

dekodera jest trudne.

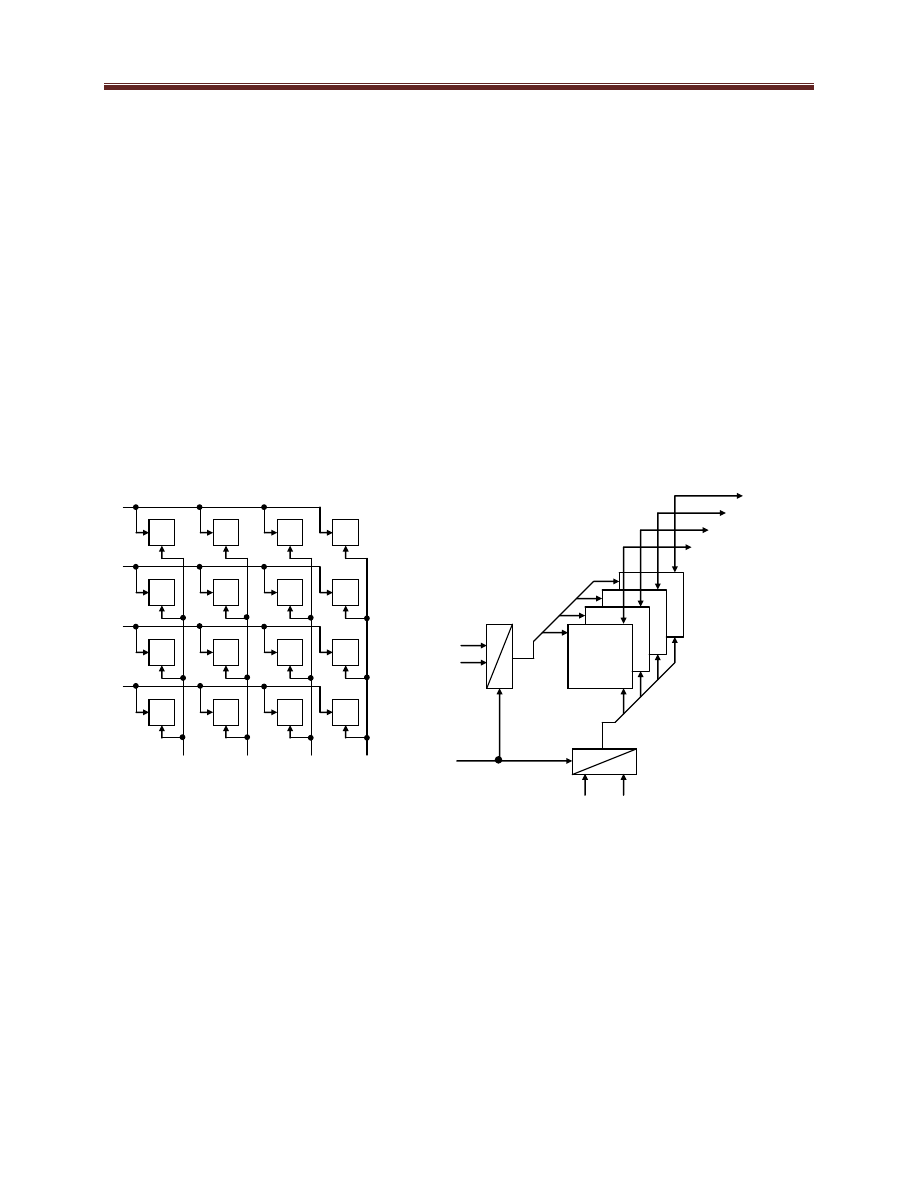

W związku z tym używa się pamięci o dwóch liniach wybierających – pamięć o takiej

organizacji nazywa się pamięcią 3D. Jedna linia wybiera wiersz matrycy, druga kolumnę. W obu

przypadkach sygnałem wybierającym jest jedynka. Matryca zorganizowana jest w płaty

(podmatryce), z których każdy przechowuje jeden bit słowa, tak więc płatów jest tyle ile bitów w

słowie. Na rysunku 9.3a (patrz niżej) pokazana jest organizacja pojedynczego płata dla pamięci

16×4 (16 słów 4-ro bitowych).

Z 4 bitów adresu 2 (a

0

a

1

) wybierają wiersz, a pozostałe dwa (

a

2

a

3

) kolumnę.

Przy typie 3D i rozmiarach pamięci 64K potrzebujemy dwa dekodery o 8 wejściach i 2

8

wyjściach. Są one prostsze do skonstruowania niż dekoder o 2

16

wyjściach niezbędny przy

realizacji pamięci o takiej samej pojemności, ale typie 2D. Ceną, która płacimy jest wydłużenie

czasu dostępu ze względu na wydłużenie czasu dekodowania.

a)

b)

linie

danych

a

0

Płat

a

1

4×4

E

a

2

a

3

Rysunek 9.3. Pamięć typu 3D: a) płat; b) układ współpracujący

Istnieje rozwiązanie pośrednie, tzw. typ 2½D. Tak jak w typie 2D jedna linia wybiera 1 wiersz,

ale do słowa wyjściowego przechodzą z tego wiersza tylko wybrane kolumny (np. co piąta licząc

od pierwszej albo co piąta licząc od drugiej albo co piąta od trzeciej albo co piąta od czwartej).

Wyboru dokonuje się za pomocą multiplekserów, z których każdy sterowany jest tą sama częścią

bitów adresu. Mamy więc jedną matrycę, a na jej wyjściu tyle multiplekserów ile bitów w słowie,

a każdy z nich wybiera po jednym, kolejnym bicie do słowa wyjściowego. Na rysunku 9.4a

pokazana jest matryca 2½D dla pamięci 16×1, a na rysunku 9.4b – 1K×8 (patrz niżej).

Pamięć (część 1)

7

a)

b)

a

0

7

a

1

Matryca

adres

Matryca

128×64

E

a

2

3

a

3

adres 1 2 .... 8

R/W

Rysunek 9.4. Pamięć typu 2½D: a) 16×1; b) 1K×8

Obliczenie parametrów dla pamięci z rysunku 9.4b wymaga nieco arytmetyki. Zauważmy, że

w ogólności, jeżeli mamy skonstruować matrycę dla 2

n

słów po 2

m

bitów w słowie, to istnienie

matrycy kwadratowej jest możliwe jeżeli n+m jest parzyste. Wtedy mamy m+n = 2∙p. Pojemność

matrycy wynosi 2

n

∙2

m

= 2

n+m

=2

2∙p

i istnieje pierwiastek z tej liczby równy 2

p

, który jest

jednocześnie liczbą wierszy (l) i kolumn (k) poszukiwanej matrycy kwadratowej. W naszym

przykładzie matryca liczy 1K=2

10

słów 8=2

3

bitowych, czyli n=10, m=3, i m+n=13, co oznacza,

że matryca kwadratowa nie istnieje i trzeba konstruować matrycę prostokątną. Liczba wierszy

wynosi l = 2

10

/2

3

=2

7

=128. Ponieważ k∙ l = 2

10

to k = 2

10

/l = 2

10

/2

7

= 2

6

= 64. Pamięć ma słowa 8-

bitowe, co oznacza, że potrzeba 64/8 = 8 multiplekserów wybierających na wyjściu 8 jego bitów.

Na zakończenie tej części należy podnieść ponownie kwestię długości słowa pamięci. Ze

względu na możliwość powstawania przekłamań (zjawisko polegające na tym, że słowo zapisane

i odczytane różnią się od siebie) powodowanych przez niewłaściwe poziomy napięć albo zbyt

duże natężenie promieniowania stosuje sie układy detekcji i korekcji takich przekłamań.

Najpopularniejszą metodą detekcji błędów są tzw. bity parzystości. Metoda polega na tym, aby

przy zapisie dopisać do każdego słowa bit z ustawioną jedynką, jeżeli liczba jedynek w słowie

jest parzysta i bit z zerem - jeżeli jest nieparzysta. Jeżeli przy odczycie wykona się identyczną

operację, to porównanie wartości odczytanego i obliczonego bitu parzystości pozwala na

wykrycie przekłamań na nieparzystej liczbie bitów słowa. Jedną z popularniejszych metod

detekcji i korekcji są tzw. kody CRC, które opierają się również na dopisywaniu do każdego

słowa dodatkowych bitów. W obu przypadkach długość słowa ulega zmianie, a z nią zmienia sie

pojemność całej pamięci. Stąd operując długością słowa pamięci należy upewnić się, czy w

podawanej liczbie zostały uwzględnione bity realizujących opisane wyżej cele.

9.2.1.2 K

lasyfikacja ze względu na technologię wytwarzania

Druga klasyfikacja pamięci opiera się o różnice w technologii wytwarzania. Omówione

zostaną dwa podziały: pierwszy dotyczy tzw. pamięci stałych (nazywanymi również pamięciami

„tylko do odczytu”) ROM (ang. read only memory) wyróżniających się swoimi własnościami na

tle wszystkich innych pamięci półprzewodnikowych, które na tą okoliczność nazywa się

nieprecyzyjnie pamięciami RAM. Podział drugi dotyczy wyłącznie pamięci RAM. Wyróżnia się

wśród nich pamięci statyczne SRAM (ang. static RAM) oraz dynamiczne DRAM (ang. dynamic

RAM).

Pamięci ROM, pomimo że są pamięciami półprzewodnikowymi zachowują swoją zawartość

po wyłączeniu napięcia zasilającego (są pamięciami nieulotnymi). Ta cecha oraz duża (w

porównaniu np. z pamięciami dyskowymi) szybkość działania zadecydowała o używaniu ich do

Pamięć (część 1)

8

przechowywaniu istotnych składników systemu operacyjnego (np. BIOSu). Zaprezentowana

poniżej klasyfikacja typów pamięci ROM podana została w ujęciu historycznym, od typów

powstałych najwcześniej do typów nowszych. Pozwala to prześledzić rozwój technologii ze

świadomością, że niektóre z typów nie są już używane.

MROM (ang. maskable ROM) – zawartość tych pamięci ustalana jest w procesie produkcji

przez stosowanie odpowiednich masek (stąd nazwa). Maski są sposobem na kształtowanie

pożądanych cech funkcjonalnych układów scalonych. Jest to najtańszy rodzaj pamięci ROM

(przy założeniu odpowiednio długiej serii produkcyjnej).

PROM (ang. programmable ROM) – zawartość tej pamięci można zaprogramować ale

można to zrobić tylko raz (proces programowania niszczy nieodwracalnie pewne połączenia

wewnętrzne pamięci). Obecnie ten typ nie jest używany.

EPROM (ang. erasable ROM) – pamięć wielokrotnie programowalna. Poprzednią

zawartość można skasować przez naświetlenie kości pamięci promieniami UV. Można to

zrobić po uprzednim wyjęciu kości z komputera. Obecnie ten typ jest używany sporadycznie.

EEPROM albo E

2

PROM (ang. electrically erasable PROM) – pamięć kasowana i

programowana w drodze podawanie na jej wejścia odpowiednich sekwencji sygnałów. Proces

ten może przebiegać bez konieczności wyjmowania kości z komputera. W ten sposób można

np. instalować nowe wersje BIOSa.

Warto wspomnieć o pamięci typu NVRAM (ang. non volatile RAM). Jest to połączenie

pamięci RAM z EEPROM. W tym typie pamięci można na żądanie przepisać zawartość pamięci

RAM do EEPROM. Czas tej operacji jest wprawdzie długi (kilkanaście ms) ale uzyskujemy

bardzo wygodną możliwość przechowania przez dowolnie długi czas określonych, wcześniej

wypracowanych wartości. Dobrym przykładem zastosowań są tu parametry konfiguracyjne, z

których korzystamy przy włączaniu systemu komputerowego, a które od czasu do czasu

zmieniamy zgodnie z naszymi potrzebami.

Czas dostępu dla pamięci typu EEPROM jest rzędu 100 – 200 ns. Mogą być one wyposażone

w mechanizm pozwalający na wprowadzanie tzw. stanu wyłączenia (ang. standby power). W taki

stan można wprowadzić układ, kiedy nie jest realizowany ani zapis ani odczyt. Wtedy pobór

mocy może spadać w nim nawet 100–krotnie w stosunku do mocy pobieranej w stanie

aktywnym.

Przejdźmy do podziału na pamięci statyczne SRAM oraz dynamiczne DRAM. Pamięci

statyczne SRAM są to szybkie, drogie, ale o niezbyt dużych pojemnościach, za to o dużym

poborze mocy pamięci półprzewodnikowe. Pojedynczy element takich pamięci (tj. element

pamiętający jeden bit) zawiera tzw. przerzutnik. Jest to 2-stanowy układ zbudowany z kilku

tranzystorów, sprzedawany na rynku również jako samodzielny układ, podobnie jak np. bramki

logiczne. To właśnie wysoki pobór mocy jest powodem problemów ze zbudowaniem układu

SRAM o dużej pojemności. Pamięci SRAM stosuje się wiec tam, gdzie pojemność nie musi być

szczególnie duża, za to wskazana jest jak największa szybkość działania. Takie właśnie

parametry powinna posiadać tzw. pamięć kieszeniowa (ang. cache memory). Problemy

organizacji takich pamięci i ich współpraca z procesorem oraz pamięcią operacyjną zostaną

omówione dalej w tym rozdziale.

Zajmijmy się teraz pamięciami dynamicznymi DRAM. Podstawowym elementem tych pamięci

jest kondensator. Jeżeli jest on naładowany, to taki stan interpretuję się jako bit równy jeden.

Pamięć (część 1)

9

Pobór mocy dla tych pamięci jest mały, a pojemność informacyjna (mierzone ilością bitów)

pojedynczych kości – duża. Szybkość tych pamięci nie jest imponująca – z reguły nie przekracza

100 ns. Ich podstawową wadą jest dosyć szybka utrata zapisanych informacji powodowana

rozładowywaniem się kondensatorów. Odczyt informacji przyśpiesza proces rozładowania. W

związku z tym zachodzi potrzeba okresowego odświeżania (ang. refresh) zawartości pamięci

(typowe wartości okresu odświeżania to 2, 4 lub 8 ms). Jeżeli dla potrzeby oszacowania

częstotliwości odświeżeń założymy, że jest to 1 ms, to mamy:

1 ms/100 ns = 10

-3

/100∙10

-9

= 10

-3

/10

-7

= 10

4

= 10 000;

co oznacza, że akcję odświeżania należy przeprowadzić raz na 10 000 cykli pamięci. Sama akcja

odświeżania polega na odczycie i powtórnym zapisie tej samej informacji. Wymaga to

chwilowego odłączenia procesora od pamięci, przejęcia magistrali przez generator adresów,

który wygeneruje kolejno wszystkie adresy komórek i wymusi na każdej z nich operację odczytu

i ponownego zapisu.

9.2.2

Banki pamięci i ich adresacja

Jak to już powiedziano, pamięci DRAM nie należą do najszybszych. W związku z tym

poszukiwano pozatechnologicznych sposobów poprawienia ich parametrów. Jednym z

powszechniej stosowanym jest podzielenie pamięci na części nazywane bankami, z których

każdy ma parę rejestrów: MAR i MDR pozwalających na niezależny zapis i odczyt.

Rozbicie pamięci operacyjnej na mniejsze banki pozwala po rozpoczęciu operacji zapisu lub

odczytu z dowolnego banku, zainicjować kolejną operację na innym banku nie czekając na

rezultat pierwszej z nich. W oczywisty sposób przyspiesza to pracę. Zysk czasowy przy n

sięgnięciach do adresów rozrzuconych po różnych bankach teoretycznie może sięgać n∙T

c

, gdzie

T

c

oznacza czas cyklu pamięci. Przykład pamięci o architekturze bankowej pokazano na rysunku

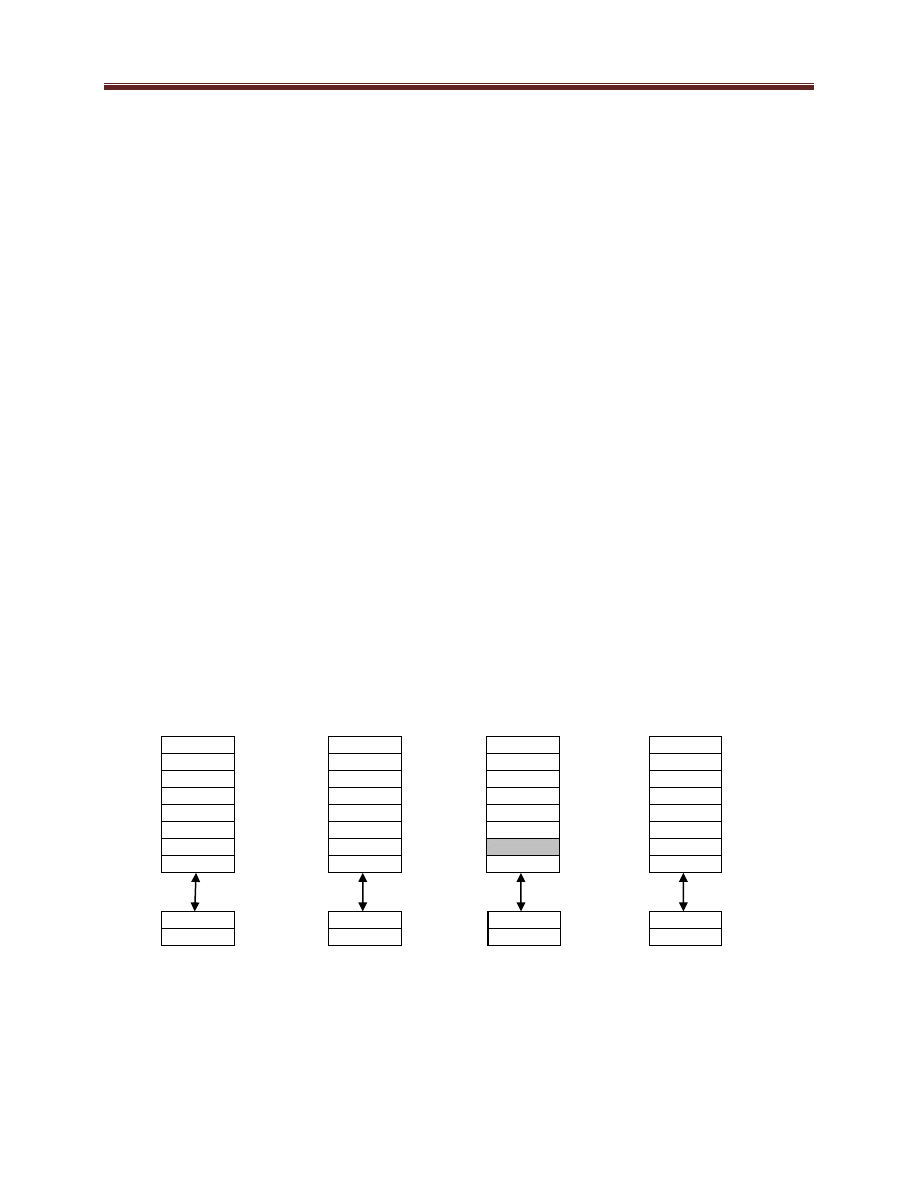

9.5. Są na nim 4 banki po 7 słów w każdym. Adresy takiej pamięci są 5-cio bitowe (przy 32

komórkach pamięci mamy: 32 = 2

5

). Dwa pierwsze bity interpretowane są jako numer banku, a

pozostałe 3 jako numer komórki w tym banku, np. komórka 22 = (10110)

2

oznacza szóstą

komórkę (6 = 110

2

) w banku numer 2 (2 = 10

2

).

bank 0

bank 1

bank 2

bank 3

0

8

16

24

1

9

17

25

2

10

18

26

3

11

19

27

4

12

20

28

5

13

21

29

6

14

22

30

7

15

23

31

MDR 0

MDR 1

MDR 2

MDR 3

MAR 0

MAR 1

MAR 2

MAR 3

Rysunek 9.5. Pamięć o architekturze bankowej

Oczywiście, jeżeli kolejne adresy są z tego samego banku to należy czekać i zysk spada do

zera. Rachunek prawdopodobieństwa wskazuje, że jeżeli wystąpiło sięgnięcie do komórki o

adresie m pamięci to sięgnięcie do komórki o adresie sąsiednim jest dużo bardziej

Pamięć (część 1)

10

prawdopodobne niż sięgnięcie pod inny adres. Oznacza to, że przy architekturze bankowej zyski

będą dużo mniejsze od maksymalnych.

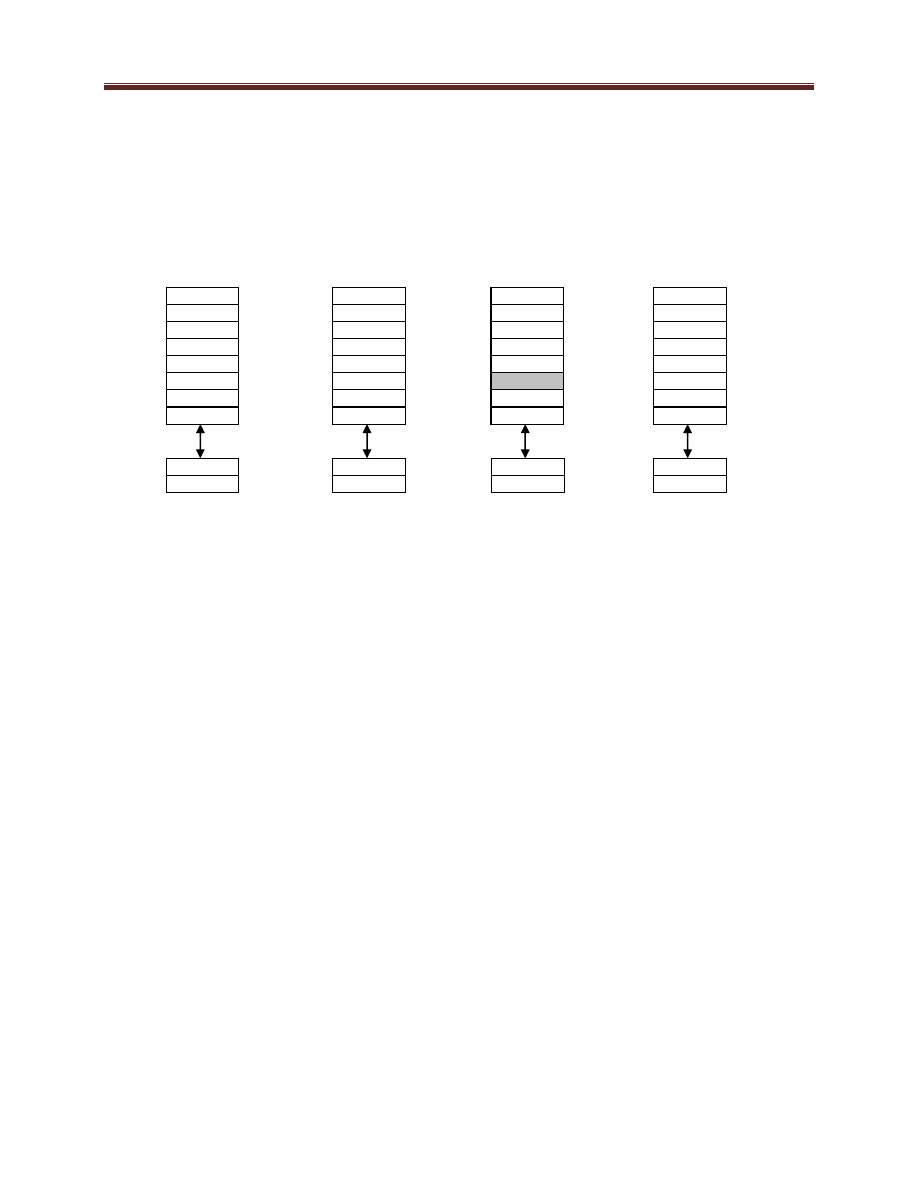

Rozwiązaniem tego problemu jest tzw. architektura z przeplotem. W takiej architekturze

komórki o sąsiednich adresach umieszczane są w różnych bankach. Efekt taki można uzyskać

używając najmniej znaczące bity w adresie jako numer banku. Przykład tego rodzaju pamięci

pokazany jest na rysunku 9.6 (patrz niżej).

bank 0

bank 1

bank 2

bank 3

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

MDR 0

MDR 1

MDR2

MDR3

MAR 0

MAR 1

MAR 2

MAR3

Rysunek 9.6. Pamięć o architekturze z przeplotem

Adresy takiej pamięci są tak jak uprzednio 5-cio bitowe. Dwa ostatnie bity interpretowane są jako

numer banku, a 3 pierwsze jako numer komórki w tym banku, np. komórka 22 = (10110)

2

oznacza piątą komórkę (5 = 101

2

) w banku o numerze 2 (2 = 10

2

).

Document Outline

Wyszukiwarka

Podobne podstrony:

9w Pamiec 3

9w Pamiec 2 v02

9w Pamiec 3

03 Odświeżanie pamięci DRAMid 4244 ppt

wykład 12 pamięć

8 Dzięki za Pamięć

06 pamięć proceduralna schematy, skrypty, ramyid 6150 ppt

Pamięć

PAMIĘĆ 3

Architektura i organizacja komuterów W5 Pamięć wewnętrzna

Test Pamięci Wzrokowej Bentona2 3

więcej podobnych podstron