2. Skrócony opis ogólny rodziny procesorów PIC

na przykladzie procesora PIC 16F84. [3]

2.1 Charakterystyka ogólna

Procesory PIC firmy MICROCHIP

®

sa procesorami posiadajacymi cechy architektury

RISC to oznacza, ze posiadaja zminimalizowana liste rozkazów. Zaleta procesorów PIC (PIC

16FXX) jest przede wszystkim:

??

tylko 35 pojedynczych rozkazów latwych do nauczenia,

??

wszystkie rozkazy wykonywane sa w jednym cyklu (dla zegara taktujacego 10 MHz jeden

cykl = 400 ns, a 1 cykl maszynowy jest równy 4 taktom oscylatora) wylaczajac rozkazy

skoków, które realizowane sa w dwóch cyklach maszynowych,

??

maksymalna czestotliwosc zegara to 20 MHz dla procesorów z pamiecia programu typu

EPROM oraz 10 MHz dla procesorów z pamiecia programu typu EEPROM i FLASH,

??

czternastobitowa dlugosc slowa rozkazu, (dwunastobitowa w PIC 12C508),

??

osmiobitowa dlugosc slowa pamieci danych RAM oraz rejestrów sterujacych,

??

15 rejestrów specjalnych sluzacych do konfigurowania ukladu,

??

osmiopoziomowy stos, (dwupoziomowy dla PIC 12C508),

??

natychmiastowy (bezposredni) i posredni tryb adresowania,

??

osmiobitowy licznik z osmiobitowym podzielnikiem wstepnym,

??

cztery zródla wywolujace przerwania (brak przerwania w PIC 12C508):

1. zewnetrzne, po wystapieniu odpowiedniego zbocza (rodzaj zbocza definiowany

programowo) na nózce RB0/INT procesora,

2. wewnetrzne, poprzez zmiane stanu na jednej z nózek portu B

(porty RB4, RB5, RB6, RB7),

3. wewnetrzne, poprzez przepelnienie TIMER-a ,

4. wewnetrzne, wywolywane gdy zakonczone zostanie programowanie jednej z

komórek pamieci danych w EEPROM-ie.

??

ponad 1.000.000 cykli programowania pamieci danych EEPROM,

??

zachowanie zawartosci pamieci danych EEPROM ponad 40 lat,

??

wykonanie w technologii CMOS,

??

szeroki zakres napiec zasilajacych oraz niewielki pobór pradu (<2mA dla 5V 4Mhz, 15

?

A

dla 2V 32kHz oraz ponizej 1

?

A w stanie uspienia).

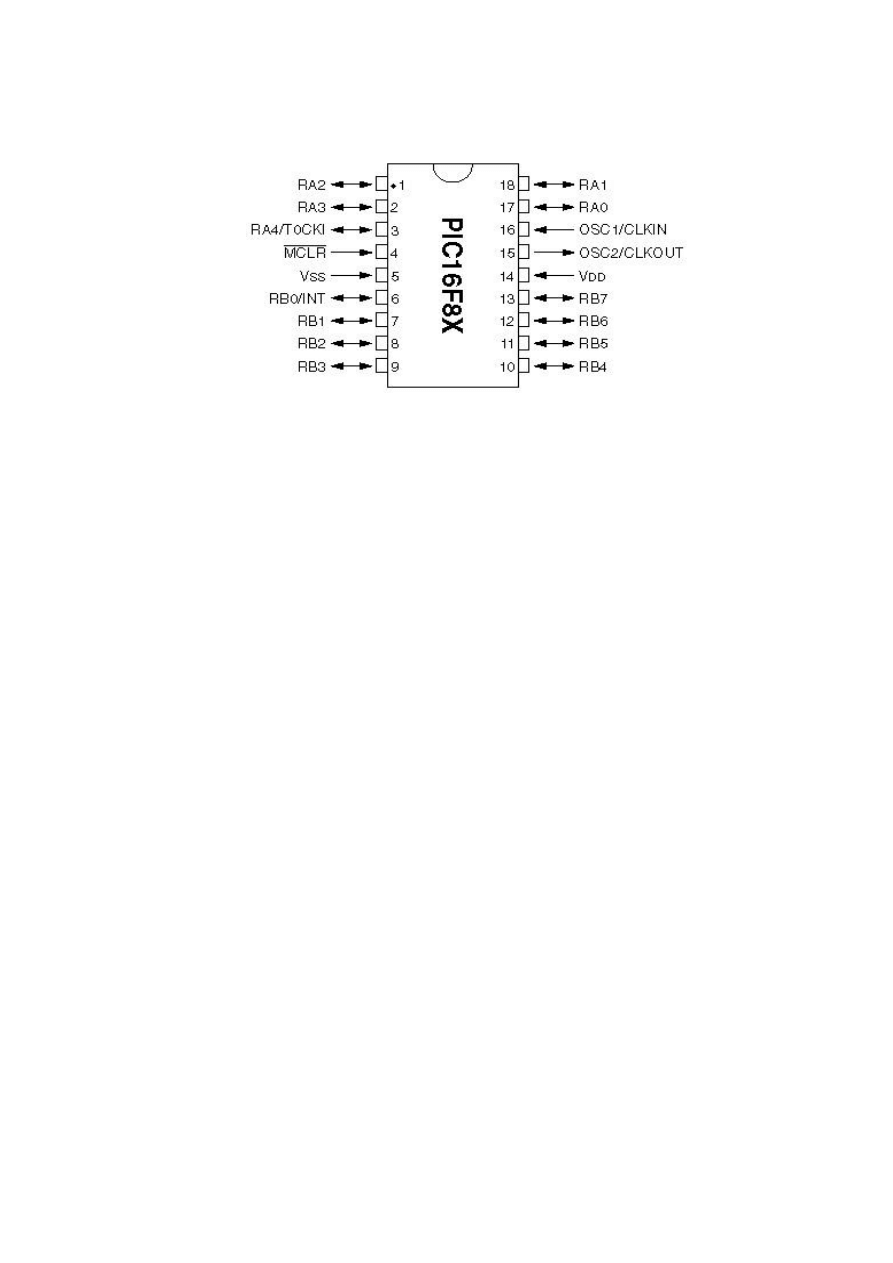

2.2 Opis wyprowadzen procesora PIC 16F84.

Opis wyprowadzen przedstawia rys.1 (obudowa typu PDIP, SOIC). Procesor ma 13

uniwersalnych wyprowadzen wejscia-wyjscia z indywidualna konfiguracja funkcji. Prad

wplywajacy do ukladu (sink)

?

25mA, wyplywajacy z ukladu (source)

?

20 mA.

Rys. 1 Opis wyprowadzen

2.3 Funkcje dodatkowe mikrokontrolera PIC 16F84.

??

POWER-ON RESET czyli zerowanie po wlaczeniu zasilania,

??

POWER-UP TIMER tzn. przedluzenie sygnalu zerowania po wlaczeniu zasilania o 72 ms

celem unikniecia niepozadanych zachowan ukladów wspólpracujacych np. wyswietlacza

LCD ze sterownikiem HD 77480 ,

??

OSCILLATOR START-UP TIMER uklad do przedluzenia zerowania wewnetrznego

procesora o 1024 takty sygnalu zegarowego,

??

WATCHDOG TIMER- uklad niezaleznego timera wewnatrz procesora, który w przypadku

jego zawieszenia zeruje go (informacja o zródle wyzerowania jest pamietana w

odpowiednim rejestrze),

??

CODE-PROTECTION - bit zabezpieczajacy program zródlowy przed odczytem,

??

mozliwosc wprowadzenia procesora w sposób programowy w stan „uspienia” (ang.

SLEEP MODE), tzn. zawieszenie wszystkich czynnosci (z zapamietaniem zawartosci

rejestrów). Powrót ze stanu SLEEP nastepuje po wystapieniu przerwania,

??

mozliwosc wyboru oscylatora (rezonator kwarcowy 1-10 MHz lub 32 – 400 kHz,

taktowanie sygnalem zewnetrznym, zewnetrzny oscylator RC),

??

wbudowany system programowania szeregowego, programowanie poprzez dwie koncówki

RB6, RB7.

2.4 Organizacja pamieci w procesorze PIC 16F84

W procesorze PIC 16F84 znajduja sie dwa bloki pamieci :

- blok pamieci programu ,

- blok pamieci danych.

2.4.1 Organizacja pamieci programu.

Pamiec programu w omawianym procesorze jest pamiecia typu FLASH, co umozliwia

wielokrotne zapisywanie tej pamieci. W praktyce umozliwia to wykorzystanie jednego

procesora w wielu aplikacjach.

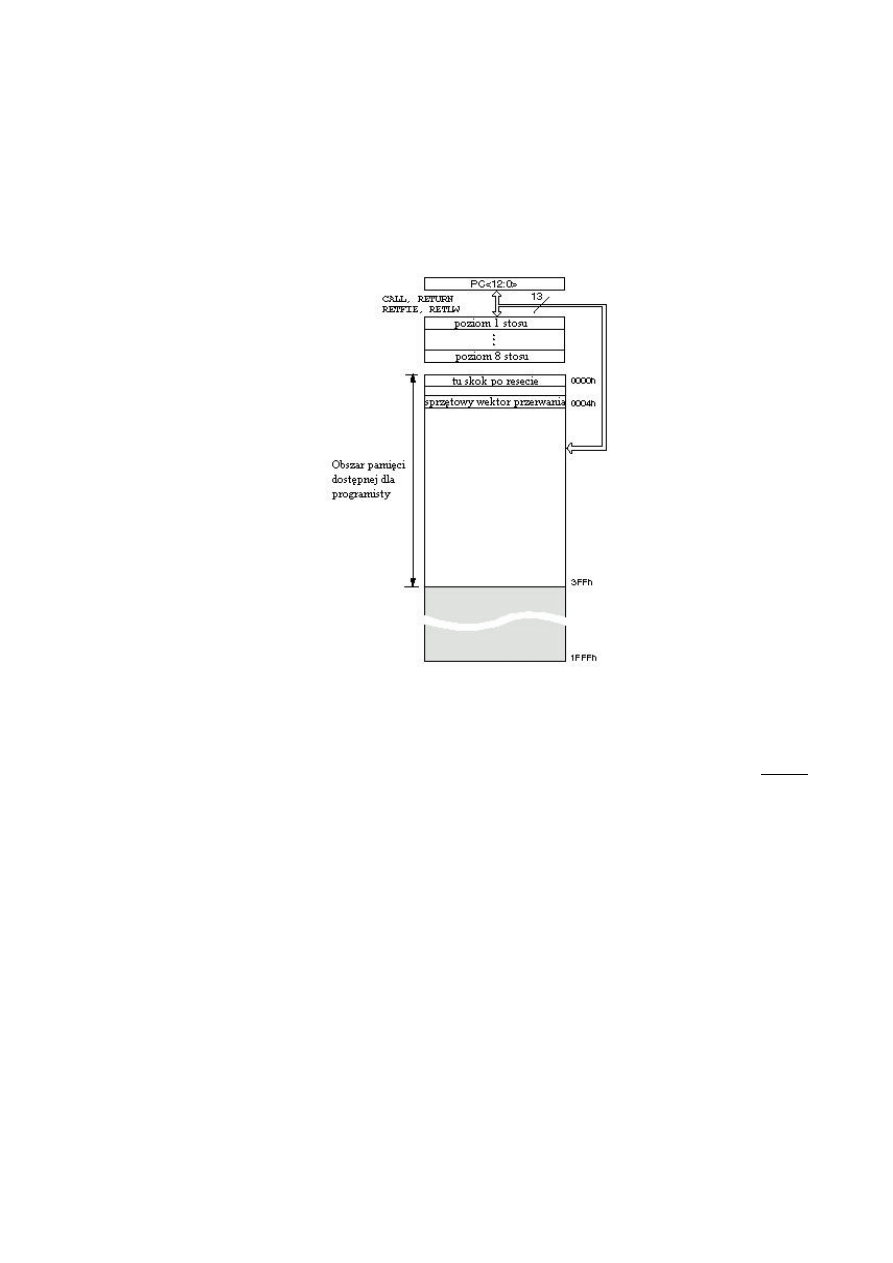

PIC 16F84 posiada trzynastobitowy licznik programu co umozliwia adresowanie bloku

pamieci o maksymalnym rozmiarze 8KB. Opisywany procesor posiada 1KB pamieci

programu. Mikroprocesor posiada jeden wektor procedury przerwania (adres 04h), dlatego

rozpoznanie przyczyny przerwania spoczywa na programie w czesci procedury przerwania.

Rys. 2 Organizacja pamieci programu

2.4.2 Organizacja pamieci danych.

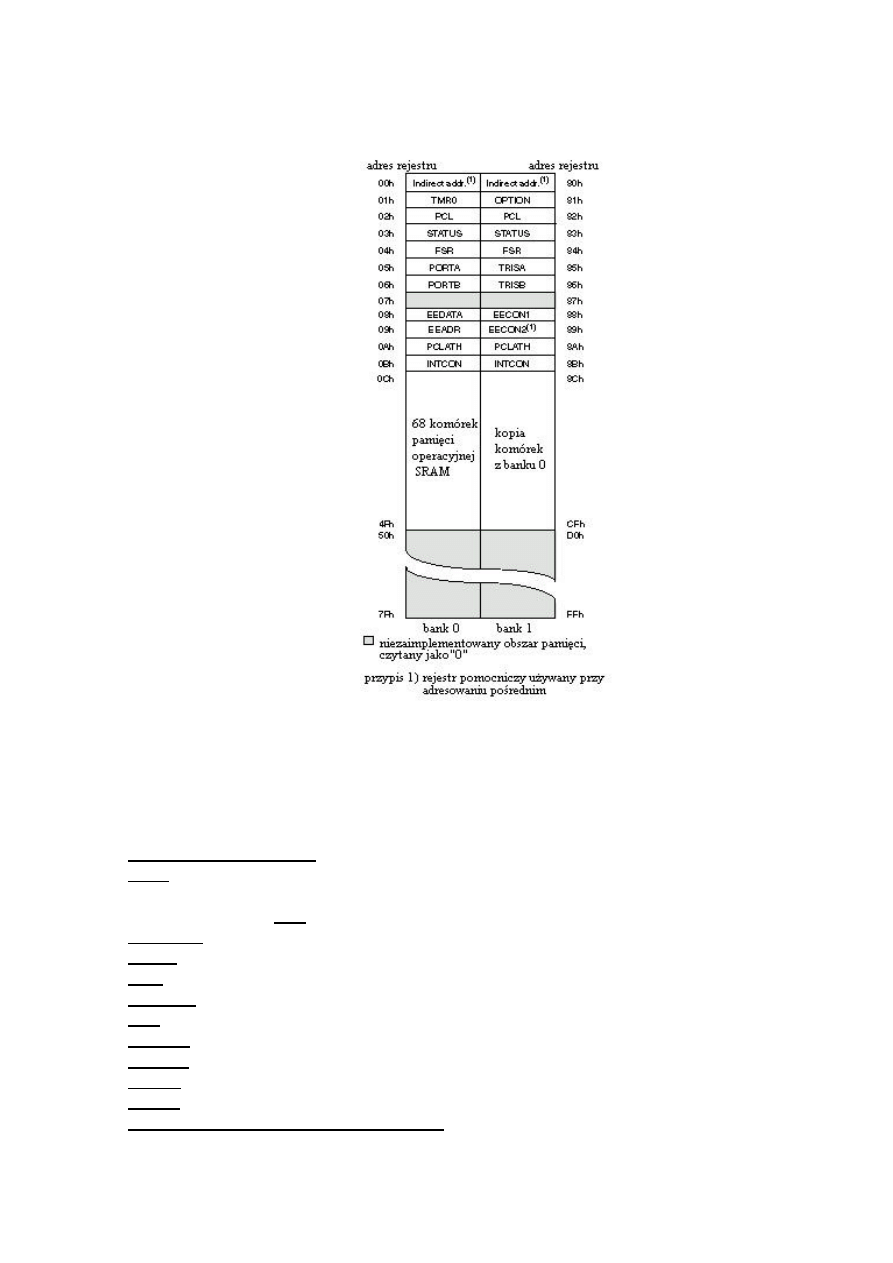

Pamiec danych jest podzielona na dwa obszary. Pierwszy obszar to rejestry

specjalnego przeznaczenia – SFR ( adresy od 00h do 0bh i od 80h do 8bh ), które sluza do

sterowania oraz kontrolowania mikroprocesora, drugi zas to rejestry ogólnego przeznaczenia

– GPR sluzace jako pamiec operacyjna (statyczna) RAM . Pamiec danych jest podzielona na

banki w PIC 16F84 znajduja sie dwa banki, patrz rys.3). Bezposredni dostep do rejestrów jest

mozliwy w obrebie tylko jednego banku.

Rys. 3 Organizacja pamieci danych

Aby przejsc do przeciwnego banku nalezy zmienic bit IRP w rejestrze STATUS (nie dotyczy

to adresowania posredniego).

2.5 Opis rejestrów sterujacych.

Rejestry i ich znaczenie:

INDF - Indirect addr. - rejestr pomocniczy przy adresowaniu posrednim, tj. wpis (odczyt)

do (z) tego rejestru jest równoznaczne z wpisem do komórki pamieci o adresie umieszczonym

w rejestrze zwanym FSR ,

OPTION - rejestr konfiguracji,

TMR0 - licznik,

PCL - mlodsza czesc ( mlodszy bajt ) licznika programu,

STATUS - rejestr flag ( znaczników ),

FSR - rejestr w którym umieszcza sie adres do adresowania posredniego,

PORTA - rejestr odzwierciedlajacy stan koncówek portu A,

PORTB - rejestr odzwierciedlajacy stan koncówek portu B,

TRISA - konfiguracja kierunku portu A,

TRISB - konfiguracja kierunku portu B,

EEDATA, EECON1, EEADR, EECON2 - rejestry sluzace do obslugi pamieci EEPROM

wewnatrz procesora,

PCLATH - starsza czesc ( tj. piec bitów ) licznika programu,

INTCON - konfiguracja przerwan.

Ciekawym moze byc fakt, iz rejestr „PCL” reprezentuje soba mniej znaczaca czesc

licznika programu PC i dozwolone sa manipulacje na tym rejestrze. Porty wejscia-wyjscia

dostepne sa poprzez rejestry „PORTA” oraz „PORTB”, przy czym kierunek poszczególnych

linii ustala sie wykorzystujac pare rejestrów „TRISA” oraz „TRISB”. Rejestr „TMR0”

odzwierciedla zawartosc licznika i dozwolone sa na nim operacje arytmetyczno-logiczne. W

rejestrze „STATUS” oprócz wspomnianych powyzej bitów przelaczania banków pamieci

znajduja sie bity przedstawiajace stan jednostki arytmetyczno-logicznej (odpowiednik

powszechnie znanego rejestru znaczników) oraz bity informujace o przyczynie wyzerowania

mikrokontrolera (wlaczenie zasilania, zadzialanie ukladu WatchDog-a). Rejestr „OPTION”

odpowiedzialny jest za konfiguracje peryferii jednostki centralnej natomiast rejestr

„INTCON” konfiguruje prace systemu przerwan. Rejestry „EEDATA”, „EEADR”,

„EECON1”, „EECON2” umozliwiaja obsluge wewnetrznej pamieci typu EEPROM. Dalej

znajduje sie 68 rejestrów ogólnego przeznaczenia (odpowiednik pamieci RAM) w których

przechowywane sa dane programu. Najczesciej uzywane rejestry sa zaimplementowane w

obu bankach jednoczesnie by uniknac klopotliwego przelaczania banków. Interesujacy moze

byc fakt, iz producent mikrokontrolera zapewnia tylko programowa zgodnosc róznych typów

mikrokontrolerów w ramach jednej rodziny. Program napisany na mikrokontroler

okreslonego typu musi byc ponownie skompilowany na mikrokontroler innego typu by mógl

pracowac poprawnie, gdyz nie jest zapewniona sprzetowa zgodnosc adresów rejestrów

sterujacych.

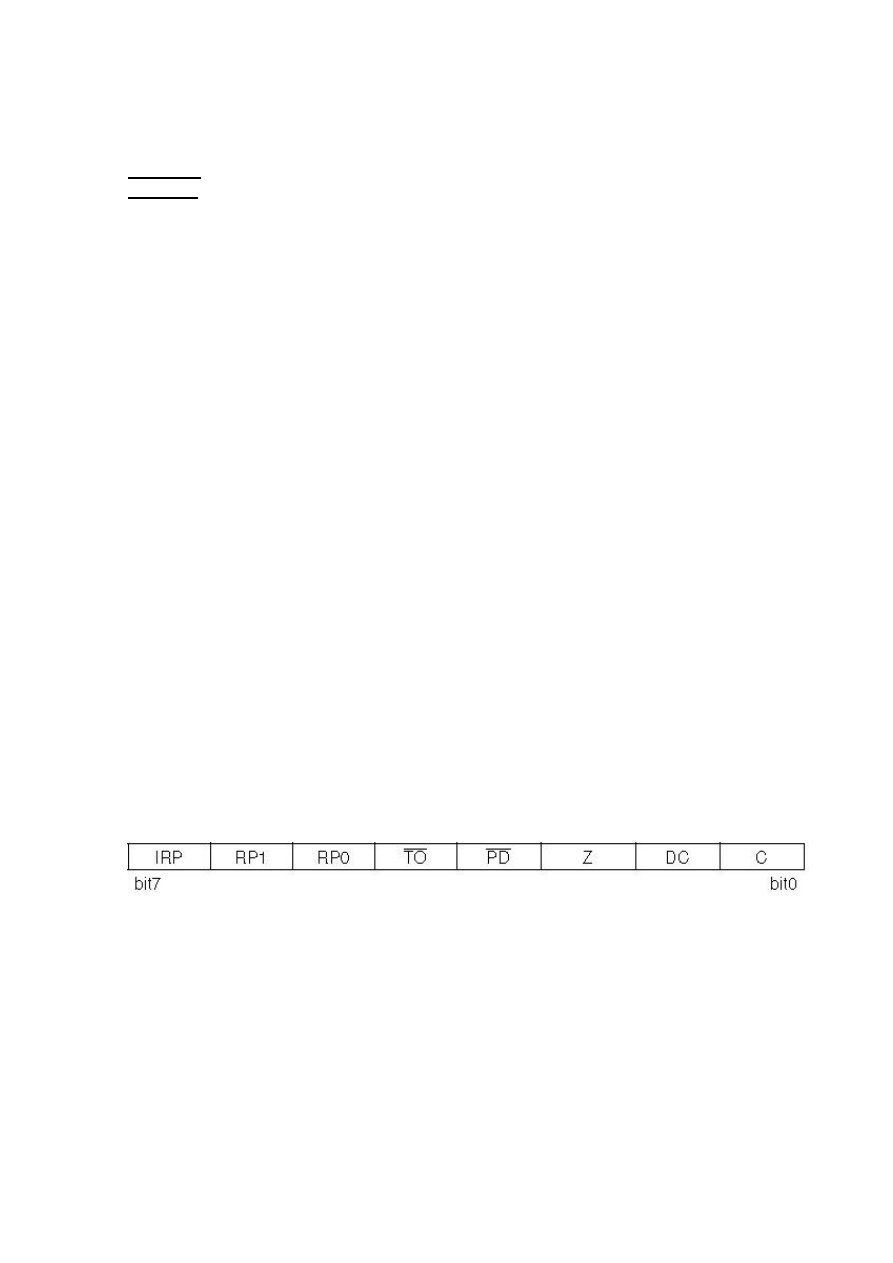

2.6. Znaczenie poszczególnych bitów w rejestrach.

2.6.1 Rejestr STATUS (adres 03h, 83h):

Rejestr statusu zawiera znaczniki odzwierciedlajace :

- wynik ostatnio wykonanej operacji arytmetycznej ,

- aktualny stan procesora tzn. informacje o zródle ewentualnego wyzerowania

procesora oraz informacje o aktywnym banku. Rejestr ten wykorzystywany jest przy

sprawdzaniu wyniku ostatnio wykonanej operacji arytmetyczno-logicznej.

Znaczenie poszczególnych bitów :

bit 7 IRP : Bit wybierajacy bank ( uzywany do adresowania posredniego ) :

0 - Bank 0, 1 (adres 00h - FFh),

1 - Bank 2, 3 (adres 100h - 1FFh),

Bit IRP nie jest wykorzystywany w procesorze PIC 16F8X . Zaleca sie zerowanie tego

bitu w programie w celu zachowania kompatybilnosci tego programu z przyszlymi

wersjami procesorów .

bit 6-5 RP1:RP0 : Bity do selekcji banków (uzywane do adresowania bezposredniego):

0,0 - Bank 0 (adres 00h - 7Fh),

0,1 - Bank 1 (adres 80h - FFh),

1,0 - Bank 2 (adres 100h - 17Fh),

1,1 - Bank 3 (adres 180h - 1FFh),

Kazdy bank jest 128-bajtowy . W PIC 16F8X wykorzystywany jest tylko bit RP0.

bit 4

TO

:"Time out bit", bit informujacy o zadzialaniu WatchDog-a:

1 - po wlaczeniu zasilania , po instrukcji CLRWDT (zerowanie licznika

WatchDog-a) oraz po instrukcji SLEEP,

0 - po zadzialaniu WatchDog-a (po przepelnieniu licznika WatchDog-a),

bit 3

PD

: "Power down bit" - Bit informujacy o przyczynie wyzerowania procesora:

1 - po wlaczeniu zasilania, po instrukcji CLRWDT (zerowanie licznika

WatchDog-a),

0 - po wykonaniu instrukcji SLEEP,

bit 2 Z:

Bit zera:

1 - jezeli wynikiem ostatniej operacji arytmetycznej lub logicznej jest zero,

0 - jezeli wynik jest rózny od zera,

bit 1 DC :

Znacznik przeniesienia pomocniczego (CARRY) lub pozyczki (BORROW),

do którego w czasie operacji dodawania (ADDWF i ADDLW) jest wpisywane

przeniesienie z bitu 3 lub pozyczka z bitu 4 (wykorzystywany przy korekcji dziesietnej,

dla BORROW obowiazuje logika odwrotna):

1 - jezeli wystapilo przeniesienie z bitu 3-go na 4-ty (z mlodszej do starszej

tetrady),

0 - przy braku przeniesienia,

bit 0 C :

Znacznik przeniesienia (CARRY) oraz pozyczki (BORROW), do którego

wpisuje sie przeniesienie z najbardziej znaczacego bitu, ustawiany w wyniku wykonania

operacji arytmetycznych oraz przesuniec a takze rotacji:

1 - jezeli nastapilo przeniesienie z najbardziej znaczacego bitu aktualnego

wyniku

0 - przy braku przeniesienia

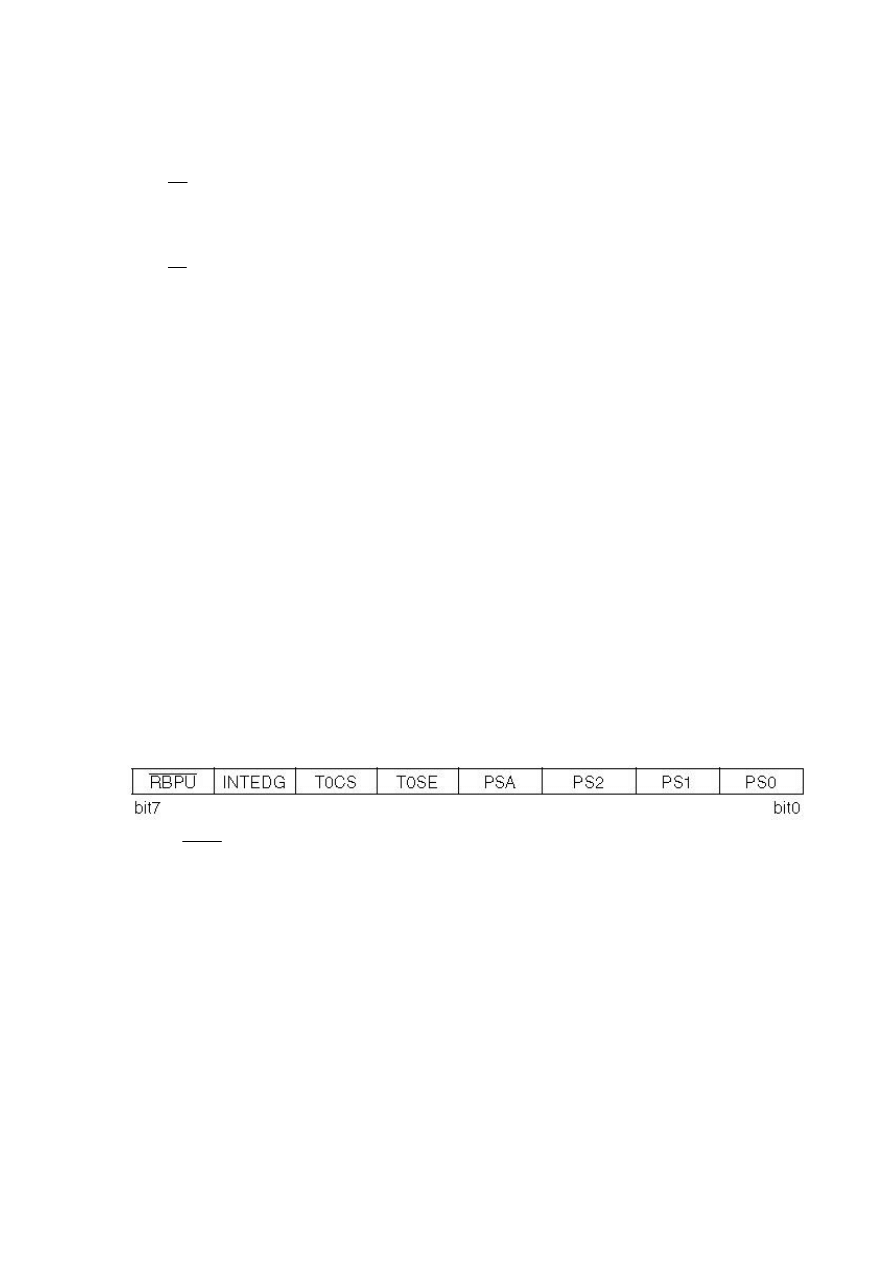

2.6.2 Rejestr OPTION (adres 81h):

Znaczenie poszczególnych bitów :

Bit 7

RBPU

: Bit polaryzujacy wyprowadzenia portu B do potencjalu +Vcc przez opory

(tylko przy konfiguracji portu jako wejsciowe):

1 - praca portu PORTB bez polaryzacji,

0 - praca portu PORTB z polaryzacja,

Bit 6 INTEDG: Wybór rodzaju zbocza jakie nalezy podac na RB0/INT aby wywolac

przerwanie:

1 - przerwanie po zboczu narastajacym na pinie RB0/INT,

0 - przerwanie po zboczu opadajacym na pinie RB0/INT,

Bit 5 T0CS: Wybór zródla sygnalu zegarowego licznika TMR0:

1 - podlaczenie do sygnalu taktujacego zewnetrznego przez koncówke

RA4/T0CKI,

0 - podlaczenie do wewnetrznego sygnalu taktujacego,

Bit 4 T0SE: Wybór zbocza jakie musi wystapic na koncówce RA4/T0CKI aby zwiekszyc

licznik TMR0 o jeden:

1 - zwiekszenie TMR0 o jeden po przejsciu ze stanu wysokiego na niski,

0 - zwiekszenie TMR0 o jeden po przejsciu ze stanu niskiego na wysoki,

Bit 3 PSA: Bit wyboru przeznaczenia podzielnika:

1 - podzielnik podlaczony do WatchDog-a,

0 - podzielnik podlaczony do licznika TMR0,

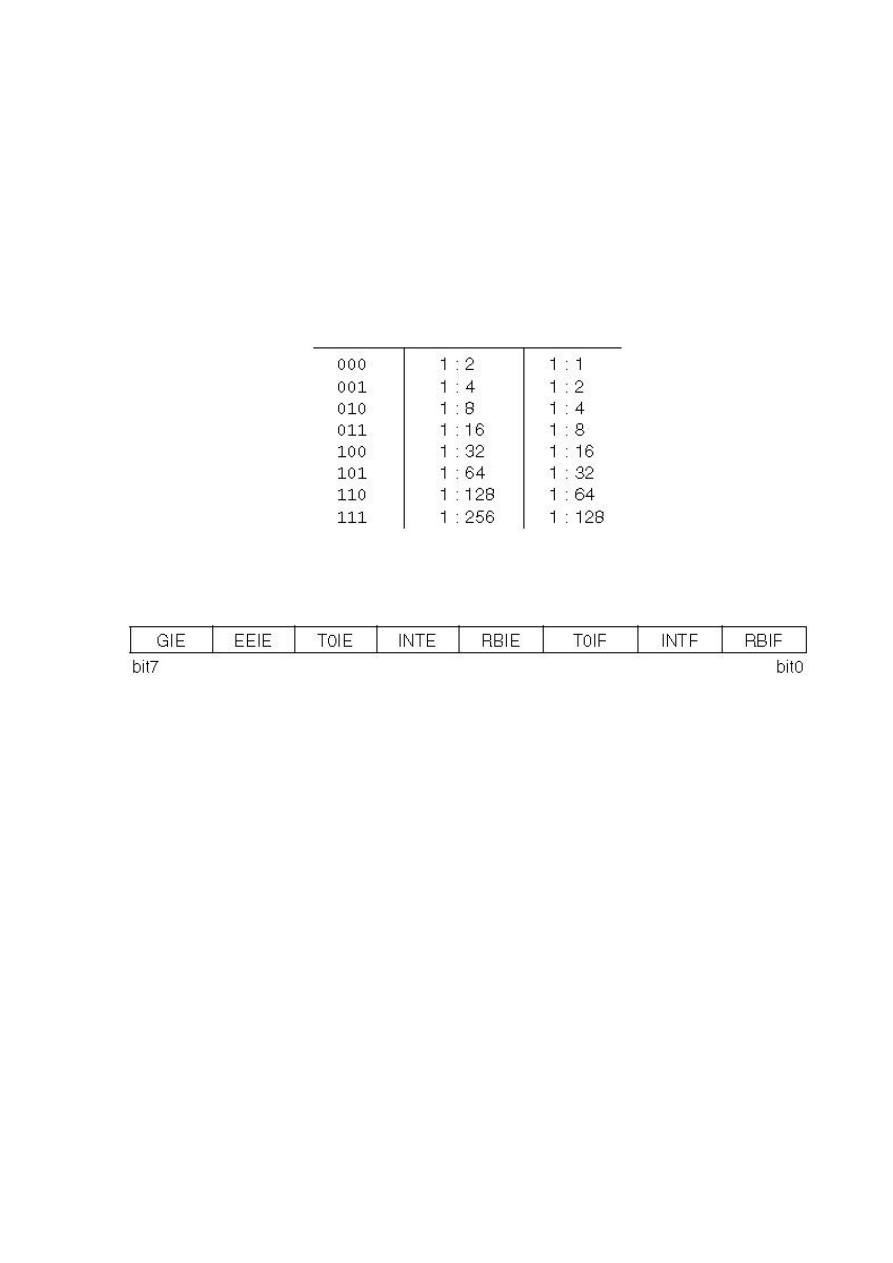

Bit 2-0 PS2,PS1,PS0 : Ustawienie podzialu podzielnika (ang. prescaler) dla licznika TMR0 i

WatchDog-a (WDT):

Tabela 1:

bity 2 1 0

dla TMR0

dla WDT

2.6.3 Rejestr INTCON (adres 0Bh, 8Bh):

Rejestr INTCON sluzy do konfigurowania systemu przerwan.

Bit 7 GIE: Wlaczenie lub wylaczenie wszystkich przerwan (bit GIE posiada najwyzszy

priorytet ):

1 - wlaczenie wszystkich nie zamaskowanych przerwan,

0 - wylaczenie wszystkich przerwan,

Bit 6 EEIE: Uaktywnienie przerwania wywolywanego po zakonczeniu zapisu danej do

pamieci EEPROM wewnatrz procesora:

1 - po zakonczeniu zapisu zostanie wywolane przerwanie,

0 - po zakonczeniu zapisu nie zostanie wywolane przerwanie,

Bit 5 T0IE: Bit uaktywniajacy wywolanie przerwania po przepelnieniu licznika TMR0,

1 - jezeli chcemy aby przerwanie zostalo wywolywane po przepelnieniu

TMR0,

0 - jezeli nie chcemy aby przerwanie zostalo wywolywane po przepelnieniu

TMR0,

Bit 4 INTE: Uaktywnienie przerwania zewnetrznego (z koncówki RB0/INT):

1 - przerwanie bedzie wywolywane,

0 - przerwanie nie bedzie wywolywane,

Bit 3 RBIE: Wlaczenie przerwania pochodzacego od zmiany stanu na porcie PORTB:

1 - przerwanie bedzie wywolywane,

0 - przerwanie nie bedzie wywolywane,

Bit 2 T0IF: Przepelnienie licznika TMR0 powoduje jego ustawienie co jest równoznaczne z

natychmiastowym wywolaniem przerwania. Jezeli programowo ustawimy bit T0IF

(bit T0IF =1) to takze zostanie wywolane przerwanie (od razu po rozkazie „ BSF

INTCON,T0IF”)

1 - nastapilo przepelnienie (bit ten musi byc zerowany programowo)

0 - nie nastapilo przepelnienie,

Bit 1 INTF: Bit informujacy o tym, ze ostatnie przerwanie zostalo wywolane zboczem na

koncówce RB0/INT:

1 - nastapilo przerwanie pochodzace od RB0/INT,

0 - nie nastapilo przerwanie pochodzace od RB0/INT,

Bit 0 RBIF: Bit informujacy o tym, ze ostatnie przerwanie zostalo wywolane zmiana stanu

na jednej z koncówek portu B (RB7 do RB4):

1 - jezeli nastapila zmiana stanu na którejs z koncówek RB7:RB4 (bit musi byc

kasowany programowo),

0 - jezeli nie bylo zmiany stanów,

2.7 Porty wejscia-wyjscia:

Dzieki dobrym parametrom tranzystorów z których zbudowano wyjscia portów do

koncówek tych mozna podlaczyc bezposrednio diody LED co jest ogromna zaleta tych

procesorów. Porty te moga pracowac zarówno jako uklady wyjsciowe jak i wejsciowe.

Konfiguracja kierunku portu mozliwa jest w sposób programowy poprzez rejestr TRISA/B.

2.7.1 Port A

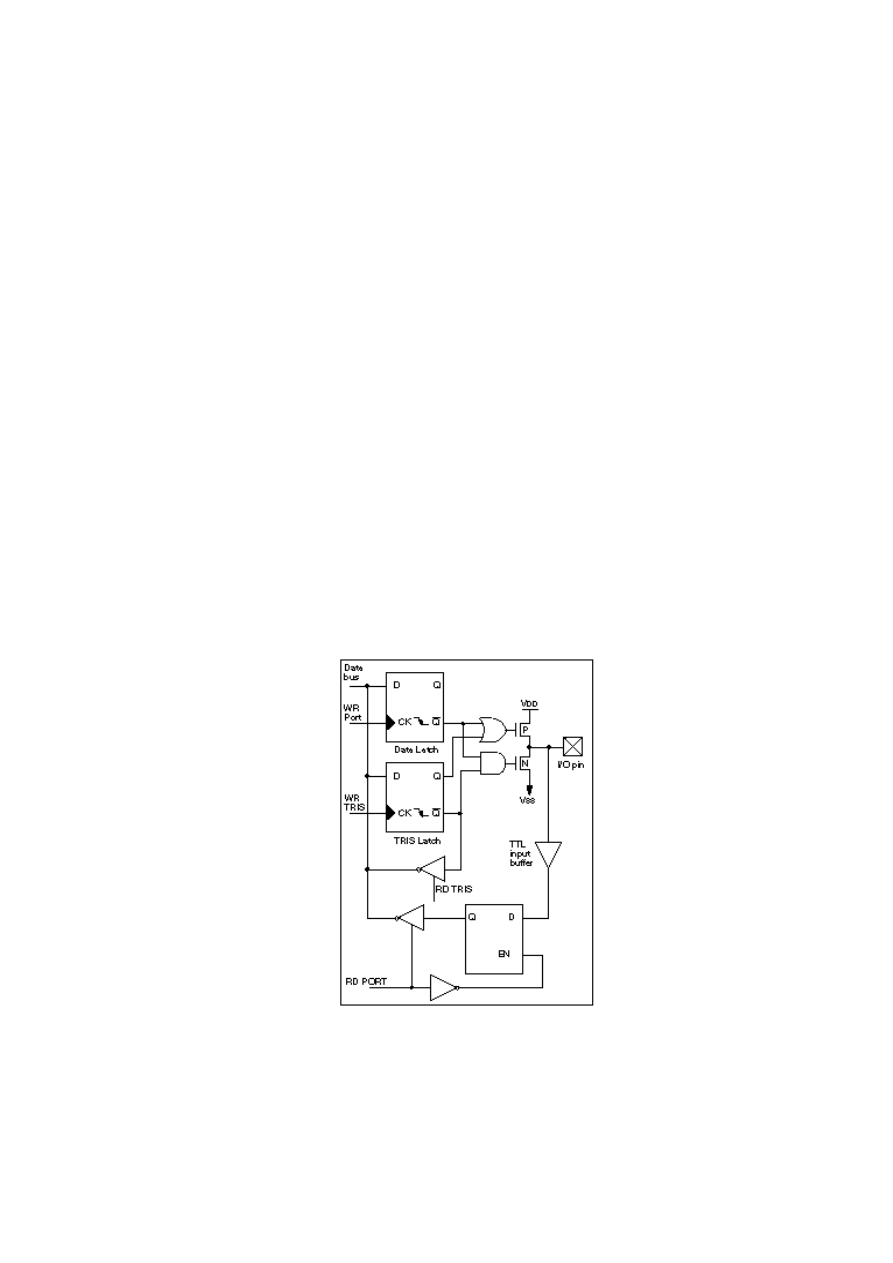

Strukture koncówek RA0, RA1, RA2, RA3 portu PORTA przedstawia rys.4.

Rys. 4 Struktura wewnetrzna koncówek RA0 do RA3

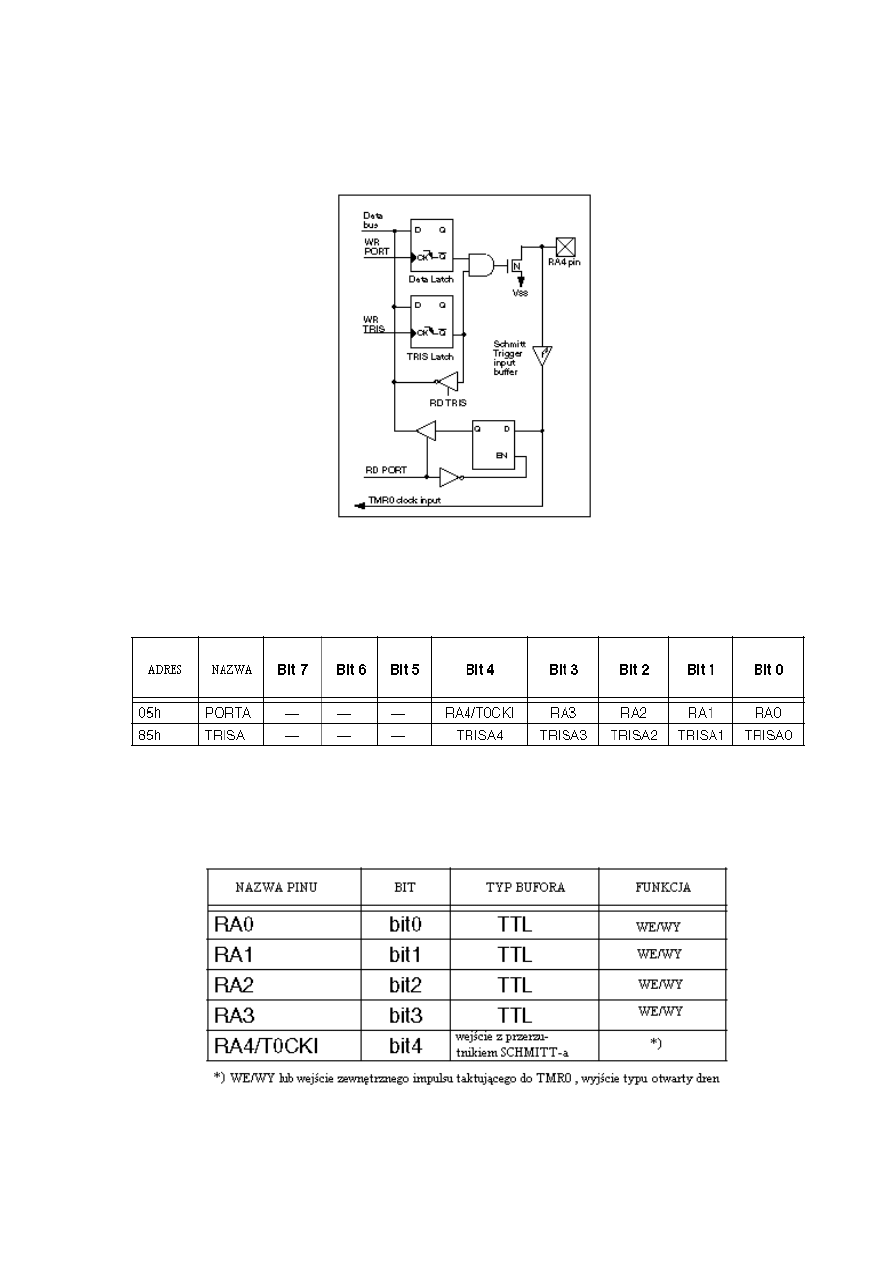

Strukture portu dla koncówki RA4 przedstawia rys.5. Jest to wyprowadzenie typu otwarty

dren, z mozliwoscia wymuszenia na nim przez procesor stanu niskiego. Na wejsciu uklad

wyposazony jest w bramke Schmit’a co pozwala na wykorzystanie portu jako wejscie dla

sygnalu taktujacego licznik TMR0.

Rys. 5 Struktura wewnetrzna koncówki RA4

Tabele 2 przedstawiono w ramach podsumowania rejestrów PORTA i TRISA.

Tabela 2:

Ustawienie bitu TRISx (TRISx = 1) powoduje zdefiniowanie odpowiedniego

wyprowadzenia (RAx) jako wejscie, wyzerowanie jako wyjscie. Tabela 3 przedstawia opis

cech poszczególnych wyprowadzen.

Tabela 3:

2.7.2 Port B

Port ten jest 8-bitowym dwukierunkowym portem równoleglym z mozliwoscia

wewnetrznego podciagniecia tych koncówek do +Vcc poprzez tranzystor o duzej impedancji

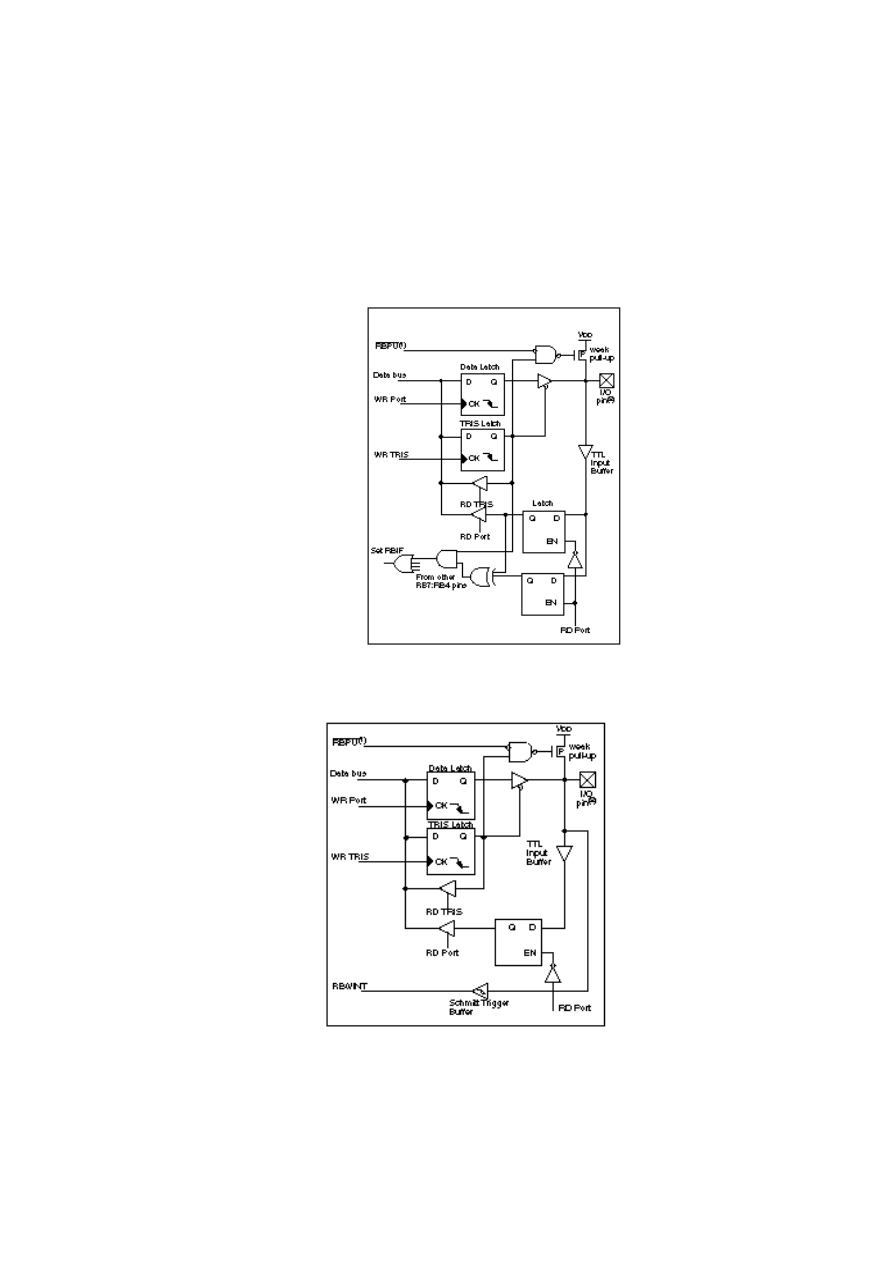

zlacza zródlo-dren w stanie przewodzenia. Strukture koncówek RB4, RB5, RB6, RB7

przedstawia rys.6 . Zmiana stanu na którejs z nózek RB4, RB5, RB6, RB7 moze byc zródlem

wywolujacym przerwanie.

Rys.6 Struktura wew. koncówek RB4 do RB7

Rys.7 Struktura wew. koncówek RB0 do RB3

Strukture koncówek RB0-RB3 przedstawia rys.7.

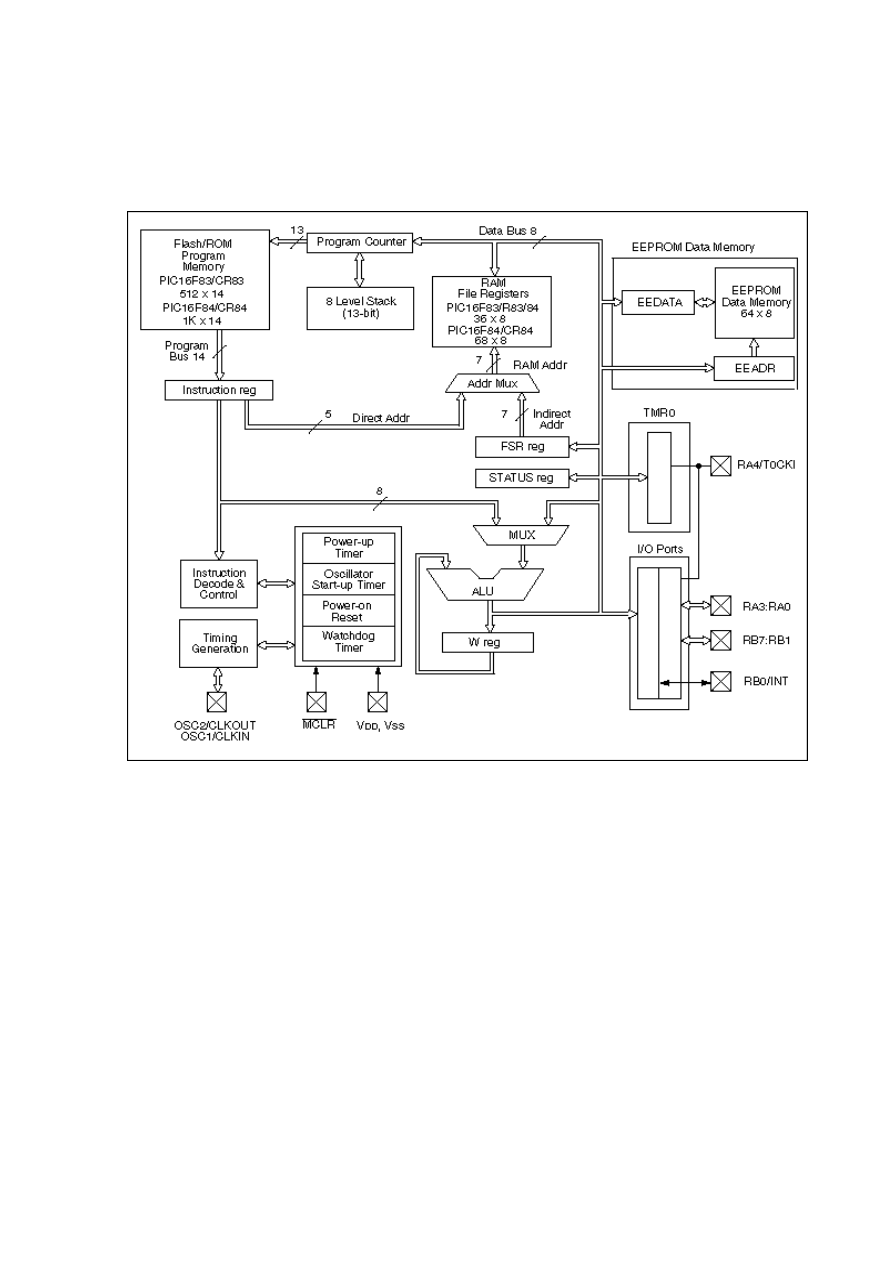

2.8. Architektura procesora:

Rys. 8Architektura procesora PIC 16F84

Procesor zbudowany jest w oparciu o harwardzka architekture, która w

przeciwienstwie do tradycyjnej (von Neumann’a) posiada rozdzielona magistrale programu i

danych. Dzieki temu pamiec danych zostala zorganizowana jako slowa 8-bitowe, natomiast

pamiec programu posiada 14-bitowa dlugosc slowa. Zwiekszenie dlugosci slowa pamieci

programu umozliwilo, przy jednoczesnym zmniejszeniu liczby instrukcji procesora,

zmniejszenie czasu wykonywania wiekszosci instrukcji do jednego cyklu maszynowego gdyz

wszystkie instrukcje mieszcza sie w jednym slowie pamieci i nie jest potrzebny dodatkowy

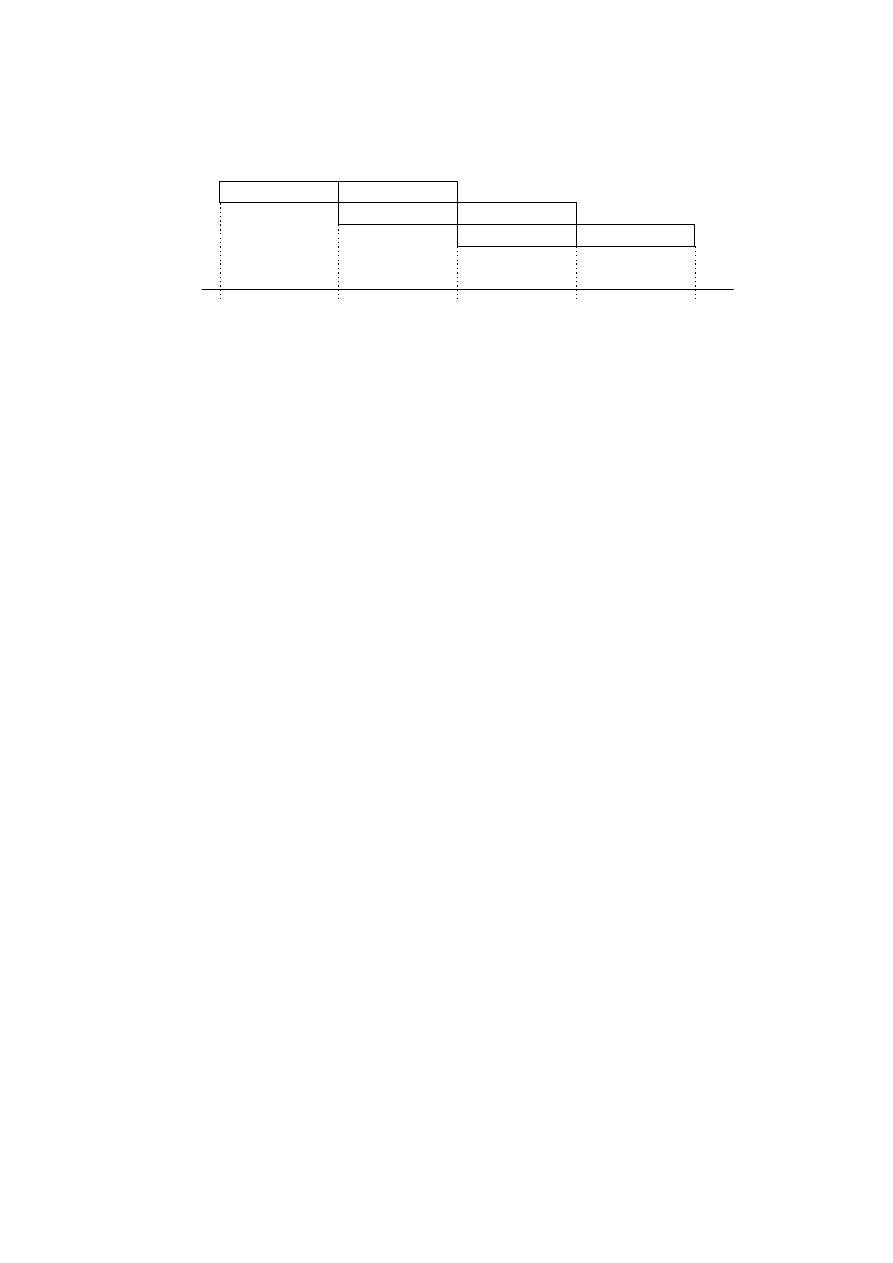

cykl odczytu celem pobrania argumentów rozkazu. Dalsze skrócenie czasu wykonywania

instrukcji przyniósl zastosowany w procesorze flow/pipelining to znaczy podczas cyklu

wykonywania jednej instrukcji nastepuje pobranie kodu nastepnej instrukcji. Ilustruje to rys.9.

Cykl masz. n-ty+3

Cykl masz. n-ty+2

Cykl masz. n-ty+1

Cykl masz. n-ty

Pobranie rozkazu 1

Pobranie rozkazu 2

Pobranie rozkazu 3

Wykonanie rozkazu 1

Wykonanie rozkazu 2

Wykonanie rozkazu 3

Rys. 9 Pobieranie i wykonywanie rozkazów metoda flow/pipelining

Uzyskano tu dwukrotny wzrost predkosci pracy procesora. Metoda ta nie sprawdza sie

podczas wykonywania instrukcji sterujacych programem typu CALL lub GOTO, gdyz nie jest

wtedy pobierany kod nastepnej instrukcji. Zastosowanie w procesorze wspomnianych

mechanizmów doprowadzilo do 4-taktowego cyklu maszynowego. Na uwage zasluguje fakt,

iz w procesorze nie wystepuja tradycyjne instrukcje warunkowe typu „skocz gdy...”, które nie

zmiescily by sie w jednym slowie pamieci programu. W ich miejsce zastosowano grupe

instrukcji typu „testuj bit i nie wykonaj nastepnej instrukcji gdy...”. Liste rozkazów

uzupelniaja instrukcje petli iteracyjnych typu „zmniejsz-zwieksz komórke pamieci i omin

nastepna instrukcje gdy komórka pamieci jest równa zero”.

Procesor posiada standardowa jednostke arytmetyczno-logiczna (ALU), która potrafi

wykonywac podstawowe operacje arytmetyczne (dodawanie, odejmowanie), logiczne (i, lub,

alternatywe, przesuniecia bitowe). Z jednostka arytmetyczno-logiczna zwiazany jest rejestr W

(ang. working register), w którym to pamietany jest jeden z argumentów operacji 2-

argumentowych. Nie nalezy jednak utozsamiac tego rejestru ze znanym powszechnie

rejestrem akumulatora w procesorach „konwencjonalnych”, gdyz pamietany jest w nim 2-gi

argument operacji. Rzadko spotykana cecha procesora jest to, ze wynik operacji moze byc

zapamietany w rejestrze „W” badz komórce pamieci (rejestrze) bioracej udzial w operacji.

Podobnie jak w procesorach serii MCS51, wszystkie rejestry procesora (w tym rejestr

znaczników) leza w przestrzeni adresowej pamieci RAM lub inaczej w przestrzeni „file

registers”.

Procesor posiada 8-poziomowy sprzetowy stos dla instrukcji typu „CALL” oraz

wykorzystywany w systemie przerwan mikrokontrolera. Interesujacym moze takze byc fakt,

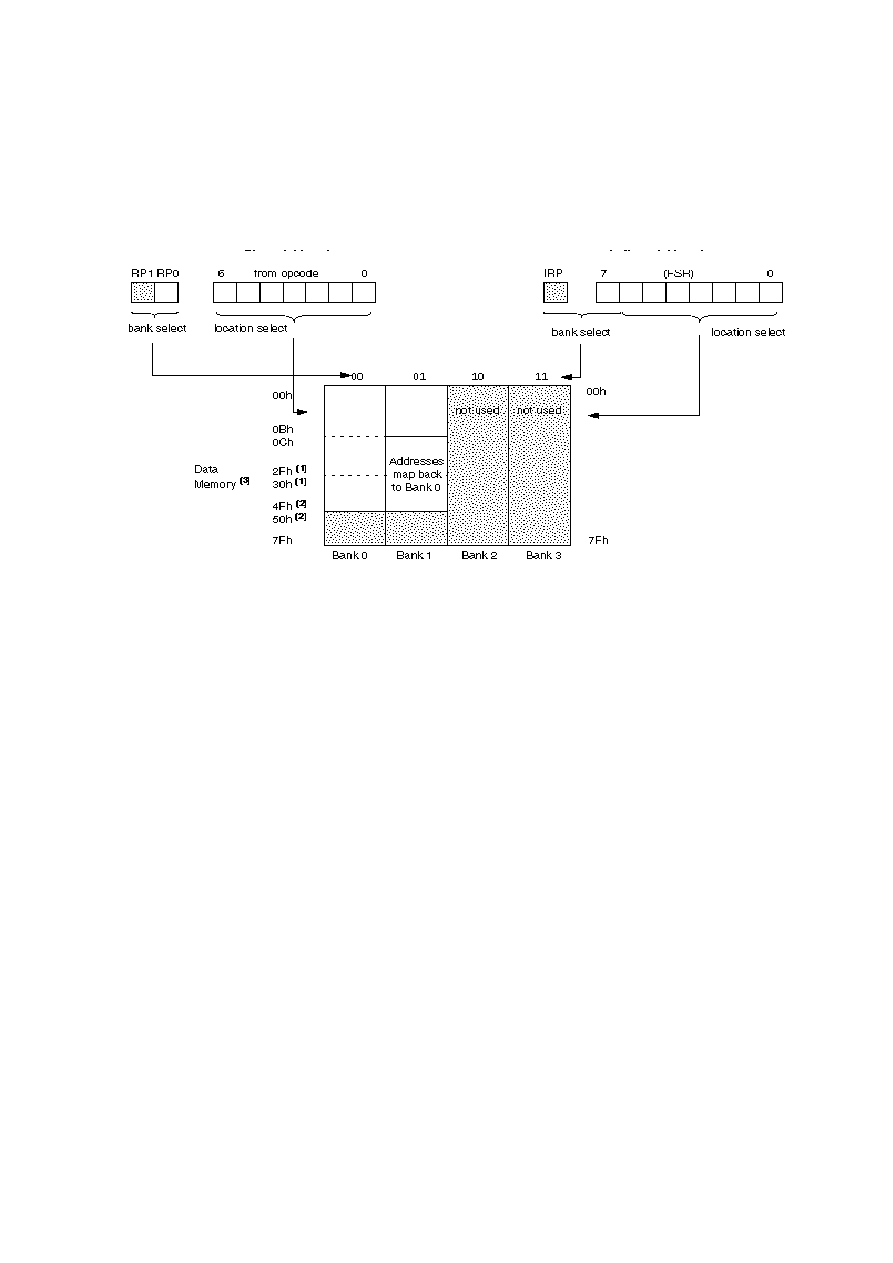

ze procesor nie posiada tradycyjnego trybu adresowania posredniego. W przestrzeni

adresowej rejestrów zaimplementowano specjalny, nieistniejacy fizycznie rejestr (INDF), do

którego wpis lub odczyt powoduje fizyczny wpis lub odczyt komórki pamieci o adresie

zawartym w specjalnym rejestrze FSR. Poniewaz rejestry te sa 8-bitowe, a komórek pamieci

moze byc wiecej niz 256, wiec ewentualne brakujace bity adresu pobierane sa z innego

rejestru (STATUS- bit IRP). Ilustruje to rys.10 .

Z inna sytuacja mamy do czynienia w przypadku adresowania bezposredniego.

Pamiec danych (rejestry ogólnego i specjalnego przeznaczenia) podzielona jest na 128

bajtowe banki, gdyz w kodzie operacji mikrokontrolera przewidziano tylko 7-bitów na adres

bezposredni. Dodatkowe, brakujace bity adresu sa uzupelnione podobnie jak w przypadku

adresowania posredniego bitami zawartymi w rejestrze „STATUS” (bity IRP1,IRP0).

Lista rozkazów mikrokontrolerów tej rodziny nie jest zbyt duza, ale zostala dobrana w

taki sposób, aby mozliwie najbardziej ulatwic pisanie prostych aplikacji dla celów sterowania.

Nie brakuje tu rozkazów operujacych na pojedynczych bitach, oraz rozkazów petli

iteracyjnych bedacych podstawa implementacji algorytmów sterowania. Pelna liste rozkazów

przedstawiono w rozdziale 3.

Adresowanie posrednie

Adresowanie bezposrednie

Rys. 10 Tryby adresowania w procesorze PIC 16F84

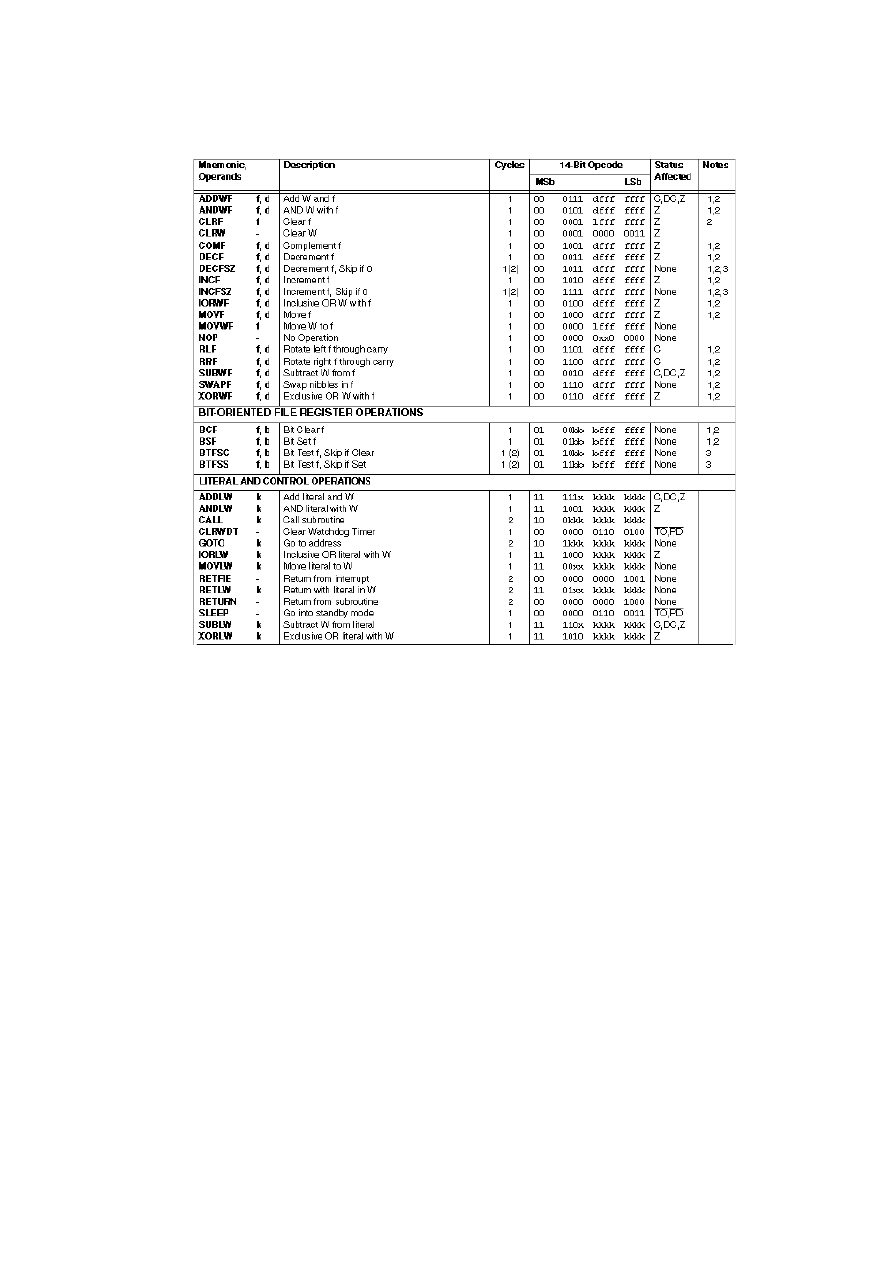

3. Lista rozkazów

Jak juz uprzednio wspomniano lista instrukcji zawiera tylko 35 rozkazów które mozna

podzielic na instrukcje zorientowane bajtowo, zorientowane bajtowo, instrukcje ze stalymi

oraz instrukcje sterujace.

3.1 Format instrukcji

Ponizej przedstawiono formaty dla poszczególnych typów instrukcji.

Instrukcje zorientowana bitowo

Instrukcje zorientowana bajtowo

Instrukcje ze stalymi liczbowymi i sterujace

Instrukcje skoków CALL i GOTO

Bit d (destination) jest drugim argumentem instrukcji, okreslajacym miejsce gdzie

przeslany ma byc wynik operacji. Jezeli d = 1 to wynik przesylany jest do rejestru f

wskazanego w instrukcji, natomiast dla d = 0 przesylany jest do rejestru roboczego

3.2 Lista instrukcji

W tabeli przedstawiono liste rozkazów dla procesorów PIC 16 XXX. Przyjeto, ze „f”

oznacza 7-bitowy adres bezposredni komórki pamieci, „d” miejsce przechowania wyniku

operacji (rejestr „W” lub komórka pamieci), „b” numer uzywanego w operacji bitu (0-7), a

„k” wartosc natychmiastowa. Podano równiez liczbe cykli maszynowych potrzebnych do

wykonania rozkazu i oddzialywanie na flagi w rejestrze STATUS .

13 8

7

6 0

Kod instrukcji

d

f – adres rejestru

d = 0 ......... W

d = 1 f

f = 7 bitowy adres rejestru

13 10

9 7

6 0

Kod instrukcji

b

f – adres rejestru

b = 3 bitowy numer bitu

f = 7 bitowy adres rejestru

13 8

7 0

Kod instrukcji

k (stala)

k = 8 bitowa stala liczbowa

13 11

10 0

Kod instrukcji

k (stala)

k = 11 bitowa stala liczbowa

4. Makroasembler MPASM

4.1 Format pliku wejsciowego i okreslenia

Pliki zródlowe powinny miec rozszerzenie .asm . Zazwyczaj pliki zródlowe pisze sie

za pomoca edytora wbudowanego w MPLAB co ma wiele zalet, ale moga byc one tworzone i

edytowane za pomoca dowolnego edytora tekstowego.

Linia

Linia (maksimum 255 znaków) sklada sie z kolumn rozdzielonych separatorami..

Poszczególne kolumny moga zawierac: etykiety (labels), polecenia (directives), rozkazy i

komentarze. Kolumna pierwsza przeznaczona jest na etykiety i polecenia. Kolumna druga i

nastepne przeznaczone sa na rozkazy i polecenia.

Separator

Separatorem moze byc spacja, dwukropek, tabulator lub znak konca linii.

Komentarz

Srednik (;) jest znakiem komentarza, po którym ignorowane sa wszystkie znaki do konca

linii.

Znak komentarza moze znajdowac sie w dowolnej kolumnie.

Etykiety

Wyszukiwarka

Podobne podstrony:

więcej podobnych podstron