P R O G R A M Y

Elektronika Praktyczna 3/2004

54

do pojedynczego uk³adu FPGA, zamiast

przybieraÊ formÍ p³yty PCB. Wszystkie

dostarczone komponenty wirtualne s¹ pre-

syntezowane, a†ich dzia³anie dok³adnie

zweryfikowane. Daje to duø¹ swobodÍ

dzia³ania i†moøliwoúÊ ³atwego ekspery-

mentowania z†rÛønymi opcjami projektu.

W†sk³ad zestawu Nexar 2004 wchodzi

p³yta uruchomieniowa NanoBoard (fot. 1),

ktÛra wspÛ³pracuje bezpoúrednio z†progra-

mem i†umoøliwia konfigurowanie struktu-

ry FPGA, czyli budowÍ ìna øywoî wars-

twy sprzÍtowej. Ponadto, p³yta pozwala

na za³adowanie kodu do pamiÍÊ progra-

mu procesora, ktÛry zaimplementowaliúmy

w†naszym FPGA oraz jego uruchamianie,

ktÛre rÛwnieø odbywa siÍ ìna øywoî

w†prawdziwym sprzÍcie. Debugowanie

u³atwiaj¹ w†znakomity sposÛb tzw. instru-

menty wirtualne, takie jak analizatory lo-

giczne, generatory czÍstotliwoúci, liczniki

i†wiele innych, ktÛre wstawiamy wprost

na schemacie, a†system umieszcza je we-

wn¹trz naszego FPGA. Program komuniku-

je siÍ z†tymi instrumentami wirtualnymi

rÛwnieø ìna øywoî, za poúrednictwem in-

terfejsu JTAG, ktÛry zarz¹dza zarÛwno

warstw¹ sprzÍtow¹, jak i†programow¹ ca-

³ego projektu. Moøna rzec, øe nasz pro-

jekt jest ìøywyî na kaødym etapie, zarÛ-

wno w†warstwie sprzÍtowej, jak i†progra-

mowej. St¹d okreúlenie LiveDesign, ktÛre

pojawi³o siÍ wraz z†Nexarem, ale dotyczy

rÛwnieø programÛw z†nim wspÛ³pracuj¹-

Wprowadzony niedawno na rynek Ne-

xar jest pierwszym ìosobistymî systemem

wspomagaj¹cym ca³y proces projektowa-

nia, programowania i†uruchamiania syste-

mÛw mikroprocesorowych, implementowa-

nych w†dowolnym uk³adzie FPGA, niewy-

magaj¹cym od projektanta znajomoúci jÍ-

zyka HDL, takiego jak VHDL czy Verilog.

Nexar jest dostarczany wraz z†bibliote-

k¹ komponentÛw wirtualnych (IP cores)

obejmuj¹c¹ kilka procesorÛw, wiele goto-

wych komponentÛw logicznych oraz uk³a-

dÛw†peryferyjnych. Wszystkie te wirtual-

ne komponenty moøemy umieszczaÊ na

schematach oraz ³¹czyÊ razem, buduj¹c

w³asny projekt. Na tym etapie projektowa-

nie uk³adu nie rÛøni siÍ niczym od kreú-

lenia zwyk³ych schematÛw z†wykorzysta-

niem tradycyjnych elementÛw. Istotna rÛø-

nica jest widoczna dopiero w†kolejnych

etapach, kiedy realizowany projekt trafia

Spadaj¹ce ceny oraz rosn¹ca pojemnoúÊ najnowszych

uk³adÛw FPGA zachÍcaj¹ do ich szerszego stosowania

w†projektach elektronicznych. Moøliwoúci wspÛ³czesnych

uk³adÛw programowalnych pozwalaj¹ na implementacjÍ

ca³ych systemÛw mikroprocesorowych wewn¹trz

pojedynczego uk³adu, jednak istotn¹ przeszkod¹

w†masowym zastosowaniu tej technologii by³ brak

odpowiednich, niedrogich i†³atwych w†stosowaniu

narzÍdzi wspomagaj¹cych projektowanie i†uruchamianie

takich aplikacji. Prze³om w†tej dziedzinie przynosi

Nexar - najnowszy produkt firmy Altium.

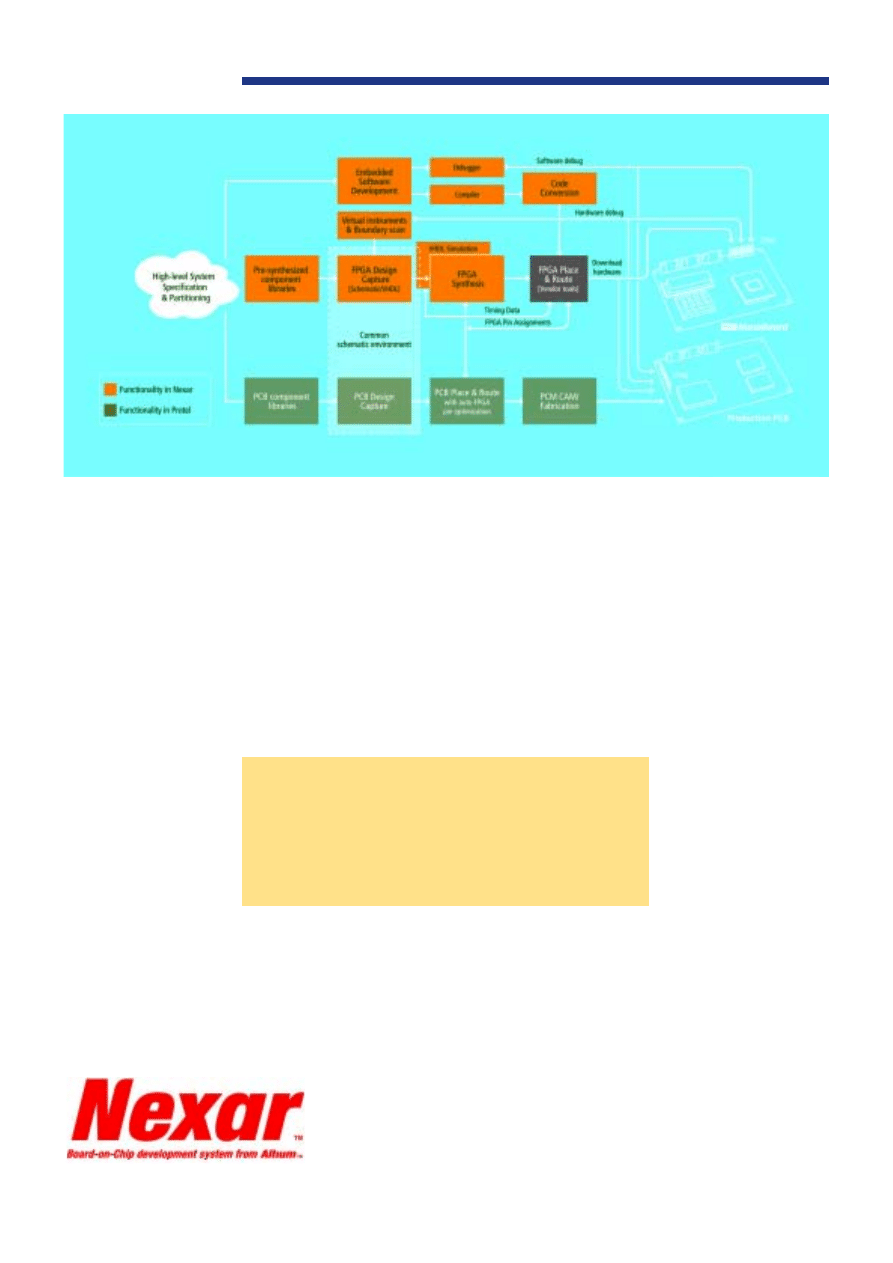

Rys. 1

Wirtualne peryferia

Cyfrowe bloki funkcjonalne

są zapisane najczęściej

w formacie EDIF lub innym

przystosowanym do syntezy

logicznej. Przyjmują one

postać fizyczną po

implementacji w układzie

PLD, w praktyce najczęściej

w FPGA.

P R O G R A M Y

Elektronika Praktyczna 3/2004

56

cych, takich jak nowy Protel 2004 czy

nVisage 2004.

Istotn¹ czÍúci¹ filozofii, jaka przyúwieca-

³a twÛrcom Nexara, jest obs³uga wielu rÛø-

nych platform sprzÍtowych. W†obecnej

wersji Nexar obs³uguje rodziny uk³a-

dÛw†FPGA firm Altera i†Xilinx, a†docelo-

wo liczba platform jeszcze siÍ poszerzy.

Nie mniej istotny jest fakt, øe dostarczone

komponenty wirtualne s¹ wolne od op³at

licencyjnych, pomimo tego, øe w†bibliote-

kach znajduje siÍ wiele wartoúciowych

komponentÛw, jak procesory czy interfejsy

komunikacyjne, oprÛcz tego wiele podsta-

wowych komponentÛw logicznych oraz

tzw. instrumenty wirtualne wspomagaj¹ce

uruchamianie urz¹dzenia na

poziomie sprzÍtu.

Pomimo tego, øe projektuj¹c

za pomoc¹ Nexara, tworzymy

i†uruchamiamy system bazuj¹c

na p³ycie NanoBoard wyposa-

øonej w†rekonfigurowalny

uk³ad FPGA, nic nie stoi na

przeszkodzie, aby ostatecznie

zaimplementowaÊ go na innej

platformie, korzystaj¹c z†trady-

cyjnych elementÛw dyskret-

nych i†p³yty drukowanej czy

nawet w†formie wielkoseryjnego uk³adu

ASIC. Inaczej mÛwi¹c, moøemy wykorzys-

taÊ wszystkie dobrodziejstwa, jakie daje

FPGA na etapie projektowania, uruchamia-

nia i†testowania uk³adu, a†docelow¹ plat-

formÍ wybraÊ zaleønie od innych czynni-

kÛw, takich jak wymagane gabaryty urz¹-

dzenia, cena czy wielkoúÊ serii.

Inn¹ istotn¹ cech¹ úrodowiska Nexar jest

úcis³a integracja z†narzÍdziami do projek-

towania PCB, w†szczegÛlnoúci z†najnow-

szym programem Protel 2004. Nexar jest

wyposaøony w†specjalne narzÍdzia, ktÛre

optymalizuj¹ rozk³ad wyprowadzeÒ uk³adu

FPGA tak, aby moøna by³o jak najproúciej

zaprojektowaÊ p³ytÍ PCB, na ktÛrej uk³ad

bÍdzie zamontowany. FunkcjonalnoúÊ pro-

gramÛw Nexar 2004 i†Protel 2004 siÍ uzu-

pe³nia, co pokazano na rys. 2.

Wspomnieliúmy juø wczeúniej, øe Nexar

dostarczany jest w†komplecie z†p³yt¹ uru-

chomieniow¹ NanoBoard, ktÛra wspÛ³pra-

cuje z†programem, pozwalaj¹c na konfigu-

racjÍ, programowanie i†uruchamianie sys-

temu wewn¹trz FPGA. Konstrukcja Nano-

Board pozwala na stosowanie rÛønych

uk³adÛw FPGA, poniewaø nie s¹ one osa-

dzone bezpoúrednio na p³ycie, lecz za po-

moc¹ do³¹czanej p³ytki ìprzejúciÛwkiî,

tzw. doughterboard. Pierwsza wersja pro-

gramu dostarczana jest z†dwoma takimi

uk³adami - z†rodziny Spartan IIE (Xilinx)

oraz Cyclone (Altera).

Warto nadmieniÊ, øe NanoBoard wypo-

saøona jest w†zestaw uk³adÛw peryferyj-

nych. Znajdziemy tam m.in. klawiaturÍ,

wyúwietlacz LCD, matrycÍ LED, prze³¹cz-

niki DIP, przetworniki AC/CA, zestaw

portÛw I/O oraz pamiÍci zewnÍtrzne. Po-

nadto specjalne dedykowane z³¹cze umoø-

liwia zestawienie kilku p³yt w†³aÒcuch

i†uruchamianie projektÛw, ktÛrych wiel-

koúÊ nie pozwala na implementacjÍ w†po-

jedynczej koúci FPGA. P³yta NanoBoard

³¹czy si͆z†komputerem poprzez port rÛw-

Rys. 2

noleg³y i†komunikuje ze úrodowiskiem Ne-

xar za pomoc¹ interfejsu JTAG.

Wspomnieliúmy wczeúniej o†procesorach,

ktÛre znajdziemy w†bibliotekach kompo-

nentÛw wirtualnych, dostarczanych z†Nexa-

rem. Na dzieÒ dzisiejszy znajdziemy

w†nich procesory 8-bitowe, oparte na sze-

roko stosowanej rodzinie 8051, Z80 oraz

PIC165x. RÛwnie istotnym elementem, jak

sam procesor, jest jego oprogramowanie.

Nexar nie by³by kompletnym úrodowis-

kiem, gdyby nie zawiera³ narzÍdzi progra-

mistycznych, wspomagaj¹cych tworzenie

i†uruchamianie kodu dla procesorÛw. Tak

wiÍc, Nexar zosta³ wyposaøony w†najnow-

szej generacji kompilator, oparty na tech-

nologii Viper firmy Altium.

Identyczny kompilator jest sto-

sowany i†sprawdzony rÛwnieø

w†szerokiej gamie produktÛw

TASKING, znanych zapewne

niektÛrym Czytelnikom. Kom-

pilator jest konfigurowalny

pod konkretny procesor i†gene-

ruje wysokiej jakoúci, dobrze

zoptymalizowany kod, zarÛ-

wno z†plikÛw ürÛd³owych

w†C, jak i†w†asemblerze.

Tak specyficzny, oryginalny

i†kompleksowy produkt, jakim jest Nexar,

stanowi niew¹tpliwie prze³om na rynku

narzÍdzi projektowych. System oferuje

niespotykan¹ dot¹d prostotÍ projektowania

oraz implementacji w†FPGA, ca³ych syste-

mÛw†mikroprocesorowych lub podobnych

z³oøonych projektÛw. Maj¹c do dyspozy-

cji narzÍdzie, ktÛre pozwala zaprojekto-

waÊ i†uruchomiÊ system, od pocz¹tku do

koÒca nie ruszaj¹c siÍ od biurka, moøemy

inaczej spojrzeÊ na wiele problemÛw, ktÛ-

re wczeúniej wydawa³y siÍ nie do przej-

úcia. Moøemy budowaÊ urz¹dzenia, jakich

nie byliúmy w†stanie wykonaÊ tradycyjny-

mi technikami. Urz¹dzenia mniejsze, szyb-

sze, bardziej niezawodne - takie, jakich

wymaga wspÛ³czesny rynek.

Grzegorz Witek, Evatronix

JTAG

Interfejs szeregowy służący do programowania,

konfigurowania oraz testowania układów po

zamontowaniu ich w systemie. Testowanie odbywa

się za pomocą wbudowanej w układy tzw. ścieżki

krawędziowej (BST − Boundary Scan Testing),

za pomocą której można weryfikować także

działanie elementów zewnętrznych.

Wyszukiwarka

Podobne podstrony:

54-56, polski

54 56

54 56

ei 01 2002 s 54 56

53-54-56-69-75, Studia - informatyka, materialy, KSA

(11) 54 i 56 64 Ets Consten SARL & Grundig Verkaufs a porozumienia wertykalne i import równoległy

ei 07 2002 s 54 56

54 56

54-56, polski

ei 05 2002 s 54 56

12 1993 54 56

54, ,56,41

Zagadnienie nr 56, 54

więcej podobnych podstron