©Wojciech Surtel

TECHNIKA

TECHNIKA

MIKROPROCESOROWA

MIKROPROCESOROWA

Pamięci półprzewodnikowe

Pamięci półprzewodnikowe

TECHNIKA MIKROPROCESOROWA

TECHNIKA MIKROPROCESOROWA

• Półprzewodnikowe pamięci statyczne RAM (SRAM)

• Półprzewodnikowe

p

amięci dynamiczne RAM (DRAM)

• Łączenie układów pamięci

• Pamięć podręczna

Klasyfikacja pamięci fizycznych w systemach

Klasyfikacja pamięci fizycznych w systemach

komputerowych

komputerowych

TECHNIKA MIKROPROCESOROWA

TECHNIKA MIKROPROCESOROWA

PAMIĘĆ

PAMIĘĆ

Bit – podstawowa jednostka przechowywania informacji,

Bajt – uporządkowane 8 bitów,

do przechowywania informacji służą rejestry,

Pamięć:

–

zestaw ponumerowanych rejestrów, najczęściej 8-bitowych,

–

każdy rejestr to komórka pamięci,

–

numer każdego rejestru to adres,

Pojemność pamięci – ilość dostępnych komórek pamięci:

–

jednostki,

–

1 KB = 1024 B = 2

10

B,

Do obsługi pamięci wymagana odpowiednia szyna systemowa

Rodzaje pamięci:

–

RAM,

–

ROM,

–

EPROM,

–

EEPROM,

–

EEPROM FLASH

TECHNIKA MIKROPROCESOROWA

TECHNIKA MIKROPROCESOROWA

•

pamięć programu

(zawierająca kod programu, tablice stałych, wektor

resetu i przerwań)

•

pamięć danych

(przechowująca zmienne)

•

stos sprzętowy

(obsługi przerwań i wywołań funkcji odkładają na niego

bieżącą wartość

licznika rozkazów i po zakończeniu działania „zdejmują”

ją)

•

pamięć EEPROM

(przechowuje zmienne lub tablice stałych, które po

wyłączeniu

zasilania nie mogą ulec skasowaniu)

Pamięć programu jest wykonana w technologii ROM, EPROM, OTP lub

FLASH. Natomiast pamięć danych najczęściej jest typu

SRAM.

W mikrokontrolerach mo

W mikrokontrolerach mo

ż

ż

na wyró

na wyró

ż

ż

ni

ni

ć

ć

nast

nast

ę

ę

puj

puj

ą

ą

ce

ce

typy pami

typy pami

ę

ę

ci:

ci:

ROM (Read Only Memory) - programowanie zawartości

pamięci następuje w procesie produkcyjnym i nie może być

przeprowadzone przez użytkownika.

EPROM (Erasable Programmable ROM) - pamięci z

możliwością kasowania dotychczasowej zawartości

promieniami ultrafioletowymi i prowadzania nowej zawartości

za pomocą zewnętrznego programatora. Umieszczane

są w obudowach z okienkiem kwarcowym w celu

umożliwienia kasowania.

OTP (One Time Programmable) - pamięci typu EPROM

umieszczane w obudowach bez okienka kwarcowego. Dlatego

możliwe jest tylko jednokrotne zaprogramowanie pamięci bez

możliwości skasowanie jej zawartości.

FLASH (Bulk Erasable Non-Volatile Memory) - pamięci z

możliwością kasowanie zawartości i programowania

bezpośrednio w systemie mikroprocesorowym –

reprogramowalna.

SRAM (Static Random Access Memory) - pamięci RAM

statyczne.

Są to pamięci o krótkich czasach dostępu, prostsze w

obsłudze przez jednostkę centralną, ale droższe.

DRAM (Dynamic Random Access Memory) - pamięci RAM

dynamiczne. Sto pamięci tańsze, ale ich obsługa przez

jednostkę centralną jest bardziej skomplikowana. Polega to na

konieczności wykonywania w krótkich odstępach czasu

określonych operacji na pamięci (tzw. odświeżaniu). W

przeciwnym razie dane zawarte w pamięci dynamicznej zanikaj.

Zawartość pamięci nie zanika wraz z

wyłączeniem napicia zasilania.

Z pamięci można czytać, lecz nie można do

niej wpisywać danych. Umieszczanie

danych w pamięci wymaga specjalnego

procesu, zwanego programowaniem

.

.

TECHNIKA MIKROPROCESOROWA

TECHNIKA MIKROPROCESOROWA

Przegl

Przegl

ą

ą

d podstawowych typów

d podstawowych typów

pami

pami

ę

ę

ci

ci

Własnośc

Własnośc

i:

i:

Rodzaje

Rodzaje

:

:

Zawartość pamięci znika wraz z wyłączeniem

zasilania

Z pamięci można zarówno czytać jak i

wpisywać dane

TECHNIKA MIKROPROCESOROWA

TECHNIKA MIKROPROCESOROWA

Układy pamięciowe dzielą się na:

Układy pamięciowe dzielą się na:

•

pamięci ulotne

– trzymają dane tylko wtedy, gdy są

zasilane. Zanik napięcia

zasilania powoduje

utratę przechowywanych informacji

• pamięci nieulotne

- zachowane dane nie ulegają

skasowaniu po wyłączeniu

napicia zasilania

Pierwsza grupa to pamięci RAM (

Random Access Memory

Random Access Memory).

Są one pamięciami, w których dane mogą być zarówno

zapisywane, jak z niej odczytywane. Istnieją dwa główne

typy tych pamięci:

• pamięć STATYCZNA RAM (

SRAM

SRAM)

• pamięć DYNAMICZNA RAM (

DRAM

DRAM)

Pamięć RAM – rejestr D-

Pamięć RAM – rejestr D-

LATCH

LATCH

FP1 - FP8

3 - STATE

OUTPUTS

Q0 19

Q1 18

Q2 17

Q3 16

Q4 15

Q5 14

Q6 13

Q7 12

2 D0

3 D1

4 D2

5 D3

6 D4

7 D5

8 D6

9 D7

11 CP

1 OE

TECHNIKA MIKROPROCESOROWA

TECHNIKA MIKROPROCESOROWA

Pamięć

SRAM

SRAM - przechowuje bity informacji w

postaci stanów przerzutników bistabilnych. Każda

komórka pamięci składa się z około od 4 do 6

tranzystorów. Układy SRAM mogą mieć względnie

niski pobór mocy w trybie podtrzymywania

zawartoci pamięci, natomiast w trybie pracy

pobierają dość duży prąd. Zaletą tych pamięci jest

prostota sterowania oraz szybkość (pamięci te

wykonane z arsenku galu GaAs mają czas dostępu

poniżej 1 ns). Dziki prostemu sterowaniu sone

najczęściej stosowane w mikrosystemach

elektronicznych.

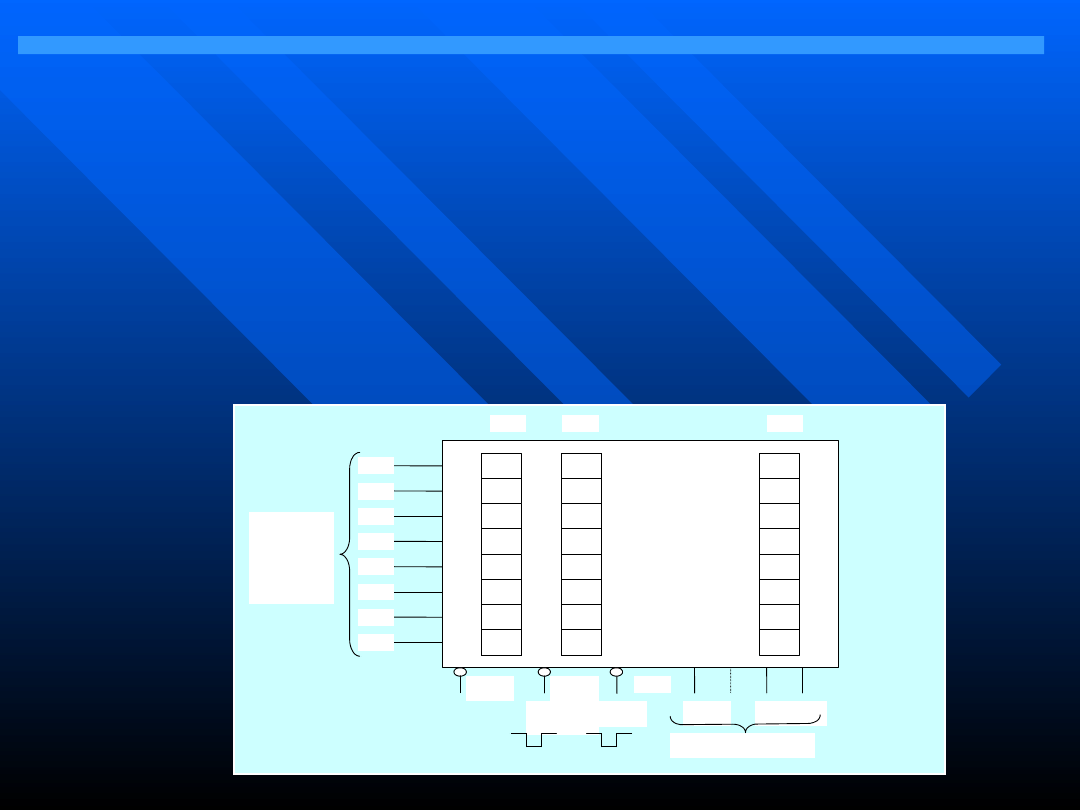

Szkic ogólny pamięci

RAM

1

0

0

0

0

1

1

1

1

0

1

0

1

0

1

0

D7

D6

D5

D4

D3

D2

D1

D0

1

0

m

8 - bitowa

szyna danych

A0

A1

An

Szyna adresowa

OE\

RD\

WE\

WR\

CE\

TECHNIKA MIKROPROCESOROWA

TECHNIKA MIKROPROCESOROWA

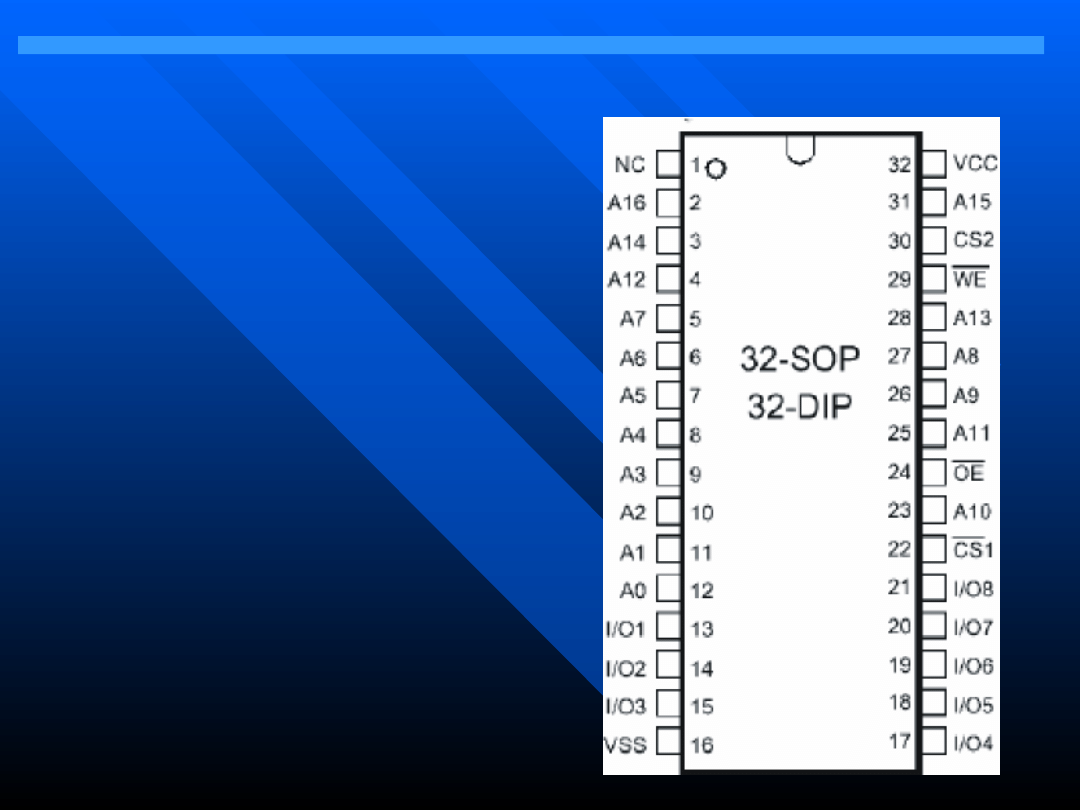

Pamięć SRAM przedstawiona jest na

przykładzie układu K6T008C2E firmy

Samsung Electronics. Jest to pamięć

SRAM o pojemności 28K x 8 bitów -

wykonana w technologii CMOS o

małym poborze mocy.

TECHNIKA MIKROPROCESOROWA

TECHNIKA MIKROPROCESOROWA

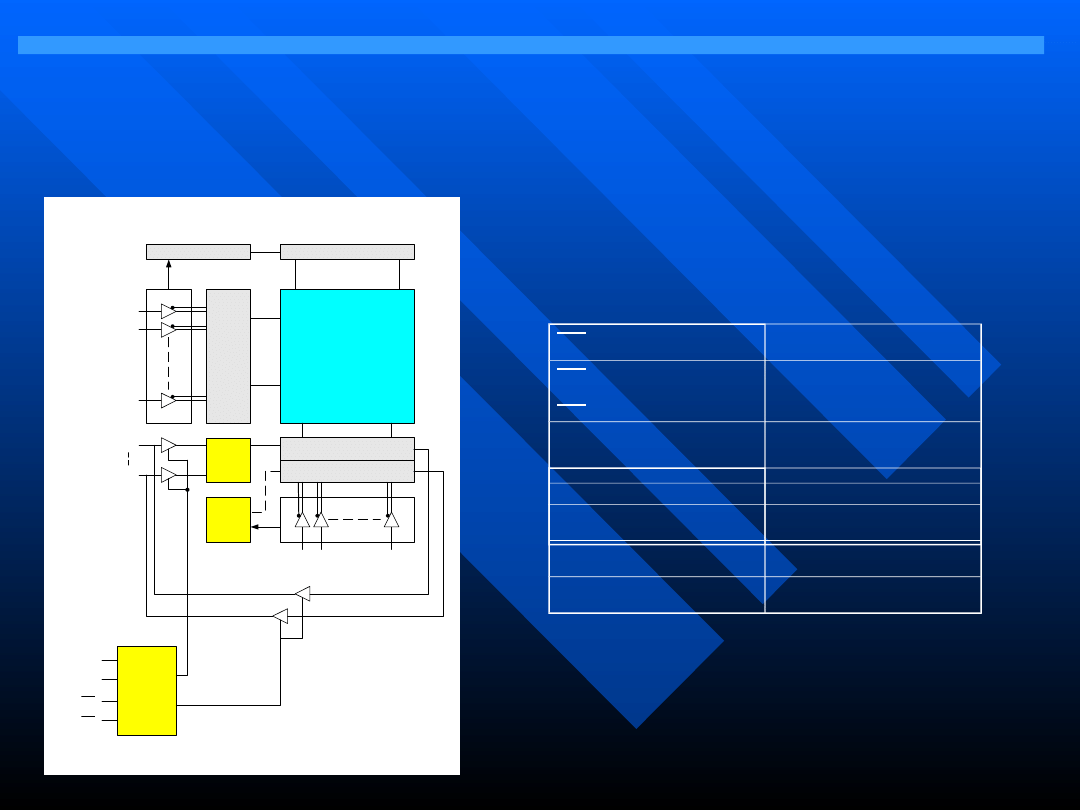

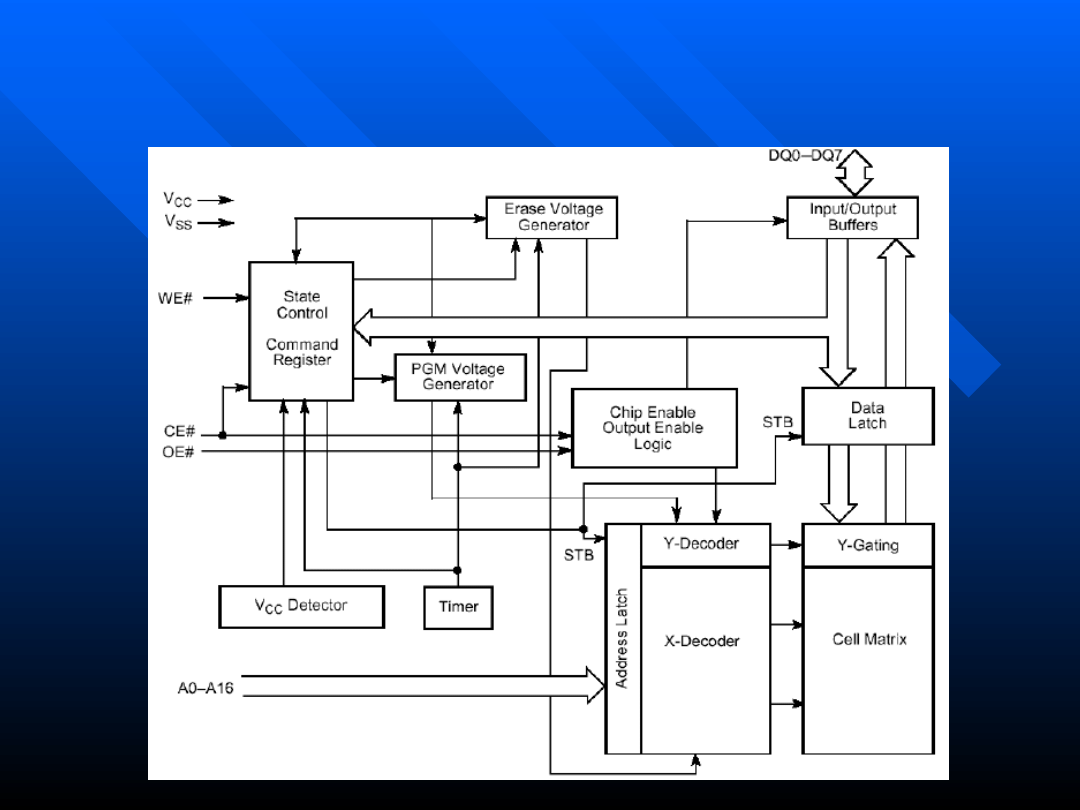

CLK GENERATOR

PRECHANGE CIRCUIT

MEMORY ARRAY

1024 rows

128 x 8 column

s

Row

Select

Row

Address

I/O CIRCUIT

COLUMN SELECT

DATA

CONTROL

DATA

CONTROL

COLUMN ADDRESS

I/O

0

I/O

7

CONTROL

LOGIC

CS1

CS2

WE

OE

Pamięć SRAM – schemat

Pamięć SRAM – schemat

blokowy

blokowy

Na przykładzie K6T008C2E

Funkcje sygnałów :

Nazwa: Funkcja:

CS1 , CS2

CS1 , CS2

Chip Select Input

Chip Select Input

OE

OE

Output Enable

Output Enable

Input

Input

WE

WE

Write Enable

Write Enable

Input

Input

I/O1 ~ I/O8

I/O1 ~ I/O8

Data

Data

Inputs/Outputs

Inputs/Outputs

A0 ~ A16

A0 ~ A16

Address Inputs

Address Inputs

Vcc

Vcc

Power

Power

Vss

Vss

Groud

Groud

NC

NC

No Connection

No Connection

TECHNIKA MIKROPROCESOROWA

TECHNIKA MIKROPROCESOROWA

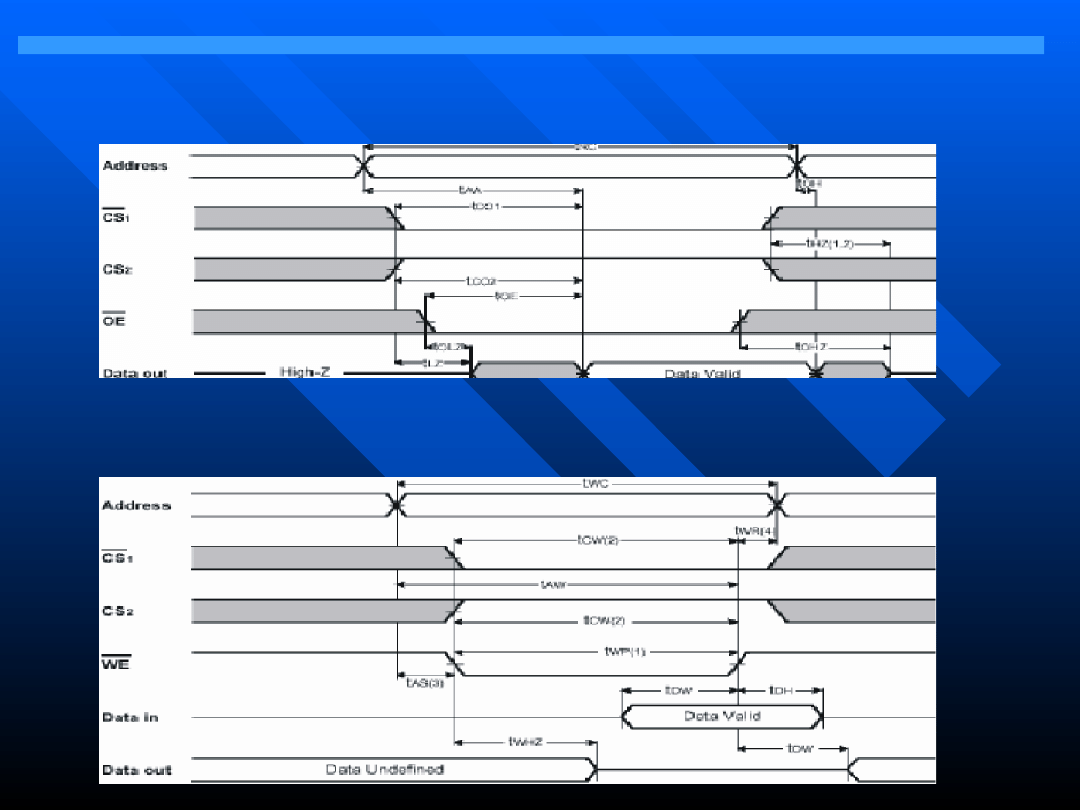

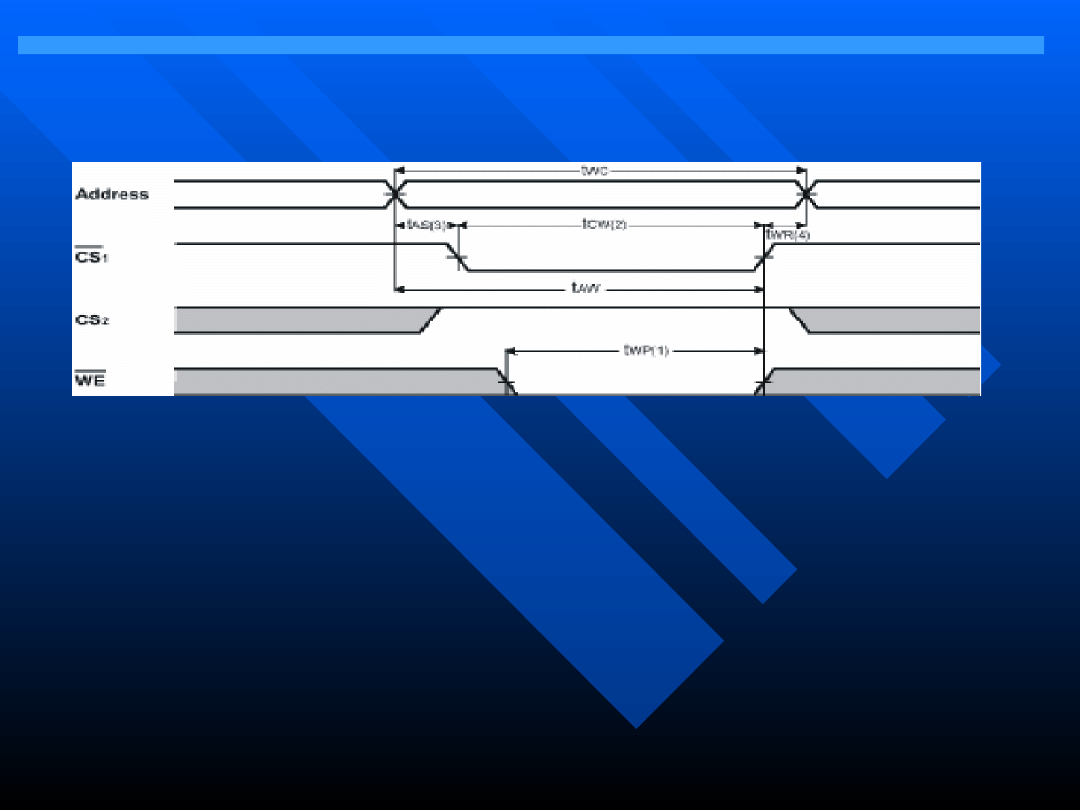

Przebiegi czasowe cyklu

Przebiegi czasowe cyklu

odczytu

odczytu

danych z pami

danych z pami

ę

ę

ci (sygna

ci (sygna

ł

ł

WE w

WE w

stanie Hi)

stanie Hi)

Przebiegi czasowe cyklu

Przebiegi czasowe cyklu

zapisu

zapisu

danych do pami

danych do pami

ę

ę

ci (sterowanie

ci (sterowanie

sygna

sygna

ł

ł

em WE

em WE

)

)

TECHNIKA MIKROPROCESOROWA

TECHNIKA MIKROPROCESOROWA

Przebiegi czasowe cyklu zapisu danych do pami

Przebiegi czasowe cyklu zapisu danych do pami

ę

ę

ci (sterowanie sygna

ci (sterowanie sygna

ł

ł

em CS1)

em CS1)

TECHNIKA MIKROPROCESOROWA

TECHNIKA MIKROPROCESOROWA

Podział pamięci ROM

Podział pamięci ROM

MROM

MROM (

mask rom

)

PROM

PROM

(

Programable ROM

)

• OTPROM (

One Time

Programable

ROM

)

• EEPROM (

Electrical Eraseable

Programable

ROM

)

• EPROM (

Eraseable

Programable

ROM

)

• FLASH (pamięć

błyskowa)

Pamięć EEPROM FLASH

Pamięć EEPROM FLASH

Pamięć ta posiada następujace właściwości:

Pamięć ta posiada następujace właściwości:

pojedyncze zasilanie, 5V +-10% dla czytania, zapisu i operacji

pojedyncze zasilanie, 5V +-10% dla czytania, zapisu i operacji

kasowania programu,

kasowania programu,

maksymalny czas dostępu 45ns,

maksymalny czas dostępu 45ns,

niskie zużycie energii, maksymalnie 30mA na odczyt i 50mA na

niskie zużycie energii, maksymalnie 30mA na odczyt i 50mA na

programowanie oraz czyszczenie, mniej niż 25

programowanie oraz czyszczenie, mniej niż 25

μ

μ

A podczas trybu

A podczas trybu

standby,

standby,

elastyczna architektura oparta na sektorach, 8 zunifikowanych

elastyczna architektura oparta na sektorach, 8 zunifikowanych

sektorów, wszystkie kombinacje sektorów mogą być czyszczone,

sektorów, wszystkie kombinacje sektorów mogą być czyszczone,

możliwość wymazania całego chipu,

możliwość wymazania całego chipu,

ochrona sektorów przed zapisem,

ochrona sektorów przed zapisem,

wsparcie sprzętowe dla zablokowania i odblokowania

wsparcie sprzętowe dla zablokowania i odblokowania

programowania i czyszczenia dla wszystkich kombinacji sektorów,

programowania i czyszczenia dla wszystkich kombinacji sektorów,

wbudowany algorytm czyszczenia automatycznie przeprogramuje i

wbudowany algorytm czyszczenia automatycznie przeprogramuje i

czyści chip lub wszystkie kombinacje wybranych sektorów,

czyści chip lub wszystkie kombinacje wybranych sektorów,

wbudowany algorytm programowania automatycznie programujący

wbudowany algorytm programowania automatycznie programujący

i sprawdzający dane z zadanego adresu,

i sprawdzający dane z zadanego adresu,

minimum 100000 gwarantowanych cykli programowania i

minimum 100000 gwarantowanych cykli programowania i

czyszczenia,

czyszczenia,

programowe metody detekcji końca cyklu programowania i

programowe metody detekcji końca cyklu programowania i

czyszczenia.

czyszczenia.

TECHNIKA MIKROPROCESOROWA

TECHNIKA MIKROPROCESOROWA

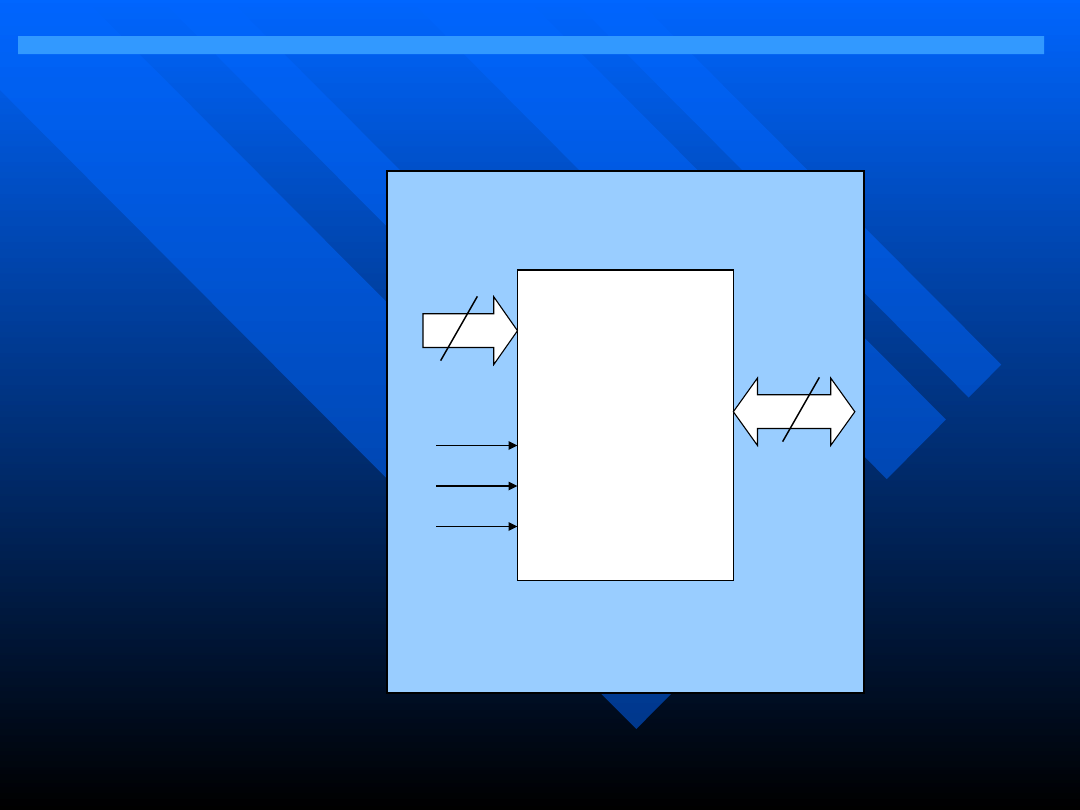

AA0-A16 0

-A16

DQ0-

DQ7

CE#

-DQ7

OE#

WE#

17

8

Symbol logiczny pamięci

Symbol logiczny pamięci

FLASH

FLASH

A0-A16 = 17 Adresses

Dqo-DQ7 = 8 Data

Inputs/Outputs

CE# = Chip Enable

OE# = Output Enable

WE# = Write Enable

Vcc = +5.0 V Single

Power Supply

Vss = Device Ground

NC = Pin Not

Connected

Internally

Pamięć EEPROM FLASH

Pamięć EEPROM FLASH

TECHNIKA MIKROPROCESOROWA

TECHNIKA MIKROPROCESOROWA

Szczególną zaletą pamięci błyskowych (FLASH) w stosunku do

pamięci EEPROM jest krótki czas kasowania i zapisu. Do

programowania i kasowania pamięci byskowych potrzebne jest

podwyższone napięcie ,5 - 3,5V, które w zalenoci od typu ukadu

może być podawane z zewnątrz lub wytwarzane przez wbudowaną

przetwornicę.

Aby odczytać dane z pamięci, system musi zapewnić niski stan linii

CE# i OE#. Linia CE# kontroluje odczyt. Linia OE# steruje

buforem wyjciowym. Sygnał na linii WE# powinien być na poziomie

VIH.Żadna komenda nie jest wymagana w tym trybie. Jest on

trybem domyślnym po włączeniu napięcia zasilania. Zatem mk

może podawać na linie adresowe A0 – A6 adresy danych, które

chce otrzymać na liniach danych DQ0 – DQ7. Urzdzenie pozostaje

dostępne do odczytu dopóki nie zmieni się zawartość rejestru

komend.

Aby zapisać komendę lub sekwencję komend (które zawierają dane

programujące czy czyszczące wybrane sektory pamięci), system

musi zapewnić nastpujce stany: na liniach WE# i CE# stan niski

VIH

oraz na linii OE# stan wysoki VIH .

TECHNIKA MIKROPROCESOROWA

TECHNIKA MIKROPROCESOROWA

• Pamięć ta posiada tryb

autoselect

autoselect

- umożliwia on identyfikację

urzdzenia oraz

producenta, a także weryfikację chronionych

sektorów przez kody identyfikacyjne podane na DQ7-DQ0.

• Ten tryb jest niezbędny dla urządzeń programujcych, aby mogły

wykorzystaćdpowiedni algorytm programujący. Ten tryb może

być także

wykorzystany w

systemie przez rejestr komend.

• Programowanie pamięci składa się z 4 cykli szyny (rozkaz

PROGARM). Na

sekwencję rozkazową składa się rozkaz

ustawiający tryb programowania

poprzedzony zapisem 2 cykli

odblokowujących. Dane i adres swysyłane w

następnej

kolejnoci. Operacja ta inicjuje wykonanie wbudowanego algorytmu

programowania.

• Sekwencja kasowania pamięci składa się z 6 cykli szyny. W jej skad

wchodzi rozkaz

ustawienia (set-up) poprzedzony zapisem 2 cykli

odblokowujących. Po nich

następują kolejne 2 cykle odblokowujące

zapis i rozkaz kasowania, który

uruchamia wbudowany algorytm

kasowania.

TECHNIKA MIKROPROCESOROWA

TECHNIKA MIKROPROCESOROWA

Przebieg czasowy operacji odczytu z pamięci

Am29F00

Przebieg czasowy operacji programowania pamięci

Am29F00

TECHNIKA MIKROPROCESOROWA

TECHNIKA MIKROPROCESOROWA

Przebieg czasowy operacji kasowania pamici

Am29F00

TECHNIKA MIKROPROCESOROWA

TECHNIKA MIKROPROCESOROWA

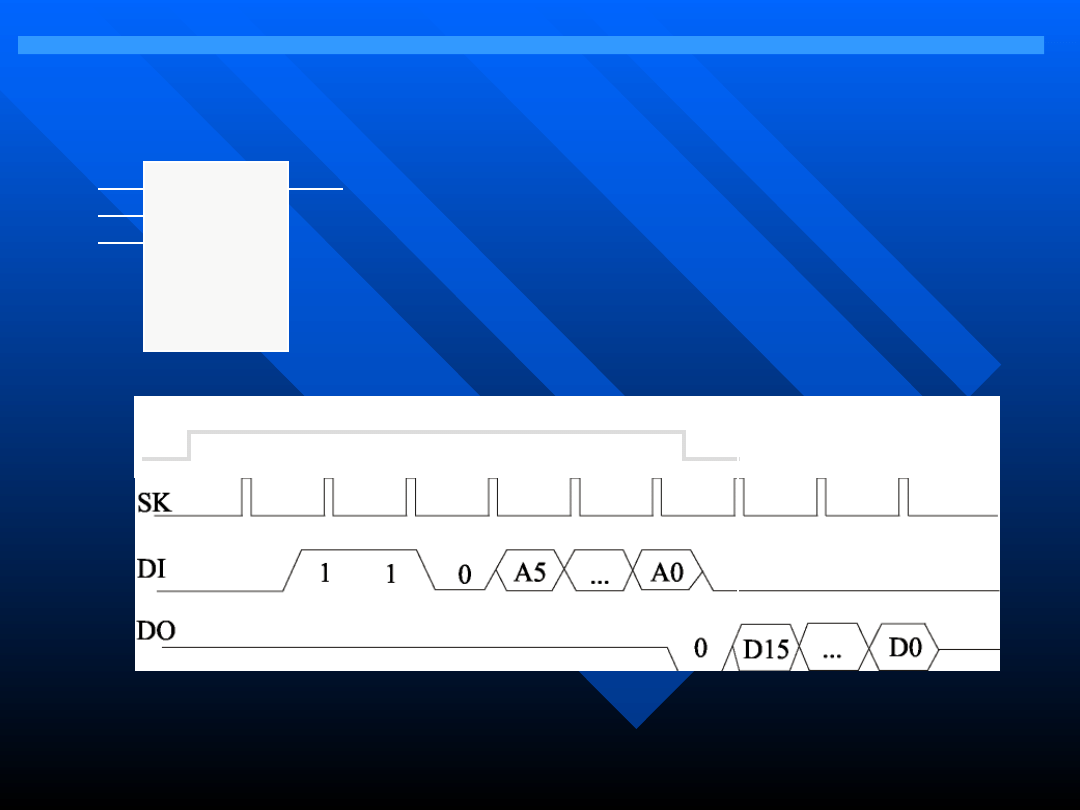

PAMIĘĆ EEPROM

PAMIĘĆ EEPROM

DI

SK

CS

D

O

• CS - chip select – wybór układu.Podanie stanu

1 powoduje

uaktywnienie pamięci EEPROM

• SK - serial clock-zegar transmisji.Impulsy

podawane na to

wejście taktują

przesyłanie danych

• DI - data input – wejście danych

• DO – data output – wyjście danych

CS

TECHNIKA MIKROPROCESOROWA

TECHNIKA MIKROPROCESOROWA

• Pamięci

EEPROM

EEPROM są układami, które nie tylko są elektrycznie

programowalne, ale również

elektrycznie kasowane.

• Mają ograniczoną liczbę cyklów programowania od około 10000

razy do 1000000 razy.

• Komórka pamięci EEPROM składa się z tranzystora NMOS (Metal

Nitride Oxide Semiconductor). Do kadżej komórki można wprowadzić

ładunek elektryczny,

który przechowywany jest w izolowanej

warstwie azotku krzemu, znajdujcej się

między bramką

tranzystora, a podłożem z tlenku krzemu. Ładowanie inicjuje

się

poprzez

tzw. efekt tunelowy. Powstaje on po przyłożeniu

wysokiego

napięcia (20-40V) do bramki tranzystora. Przez zmianę

polaryzacji tego

napięcia, układ można programować, bądź też

kasować.

TECHNIKA MIKROPROCESOROWA

TECHNIKA MIKROPROCESOROWA

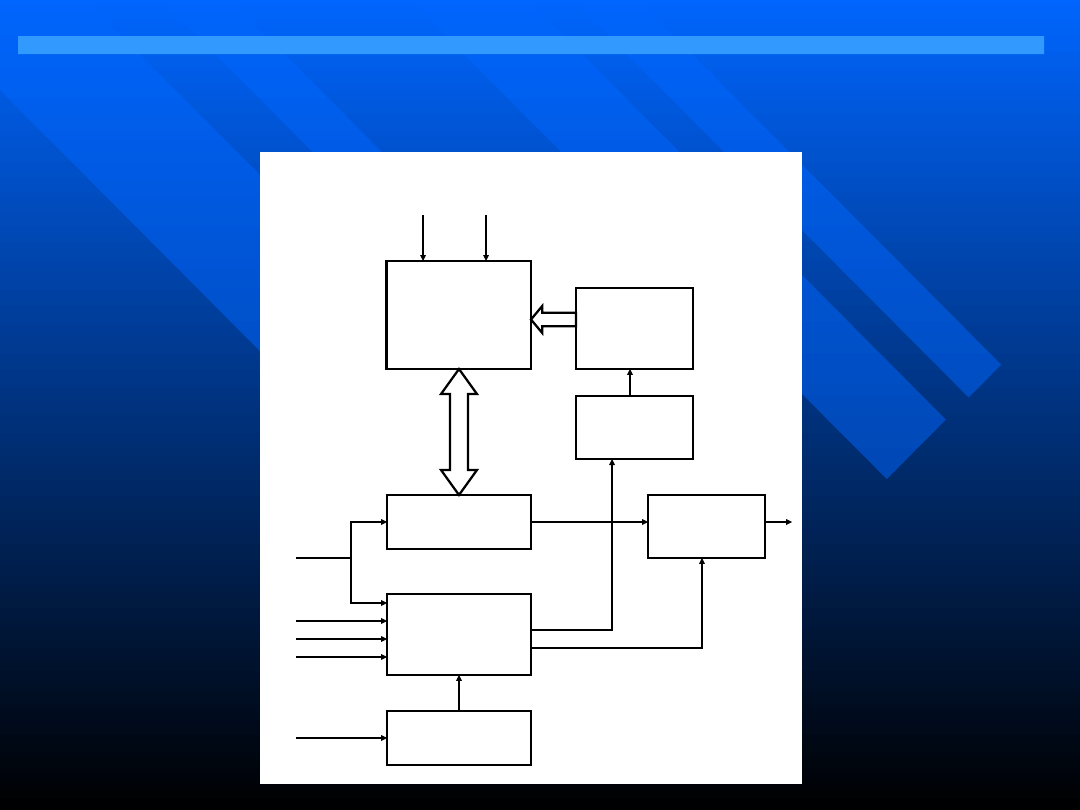

DATA REGISTER

ADRES

COUNTER

OUTPUT BUFFER

MEMORY ARRAY

256 x 16

ADRESS

DECODER

MODE

DECODE

LOGIC

CLOCK GENERATOR

DO

Vcc

Vss

DI

PRE

PE

CS

CLK

Schemat blokowy EEPROM

Schemat blokowy EEPROM

TECHNIKA MIKROPROCESOROWA

TECHNIKA MIKROPROCESOROWA

TECHNIKA MIKROPROCESOROWA

TECHNIKA MIKROPROCESOROWA

TECHNIKA MIKROPROCESOROWA

TECHNIKA MIKROPROCESOROWA

Łączenie pamięci

Łączenie pamięci

statycznych

statycznych

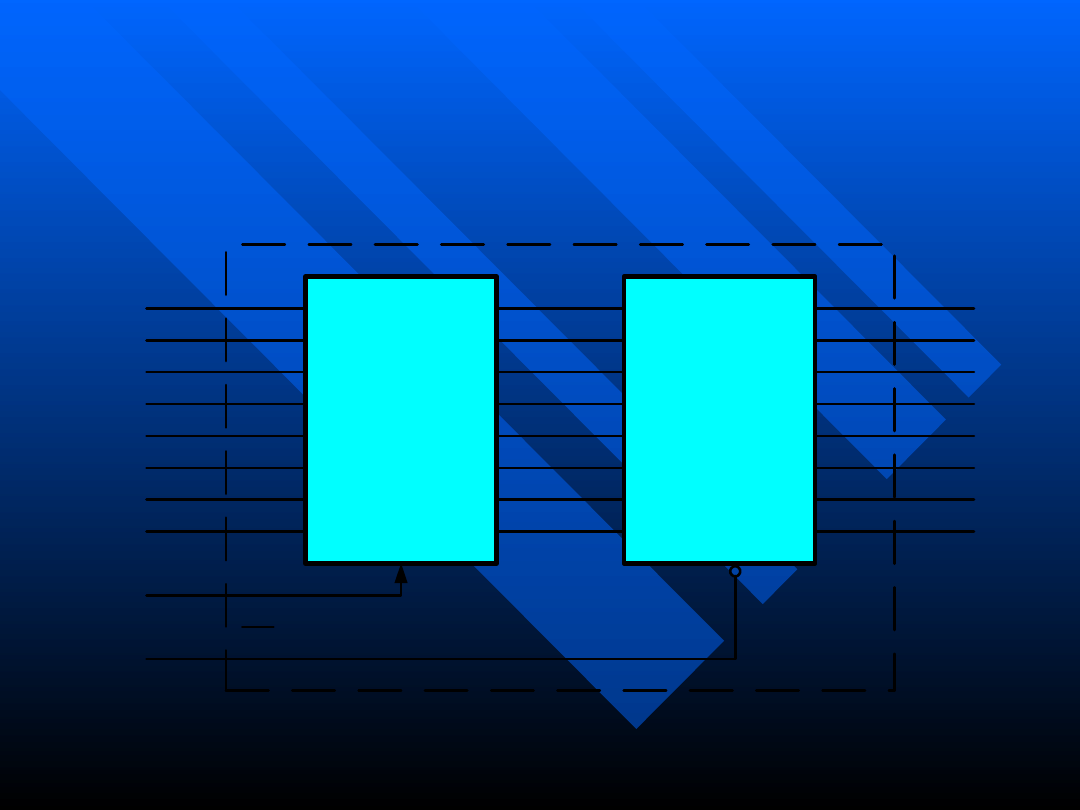

Układy pamięci RAM zbudowane są z elektronicznych elementów, które mogą

zapamiętać swój stan. Dla każdego bitu informacji potrzebny jest jeden taki

układ. W zależności od tego czy pamięć RAM jest tak zwaną statyczną

pamięcią (SRAM-Static RAM), czy dynamiczną (DRAM-Dynamic RAM)

zbudowana jest z innych komponentów i soje działanie opiera na innych

zasadach. Pamięć SRAM jako element pamiętający wykorzystuje przerzutnik,

natomiast DRAM bazuje najczęściej na tzw. pojemnościach pasożytniczych

(kondensator

).

).

Budowa

Budowa

:

:

•

Aby zorganizować komórki pamięci w sprawnie funkcjonujący układ,

należy je odpowiednio

zaadresować. Najprostszym sposobem jest

zorganizowanie pamięci liniowo - jest to tak

zwane adresowanie

2D . Do każdej komórki podłączone jest wejście, sygnał wybierania

pochodzący z dekodera oraz wyjście.

•

Nieco innym sposobem jest adresowanie przy użyciu tzw. matrycy

3D.Pamięć organizuje się

tutaj dzieląc dostępne elementy na wiersze i

kolumny. Dostęp do pojedynczego elementu

pamiętającego można

uzyskać po zaadresowaniu odpowiedniego wiersza i kolumny.

TECHNIKA MIKROPROCESOROWA

TECHNIKA MIKROPROCESOROWA

Dlatego też komórka RAM obok wejścia i wyjścia musi dysponować

jeszcze dwoma sygnałami wybierania, odpowiednio z dekodera kolumn i

wierszy.Zaletą pamięci adresowanej liniowo jest prosty i szybszy dostęp do

poszczególnych bitów niż w przypadku pamięci stronicowanej (3D), lecz

niestety, przy takiej organizacji budowanie większych modułów RAM jest

kłopotliwe.

Dlatego też w przemyśle stosuje się zazwyczaj układy pamięci zorganizowanej

w matrycę 3D, pozwala to na nieskomplikowane tworzenie większych modułów

o jednolitym sposobie adresowania.

Document Outline

- Slide 1

- Slide 2

- Slide 3

- Slide 4

- Slide 5

- Slide 6

- Slide 7

- Slide 8

- Slide 9

- Slide 10

- Slide 11

- Slide 12

- Slide 13

- Slide 14

- Slide 15

- Slide 16

- Slide 17

- Slide 18

- Slide 19

- Slide 20

- Slide 21

- Slide 22

- Slide 23

- Slide 24

- Slide 25

- Slide 26

- Slide 27

Wyszukiwarka

Podobne podstrony:

PODSTAWY TECHNIK MIKROPROCESOROWYCH, Studia Pwr INF, Semestr IV, PTM

C1 Techniki mikroprocesorowe sprawozdanie

Podstawy techniki mikroprocesor Nieznany

zadania egzaminacyjne dzienne (PTM), elektro, 1, Podstawy Techniki Mikroprocesorowej

80C51 pytania i odpowiedzi, elektro, 1, Podstawy Techniki Mikroprocesorowej

zadania egzaminacyjne zaoczne 2006 07 (PTM), elektro, 1, Podstawy Techniki Mikroprocesorowej

Egzamin z PTC podst kombinacyjne, elektro, 1, Podstawy Techniki Mikroprocesorowej

C2 Techniki mikroprocesorowe sprawozdanie

Technika mikroprocesorowa

Zagadnienia do egzaminu z Elektroniki i Technik Mikroprocesorowych

cw03spp, Przwatne, Studia, Semestr 3, Technika Mikropocesorowa

TECHNIKA MIKROPROCESOROWA (1), Edukacja, studia, Semestr IV, Technika Mikroprocesorowa

Technika Mikroprocesorowa, tup-cw 4, Program 1:

Technika mikroprocesorowa projekt(1)

7 Zastosowanie techniki mikroprocesorowej II

więcej podobnych podstron