Politechnika Lubelska |

Laboratorium podstaw elektroniki |

|||

w Lublinie |

Ćwiczenie nr 9 |

|||

Sidor Piotr Bernard Jagieło

|

Semestr IV |

Grupa: ED 4.3 |

Rok akademicki: 1996/97 |

|

Temat ćwiczenia: Bramki logiczne TTL |

Data wykonania: 14.05.1997 |

Ocena: |

||

Wyznaczanie charakterystyk statycznych bramki NAND

Schemat pomiarowy

Tabela pomiarów

u |

v |

0 |

1 |

1.25 |

2 |

2.25 |

3 |

4 |

4.5 |

I |

mA |

-6.5 |

-0.4 |

0 |

0.4 |

0.5 |

0.6 |

0.8 |

0.98 |

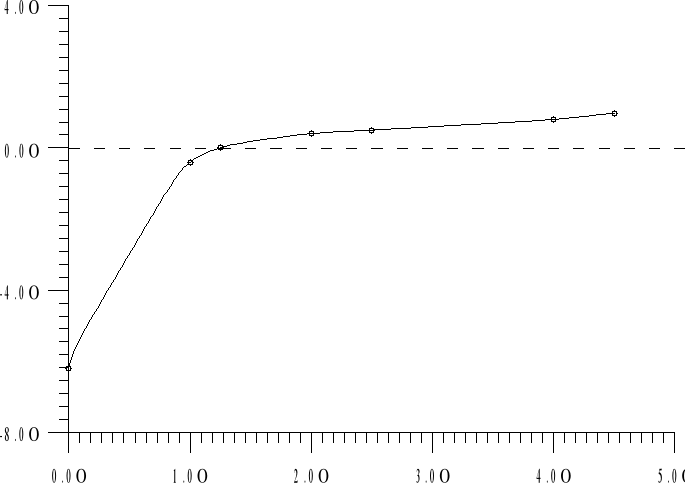

Charakterystyka wejściowa

Wyznaczanie charakterystyki przełączania

Schemat pomiarowy

Wyniki pomiarów

U0 |

V |

3.28 |

2,54 |

0.8 |

0.081 |

0.081 |

0.081 |

U1 |

V |

0 |

1 |

1,5 |

2 |

3 |

4 |

Icc |

mA |

4.5 |

4.8 |

23 |

5,3 |

5 |

5 |

Wnioski:

W ćwiczeniu badamy właściwości bramki typu NAND . Wyznaczamy ich charakterystyki statyczne, dzięki nim można określić podstawowe parametry tych bramek.

Stany wyjściowe 0, 1 uzyskuje się przy pewnych zakresach napięć wejściowych wartość tego napięcia powinna znajdować się w pewnym przedziale . Jednocześnie powinien być zachowany pewien odstęp w obszarze przejściowym dzięki czemu zwiększa się odporność bramki na zakłócenia .Wartość napięcia wejściowego interpretowanego jako 1 na wejściu zawiera się w granicy (2; 5) [V] na wyjściu (2,4 ;5), a 0 logiczne na wejściu (-0.5 ; 0,8 ) i wyjściu (0 ;0,4 ).Stanie włączenia na obydwóch wejściach jest poziom H powoduje to że na wyjściu jest poziom L . Gdy choć na jednym wejściu jest poziom L to na wyjściu mamy H .

Zasadę działania tej bramki oraz bramek typu OR , EX-OR w zależności od poziomu logicznego na wejściu obrazują tablice stanów.

Z charakterystyk wejściowych przedstawia zależność prądu wejściowego od napięcia

na wejściu bramki ,Mamy tam dwa obszary do U=1,4 prąd wejściowy wypływa z bramki

, powyżej tego napięcia prąd stopniowo zwiększa się ( wpływa do bramki ).Na charakterystyce przełączania mamy trzy zakresy od 2 [V]na wyjściu jest stan niski, od zera do 1.4 stan wysoki

a, pomiędzy 1.3 do 1.9 następuje okres przełączania.

Zależność prądu od obciążenia jest przedstawiona na charakterystyce wyjściowej w stanie 1 im bardziej bramka jest obciążana tym napięcie wyjściowe proporcjonalnie maleje.

Z charakterystyki poboru prądu (dla około 1,5 [V] ) w czasie przełączania widoczny jest bardzo duży skok poboru prądu .Spowodowany on jest tym ,że tranzystor T4 wychodzi z nasycenia a przy dużej wartości ładunku zgromadzonego w nim dzięki temu możliwe jest przejście w nasycenie tranzystora T3 czyli oba tranzystory przewodzą . Spowoduje to przejściowe zwiększenie prądu pobieranego przez bramkę.

U [V]

I [mA]

Wyszukiwarka