Dodatek B

1 Magistrala 1-Wire

Ciągle rosnąca liczba układów peryferyjnych podłączanych do mikroprocesorów zmusza

konstruktorów do opracowywania nowych interfejsów. Drugą przyczyną powstawania

nowych rozwiązań są ograniczenia patentowe obowiązujące dla już istniejących. Jednym

z takich przykładów jest magistrala 1-Wire opracowana przez firmę Dallas Semiconductors

(obecnie Maxim-Dallas). Oryginalność tego rozwiązania polega na wykorzystaniu jedynie

dwóch przewodów. Jeden z nich to dwukierunkowa linia transmisyjna, drugi zaś to przewód

odniesienia (masa). Większość układów peryferyjnych opracowanych również przez firmę

Dallas zwanych układami iButton, nie wymaga zasilania, czerpiąc całą energię

z transmitowanych sygnałów. Przykładem takich układów mogą być „pastylki identyfikujące”

DS1992 (Fot. 1).

Fot. 1. Układ iButton DS1992 oraz gniazdo-czytnik.

Zasadniczą częścią układu DS1992 jest pamięć ROM, w której na etapie produkcji zapisano

niepowtarzalny, 48-bitowy numer seryjny. W drugiej części układ posiada zapisywalną

pamięć typu NVRAM, umożliwiającą przechowywanie krótkich informacji. Pojemność tej

pamięci wynosi 1024 bity i podzielona jest na strony po 256 bitów każda.

Właściwości układów z serii DS199x sprawiają, że nadają się one np. do identyfikowania

posiadacza. Oczywiście numer seryjny zapisany w ROM każdego układu jest jawny, co jest

widoczne na fot. 1. i zmusza posiadacza do zabezpieczenia układu przed dostaniem się

w niepowołane ręce.

2 Protokół komunikacyjny magistrali 1-Wire.

Współpraca układów podłączonych do magistrali 1-Wire przebiega na zasadzie „master-

slave”, czyli jest zawsze jeden układ nadrzędny (master) i co najmniej jeden układ podrzędny

(slave). Transmisja odbywa się poprzez odpowiednio określone szczeliny czasowe (slots).

Wyróżnić można cztery rodzaje szczelin czasowych.

2.1 Szczelina inicjująca.

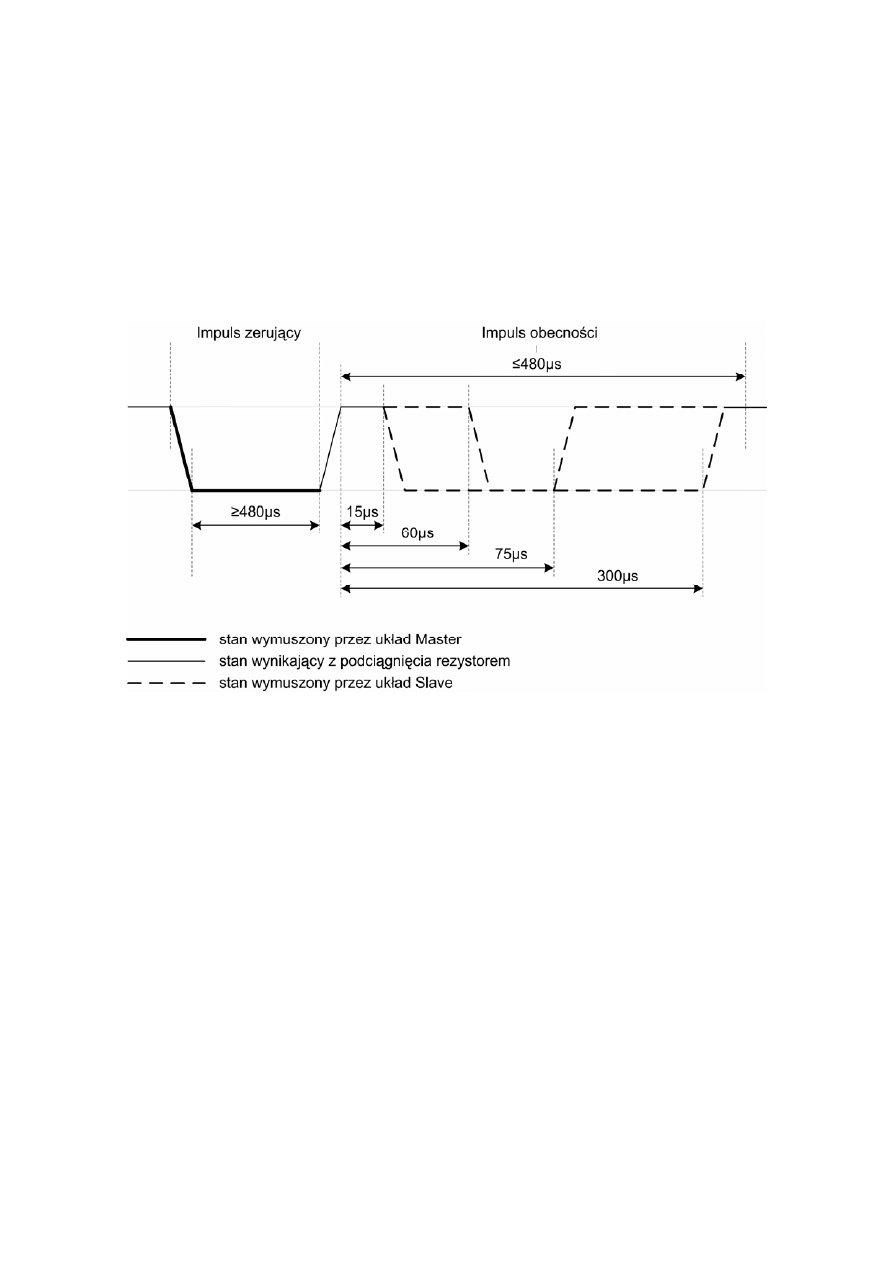

Pierwszą z nich jest szczelina inicjująca. W pierwszej fazie tej szczeliny, zwanej impulsem

zerującym, układ nadrzędny wystawia niski stan na linii transmisyjnej na czas nie krótszy niż

480µs. Następnie układ nadrzędny zwalnia linię poprzez ustawienie stanu wysokiego.

Po upływie kolejnych 60µs układy podrzędne powinny zgłosić swoją obecność przez

wystawienie stanu niskiego na linii. Stan ten powinien być utrzymywany przez co najmniej

15µs lecz nie więcej niż 240µs. Tę fazę nazywamy impulsem obecności i może ona trwać

maksymalnie 480µs. Odpowiednie przebiegi czasowe przedstawia rys. 1.

Rys. 1. Przebiegi czasowe na linii transmisyjnej podczas szczeliny inicjującej.

2.2 Szczelina zapisu „1”.

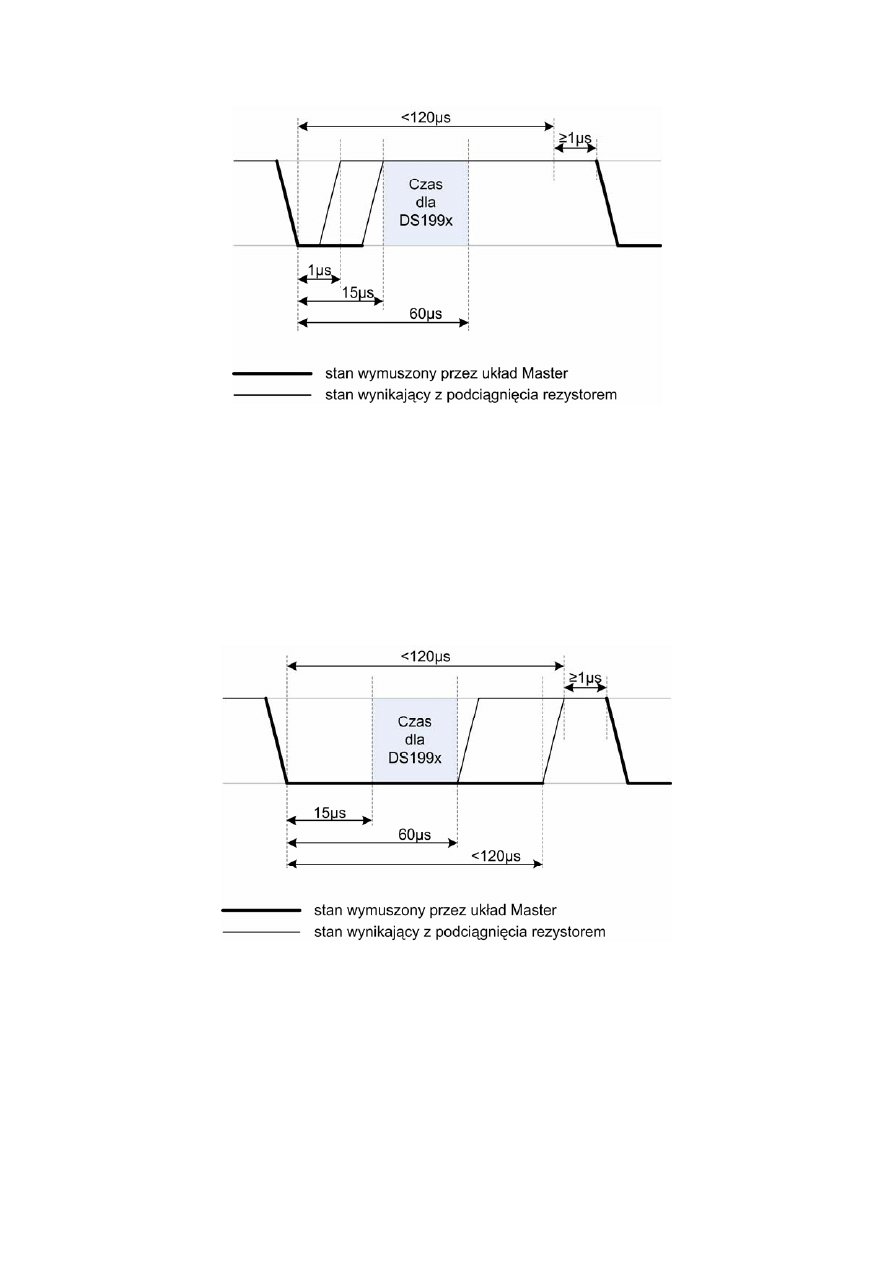

Ten typ szczeliny rozpoczyna się wystawieniem stanu niskiego na linię transmisyjną przez

układ nadrzędny. Czas trwania tego stanu musi wynosić co najmniej 1µs lecz mniej niż 15µs.

Następnie układ nadrzędny zwalnia linię dzięki czemu na linii pojawia się stan wysoki.

Począwszy od piętnastej mikrosekundy do sześćdziesiątej mikrosekundy układy podrzędne

mają czas na odczyt stanu linii (okno próbkowania - ang. sampling window). W tym czasie

stan linii nie powinien się zmieniac. Odpowiednie przebiegi przedstawia rys. 2.

Rys. 2. Przebiegi czasowe na linii transmisyjnej podczas szczeliny zapisu „1”.

2.3 Szczelina zapisu „0”.

Podczas trwania tego typu szczeliny układ nadrzędny wystawia stan niski na linii

transmisyjnej i utrzymuje go przez co najmniej 60µs lecz krócej niż 120µs. Układy podrzędne

mogą odczytywać stan linii między piętnastą a sześćdziesiąta mikrosekundą trwania

szczeliny. Odpowiednie przebiegi przedstawia rys. 3.

Rys. 3. Przebiegi czasowe na linii transmisyjnej podczas szczeliny zapisu „0”.

2.4 Szczelina odczytu.

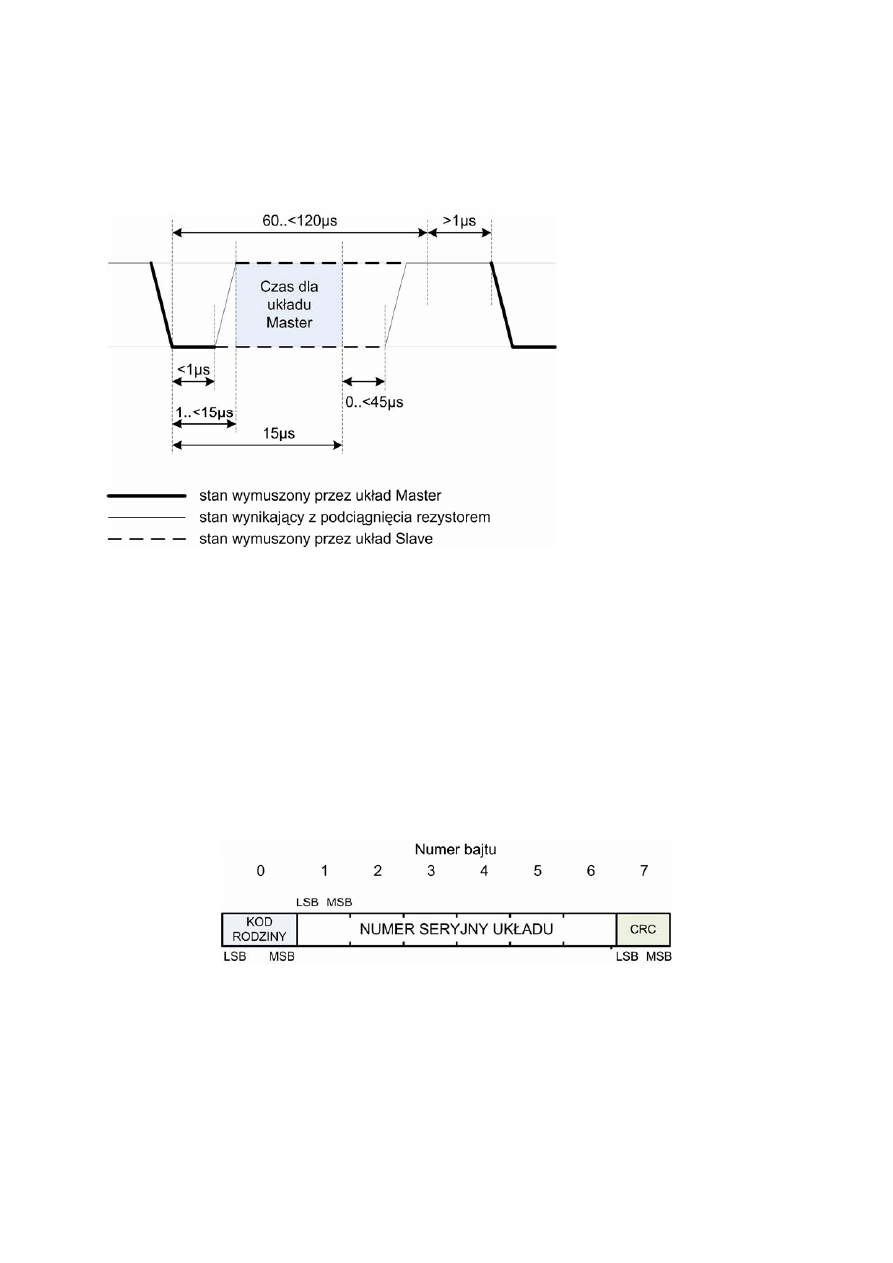

Szczelina czasowa tego typu rozpoczyna się wystawieniem przez układ nadrzędny stanu

niskiego na czas co najwyżej 1µs. Następnie układ nadrzędny zwalnia linię i przechodzi

w stan odczytu. Okno próbkowania stanu linii przez układ nadrzędny trwa do piętnastej

mikrosekundy trwania szczeliny. Układ podrzędny może utrzymywać stan linii nie dłużej niż

przez 45µs od momentu zakończenia okna próbkowania. Odpowiednie przebiegi przedstawia

rys. 4.

Rys. 4. Przebiegi czasowe na linii transmisyjnej podczas szczeliny odczytu.

Zapis lub odczyt danych po magistrali 1-Wire odbywa się przez złożenie odpowiednich

szczelin czasowych. Przykładowo aby odczytać numer seryjny układu DS199x należy

postępować zgodnie z następującym algorytmem:

• Układ nadrzędny wysyła szczelinę inicjującą.

• Jeżeli podczas szczeliny inicjującej układ podrzędny potwierdzi swoją obecność, to

układ nadrzędny przystępuje do wysłania rozkazu np. „czytaj ROM” (0x33).

• Następnie układ nadrzędny przechodzi do odczytywania danych z układu

podrzędnego, który wystawia kolejno 64 bity. Ich znaczenie obrazuje rys. 5.

Rys. 5. Znaczenie poszczególnych bajtów wystawianych przez układ podrzędny podczas

wykonywania rozkazu „czytaj ROM”.

3 Rozkazy obsługi pamięci ROM

Pierwszym etapem komunikacji systemu mikroprocesorowego (master) z układami iButton

(slave) jest wysłanie sygnału RESET i sprawdzenie, czy do linii są podłączone (wstawione

do czytników) jakieś układy iButton. Jeżeli jakieś układy zasygnalizują swoją obecność,

master wysyła jeden z czterech rozkazów obsługi ROM. Każdy rozkaz składa się z 8 bitów,

wysyłanych w linię kolejno, począwszy od najmłodszego. Układy DS1990 zawierają

wyłącznie pamięć ROM, a zatem nie wykorzystują rozkazów 55H ani CCH.

3.1 Czytaj ROM [33h]

Po wysłaniu tego rozkazu master powinien wykonać operacje odczytu kolejnych 64 bitów

(zawartość pamięci ROM układu iButton) wysyłanych przez slave'a kolejno, począwszy

od najmłodszego. W układach DS199x będą to kolejno:

• 8 bitowy kod rodziny urządzeń

• unikalny 48 bitowy numer urządzenia

• 8 bitowe słowo sumy kontrolnej (CRC).

Rozkazu tego można użyć wyłącznie w przypadku, gdy do linii dołączone jest tylko jedno

urządzenie – w przeciwnym wypadku wszystkie urządzenia będą się zgłaszać jednocześnie,

a na linii sygnałowej pojawi się iloczyn logiczny (wired-AND) stanów wyjściowych

poszczególnych urządzeń. Taką sytuację można wykryć przez porównanie odebranej

i wyliczonej sumy kontrolnej.

3.2 Wybierz układ [55h]

Po wysłaniu tego rozkazu, a następnie sekwencji 64 bitów zgodnej z zawartością pamięci

ROM, mamy możliwość wyboru określonego urządzenia spośród kilku dołączonych

jednocześnie do linii. Tylko to urządzenie, którego zawartość ROM jest zgodna z wysłaną

sekwencją, będzie odpowiadać na następne rozkazy. Wszystkie pozostałe układy przechodzą

w stan oczekiwania na sygnał RESET.

3.3 Pomiń identyfikację [CCh]

W przypadku pojedynczego urządzenia dołączonego do linii można użyć tego rozkazu

zamiast sekwencji odbioru zawartości pamięci ROM (po rozkazie 33h) lub jej wysyłania

(po rozkazie 55h).

3.4 Zidentyfikuj układy [F0h]

Po uruchomieniu systemu master nie ma informacji ile urządzeń jest dołączonych do linii, ani

jakie są ich kody identyfikacyjne. Rozkaz F0h umożliwia przeprowadzenie procesu

identyfikacji wszystkich urządzeń dołączonych do linii. Proces ten polega na powtarzaniu

przez master sekwencji trzech kolejnych kroków:

• wczytanie wartości bitu (wire-AND stanów wywołanych przez wszystkie dołączone i

aktywne urządzenia),

• wczytanie wartości komplementarnej tego bitu,

• wysłanie odpowiedniej wartości bitu. Urządzenia, dla których bit ten nie jest zgodny

z ich aktualnym bitem w pamięci ROM, przechodzą w stan WAIT. (czekania na

RESET).

Master wykonuje tę sekwencję dla wszystkich 64 bitów kodu identyfikacyjnego, uzyskując

w ten sposób kod jednego urządzenia. Następne przebiegi ( RESET + F0h) pozwalają

na identyfikację kolejnych urządzeń przez odpowiedni dobór wysyłanych bitów.

4 Realizacja interfejsu 1-Wire z wykorzystaniem

mikroprocesora ATMega128.

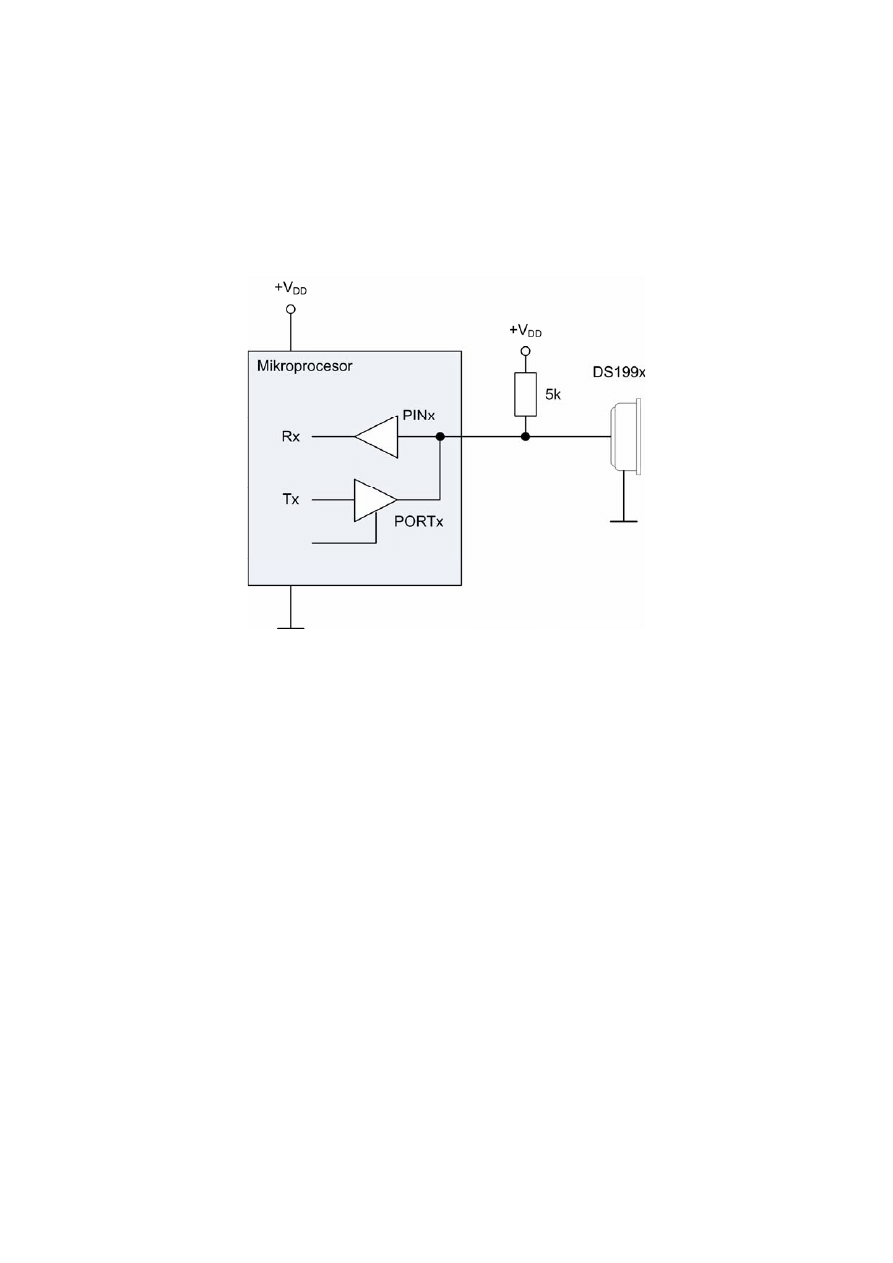

Do zapewnienia poprawnej transmisji potrzebny jest jedynie jeden port dwukierunkowy

z wyjściem „open drain”. Te wymagania spełnia większość portów procesora ATMega128.

Sposób dołączenia układów iButton do portu mikroprocesora zostało przedstawione na rys. 6.

Rys. 6. Sposób dołączenia układów iButton do portu mikroprocesora.

Obsługa linii transmisyjnej jest troszeczkę nietypowa, co wynika ze specyfiki interfejsu.

Wykorzystywana linia portu musi być skonfigurowana jako „wejście” bez wewnętrznego

„podciągania”. Odpowiedni bit portu PORTx musi być ustawiony na stałe na zero (linia Tx

na rys. 5). Realizacja stanu wysokiego na linii transmisyjnej jest uzyskiwane poprzez

ustawienie linii portu mikroprocesora jako wejście (odpowiedni bit rejestru DDRx ustawiony

na zero), dzięki czemu zewnętrzny rezystor podciągający wymusi stan wysoki. Natomiast stan

niski jest realizowany poprzez przełączenie linii portu na wyjście (odpowiedni bit rejestru

DDRx ustawiony na jeden), dzięki czemu uprzednio ustawione zero na odpowiednim bicie

rejestru PORTx wymusi stan niski na linii interfejsu. W przypadku odczytu stanu linii

transmisyjnej interfejsu 1-Wire przez mikroprocesor należy ustawić linię portu jako wejście

i odczytać odpowiedni bit rejestru PINx.

Wyszukiwarka

Podobne podstrony:

Magistrala 1 Wire Opis warstwy fizycznej interfejsu

Lokalizator ultradźwiękowy z wykorzystaniem magistrali 1 wire

wire chip SERWER POMIARU TEMPERATURY Z MAGISTRALĄ 1 WIRE

Magistrala v1

z8-opis plyty kompaktowej zawierajacej prace dyplomowa, AGH, Semestr 10, Magisterka

12.5. Energia jądrowa [v1.2], dodatek A5

Czesc III - opis jazy na rzece, PW IŚ, Magister, Sem I, metalowe konstrukcje hydrotechniczne, Projek

1 Wire Projekt V1 0id 10365 Nieznany

dodatek B Kr tki opis języka HTML

Opis przypadku, Magisterka materiały, Dydaktyka

Załącznik 1 - Opis wynalazku, Praca magisterska, Pozsostałe

12 5 Energia jądrowa [v1 2] dodatek A5id 13405

Netronix obsługa pastylek iButton 1 wire

opis budynek stalowy v1

więcej podobnych podstron