7

9

25274 75349

0 5>

CIRCUIT

CELLAR

®

ww

ww

ww

..cc

iirr

cc

uu

iitt

cc

ee

llll

aa

rr

..cc

oo

mm

T H E M A G A Z I N E F O R C O M P U T E R A P P L I C AT I O N S

$4.95 U.S. ($5.95 Canada)

# 1 3 0 M A Y 2 0 0 1

MEASUREMENT AND SENSORS

Frequency Meter Metal Detector

Digital Yard-Stick

Anemometry

Goes Ultrasonic

Testing by

Simulation

Premier GPS Inc., (403) 295-8879, Fax: (403) 274-3021, tabsha@premier-gps.com

computer systems in tiny modules

DIP-type modules with 28 - 92 pins

cut consumption (50mA @ full speed),

cut components, cut system cost

Digital, analog and serial I/O channels in module

Expansion Bus for up to 4,096 I/O lines

160 kB ... 6 MB FLASH + SRAM, RTC, Watchdog

BASIC Tigers™ deliver what developers and manufacturers

really want:

Test the Tiger at no risk today.

http://www.wilke-technology.com

ANU-2001-01.pm6

19.02.01, 17:11

1

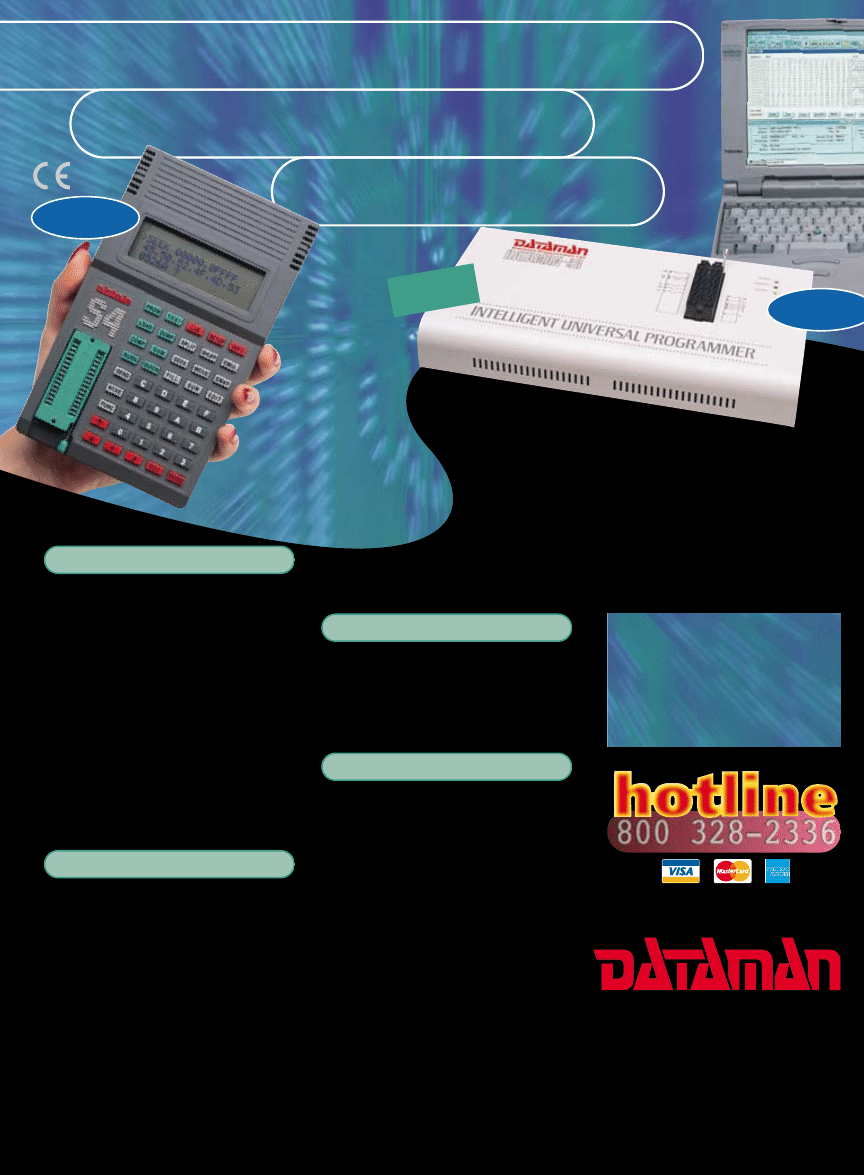

• 2 Channel Digital Oscilloscope

•

• Advanced Math options

• FFT Spectrum Analyzer options

Probes, Interface Cable, Power

Adapter, and software for

Win95/98, WinNT, Win2000

and DOS.

Optional 100 MSa/s Pattern Generator

LA2124-128K (100MSa/s, 24CH)

Clips, Wires, Interface Cable, AC

Adapter and Software

www.circuitcellar.com

CIRCUIT CELLAR

®

Issue 130 May 2001

3

Measurement and Sensing with the MPC565

Frequency Meter Metal Detector

Andrei Chtchedrine & Yuri Kolokolov

Behavioral Plant Simulation for Testing a Control

Algorithm

Return of the SBC

Multitasking Applications with SBC-386EX-S

The Company Formerly Known as Scenix

COLUMNS FEA

TURES

ISSUE

Advertiser’s Index

June Preview

Priority Interrupt

Steve Ciarcia

130

ChipCenter

DESIGNING WITH THE MMC2107

by David Gonzales

Isn't the goal always to design a complex system using a minimum amount of com-

ponents? This month David discusses the key elements of a general-purpose micro-

controller and their use in a real-time application. The peripheral and processor inter-

action is essential for collecting, processing, and outputting data and, subse-

quently, you can't fully appreciate this interaction without a review of the

microcontroller functions. That's just the beginning.

April 2001

AN HC11 FILE MANAGER

Part 1: Laying the Foundation

by Walter Krawec

The best place to start following this series is at the beginning, when the foundation

is poured. Building this project from the ground up, Walter takes us through the first

part of using an HC11 file manager and shows us how to store multiple pro-

grams without having to memorize the addresses. Remembering all the

addresses is better left to HC11 than the human mind's memory. Then you

can let your mind wander to make your own project a success story.

April 2001

A SIMPLE ADC ON AN LTC1286 CHIP

by Yury Magda

Yury's been using the LTC1286 and now he wants to pass his knowledge on to

Circuit Cellar readers. The analog-to-digital converter circuit designed on the popular

low-cost chip has proved its benefits, like allowing the measurement of an

input voltage in electronic circuits and consuming a low supply current equal

to only 250 µA. Yury's circuit is straightforward, so get ready to easily soak up

the design and details.

April 2001

AN S-7800A/PIC16F877 JOURNEY

Part 4: Road Testing

by Fred Eady

Using his signature music analogies, Fred explores practical extraction or report lan-

guage, also known as Perl. Just as Janis Joplin grew in popularity, so has been the

journey of Perl, with its talent for encoding messages. We've gone from web

services to the post office and it's always good to end a series with a little

music. Cue the final song.

April 2001

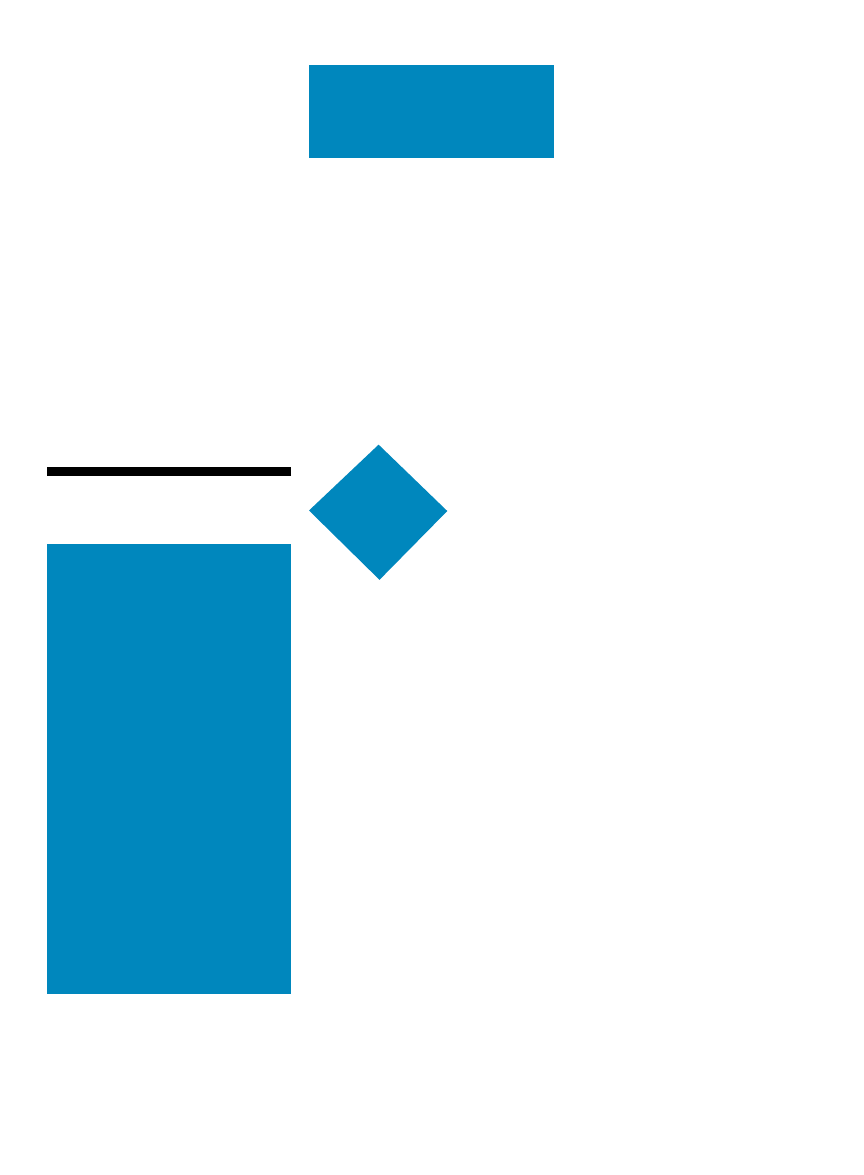

STRUCTURED DESIGN

Part 2: Putting Theory into Practice

Lessons from the Trenches— by George Martin

Revisiting a former project by Jeff Bachiochi, George continues with his use of Nassi

Schneiderman flowcharts to develop a structured, manageable design. George origi-

nally intended to include case and switch constructs, so he picks up with that this

month. So, allow him to put this structured vehicle in reverse and back things

up a bit. The end of the road holds the tool to help isolate problems..

April 2001

DESIGNCON FUSION

Silicon Update Online— by Tom Cantrell

Variety is the spice of life. This month, Tom takes us on a tour of DesignCon 2001

and shows us the way the medley of players is responding to the winds of change.

As usual, there's great potential for what Tom describes as a high "neato factor," you

just have to run with the times, or you run the risk of being left behind.

April 2001

RESOURCES

•Portable MP3

Players

Rick Prescott

•Oscilloscopes

•Ethernet Cabling

Brant Schroeder

ASK

US

THE ENGINEERS

TECH-HELP

RESOURCE

Let us help keep your

project on track or simpli-

fy your design decision.

Put your tough technical

questions to the ASK US

team.

The Ask Us research

staff of engineers has

been assembled to share

expertise with others.

The forum is a place

where engineers can

congregate to get some

tough questions

answered, or just browse

through the archived

Q&As to broaden their

own intelligence base.

★★★★★★★★★★

Test Your EQ

8 Additional Questions

CIRCUIT CELLAR

®

www.circuitcellar.com

6

Issue 130 May 2001

EDITORIAL DIRECTOR/PUBLISHER

Steve Ciarcia

MANAGING EDITOR

Rob Walker

TECHNICAL EDITORS

Jennifer Belmonte

Rachel Hill

Jennifer Huber

WEST COAST EDITOR

Tom Cantrell

CONTRIBUTING EDITORS

Mike Baptiste

Ingo Cyliax

Fred Eady

George Martin

George Novacek

NEW PRODUCTS EDITOR

Rick Prescott

PROJECT EDITORS

Steve Bedford

Bob Paddock

James Soussounis

David Tweed

ADVERTISING

ADVERTISING SALES MANAGER

Kevin Dows

Fax: (860) 871-0411

(860) 872-3064

E-mail: kevin.dows@circuitcellar.com

ADVERTISING SALES REPRESENTATIVE

Elyshia Gottier

Fax: (860) 871-0411

(860) 875-2199

E-mail: elyshia.gottier@circuitcellar.com

ADVERTISING COORDINATOR

Valerie Luster

Fax: (860) 871-0411

(860) 875-2199

E-mail: val.luster@circuitcellar.com

ADVERTISING CLERK

Sally Collins

CONTACTING CIRCUIT CELLAR

SUBSCRIPTIONS:

INFORMATION: www.circuitcellar.com or subscribe@circuitcellar.com

To Subscribe: (800) 269-6301, www.circuitcellar.com/subscribe.htm, or

subscribe@circuitcellar.com

PROBLEMS: subscribe@circuitcellar.com

GENERAL INFORMATION:

TELEPHONE: (860) 875-2199 Fax: (860) 871-0411

INTERNET: info@circuitcellar.com, editor@circuitcellar.com, or www.circuitcellar.com

EDITORIAL OFFICES: Editor, Circuit Cellar, 4 Park St., Vernon, CT 06066

NEW PRODUCTS: New Products, Circuit Cellar, 4 Park St., Vernon, CT 06066

newproducts@circuitcellar.com

AUTHOR CONTACT:

E-MAIL: Author addresses (when available) included at the end of each article.

CIRCUIT CELLAR®, THE MAGAZINE FOR COMPUTER APPLICATIONS (ISSN 1528-0608) and Circuit Cellar Online are published

monthly by Circuit Cellar Incorporated, 4 Park Street, Suite 20, Vernon, CT 06066 (860) 875-2751. Periodical rates paid at Vernon, CT

and additional offices.

One-year (12 issues) subscription rate USA and possessions $21.95, Canada/Mexico $31.95, all other

countries $49.95. Two-year (24 issues) subscription rate USA and possessions $39.95, Canada/Mexico $55, all other countries

$85.

All subscription orders payable in U.S. funds only via VISA, MasterCard, international postal money order, or check drawn on U.S.

bank.

Direct subscription orders and subscription-related questions to Circuit Cellar Subscriptions, P.O. Box 5650, Hanover, NH

03755-5650 or call (800) 269-6301.

Postmaster:

Send address changes to Circuit Cellar, Circulation Dept., P.O. Box 5650, Hanover, NH 03755-5650.

For information on authorized reprints of articles,

contact Jeannette Ciarcia (860) 875-2199 or e-mail jciarcia@circuitcellar.com.

Circuit Cellar® makes no warranties and assumes no responsibility or liability of any kind for errors in these programs or sche matics or for the con-

sequences of any such errors. Furthermore, because of possible variation in the quality and condition of materials and workmanship of reader-

assembled projects, Circuit Cellar® disclaims any responsibility for the safe and proper function of reader-assembled projects based upon or from

plans, descriptions, or information published by Circuit Cellar®.

The information provided by Circuit Cellar® is for educational purposes. Circuit Cellar® makes no claims or warrants that reade rs have a right to

build things based upon these ideas under patent or other relevant intellectual property law in their jurisdiction, or that readers have a right to con-

struct or operate any of the devices described herein under the relevant patent or other intellectual property law of the reader’s jurisdiction. The

reader assumes any risk of infringement liability for constructing or operating such devices.

Entire contents copyright © 2001 by Circuit Cellar Incorporated. All rights reserved. Circuit Cellar and Circuit Cellar INK are registered trademarks of

Circuit Cellar Inc. Reproduction of this publication in whole or in part without written consent from Circuit Cellar Inc. is prohibited.

ASSOCIATE PUBLISHER

Joyce Keil

CHIEF FINANCIAL OFFICER

Jeannette Ciarcia

CUSTOMER SERVICE

Elaine Johnston

ART DIRECTOR

KC Prescott

GRAPHIC DESIGNERS

Naomi Hoeger

Mary Turek

STAFF ENGINEERS

Jeff Bachiochi

John Gorsky

QUIZ COORDINATORS

David Tweed

Michael Smith

EDITORIAL ADVISORY BOARD

Ingo Cyliax

Norman Jackson

David Prutchi

TASK

MANAGER

picture may be worth a thousand words, but

never underestimate the power of a few words—

especially when they’re the wrong words. Recently I

purchased an item that boasted “Quick and easy installa-

tion.” There was a half sheet of diagrams and four bulleted sections of

directions below that. It looked quick and easy. The first bullet under the

“Mounting” section said, “We recommend that you purchase the mounting

kit…” That’s funny, the box didn’t say anything about needing a mounting

kit, nor were there any mounting kits in close proximity on the shelf when I

purchased the item. After looking at the components for a few minutes, I

decided that I could duplicate the mounting kit with spare parts.

Bullet number one under the “Wiring” section noted that the model I had

purchased may require the additional wiring harness kit. The wiring situation

would take more time to workaround than I had scheduled for the entire

project, so I caved and decided to go back to the store in search of the

wiring kit. But not before reading the rest of the directions to see what else I

actually needed. (The only section that didn’t suggest additional purchases

was “Disposal of damaged units.” Go figure.)

After I got the necessary parts, installing the unit really was quick and

easy. But the ease of installation was not satisfying enough to forget my

frustration at the outset. I’m sure the confusing language on the box was

not intentional (if the box listed the suggested “accessories” I probably

would have purchased them originally), but it makes me wonder about a

company that doesn’t look at things through the customer’s eyes.

A couple of months ago, our foreign subscribers received a letter about

the new electronic edition of

Circuit Cellar. Judging by your responses and

after looking at the letter again, it’s clear that the letter was somewhat con-

fusing. I apologize for the confusion and would like to clarify a few things

about the electronic edition of

Circuit Cellar for all of our readers.

First of all, the print magazine is not being replaced by the electronic edi-

tion and all foreign subscribers do not have to subscribe to the electronic

edition. The electronic edition is simply a new option that can benefit foreign

subscribers (no extra mailing costs and no shipping delays).

Next, a subscription to the electronic edition is not included with your print

magazine subscription. A one-year subscription to the electronic edition

costs $15 (USD), regardless of your geographic location.

And last, subscribing to the print magazine and subscribing to the elec-

tronic edition are two unrelated processes. You can subscribe to both simul-

taneously, but because electronic subscriptions and print subscriptions are

managed separately, there is not a way (at this time) to convert your sub-

scription from one form to the other. To subscribe to both formats, you need

to fill out both sets of subscription forms.

For more information, stop by our homepage and click on Electronic

Edition. There you’ll find a section of FAQ, as well as instructions for down-

loading a sample issue. If you have any questions about the electronic edi-

tion of

Circuit Cellar, feel free to e-mail us at eeinfo@circuitcellar.com.

Thank you for your patience and understanding as we work to enhance

the products and services that

Circuit Cellar provides.

rob.walker@circuitcellar.com

Cover photograph Ron Meadows—Meadows Marketing

PRINTED IN THE UNITED STATES

a

Clear as Mud

UL Class I, Group D for atmospheres with acetone,

ammonia, benzene, butane, cyclopropane, ethanol, gaso-

line, hexane, methanol, methane, natural gas, naphtha,

and propane; Class II, Groups E, F, and G for combustible

metal dusts, including aluminum, magnesium, and their

commercial alloys, and atmospheres containing com-

bustible carbonaceous dusts.

The encoders are rugged, high-performance, incremental

optical devices that feature an environmentally sealed,

cast aluminum housing. A stainless steel shaft and clear

anodized housing provide corrosion resistance. Electrical

outputs are electronically compatible with almost all

drives and PLCs. Differential line driver outputs are avail-

able for long cable runs and higher noise immunity.

The encoders sell for $750.

Danaher Controls

(847) 662-2666

Fax: (847) 662-6633

www.dancon.com

NEWS

8

Issue 130 May 2001

CIRCUIT CELLAR

®

www.circuitcellar.com

NEW PRODUCT

NEW PRODUCT

Edited by Rick Prescott

HAZARDOUS ENVIRONMENT ENCODER

Series X25 encoders are a new generation of hazardous

duty rotary encoders that are ideal for use in speed-feed-

back, cut-to-length measurement, and positioning applica-

tions in corrosive and/or explosive atmospheres. Encoders

are designed for use in environments such as UL Class I,

Group C for atmospheres such as ethyl ether and ethylene;

STD BUS CPU

The MCM-DXS is a high-integration STD bus CPU.

The CPU is a mid-ranged product based on the AMD 586

processor. This board is targeted for embedded applica-

tions including medical, transportation, test and instru-

mentation equipment, telecommunications, and machine

control.

Compatible with the x86-class of CPUs, the

CPU runs a vast amount of software

tools, utilities, and operat-

ing systems. The AMD

586 CPU also includes

a 16-KB cache and float-

ing-point processor for

math-intensive applica-

tions. The board is popu-

lated with 4 to 32 MB of

surface-mounted DRAM.

The DRAM is soldered

directly to the printed circuit

board to improve reliability for

applications subject to shock

and vibration. The CPU can

operate as a standalone SBC or

you can add off-the-shelf or user-designed IEEE 96 I STD

bus or PC/104 expansion UO modules to match the exact

application. These two expansion methods allow your

hardware solution to conform to open standard architec-

tures without having to pay for expensive pro-

prietary solutions.

The board integrates the basic AT peripher-

al complement including the keyboard con-

troller, 16-channel interrupt controller, and

real-time clock. Onboard peripherals are

mapped in the same location as a PC-AT,

including seven DMA controllers, three

16-bit counter/timers, two interrupt con-

trollers, keyboard controller, speaker

port, and battery-backed real-time

clock.

The price, which includes 4 MB of

DRAM memory is $795.

www.circuitcellar.com

CIRCUIT CELLAR

®

Issue 130 May 2001

9

NEW PRODUCT

NEWS

SURFACE-MOUNTABLE LED DISPLAY

This LED display is the world’s first 7-segment numer-

ic surface-mountable display. This device makes it possi-

ble for design and construction of equipment and instru-

mentation with numeric LED readouts on surface-mount

technology (SMT) boards and manu-

facturing processes. The LED dis-

play is ideal for a wide range of

applications including

timers, controllers, coun-

ters, test equipment,

or virtually any

system requiring

a numeric dis-

play where sur-

face-mount technolo-

gy is mandated by the

overall design and cost

parameters.

This display is based on a low-

profile, insert molded flat lead

frame package which stands just 3.3 mm (0.130

″

) off the

surface of the circuit board. The package measures 19

mm (0.748

″

) high × 12.7 mm (0.500

″

) wide, with a 14.22-

mm (0.56

″

) high numeric character. Each of the seven

segments is individually-addressable to create all digits

from zero through nine, plus several additional charac-

ters. A trailing decimal point is also included. Standard

color choices include state-of-the-art GaP green (565 nm)

and GaAsP high-intensity red (635 nm), with optional

blue and yellow available. Light output levels are as high

as 3200 MCD with a forward current of 10 mA. Units

can be ordered with a choice of common cathode or

common anode configurations.

The cost is $0.82 each in quantities of 1000.

Lumex, Inc.

(800) 278-5666

Fax: (800) 944-2790

www.lumex.com

– create a GUI in hours/days instead

– converts from HTML, JPEG, and GIF

into small, quickly-executable Amulet µHTML

1/4 VGA, 3.8-inch, Monochrome Display

bright backlight and fully-integrated analog touch panel

– manages the GUI, interacts with

the user, and controls the LCD – Frees up your micro!

– easily interfaces to most micro-

controllers (8/16/32-bit and even DSPs)

Replaces Traditional GUI Library

complex GUI programming, or RTOS required

– Up to 115.2 Kbps, cable included

64K-Bytes of Onboard Flash Memory

hundreds of Amulet µHTML pages that you create

Starter kit (STK-GT320) also includes our

Compiler, sample HTML files, and sample images.

Ready To Integrate Into Your Product

www.AmuletTechnologies.com (408) 244-0363

©2001 Easy GUI and µHTML are Trademarks of Amulet Technologies. U.S. and Foreign Patents Pending.

10

Issue 130 May 2001

CIRCUIT CELLAR

®

www.circuitcellar.com

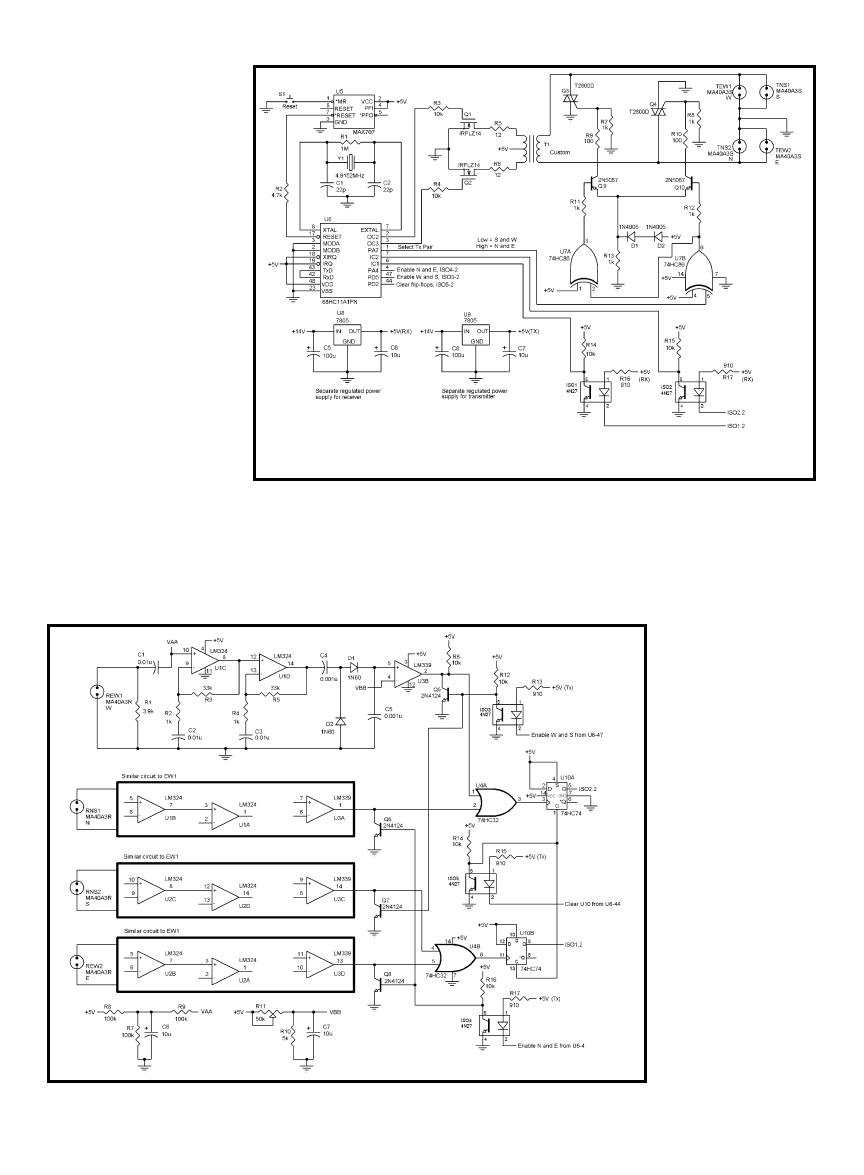

ost of the com-

plexity of today’s

vehicles results from

requirements for cleaner,

more efficient engines. These engines

are controlled by algorithms and look-

up tables, which ensure that the

engine is running optimally. Sensors

carefully measure crank position, air

temperature and pressure, and throttle

position. Microcontrollers such as

Motorola’s MPC565 then are used to

examine the output of the sensors and

use the data to manage the engine.

In this arti-

cle, I will

explore signal

measurement

and sensing

using Motorola’s

MPC565.

Designed for

powertrain con-

trol, the

MPC565 is one

of the largest

microcontrollers

on the market

today, with 14

million transis-

tors and 1 MB of

internal flash

memory.

There’s no question

that the automotive

industry has benefit-

ted from the growth

and development of

the microcontroller.

Engine control is one

of the main automo-

tive applications for

today’s micros, so

Andrew shows us

how controllers like

the MPC565 do it.

The modular I/O system (MIOS) is

capable of input capture, pulse width,

and period measurement. To illustrate

the use of the MIOS for signal meas-

urement, I’ll show you how to gener-

ate and vary the frequency and pulse

width of a waveform and then meas-

ure the period and duty cycle of the

signal using the dual-action sub-mod-

ule (MDASM).

THE MIOS

The MDASM can take pulse width

and period measurements and also

perform input capture on 10 channels.

You’re going to use the MDASM to

measure the period and pulse width of

a waveform that you’ll generate using

the PWM sub-module. You’ll also

capture the waveform using the Input

Capture mode. These three measure-

ment and sensing tools allow the

MPC565 to sense input waveforms

and demodulate PWM to gather infor-

mation for further processing using

the PowerPC microprocessor core.

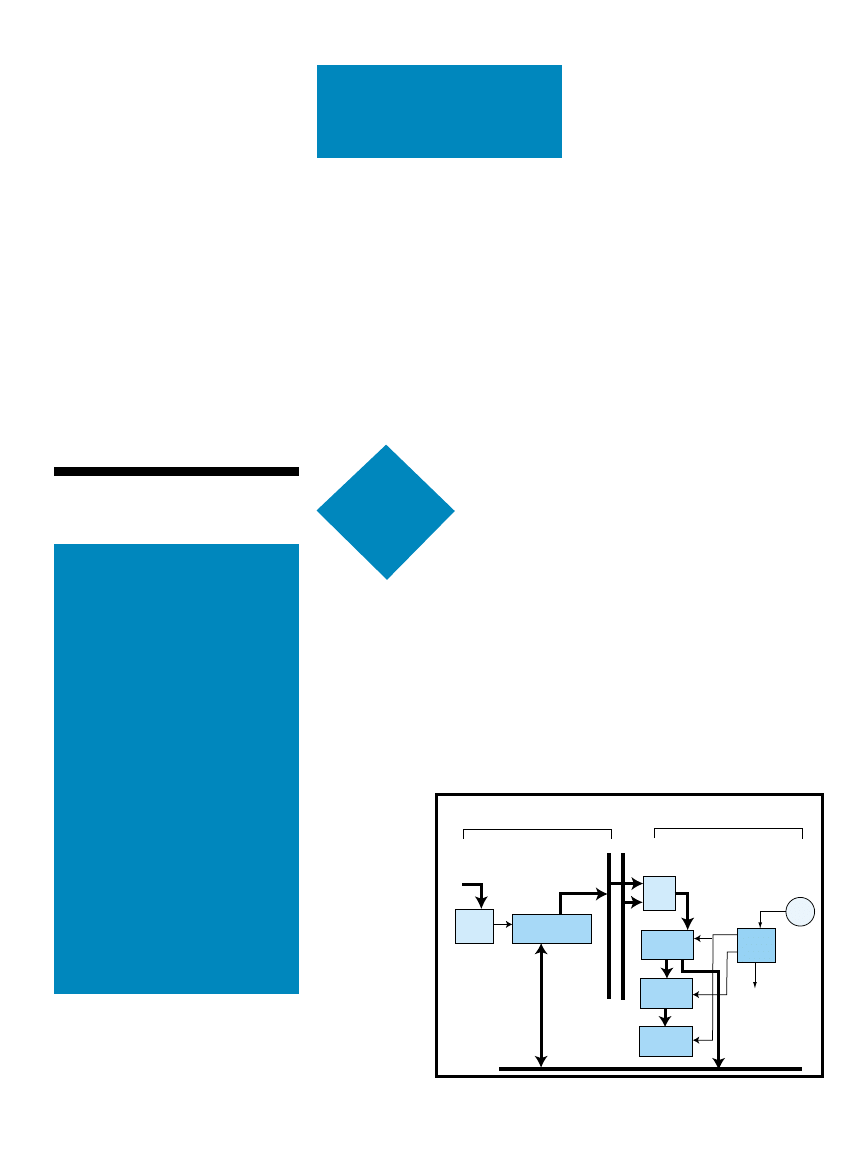

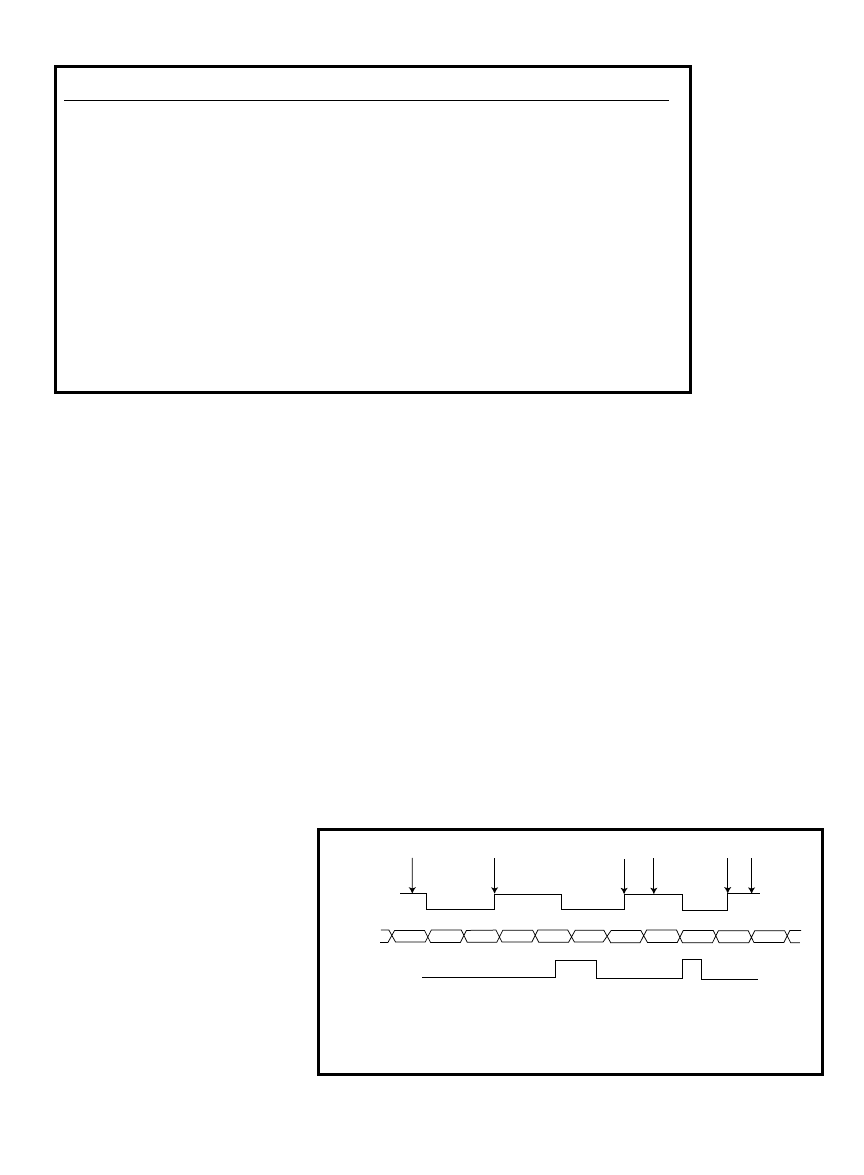

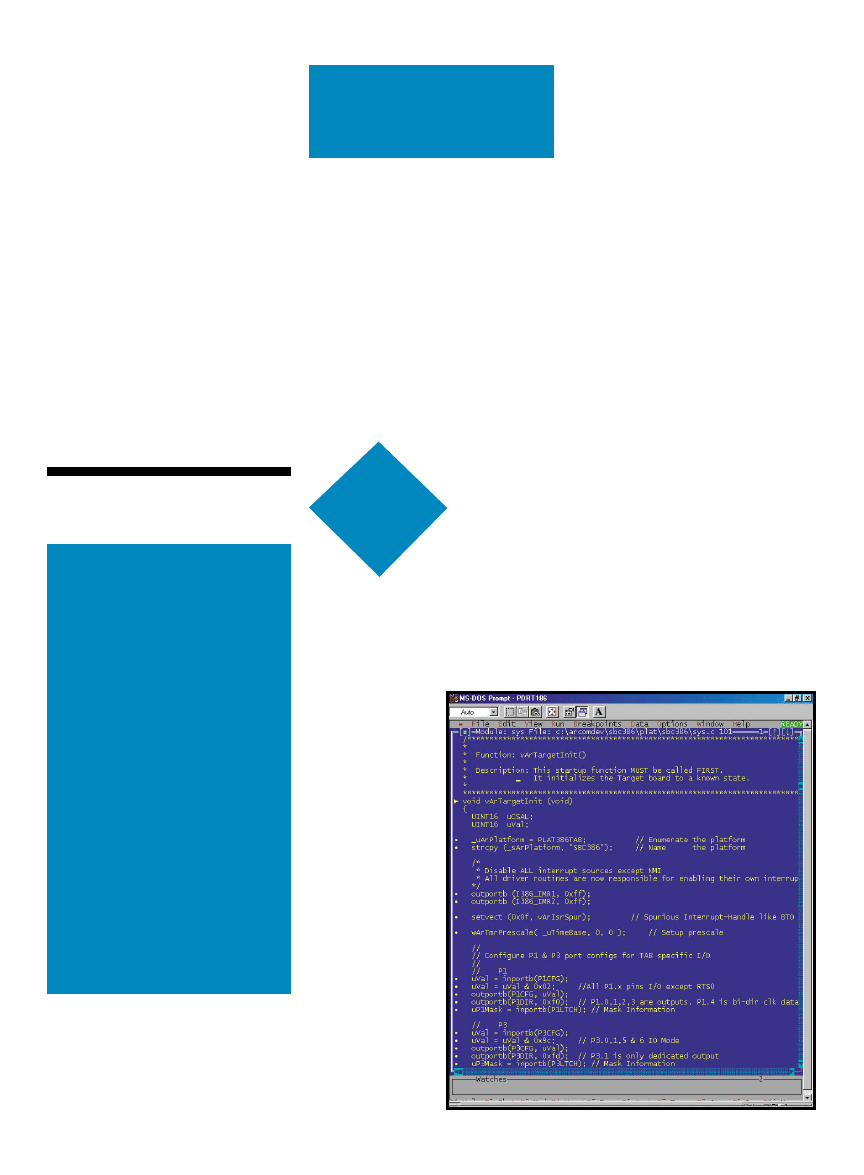

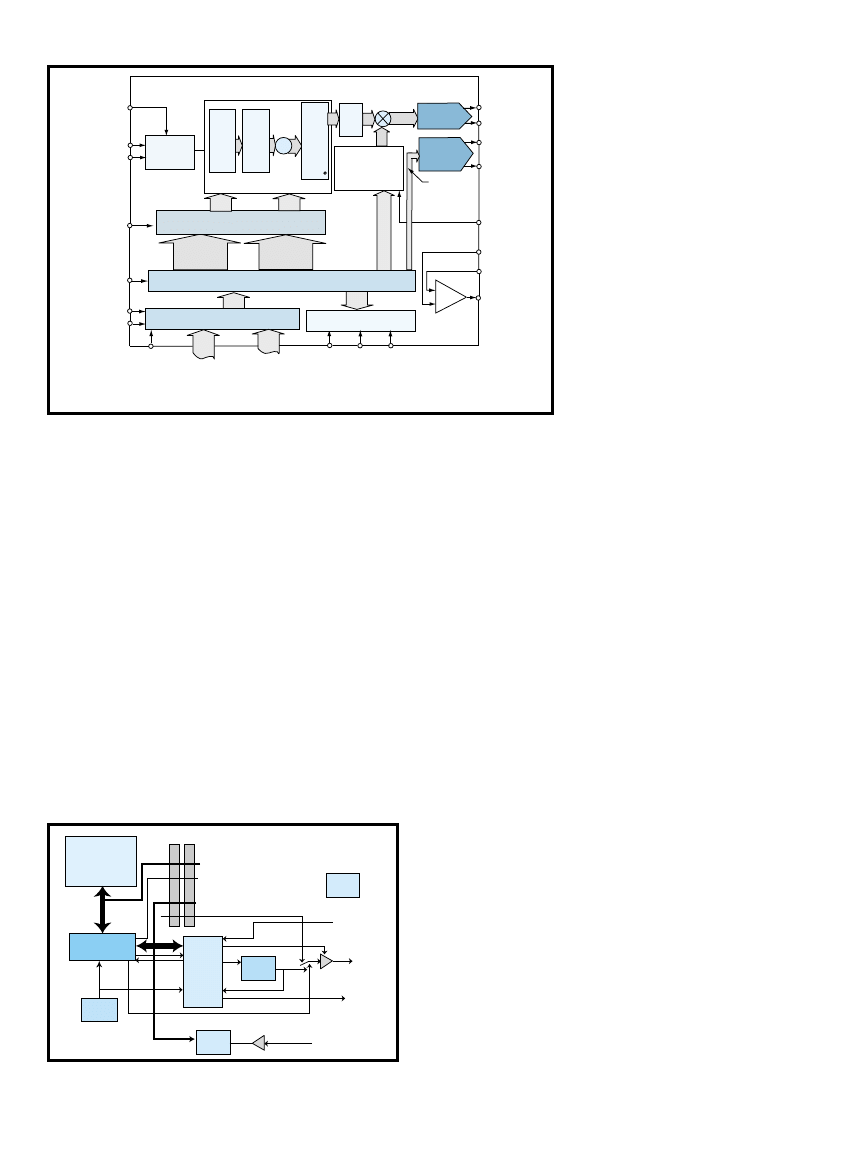

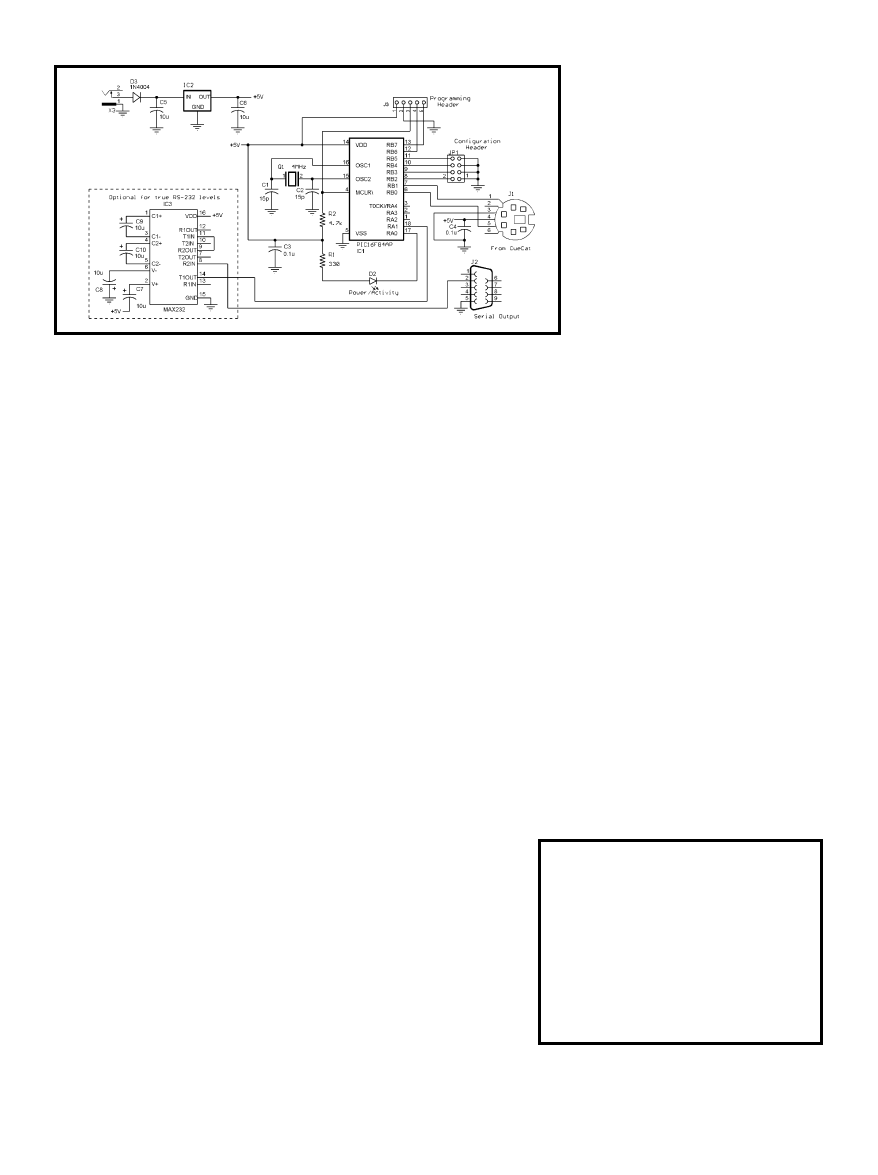

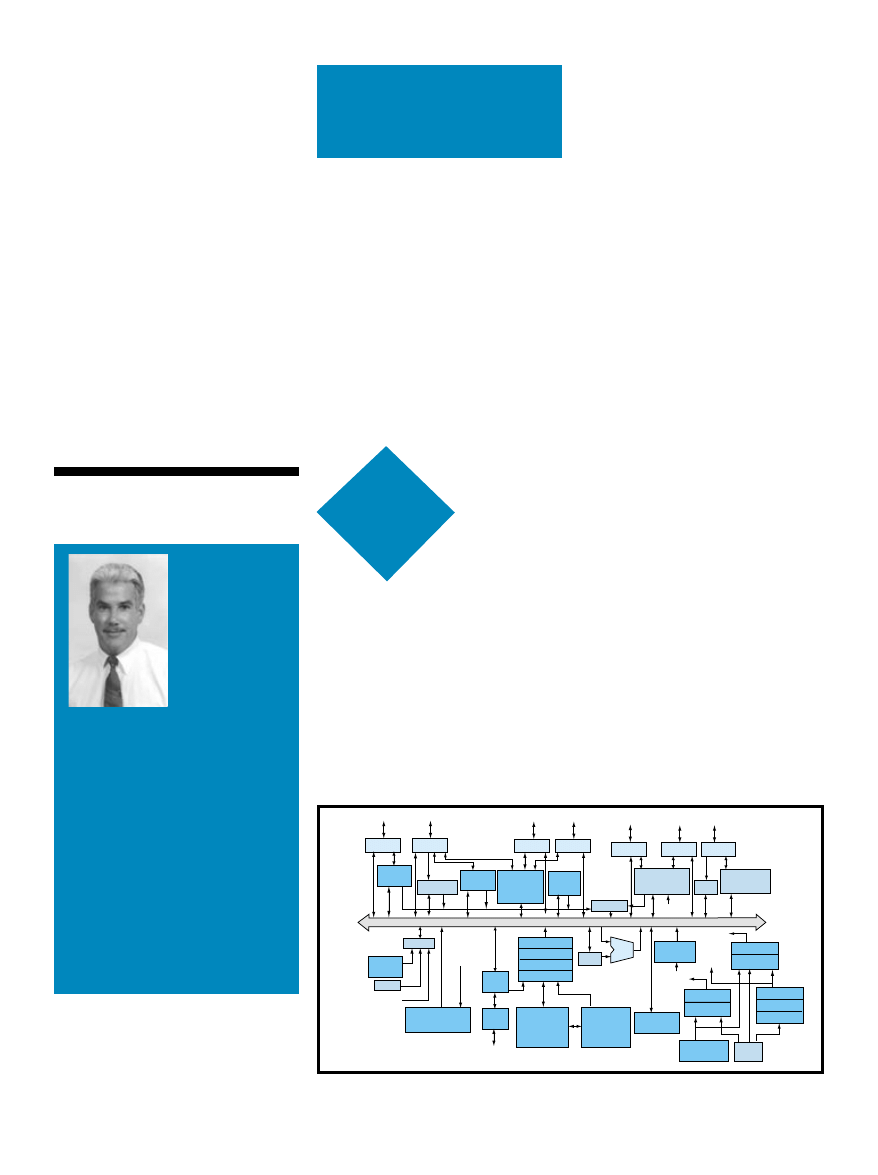

Figure 1 shows the MDASM. It has

three data registers that are accessible

to the software from the various

modes. For some of the modes, two of

the registers are cascaded together to

provide double buffering. The value in

one register automatically transfers to

another register at the correct time so

that the minimum pulse is just one

16-bit count.

To measure the width of an input

pulse, the MDASM has two capture

registers so that only one interrupt is

Andrew Lillie

Measurement and

Sensing with the MPC565

m

MIOS Modulus counter sub-module

From

prescaler

or pin

Clock

select

16-bit Up-counter

Bus

select

16-bit

Register A

16-bit

Register B1

16-bit

Register B2

Edge

detect

Input

pin

Input

capture

interrupt

on

designated

edge

Up to four

16-bit

counter

buses

MIOS Double-action sub-module

in IPM mode (MOD3 to MOD0 = 0b0010)

Sub-module bus

Figure 1—

The MDASM block diagram shows the function of the three result registers

and the modulus counter.

FEATURE

ARTICLE

www.circuitcellar.com

CIRCUIT CELLAR

®

Issue 130 May 2001

11

interested only in the latest period

measurement, one 32-bit coherent

read instruction can get both the cur-

rent and previous samples.

A configurable PWM module is

within the MIOS, allowing you to

adjust the frequency from 10 MHz to

less than 1 Hz and the duty cycle

from 0 to 100% with a variable degree

of resolution.

Now, you’re ready to experiment

using the MDASM. So, it’s time to

generate a waveform using the PWM.

GENERATING TEST SIGNALS

The MPC565 MIOS has 12 chan-

nels that can be used as pulse width

modulators. You’ll use channel 0.

Each PWM channel is controlled by

one system register and four registers

specific to that channel.

In order to use the PWM channels,

first you need to start the MIOS

counter. By default, the inter-module

bus (IMB) clock is half of the system

clock, but for this case, set it at

40 MHz to maximize the resolution

at a given frequency of the generated

needed after the second edge.

The software can read both

edge samples and subtract

them to get the pulse width.

The leading edge sample is

double latched so that the

software has the time of one

full period of the input signal

to read the samples to be

sure that nothing is lost.

A modulus counter sub-

module serves as the time-

base for the MDASM config-

ured in the Input Pulse

Width Measurement mode.

When the leading edge (programmed

to be rising or falling) of the input sig-

nal occurs, the state of the 16-bit

counter bus is saved in data register

B1. When the trailing edge occurs, the

counter bus is latched into data regis-

ter A and the content of register B1 is

transferred to register B2.

This operation leaves register B1

free for the next leading edge, which

occurs as soon as the next clock

cycle. When enabled, an interrupt is

provided after the trailing edge to

notify the software that PWM data is

available for a new pulse. After the

trailing edge, the software has one

cycle time of the input signal to

obtain the values for each edge.

Two samples are also available from

a MDASM sub-module for period

measurement. The software can read

and subtract the previous and current

edge counter values. As with pulse

width measurement, the software

avoids missing samples by ensuring

that the interrupt response time is

faster than the fastest input period.

Alternatively, when the software is

waveforms.

The MIOS counter

prescaler sub-module

(MCPSM) divides the sys-

tem IMB clock to generate

the counter clock. It is

designed to synchronize all

of the sub-modules with

the same division of the

main clock. The clock sig-

nal is prescaled by loading

the value of the clock

prescaler register into the

prescaler counter every time

it overflows. This allows all

prescaling factors between 2 and 16.

Counting is enabled by asserting the

PREN bit in the control register.

The PWM uses one count of the

MIOS counter per transition (rise and

fall) of the PWM signal; therefore, the

maximum frequency that the PWM

can generate is half of the MIOS

counter clock, even if the PWM chan-

nel divider is set to 1.

The status/control register controls

the MCPSM. Set bit 1 high to enable

the counter and write 0010 to bits 12

to 15 to set the divider to 2 for the

fastest counter possible. The faster

the counter, the faster the waveforms

you can produce and the greater the

resolution of the waveform definition.

Write 0x8002 to register 0x306816

(MCPSMCR). If you want to know

more details about the MIOS register

definitions, consult the MPC565

User’s Manual

. [1]

PULSE GENERATION

With the MIOS counter pro-

grammed to 20 MHz, the next step is

to program the PWM channel. The

PWM period register sets the number

of divisions per period of the wave-

form (i.e., resolution of a single peri-

od). Special consideration must be

taken when choosing the resolution

of the wave to be produced because it

involves a compromise. The resolu-

tion of the wave is inversely propor-

tional to the maximum frequency

that can be produced. Higher resolu-

tion requires more cycles of the refer-

ence clock per period and therefore a

lower overall frequency.

The period register contains a bina-

ry value corresponding to the number

Table 1—

Prescaler bits in the MPWMSCR and MMCSM set clock divider ratios.

Prescaler value (CP7…CP0 hex)

MIOS14 Prescaler clock divided by:

FF

1

FE

2

FD

3

FC

4

FB

5

FA

6

F9

7

F8

8

…

…

02

254 (2

8

– 2)

01

255 (2

8

– 1)

00

256 (2

8

)

Bit(s)

Name

Description

0

PINC

Clock input pin status bit

1

PINL

Modulus load input pin status bit

2

FREN

Freeze enable

3

EDGN

Modulus load falling-edge sensitivity

4

EDGP

Modulus load rising-edge sensitivity

5 and 6

CLS1 and CLS0

These read/write control bits select the clock source for the modulus counter.

7

Reserved

8 to 15

CP7 to CP0

This 8-bit read/write data register stores the modulus value for loading into

the built-in 8-bit clock prescaler. The new value is loaded into the prescaler

counter during the next counter overflow or when setting bits CLS1 and

CLS0 for selecting the clock prescaler as the clock source. Table 1 gives

the clock divide ratio according to the CP7… CP0 values.

Table 2—

The MMCSM configures the modulus counter to provide a reference clock to the MDASM by which

events are recorded.

12

Issue 130 May 2001

CIRCUIT CELLAR

®

www.circuitcellar.com

of MIOS clocks allocated to the period

of the waveform. Program PWM chan-

nel 0 with a period resolution of 20

divisions. Write 0x0014 to address

0x306010. This results in each period

being divided into 20 50-ns ticks, pro-

ducing a 1-MHz waveform.

The PWM pulse register sets the

number (binary) of divisions, or ticks,

from the period register (above) that

are high. This means that the ratio of

the pulse register to the period regis-

ter determines the duty cycle of the

produced signal. The value in the

pulse register must be less than the

value in the period register. Begin by

programming channel 0 with a 50%

duty cycle (or 10, with a period of 20)

by writing 0x000A to 0x306002. Vary

the period resolution and pulse width

parameters when experimenting with

the MDASM measurement modes.

The last eight bits of the PWM sta-

tus/control register (MPWMSCR) set

the clock divider for the particular

PWM channel. This divider operates

on the MIOS clock whose frequency

you set earlier. Each PWM channel

can use a divisor to slow the MIOS

counter clock.

If the IMB is operating at 40 MHz

and you divide that by two to get a

MIOS counter at 20 MHz, then set-

ting channel 0 to divide the MIOS

counter by one provides 1 MHz at a

resolution of 20. Table 1 shows the

eight-clock prescaler bits for the

MPWMSCR. Load 0x54ff into register

0x306006 to enable the output for

PWM with a divisor of one in

Transparent mode.

MEASURING SIGNALS

Now on to the good stuff! To meas-

ure the waveforms of the signal that

you generated earlier, connect the

PWM output on channel 0 to the

MDASM input on channel 11. This is

also a good time to connect an oscil-

loscope to verify the generated signal.

The MPC565 MIOS has a modulus

counter sub-module (MMCSM) that

can be configured as a 16-bit free-run-

ning counter to which events can be

referenced as they are detected by the

MDASM. The MDASM and MMCSM

work together to measure input wave-

forms. To begin,

set the counter to

be free-running

and automatical-

ly rollover when

it reaches its

maximum value.

Again, the

MMCSM status/

control register

controls the

counter. The last

eight bits of this

register are the

clock prescaler,

exactly like those

used earlier for

the PWM in

Table 1.

Set up the

MDASM to count

on rising edges (bits 3 to 4) and to use

the MMCSM internal clock bus. You

will set it up to follow the MMCSM

clock with a prescaler divisor of one.

This means that the counter will run

at 20 MHz, or 50 ns per count.

Following Table 2, configure the

MMCSM for a divisor of one (bits 8 to

15) and to use the MMCSM clock

prescaler (CLS1:0) and load on rising

edges (EDGP) by loading 0x0eff into

0x306036.

Internal clock synchronization

using the MMCSM allows a reference

clock up to half of the system fre-

quency. Alternatively, an external

clock can be applied for externally

synchronous measurement to a maxi-

mum frequency equal to one quarter

of the system frequency.

Bit(s)

Name

Description

0

PIN

Pin input status

1

WOR

In DIS, IPWM, IPM, and IC modes, the wired OR bit is not used.

2

FREN

The freeze enable bit is cleared by reset.

3

Reserved

4

EDPOL

In DIS mode, the polarity bit isn’t used. Reading it returns the last value written.

In IPWM mode, EDPOL selects the capture edge sensitivity of channels A and B.

1 = channel A captures on a falling edge. Channel B captures on a rising edge. 0 =

channel A captures on a rising edge. Channel B captures on a falling edge.

In IPM and IC modes, EDPOL selects the input capture edge sensitivity of

channel A. 1 = channel A captures on a falling edge. 0 = channel A captures on a rising edge.

5

FORCA

In DIS, IPWM, IPM, and IC modes, the force A bit isn’t used and writing to it has no effect.

6

FORCB

In DIS, IPWM, IPM, and IC modes, the force B bit isn’t used and writing to it has no effect.

7 and 8

Reserved

9 and 10

BSL1 and BSL0

The bus select bits select which of the four 16-bit counter buses is used by the MDASM.

Note that unconnected counter bus inputs are grounded.

11

Reserved

12 to 15

MOD3 to MOD0

The four mode select bits select the MDASM’s mode of operation (see Table 4).

To avoid spurious interrupts, I recommend disabling MDASM interrupts before changing the

operating mode.

Table 3—

The MDASM status/control registers can configure each of the 10 MDASM channels independently to allow different kinds of simulta-

neous measurements.

Mode selection; EDPOL = 0

Input signal

0×0500

0×1000

0×1100

0×1250

0×1525

0×16A0

A

A

Flag reset

by software

A

Flag reset

by software

16-bit

Counter bus

Flag bit

MDASMAR Captured value

0×××××

0×1000

0×1250

0×16A0

0×××××

0×××××

0×1000

0×××××

0×1250

0×1250

0×1000

0×16A0

B1 Value

B2 Value

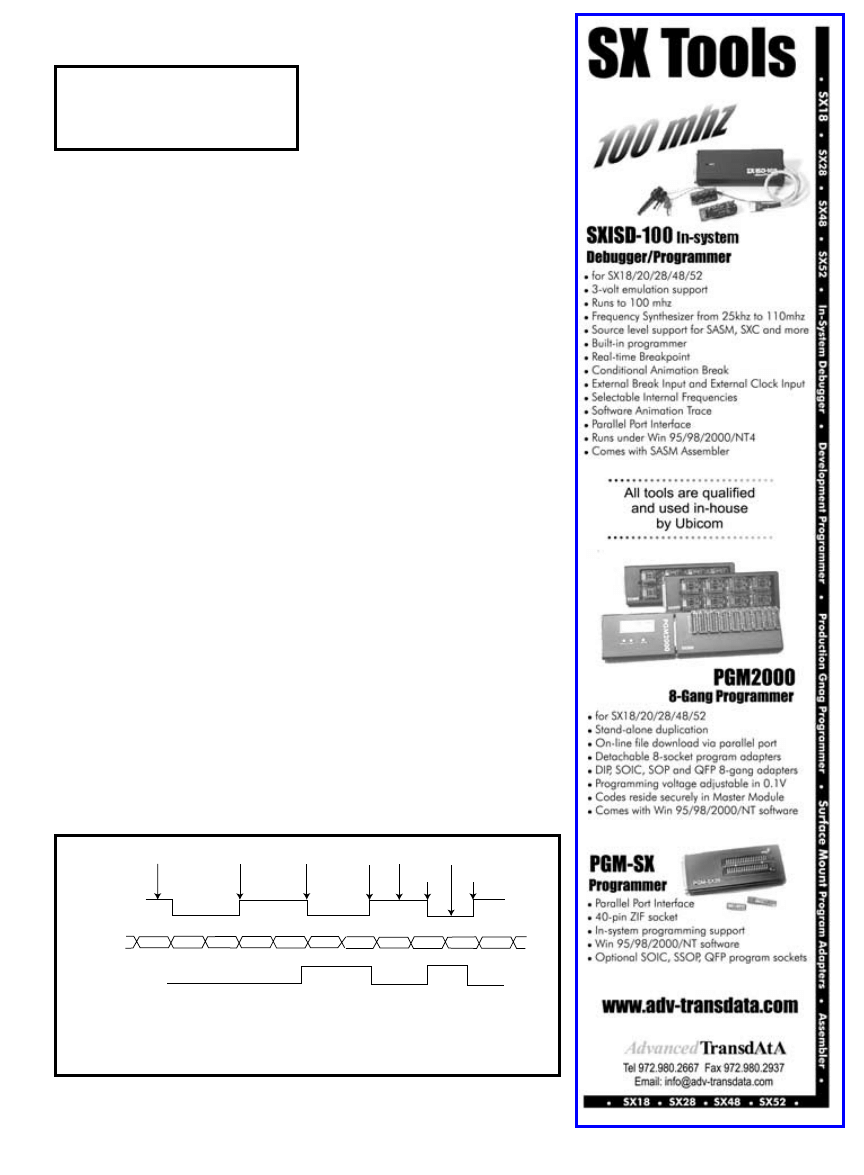

Figure 2—

Input period measurement using the MDASM allows accurate frequency measurement. Note the use of

the flag bit.

www.circuitcellar.com

CIRCUIT CELLAR

®

Issue 130 May 2001

13

To ensure that the counter starts

properly, reset it by loading zeros into

the modulus latch, read/write register.

This register contains the 16-bit value

to be loaded into the MMCSM count-

er. Write zeros to 0x306032.

With the clock now running, you

can set up the MDASM to detect the

waveform periods and reference them

to this counter. In this case, you will

use only one of the 10 MDASM chan-

nels. All of the channels can be pro-

grammed the same way. Depending

on your application, you may want to

program one each for period measure-

ment, PWM, and input capture.

A control register configures each

MDASM channel, and results are

obtained from the two data registers.

The status/control register contains a

read-only bit reflecting the status of

the MDASM pin as well as read/write

bits related to its control and configu-

ration. The MDASM status/control

(MDASMSCR) register (address

0x30605E) will be used to initialize

MDASM channel 11 for your initial

measurements (see Table 3).

When programming the MDASM-

SCR, notice that bit 0 in Table 3 is a

read-only status bit that indicates the

state of the incoming waveform.

Because you don’t want the MDASM

to freeze in Background Debug mode,

bit 2 will be left as 0. Bit 4 will be 0

to trigger the MDASM counter on the

rising edge. Write 0 to bits 9 and 10

to select counter bus 0 as pro-

grammed in the modulus counter

sub-module. In order to perform fre-

quency measurement, you need to

measure the input period (MOD 0010

in Table 4). Load 0x0002 into the

MDASMSCR (0x30605E) to perform

input period measurement.

READING THE MDASM

When the MDASM detects a rising

edge, it will write the value of the

modulus counter to the data A regis-

ter. Upon detection of the following

rising edge (one period later) the

MDASM will move the first counter

value into data register B and write

the new value to register A. You pro-

grammed the counter to count at 50-

ns intervals. Subtracting register B

from register A sums the number of

counts during one complete period of

the input waveform.

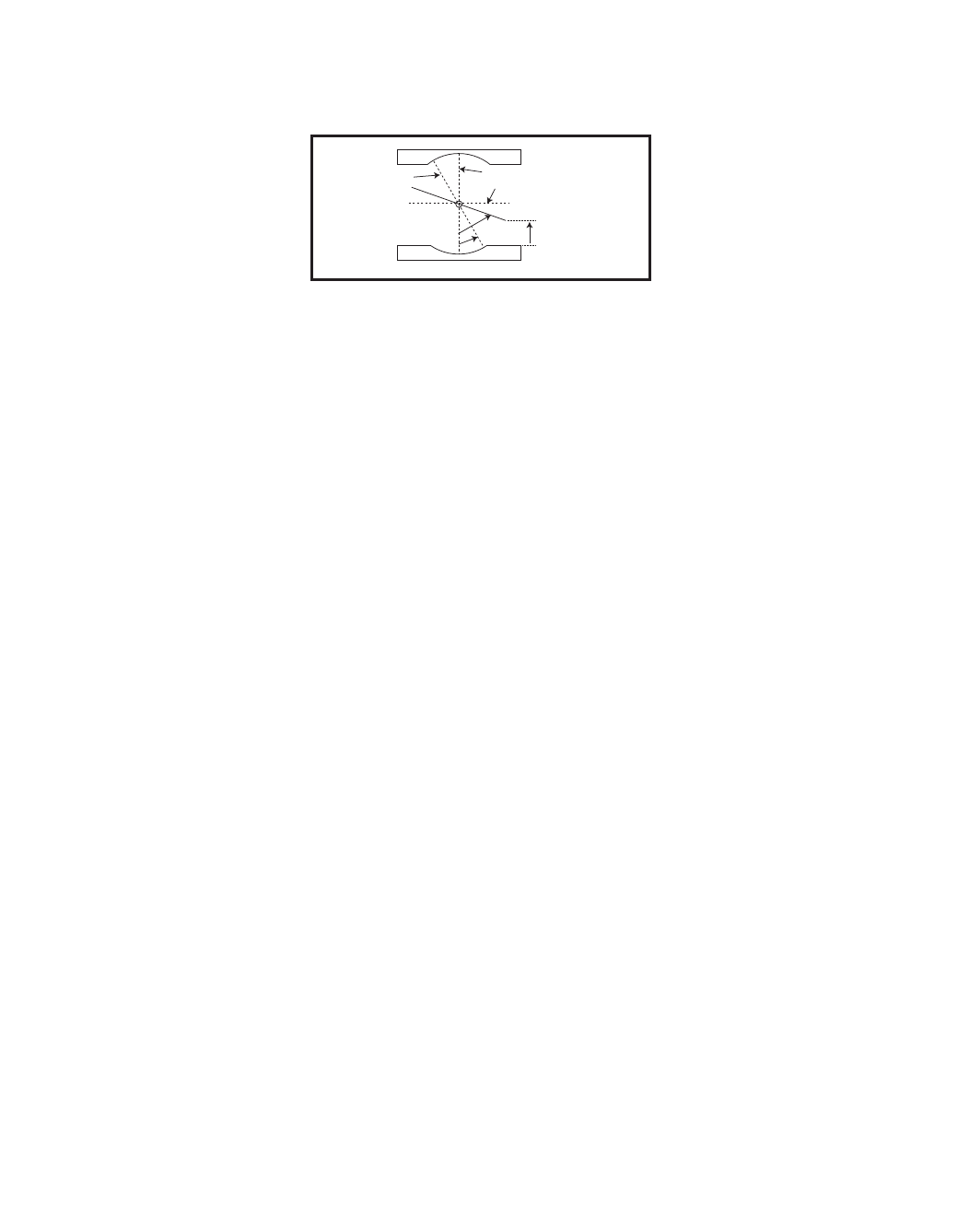

Figure 2 illustrates the events in

the Period Measurement mode. Note

the operation of the flag bit as it trig-

gers the load of the counter value

into the data register. Using the –l

command ensures that the contents

of the two data registers are presented

simultaneously, so that you don’t

miscount because of the time it takes

to read the data out of memory on

two successive reads during Debug

(freeze) mode.

The BDM software returns eight

hex characters in one long word using

Mode selection; EDPOL= 1

Input signal

0×0500

0×100

0×1100

0×1250

0×1525

0×16A0

B

A

Flag reset

by software

Flag reset

by software

16-bit

Counter bus

Flag bit

MDASMAR Captured value

0×××××

0×1000

0×1100

0×1100

0×××××

0×××××

0×1000

0×××××

0×1000

0×1000

0×1000

0×1250

B1 Value

B2 Value

B

B

0×1525

0×1525

0×1250

0×1250

0×1000

0×16A0

A

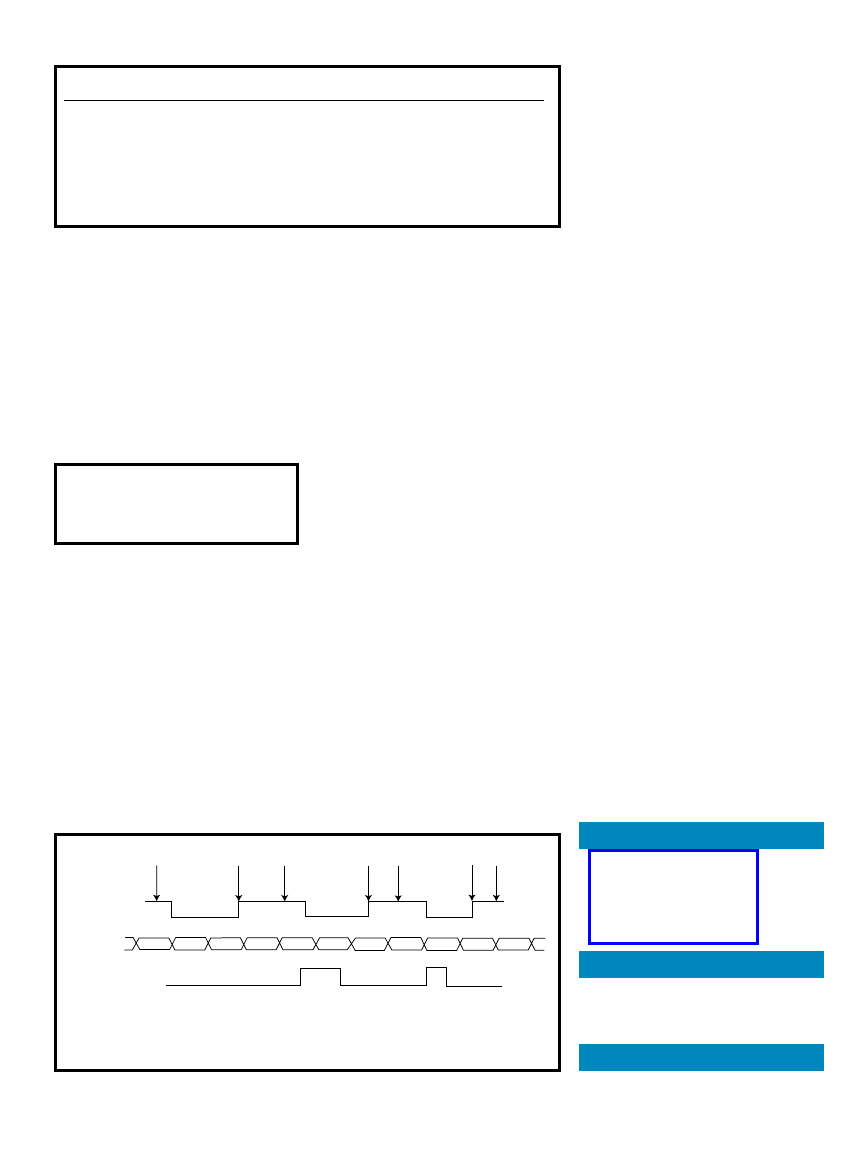

Figure 4—

Pulse width measurement is the same as period measurement except that the falling edge triggers the

second bus counter read. This example shows negative pulse width measurement.

#> read -l 0×306058

(0×306058)

00306058

5020500C

00028002

.

.

.

.

.

.

.

.

.

Figure 3—

When you use the – l command, the BDM

software returns eight hex characters in one long

word.

14

Issue 130 May 2001

CIRCUIT CELLAR

®

www.circuitcellar.com

measurements, set the MOD[3:0] bits

to 0001 (see Table 4). This mode

allows the width of a positive or nega-

tive pulse to be determined by captur-

ing the leading edge of the pulse on

channel B and the trailing edge of the

pulse on channel A; successive cap-

tures are done on consecutive edges of

opposite polarity. The edge sensitivity

is selected by the EDPOL bit in the

MDASMSCR register.

After performing a long read of data

registers A and B again, you now have

the number of 50-ns counts that rep-

resents the length of the positive

pulse. Using the PWM pulse width

register, vary the width of the PWM

pulse by changing the number of posi-

tive 50-ns ticks. Set the waveform

resolution to 20 so there’s room to

play with when you experiment with

the Pulse Width Measurement mode.

For my 10% duty cycle signal (still at

1 MHz), I achieved the results dis-

played in Figure 5.

One more MDASM mode allows

you to capture the events of an

incoming waveform. The Input

Capture mode (ICM) can be useful for

communication circuits or timing cir-

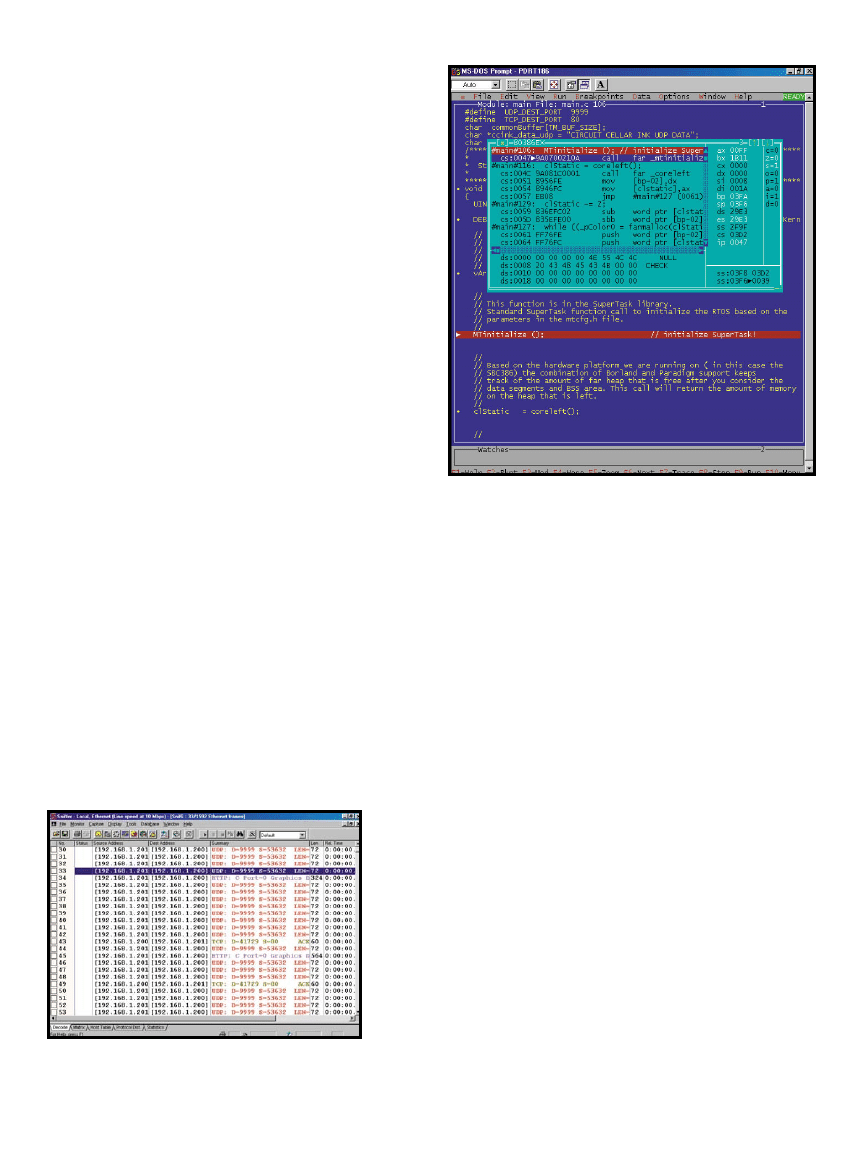

the code shown in Figure 3. Don’t be

alarmed if your results are different

from these, because these values are

read from a free-running counter, and

the values constantly change. What

matters is the difference between the

two bytes of the word. Also remember

that the counter may pass zero and

restart during a measurement.

The long word 5020500C contains

the contents of the two data registers.

Data A contains 5020 and data B con-

tains 500C. When you subtract regis-

ter B from register A, you get 20 in

decimal. To calculate the frequency,

multiply by 50 ns and take the recip-

rocal to get 1 MHz. Using a similar

approach, you can measure the pulse

width of the waveforms (see Figure 4).

To reprogram the MDASM status

and control register for pulse width

Mode selection; EDPOL = 0

Input signal

0×0500

0×1000

0×1100

0×1250

0×1525

0×16A0

A

A

Flag reset

by software

Flag reset

by software

A

Flag reset

by software

16-bit

Counter bus

Flag bit

MDASMAR Captured value

0×××××

0×1000

0×1250

0×16A0

0×××××

0×××××

0×1000

0×××××

0×1250

0×1250

0×1000

0×16A0

B1 Value

B2 Value

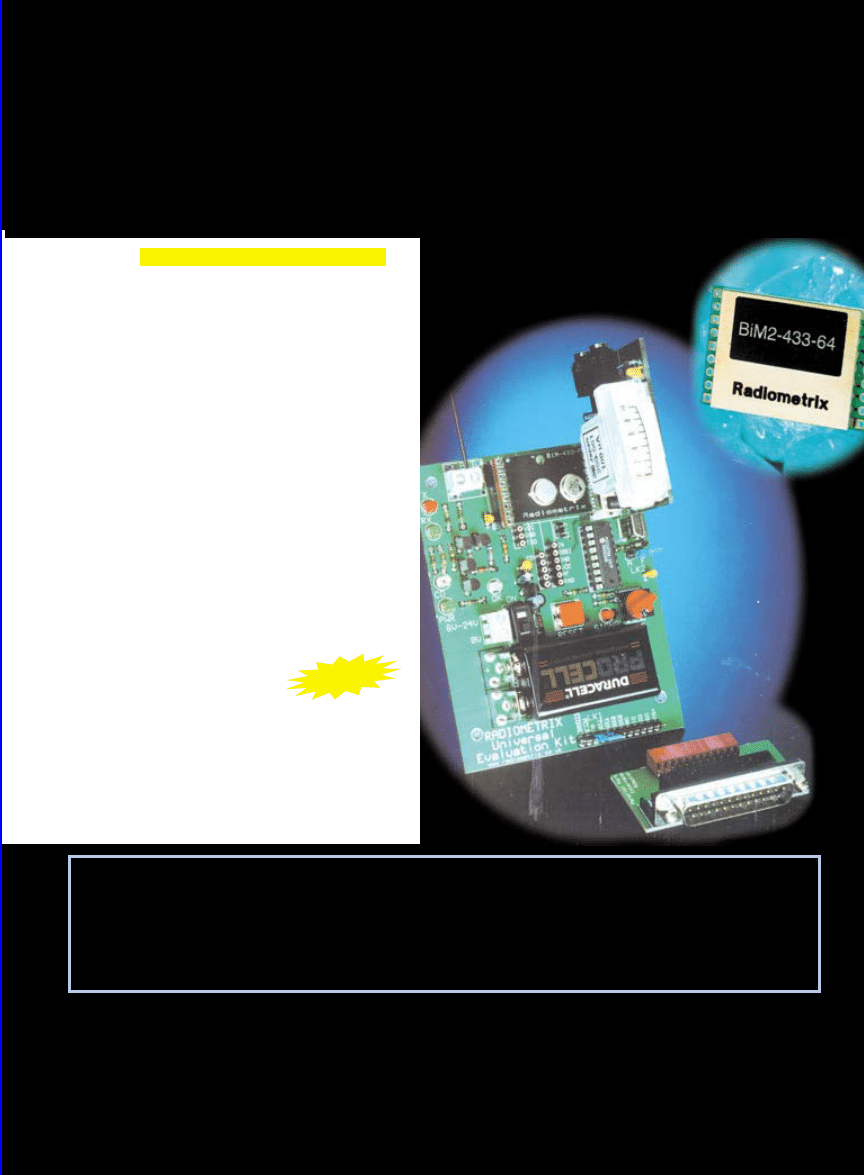

Figure 6—

Input Capture mode triggers the flag to capture the transitions on the input waveform, allowing an accu-

rate representation of the applied waveform in memory.

SOURCE

MPC565

Motorola, Inc.

(847) 576-5000

Fax: (847) 576-5372

www.motorola.com

REFERENCE

[1] Motorola, Inc., MPC565 User’s

Manual

.

RESOURCE

A. Lillie and R. Dees, “Using the

MIOS on the MPC555 Evaluation

Board,” AN1778, 1998.

cuits where periods of inactivity

greater than a certain length may

indicate a new condition. This mode

is identical to the Input Period

Measurement mode (IPM), with the

exception that the flag line is activat-

ed at the occurrence of the first

detected edge of the selected polarity.

In this mode, the MDASM functions

as a standard input capture function.

In this case, the value latched in

channel B can be ignored. Using the

ICM of the MDASM, you can record

at what times the edges occur on the

waveform (see Figure 6).

The dual-action sub-module of the

MIOS provides 10 channels that can

be used for similar measurements and

are easily configurable. Using all three

of the measurement modes I have

explored on a single signal provides a

thorough analysis. You can measure

the period, pulse width, and capture

when the pulses occur on any signal,

even one that isn’t periodic.

The MIOS is becoming a common

feature on many Motorola microcon-

trollers and offers flexibility for pulse

generation and measurement. Since

working with the MIOS, I‘ve found

some great applications for these

measurement modes and I expect that

you will find many more.

I

Andrew Lillie works in the Advanced

Vehicle Systems Division at Motorola

and helped design the MPC565. He

can be reached at andrew.lillie@

motorola.com.

MODE[3:0]

Mode

Description of mode

0000

DIS

During Disabled mode, the input pin is high impedance. PIN gives the state of

the input pin.

0001

IPWM

The input pulse width measurement is captured on the leading and trailing edges

of an input pulse.

0010

IPM

The input period measurement is captured during two consecutive rising or falling

edges.

0011

IC

This mode captures the input when the designated edge is detected.

Table 4—

The three input measurement modes are programmed into the MDASMSCR. Each channel can operate

in a different measurement mode concurrently.

#> read -l 0×306058

(0×306058)

00306058

E06AE068

00088800

.

.

.

.

.

.

.

.

.

Figure 5—

Subtracting E068 from EO6A makes two

counts, or 100 ns. One-hundred ns out of 1 µs is 10%

at 1 MHz.

RF modules and your Data Links....

65 Southbridge St., Auburn, MA. 01501 • Tel: 508-798-5004 • Fax: 508-798-4782

sales@lemosint.com • www.lemosint.com

Radiometrix specializes in the design and manufacture of low power radio products which help you to

rapidly implement high-reliability, cable free data links.

16

Issue 130 May 2001

CIRCUIT CELLAR

®

www.circuitcellar.com

ome springtime,

do your thoughts

turn to mulching the

planter beds? Each year

the discussion between my wife and I

goes the same way.

“Are you going to order the mulch

today?”

“Well, I really don’t know how

much to order.”

“Why don’t you just order what you

did last time?”

“It’s been so long, I’ve forgotten.”

“Why don’t you just measure the

beds and figure it out?”

“They’re all so irregular it’s almost

impossible.”

And so on. In case you had difficul-

ty identifying the speakers in that dia-

log, associate all the question marks

with the wife and the lame answers

with the husband—me.

Being a dyed-in-the-wool technolo-

gist, I thought there must be an easier

way to figure out an answer to this

problem other than putting in more

concrete or blacktop. The answer

turned into the Yard-Stick. I started

with the basic measuring wheel that

measures distance by rolling a wheel

along the path. I added a compass to

indicate direction, then recorded the

data so I could later send it to a PC. In

the PC, the direction and distance

data can be used to plot the area or

measure it. I included an LCD to give

you some real-time feedback, a few

switches, and a buzzer, and presto, I

arrived at the answer to every land-

scaper’s and home handyman’s dream.

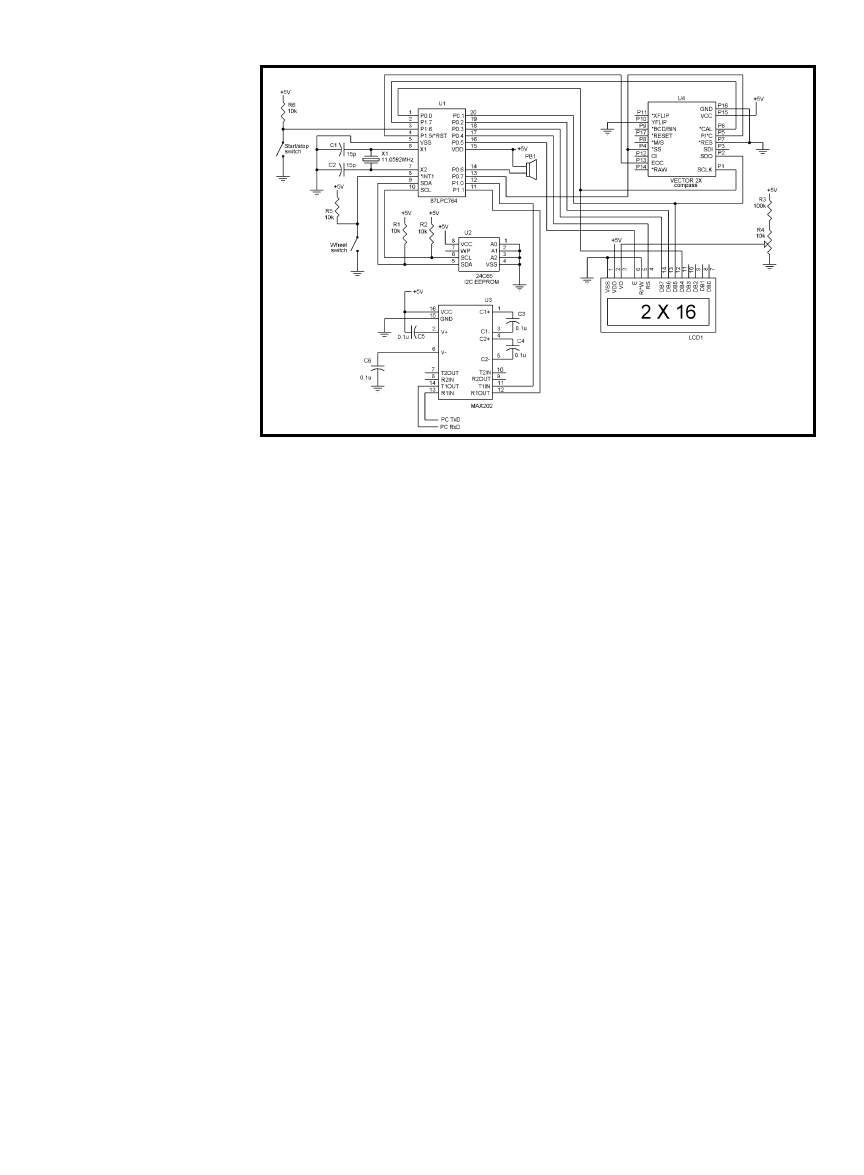

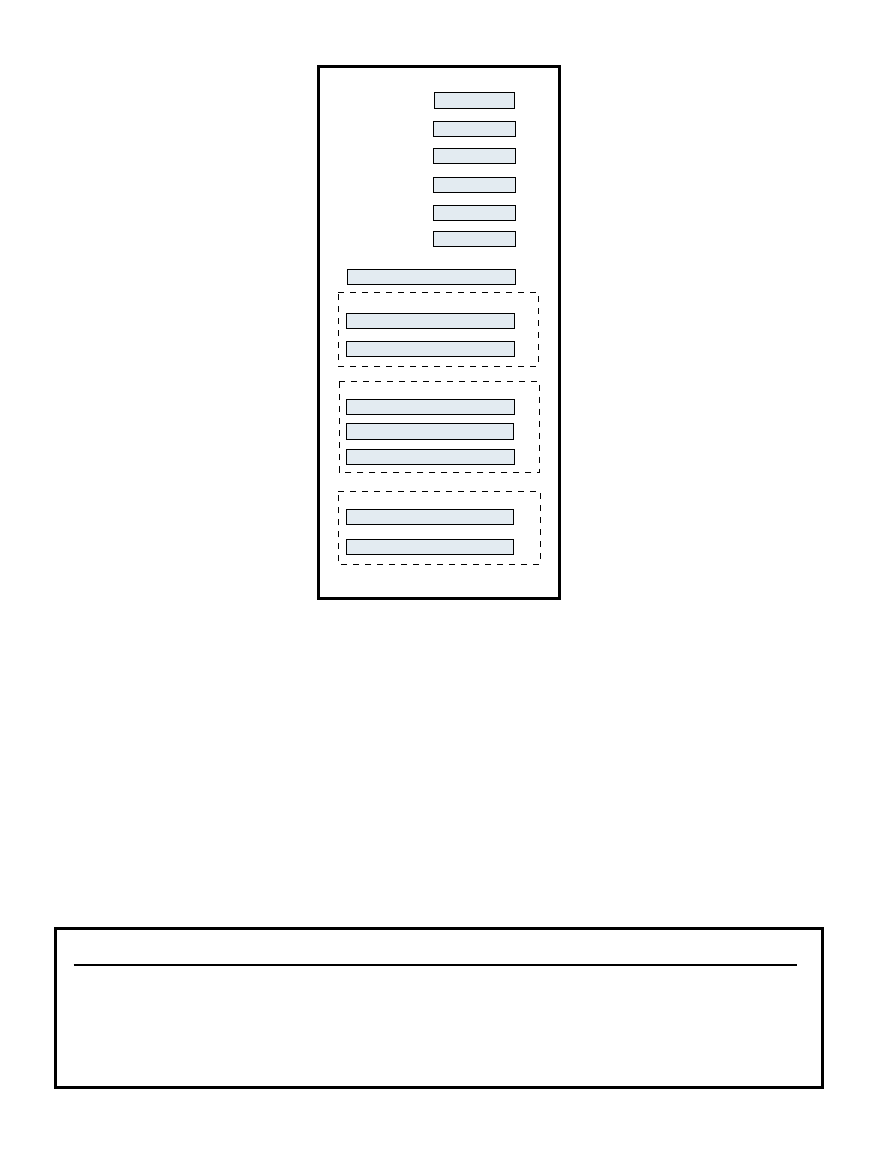

The Yard-Stick uses an 87LPC764

microprocessor to integrate a compass

module, two-line LCD display, I

2

C

EPROM memory, RS-232 interface,

switch closure from the rolling wheel,

push button to start and stop meas-

urements, and a buzzer. The buzzer

warns you when the memory is full.

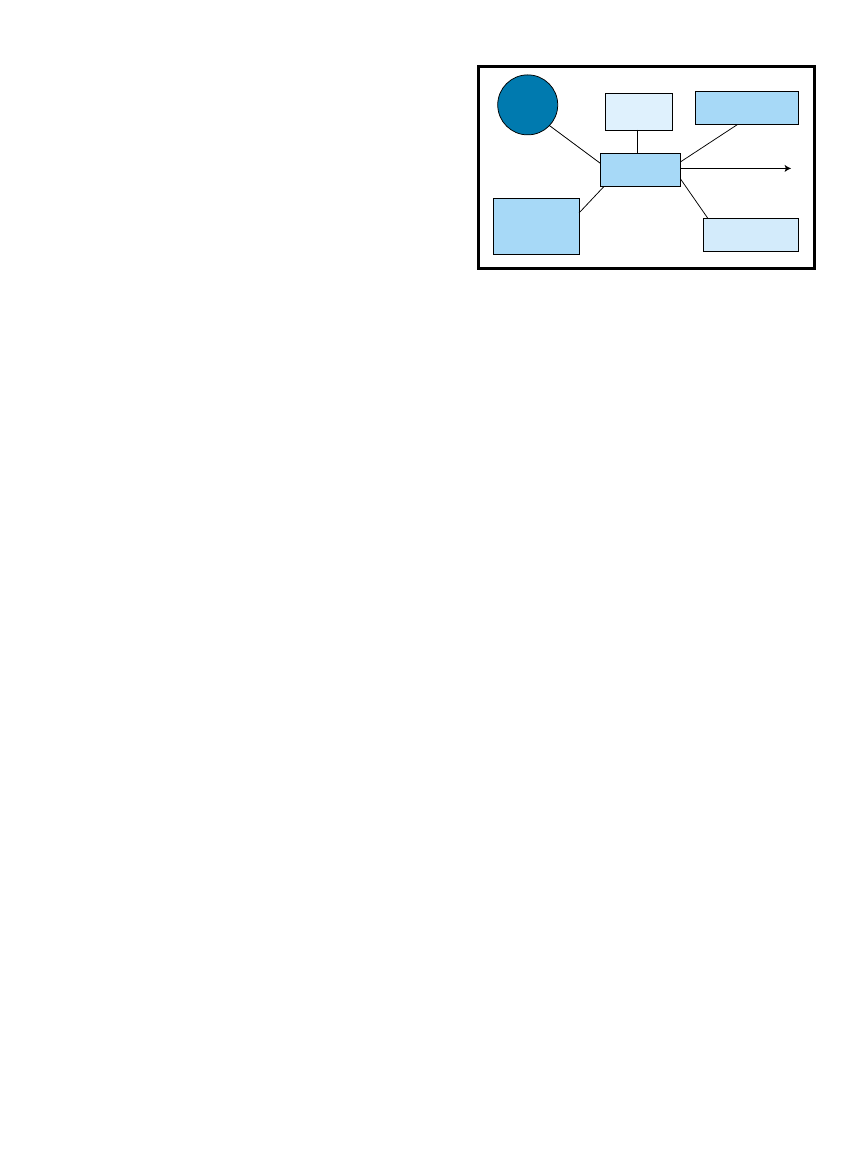

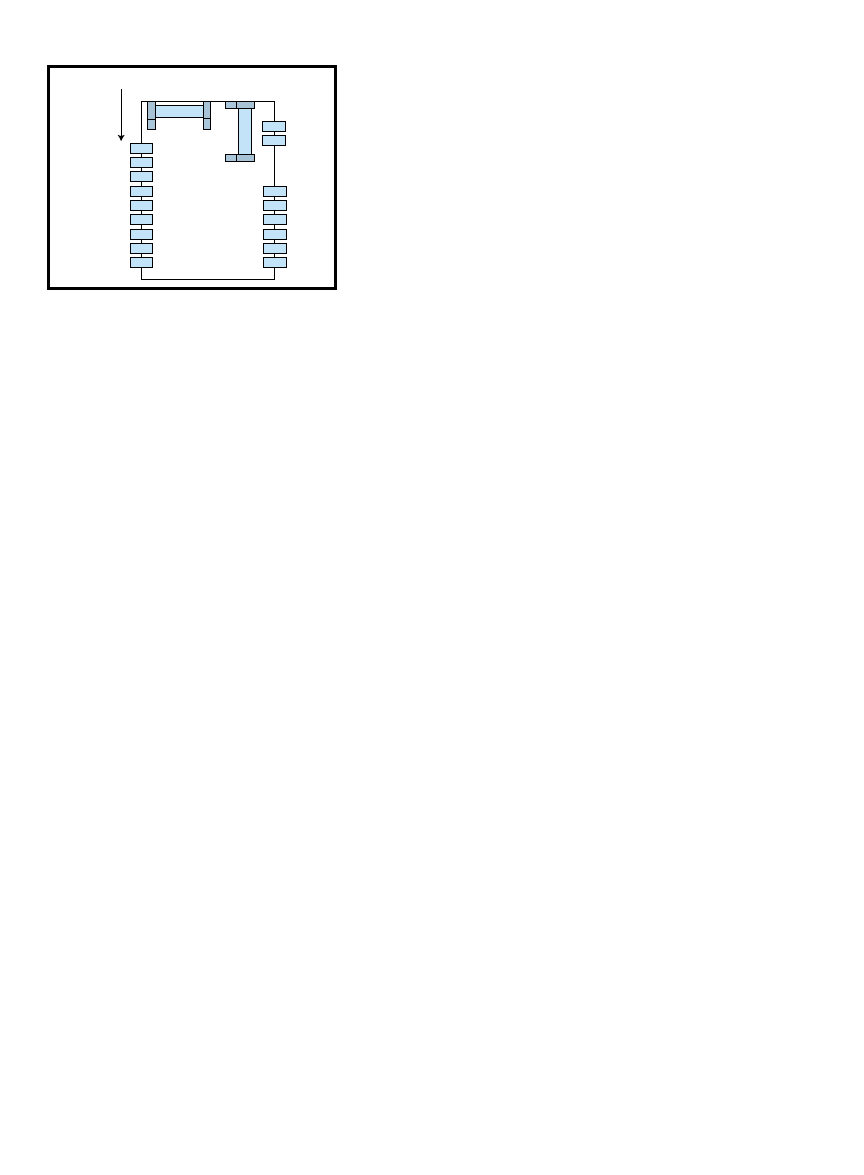

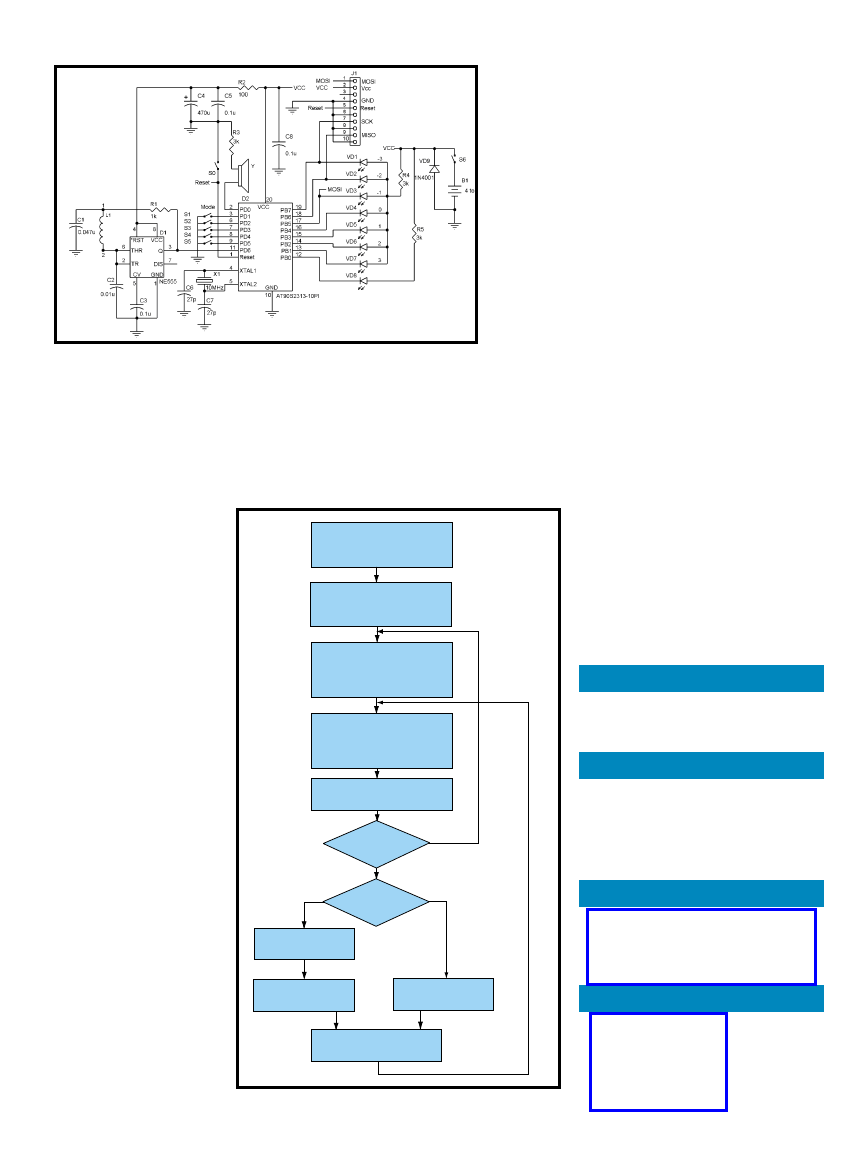

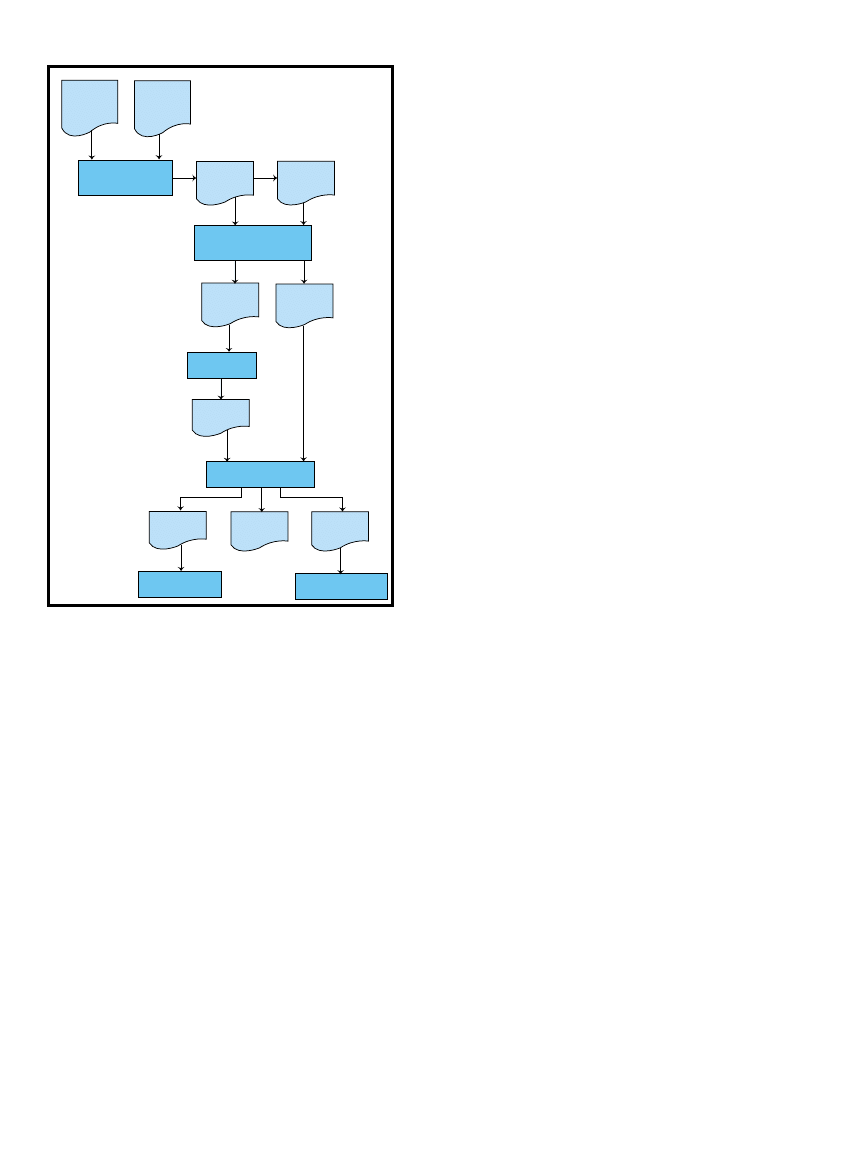

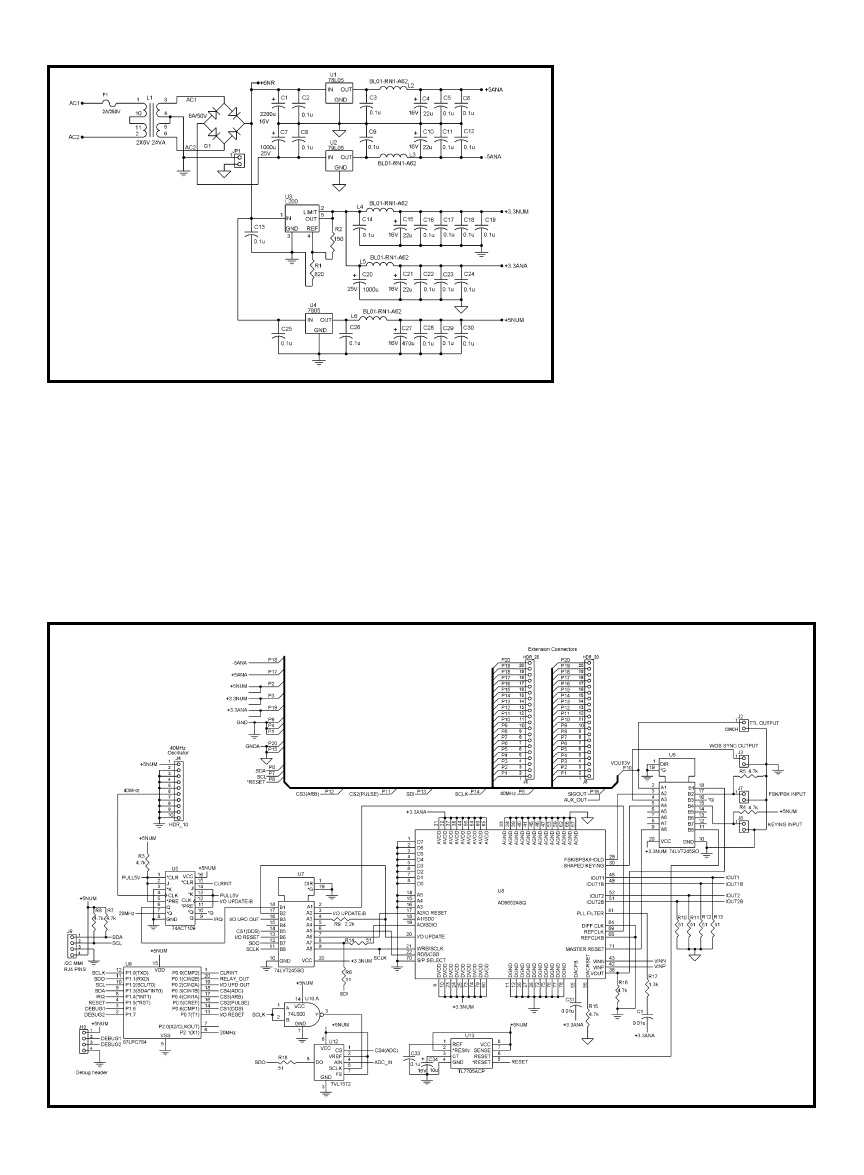

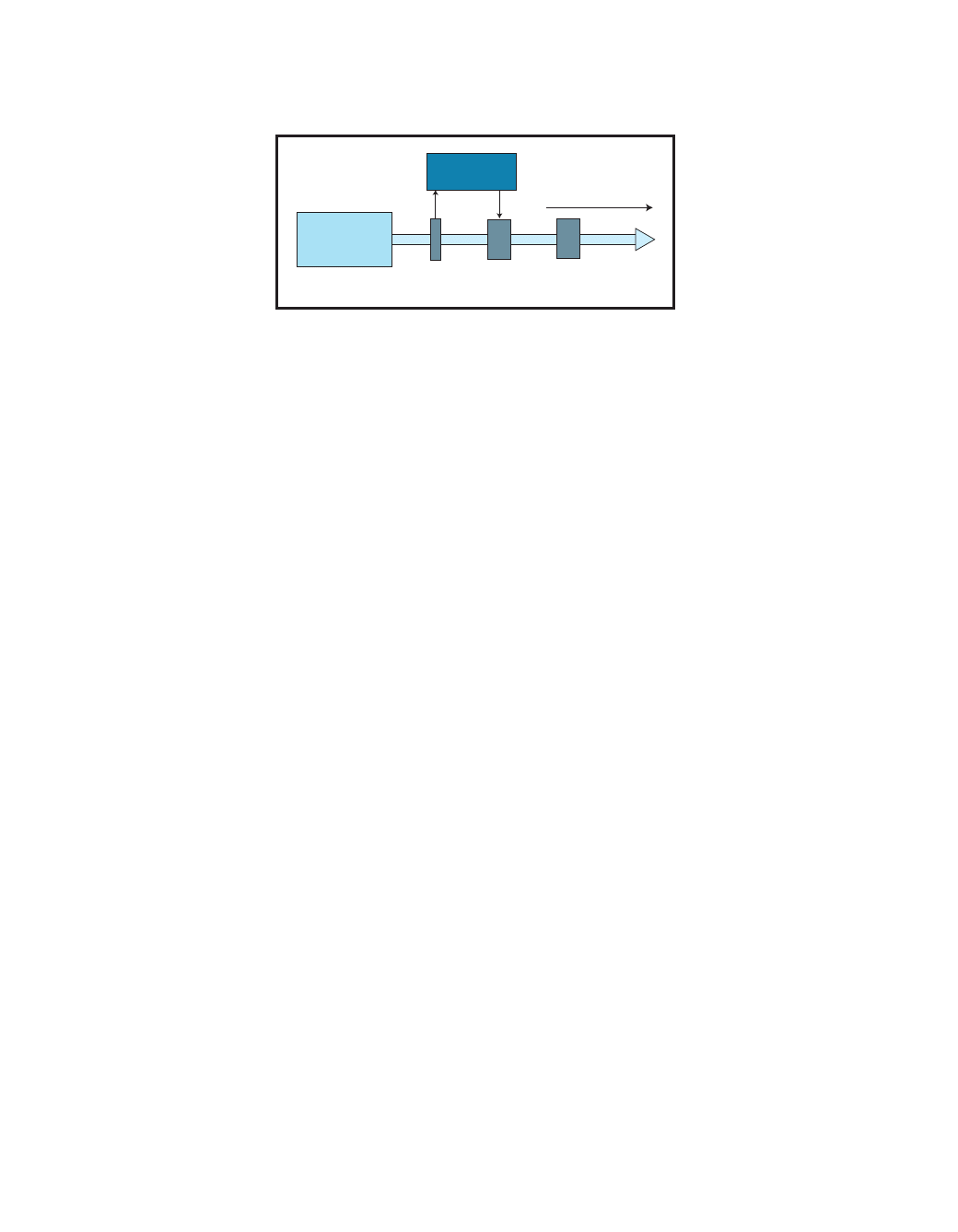

Figure 1 illustrates the system.

The device mounts on a shaft with

a wheel on the other end. The wheel

has a switch that closes every 6

″

. The

LCD tells you how to operate the

device and provides real-time feed-

back of the distance recorded and the

direction the unit is pointed. The

Yard-Stick constantly reads and aver-

ages the compass data, and every 6

″

it

records the current compass heading.

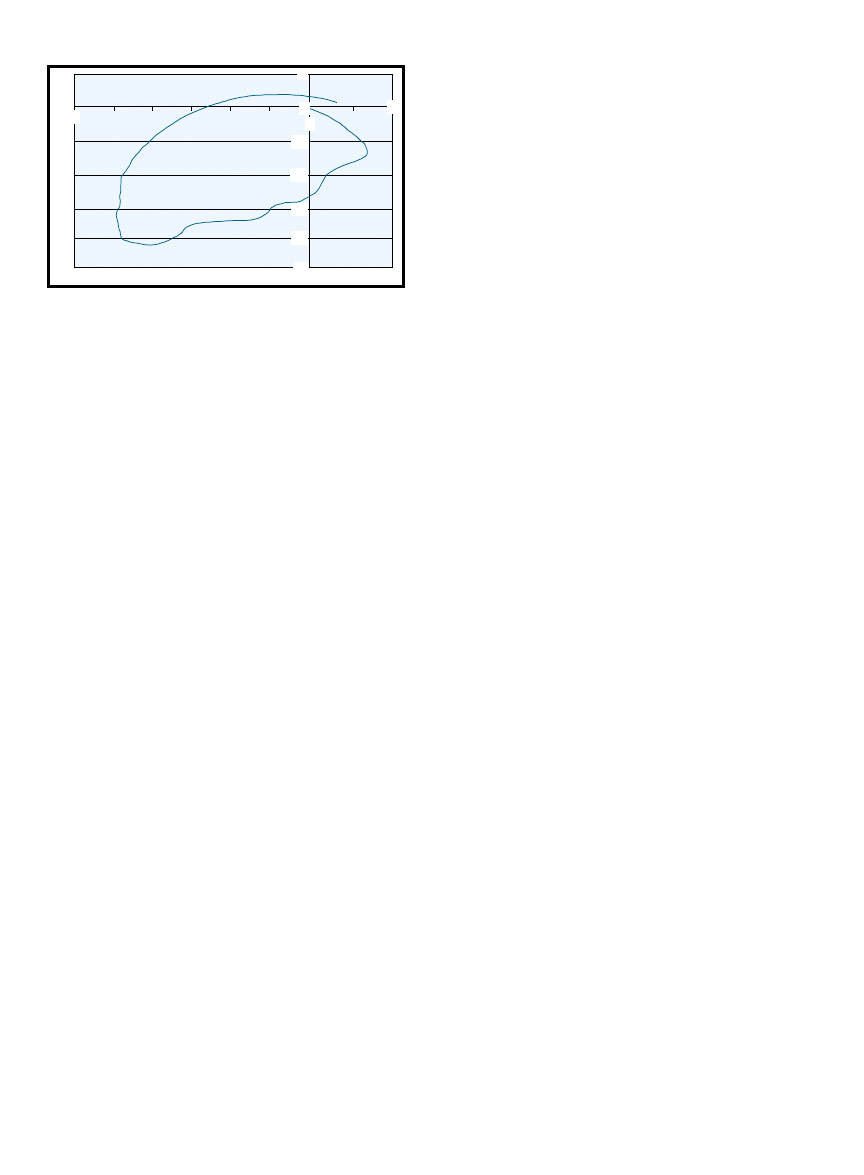

You can map the outline of multi-

ple areas by pressing the Start/Stop

button. Each closure defines a new

section to record. These sections then

can be downloaded to a PC via the

standard serial port as a text file. The

FEATURE

ARTICLE

With gardening sea-

son approaching,

David needed a way

to find out just how

much space the

flower beds took up.

With a little help from

a Philips LPC micro-

controller, there was

still plenty of time to

measure the gardens

and order the mulch

before snowfall.

David Penrose

The Yard-Stick

c

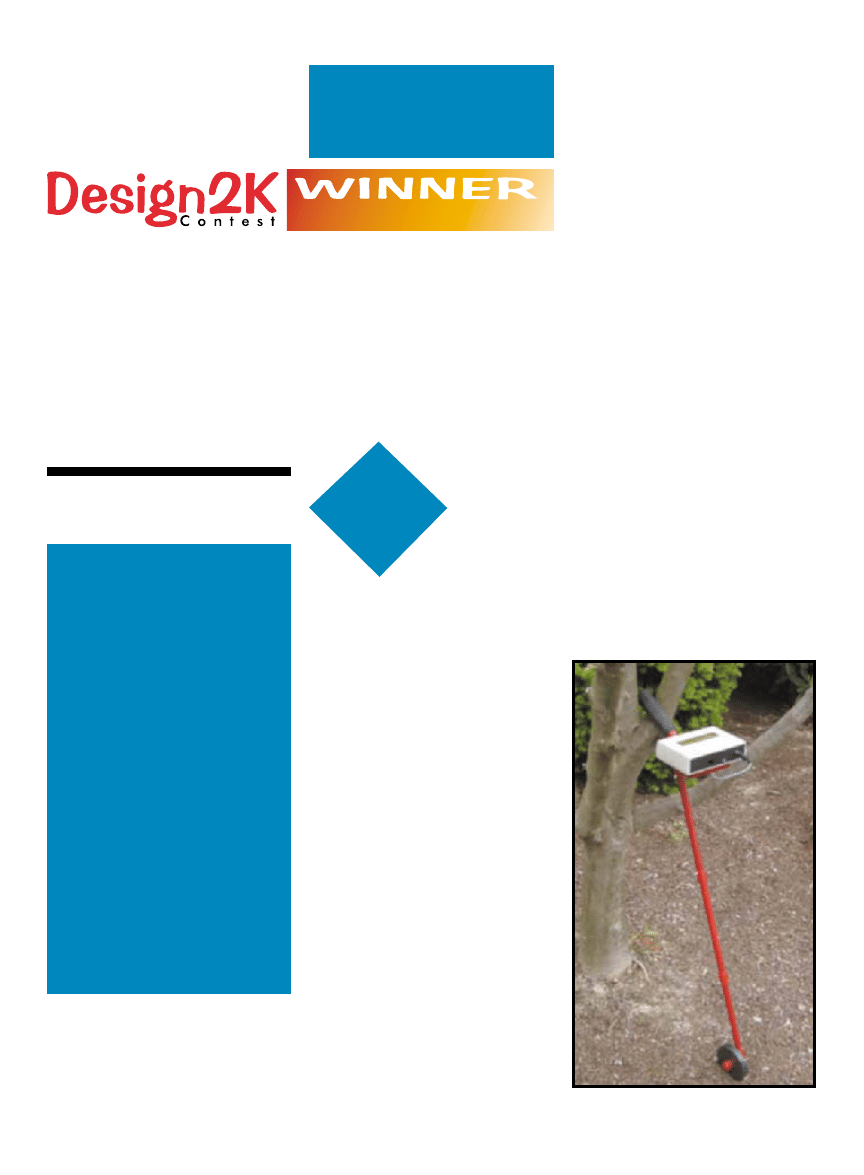

Photo 1—

Here’s the completed Yard-Stick.

www.circuitcellar.com

CIRCUIT CELLAR

®

Issue 130 May 2001

17

I

2

C EEPROM can record 4096 points

(two 8-bit words per point with 1° res-

olution); at 6

″

per point, that’s 2048

′

.

Section definitions are integrated with

the distance measurement; thus, they

don’t require additional storage. The

display is limited to 99.

The software was designed to make

the device simple and foolproof. You

can turn off power at any time and

not lose the data recorded. If the dis-

tances exceed 1800

′

, a display and

buzzer warn you that the memory is

filling up. You also are warned when

memory overflows, but at this point

the processor starts recording over the

oldest data. These features should

allow even the most avid gardener to

capture all the flowerbeds in one ses-

sion. Photo 1 shows the complete

unit with the measuring wheel,

frame, and electronic box.

Spring no longer carries the threat

of the unknown planter bed dimen-

sions. I am armed with the right tool

for the right job. But now spring has

passed, so I guess I have to wait until

next year to mulch. Once again tech-

nology comes to the rescue!

HARDWARE

The Yard-Stick uses a Vector 2X

compass. It is a two-axis, magneto-

inductive magnetometer that claims

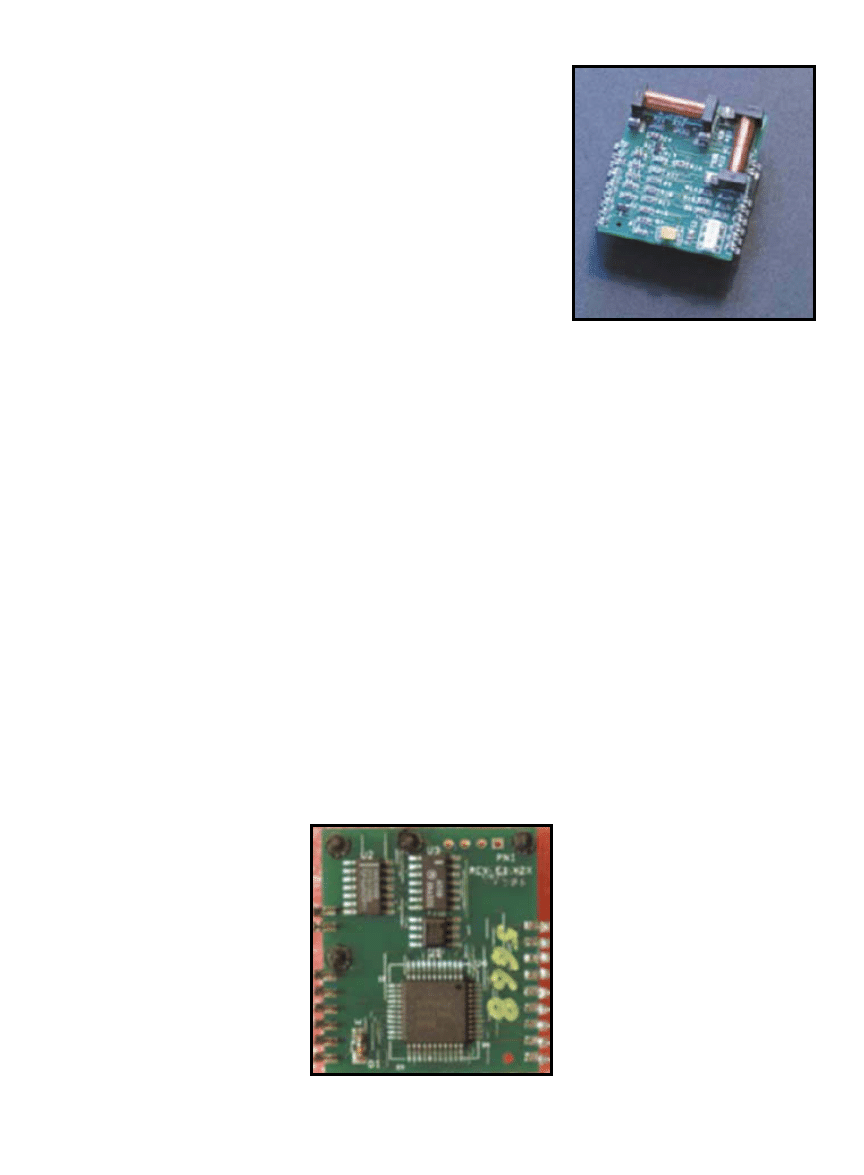

2° accuracy and 1° resolution. Photo 2

shows a top view of the unit and

Photo 3 shows a bottom view.

In Low Resolution mode, the com-

pass module is capable of five meas-

urements per second. The output is a

serial three-wire format compatible

with the SPI standard. The output for-

mat can be selected as binary coded

decimal (BCD) or binary output. This

project uses the latter. The Vector 2X

can be calibrated for “hard iron” devi-

ations, which means that it can be

mounted close to nonferrous metals

and the effect of these metals can be

calibrated out of the system’s output.

The Vector 2X can be operated in

Master or Slave mode. In Master

mode, it constantly outputs readings

following each internal calculation. In

Slave mode, a second device requests

a measurement and is notified when

the data is available. The processor

then must clock out 16 bits using the

clock line. Power for the Vector 2X is

standard TTL (5 V). Current draw in

Slave mode is about 4 mA when

polled at the 5-Hz rate and 100-µA

when idle. These power levels make

the unit attractive for a battery-pow-

ered device such as the Yard-Stick.

The Yard-Stick’s microprocessor is

the Philips 87LPC764, a 20-pin device

with 4 KB of onboard program memo-

ry and 128 bytes of RAM. The device

offers the option of disabling the

external reset and using an internal

reset, which frees one of the pins as

an additional input. I used this pin for

the end of conversion (EOC) signal

from the compass module to the

processor. If critical timing is not a

requirement for you, then an internal

oscillator can be selected, freeing the

two crystal pins as well.

In this application, the timing is

critical because the processor needs to

communicate using RS-232, so an

external crystal (11.0592) establishes

the clock frequency. The 87LPC764

has a high voltage tolerance allowing

for sloppy input supplies. Current

draw is about 5 mA when active, so

it’s an ideal device for a battery-pow-

ered application.

The processor includes the hard-

ware and firmware to support an I

2

C

bus that the Yard-Stick uses to com-

municate with an 8-KB EEPROM. If

you don’t use these pins for the I

2

C

feature, keep in mind that they are

open-drain outputs and must have a

pull-up to V

CC

to operate as outputs.

I’ve managed to forget these resis-

tors more than once and spent some

serious debug time chasing this trivial

mistake. The processor also has a

standard RS-232 serial port supported

by two pins (TxD and RxD). The

firmware behind this feature is stan-

dard with the ’8751 family and makes

serial communication a snap. In this

application, a MAX202 converts the

voltage on these pins to interface to

standard RS-232 levels using only the

5-V supply. The processor supports

two external interrupts, *INT0 and

*INT1 (*INT0 is shared with the SDA

pin on the I

2

C interface). The Yard-

Stick uses *INT1 to recognize switch

closure from the rolling wheel.

The processor has multiple timers

(Timer0, Timer1, watchdog, TimerI)

that are capable of supporting dedicat-

ed uses. Timer0 runs at about 8 ms to

establish a basic drumbeat to time

messages to you and debounce the

wheel and push-button switches.

Because I have faith in my software

(tongue is firmly in cheek) and upsets

can be cured with the off/on switch, I

didn’t use the watchdog timer.

Timer1I is capable of rescuing the

I

2

C bus from a hung condition. This

timer is tightly integrated with the

I

2

C hardware but still must be config-

ured for the approximate CPU clock

frequency and then enabled by the

software prior to the first I

2

C access.

After being enabled, it will interrupt

if activity on the bus ceases without a

stop condition being issued. The

interrupt logic should then try to free

the bus and reinitiate the processing.

The processor is also loaded with a

bunch of other features that allow you

Photo 2—

The X and Y sensor coils and the two rows

of connecting pins are on either side of the Vector 2X.

Photo 3—

The processing power is located underneath

the compass module.

18

Issue 130 May 2001

CIRCUIT CELLAR

®

www.circuitcellar.com

to compare voltage levels with

interrupts, detect brownout at

different power supply levels,

and so on. I see years of happy

experimentation with these

other features, but at some

point I decided to focus only on

the basics for the Yard-Stick.

NONVOLATILE STORAGE

Data storage is accomplished

using a 24C65 64-Kb serial EEP-

ROM. This chip is implement-

ed as 8192 8-bit words and is

designed to work with the I

2

C

bus. Multiple chips can be tied

to the I

2

C bus and addressed

separately using pins A0

through A2 on the 8-pin device. I

implemented only one chip at address

0 but included an extra socket just in

case the urge to grow hits me. The

chip has a pin that allows you to

write-protect the upper section of

memory in case the operating system

or some critical values need to be

stored in a secure space. The Yard-

Stick doesn’t use this and the words

are available for data storage.

The EEPROM’s limited number of

memory write cycles (1 million for

this device) isn’t a problem because

data is only written to the memory

when the wheel moves 6

″

. That

works out to be 500,000

′

, or 100 miles

for 1,000,000 cycles.

Each write takes about 10 to 15 ms.

A write can be up to 32 bytes, howev-

er, so speedup is offered by using this

page feature. The Yard-Stick writes

two words every time a meas-

urement is recorded, so you can

progress at the brisk pace of

50

′

/s (34 mph) without losing

data. The chip maintains data

without power so you can

measure an outside area, turn

off the Yard-Stick, go inside

and connect it to a PC, and

then download the data. When

powered up, the memory uses

less than 200 µA when active

and about 10 µA when inac-

tive.

The LCD is a standard 2 × 16

display with a low-voltage

backlight. I implemented the 4-

bit Communication mode to

conserve pins on the microprocessor

and have the clock share two of the

compass data pins. Contrast is con-

trolled by varying a positive supply to

pin 3 within about 600 mV. Some

higher performance units use a nega-

tive voltage to this pin, so check your

specifications. You can adjust this

voltage with a small potentiometer

that extends through the back of the

Yard-Stick.

As mentioned earlier, the RS-232

levels are converted by a MAX202

integrated circuit. This chip uses 0.1-

µF capacitors to generate the positive

and negative supply from the 5-V

input. These smaller capacitors make

a more compact arrangement and are

cheaper than the 1- or 10-µF caps used

by other units. The Yard-Stick uses

only one receiver and one transmitter

on this chip with no hardware flow

control implemented. This does not

create problems for the Yard-Stick’s

primarily one-way communication.

The only remaining hardware are a

low-voltage, low-power piezo buzzer,

an off/on switch, a push-button

switch with a pull-up resistor, and a

reed switch with a pull-up resistor for

the wheel switch. I placed 0.1-µF

capacitors between V

CC

and ground for

each chip and put a diode between

four AAA cells and the power to the

ICs. Then, the Yard-Stick was ready

for software.

SOFTWARE

The software is a simple polling

loop with two interrupt processes.

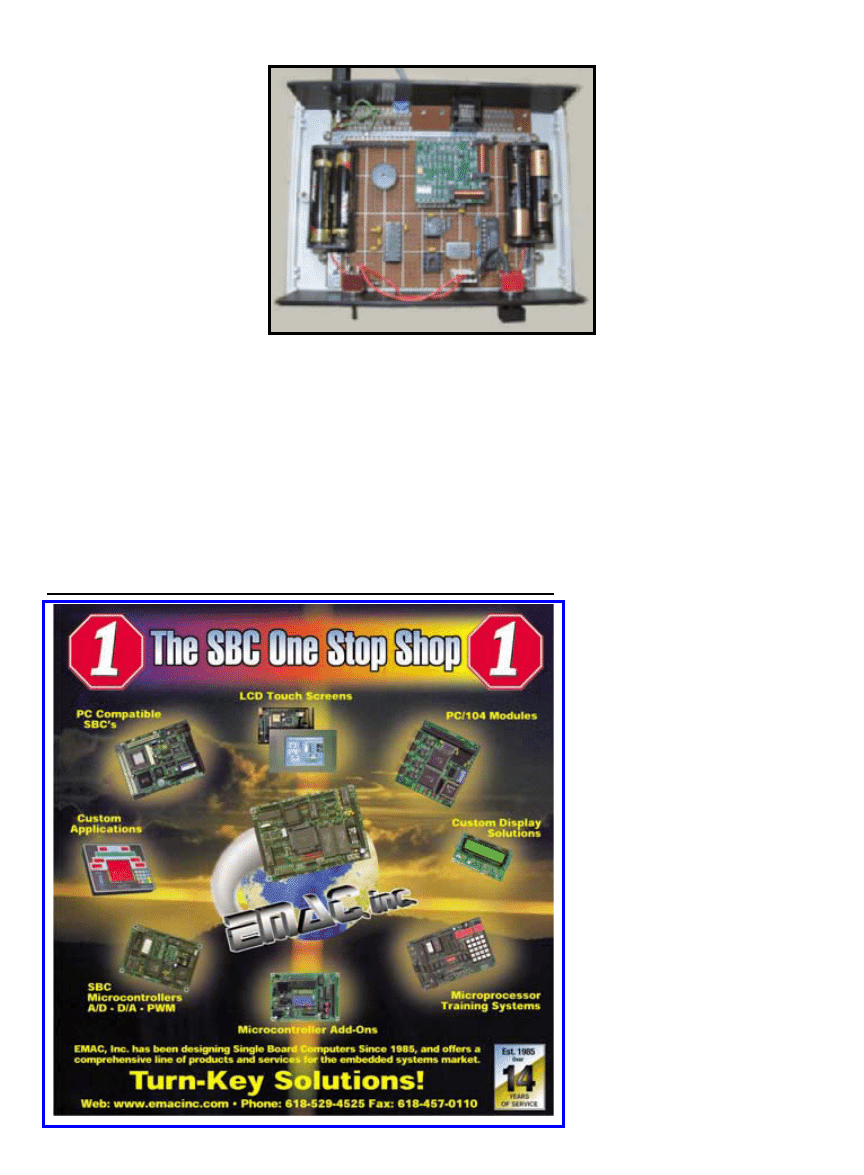

Photo 4—

The inside of the case shows the compass module mounted

with the processor, batteries, and auxiliary chips.

www.circuitcellar.com

CIRCUIT CELLAR

®

Issue 130 May 2001

19

The polling loop waits for you to push

the switch closure to change states or

for a serial character from a connected

PC to select some action. The device

begins from powerup by displaying

the sign-on message “Yard-Stick

V1.0”. It then enters a state waiting

for either a short button press to start

recording a section or a 2-s button

press to begin calibration. During the

waiting state, the Yard-Stick outputs

two messages to the display which

alternate at 2-s intervals.

The first message indicates the

device is waiting and you should press

Start to begin recording. The second

message indicates that a 2-s button

press will calibrate the unit. If the cal-

ibration action is selected, the next

message asks you to turn the unit

180° and press the button again. The

Vector 2X is placed in Calibration

mode by pulsing a pin on the device.

At the end of the calibration, the pin

is pulsed again and the compass cali-

brates its internal calculations.

Although you don’t have to cali-

brate, most people start recording ses-

sions with a calibration action

because it’s easy. Afterwards, the cali-

bration request message is suppressed.

Calibration can be done anytime the

unit is in-between sections by holding

down the button for 2 s.

When the device exits the waiting

state, it begins displaying a message

indicating the current heading both as

a compass point direction and numer-

ic degree. The distance traveled in a

direction is displayed on the same

line as the heading. The second line

of the display indicates the total dis-

tance traveled in the section. Each

time the compass direction changes

and the wheel records motion, the

distance at the current heading is

zeroed. The compass is read constant-

ly and a running average of four sam-

ples is calculated. The output of this

running average is displayed on the

LCD or recorded in memory.

Recording data in memory is trig-

gered by the wheel closure interrupt.

With each interrupt, the current com-

pass heading is recorded in memory

as two 8-bit words. The first word

contains the MSB of the integer value

and the second word contains the

LSB. Each time you

begin a new section,

the Yard-Stick records

one entry in memory

with the current head-

ing and bit 7 of the

first word set to indi-

cate the beginning of a

section.

Each wheel closure

interrupt then adds

entries to memory. If

you pause for 15 s, the

device will automatically write a stop

code (bit 6 of the first word) to the

last valid memory entry. If you con-

tinue moving, the stop code will be

removed as new entries are added.

This code ensures that if you shut

down without pressing the Start/Stop

button, a proper sequence will remain

in memory for the PC transfer. After

the stop code is added to memory, a

message asks you to press the

Stop/Start button to end the section.

The normal screen is displayed if the

unit begins moving again or after 2 s.

At the end of a section, the LCD

indicates the number of sections cur-

rently recorded and the total distance

traveled. This message is displayed for

2 s and then the “waiting for

start/stop button” message is dis-

played. These two messages alternate

until you press the button to begin a

new section or turn off the power.

If you exceed 90% of the 2048

′

capacity of memory, a low-memory

message is displayed and the piezo

buzzer is enabled. This continues for

5 s and then the normal display

returns. If the wheel is moving during

this time or if you press the button,

the normal actions will take place

because the wheel is processed during

an interrupt and the software is con-

stantly polling for a switch closure.

If recording continues past the

point of filling memory, an alarm

again will sound and the software will

record at location 0. Later, when data

is being dumped to a PC, this condi-

tion is recognized by a missing start

code in the first word of memory. All

memory is dumped to the PC to make

sure no data is lost. Normally only

data that is bracketed by a valid

start/stop code is dumped to memory,

but this overflow condition will prob-

ably disrupt these start/stop pairings.

The PC passing an “X” to the Yard-

Stick, indicating that an export of

data is desired, triggers dumping data

to a PC. The Yard-Stick responds by

putting out a message “Section x”,

indicating that the following data is

for the specified section (x). Then,

some lines of data will be output with

a three-digit number on each line

indicating the compass heading in

degrees. The format uses a carriage

return at the end of each line with no

line feed. The rate is 9600 bps with 8

bits, 1 start, 2 stop, and no parity bits.

At the end of the section, a message

“End x” will be output to indicate the

last data for the current section. If

more data is stored in memory, then

the next section will be output in the

same format. At the end of the export

process, the processor delays 10 s so

you can close the transfer operation.

After that, the processor reinitializes

itself. Data will remain unchanged in

memory; it changes only when you

press the Start/Stop button to begin a

new section.

Note that a number of other PC

actions are used to facilitate checkout

and maintenance. Any single charac-

ter code from the PC that is not rec-

ognized as one of these valid actions

will result in the display of a help

message. I did most of the unit check-

out using a hand-held terminal that

has a 4 × 20 display. One of the

actions codes (T) switches between

special positioning codes for this ter-

minal and the VT100 codes selected

for the standard PC display.

The Yard-Stick will display either

an “S-” or “H-” message indicating

which device it believes it is talking

Rolling

wheel

switch

Push-button

switch

2 × 16

LCD display

87LPC764

Microprocessor

Digital compass

module

8-KB EEPROM

memory

PC Connection

Figure 1—

This diagram of the Yard-Stick shows the major components.

20

Issue 130 May 2001

CIRCUIT CELLAR

®

www.circuitcellar.com

to. On-chip and I

2

C memory can be

read or written with the E and W

commands. The distinction between

these two memory spaces is made

when you enter either a two- or four-

character address. The former indi-

cates that the 128-byte on-chip mem-

ory is being addressed and the latter

indicates that all addresses are meant

for the I

2

C memory.

The processor can be restarted

using the F command to indicate that

a fresh start is desired. The averaging

of compass module samples can be

disabled by the A code. Each time the

A code is entered, the unit toggles

between averaging and no averaging.

The D command indicates that a

debug output is desired, and every

reading from the compass, the last

four samples, and the average value

are output to the display. This opera-

tion is toggled in the same fashion as

the A and T actions.

INTEGRATION

Photo 4 shows an internal view of

the electronic enclosure. The compass

module is a simple but demanding

device. My recommendation is to

read, reread, and read the spec sheet

again. The unit needs to be positioned

in the device with the pins labeled

P14–P11 pointing to the front, as is

shown in Figure 2.

The power-up sequence is also criti-

cal but easy. When power is applied,

the unit expects the Poll/Continuous

(*P/C), Calibrate (*CAL), Slave Select

(*SS), and Reset pins to be in a high

state. The *P/C, *CAL, *SS pins

weren’t a problem because they are

connected to the 87LPC764,

which I programmed to initial-

ize with high port pins. The

Reset pin must be left open to

make sure it goes high also.

Tying this pin to a 10-K

Ω

pull-

up resistor just confused the

unit because the voltage didn’t

rise as fast as the processor

pins. When confused, the

device plays dead.

This device is an interesting

mixture of an SPI interface and

control pins. The *SS input

selects the device for data read-

out and hence, floats serial

data out (SDO) and serial clock

(SCLK) when inactive. It doesn’t float

the calibration indicator (CI) nor end

of conversion (EOC) signals, however.

This means that pins need to be dedi-

cated on the processor to interface to

these signals.

I didn’t use the CI pin but did use

the EOC pin. I could have ignored the

EOC pin and replaced it with a soft-

ware delay that would allow for the

processing delay inside the compass,

but this gets ahead of the story.

Because *SS floats the SDO and

ignores the SCLK, I put these two sig-

nals on the same pins as two of the

data bits to the LCD display. The

LCD won’t read these pins until its

Enable (E) line is high, and the com-

pass won’t use them until the *SS

line is low, so everyone is happy if the

software cooperates. Cooperation

means leaving the shared SDO pin in

a high state when done with it (the

’51LPC issues a weak pullup in this

mode) so a read of the SDO can occur.

To use the device, the sequence

pulses the *P/C low for at least

10 ms. When this pin goes low, the

EOC pin will also drop low. After tak-

ing *P/C high, the software then

monitors the EOC line waiting for it

to return high (normally takes about

100 ms). After this line is high, the

software can select the device with

*SS low and begin clocking out 16

bits from SDO by pulsing SCLK (wait

5 ms prior to the first clock pulse).

The module allows pins *P/C and

*SS to be tied together with the only

penalty being that SDO and SCLK are

active when *P/C is pulsed low to

begin a conversion. This wasn’t a

problem in the Yard-Stick, so I saved

a pin by tying these two together.

With the low-to-high transition of

each clock, the SDO line returns a

data bit. Timing of these clock pulses

needs to be less than 1 MHz until the

last clock bit goes high, then the

processor has only 20 µs to read this

last data bit.

I turn off interrupts for this part of

the process to avoid problems. If the

*BCD/BIN pin is high or floating, this

data will be MSB to LSB of a 16-bit

integer indicating degrees. If you want

to use BCD instead, tie the *BCD/BIN

pin low and interpret the 16 bits as

BCD instead of the 16-bit integer.

The Resolution (*RES) pin selects a

high- or low-resolution internal pro-

cessing mode. The Yard-Stick uses the

latter. In Low-Resolution mode (pin

grounded), data is available at a 5-to

10-Hz rate. Pulling this pin high puts

the unit into High-Resolution mode,

which is recommended with areas of

weak magnetic force. In this mode,

samples are available at 2.5 to 5 Hz.

By the way, don’t mistake this pin for

the Reset pin.

If you want to do it yourself, note

that the compass has a Raw pin.

Grounding this pin results in the unit

returning 32 bits of raw X and Y sen-

sor data. You can then calculate head-

ing or magnetometer readings using

equations that are supplied with the

spec sheet. The advantage here is that

you can do your own calibration and

preserve this in software. The com-

pass module loses its calibration

information when power is removed.

The disadvantage is that there is an

ungainly amount of calculations

involved with bunches of sines,

cosines, tangents, and so forth.

Calibration can be maintained in

the compass module if power is held

at or above 2.5 V. However, this fea-

ture is fussy and gets back to the

problem of making sure the four criti-

cal lines are in the proper state at all

times. Because calibration is an easy

task and better accuracy is gained by

calibrating the unit in the area it will

be used in, I didn’t use this feature.

Because the unit is measuring line

angles of magnetic fields, any devia-

Front of vector compass module

x axis (L2)

y axis (L1)

P11

P10

P9

P17

P8

P4

P12

P13

P14

x *FLIP

y FLIP

*BCD/Bin

*RESET

*M/S

*SS

CI

EOC

*RAW

P6

P5

P7

P3

P2

P1

*CAL

*P/C

*RES

SDI

SDO

SCLK

P16/GND

P15/V

CC

Figure 2—

Notice that the front is actually the side of the com-

pass. The SDI pin is not used by the module.

www.circuitcellar.com

CIRCUIT CELLAR

®

Issue 130 May 2001

21

tion from level changes the

compass reading. Vector 2X

offers a gimbaled unit that

helps maintain a level posi-

tion while it’s operating. This

is a bigger unit with mechani-

cal gimbals, and it doesn’t eas-

ily fit into my initial packag-

ing. One degree of tilt will

give about 3° of heading error

in Mountain View, California.

In Greenland, that same 1°

will give 10° of heading error.

I designed the case mount so

you can move the case to

level it to ground to minimize

these errors. They can be sig-

nificant and Greenland gar-

deners are forewarned.

The unit has two pins

labeled as x Flip and y Flip.

The pins allow you to flip the x and y

axes. Normal operation is x Flip open

and y Flip grounded. This produces

the familiar 0° for north, 90° for east,

180° for south, and 270° for west.

Figure 3 shows the necessary connec-

tions to the compass unit.

I added averaging to the compass

output to smooth the data. The logic

uses a simple running average of the

last four points read from the com-

pass. The difficulty was in processing

through the 0° to 360° transitions. An

average of two samples at 359° and

two at 0° lead you to believe the unit

was pointed south at 180°.

I chose the easy way out and set a

tolerance band at about the current

averaged value, 60°. If the average

value is 300° to 359°, all entries in the

table between 0° and 59° are convert-

ed to 360° to 419° prior to extracting a

new average. If the average value is

between 59° and 0°, all entries in the

table between 300° and 359° are con-

verted to –59° to –1°. This seems to

work, but the tolerance band needs to

be set based on how rapidly the com-

pass may be moved.

I use the LCD in 4-bit interface

mode with the read/write line tied

low to make it a write-only interface

from the processor. In this mode, the

processor needs to wait after every

operation to make sure the LCD is

ready for the next one. A timeout of 5

ms for position and clear commands

is used. A 160-µs delay occurs follow-

ing the output of the two nibbles that

make up the 8-bit data word. A pin is

dedicated to the enable line (E) and

the control/data (RS) line, although

the RS can be shared. Four lines from

the processor communicate the data

nibble.

The I

2

C memory uses a 16-bit

address with the upper three bits

being forced to 0 to limit addressing

to 8192 bytes. Communication to the

device begins by the processor arbi-

trating for the I

2

C bus; that’s always a

win for the 87LPC764 because no

other masters exist.

This arbitration process involves

the issuing of a Start command by the

processor. This is a unique configura-

tion of the clock and data lines where

the data line is driven low and the

clock line is left high. Without this

condition, nothing can begin. Now

you know why leaving the resistors

off these lines will kill everything.

The I

2

C memory chip slave address

(1010000xb) is then output. The 1010,

or “Ah”, portion of the address desig-

nates an EEPROM chip and the 000

portion is the address of this chip as

selected by address pins A0 through

A2. And last, the x is a 0 for a write

from the processor or 1 for a read to

the processor.

Additional EEPROM chips would

have different LSBs for an address.

Different I

2

C types of devices would

have a different MSB. It’s a pretty

smooth system.

The master device always drives

the clock line, in this case the ’764

processor. Either the master or slave

may drive the data line depending on

the direction of the data transfer. The

I

2

C memory device will pull the data

line low on the ninth pulse of the

clock line from the processor. This is

the gratifying response called

acknowledge. Lacking this one little

pulse can make life extremely diffi-