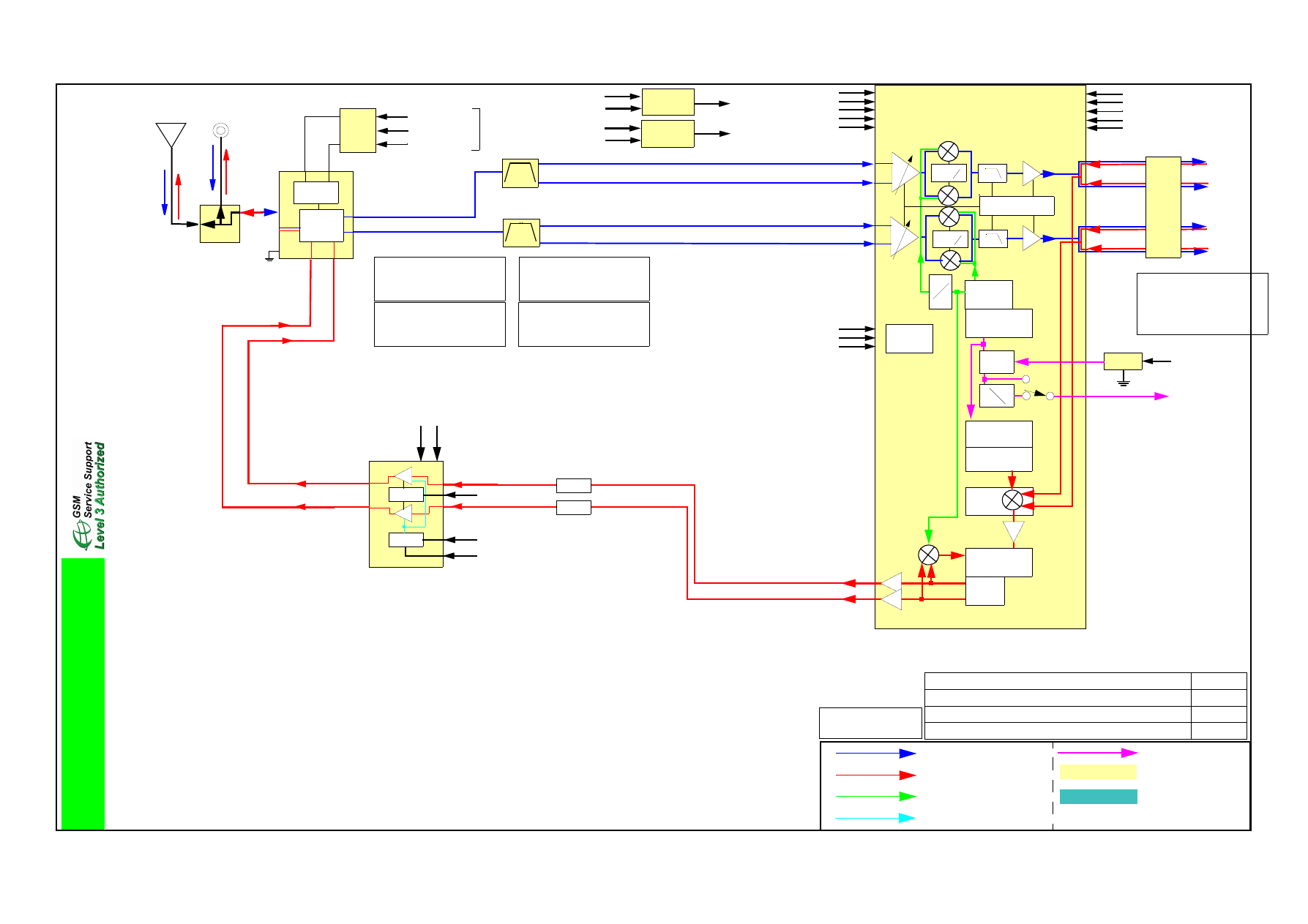

RX SIGNAL PATH

TX SIGNAL PATH

MAIN VCO SIGNAL PATH

TUNING VOLTAGES

REFERENCE CLOCK

1805-1880MHz

Orderable Part

Non - Orderable Part

925-960MHz

GSM SERVICE SUPPORT GROUP

2003.06.04

LEVEL 3 RF Block Diagram

Rev. 1.0

Dual Band C200

Michael Hansen

Page 1 of 2

ANT 1

CALIBRATION

RF PORT

GSM_RX

DCS_RX

TX_GSM

TX_DCS

U708

PA/PAC

GSMTX

DCSTX

G

S

M

T

X

D

C

S

T

X

6

RF Switch

Control

GSM_T/R

DCS_T/R

1

3

4

6

V_BR

90

o

1

2

90

o

1

2

Gain Control

26

25

24

23

6

7

9

10

IP

IN

QP

QN

U801

AFC

(SPI BUS)

17

19

1

3

13Mhz

IQ Dual

CTNL

BS1

VBAT

TCXOEN

V_BR

V_SYN

V_TX

U751

V_RX

V_BR

(VCC)

Supports:

VCC for GSM 1800 LNA - 13

VCC for OPLL & Phase detector - 15

VCC for IQ Modulator - 23

VCC for BaseBand - 46

VCC for RF Local Buffer & Divider - 47

VCC for Direct Conversion Mixers - 51

GSM TX

DCS TX

(Both Low For RX)

5

RF ANTENNA

U707

7

1

5

11

9

6

EGSM RX

Low Channel - 975 = 925.2Mhz

Mid Channel - 37 = 942.4Mhz

High Channel - 124 = 959.8Mhz

EGSM TX

Low Channel - 975 = 880.2Mhz

Mid Channel - 37 = 897.4.4Mhz

High Channel - 124 = 914.8Mhz

GSM 1800 RX

Low Channel - 512 = 1805.2Mhz

Mid Channel - 700 = 1842.8Mhz

High Channel - 885 = 1879.8Mhz

GSM 1800 TX

Low Channel - 512 = 1710.2Mhz

Mid Channel - 700 = 1747.8Mhz

High Channel - 885 = 1784.8Mhz

DUAL-BAND TRANCEIVER IC

U601

D

u

a

l

B

a

n

d

C

2

0

0

Revision Overview

Rev. 1.0: initial Block Diagram

RF VCO

2

1

2,4

35

VCXO

2

1

31

Phase Det

Charge Pump

RX

IF VCO

Phase Det

Charge Pump

TX

R624

1

2

3

4

5

6

7

8

TX I/Q

Phase Det

Charge Pump

TX

VCO

PAC

RAMP

2

TX_ON

3

R626

2dB

R628

5dB

VBAT

4

MOD

TX / RX Switch

3

8

U706

5

9

7

1

11

2, 4, 6

Duplexer

Control

Function

U701

U702

10, 12

5

U705

1

3

VBAT

TCXOEN

U751

1

3

5

5

V_BR

48

(VCCMixer)

V_SYN

42

(VCC RF Local Oscillaror)

V_RX

41

(VCCRF VCO)

V_BR

40

(VCC Base Band)

V_SYN

37

(VCC RF Synthesizer)

V_SYN

27

(VCC TX IF Synthesizer)

V_BR

22

(VCC IQ Modulator)

V_TX

14

(VCC TX VCO)

V_BR

13

(VCC PLL)

V_BR

1

(VCC Low Noise Amlifier)

SPI

DATA

CLK

LE

29

30

32

( for IC Control)

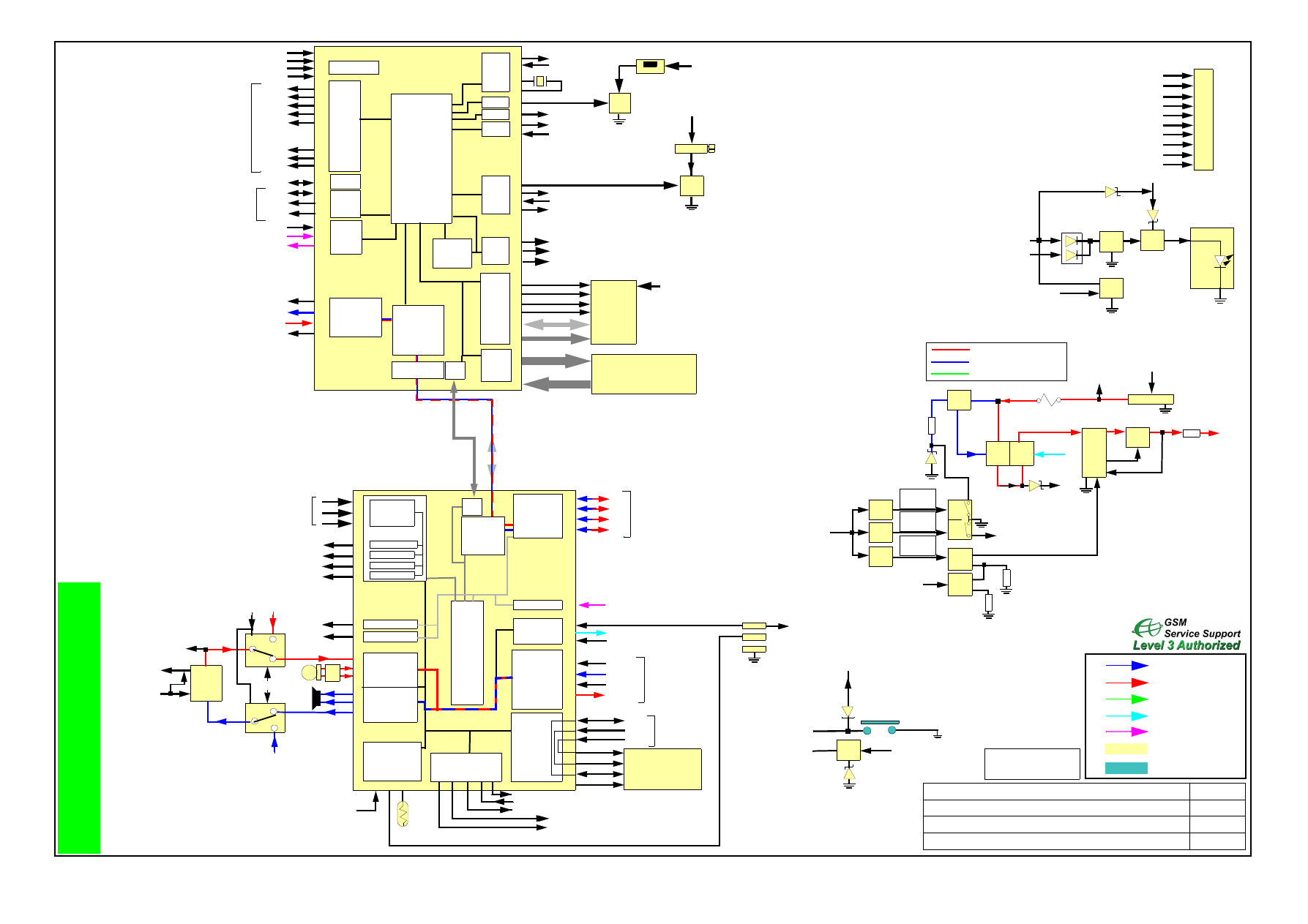

RX SIGNAL PATH

TX SIGNAL PATH

MAIN VCO SIGNAL PATH

TUNING VOLTAGES

REFERENCE CLOCK

Orderable Part

Non - Orderable Part

LS1

SPKR

QN

QP

IN

IP

from/to U601

TR1

KEYPAD MATRIX

S19

LCD

Keypad

Backlights

PWON

NFOE

NROMCS1

RNW

VIBRATOR

BQ4

b

e

c

D

u

a

l

B

a

n

d

C

2

0

0

GSM SERVICE SUPPORT GROUP

2003.06.04

LEVEL 3 AL Block Diagram

Rev. 1.0

Dual Band C200

Michael Hansen

Page 2 of 2

J2

POWER

RTC

X1

PWT

PWL

UART

IIC

GPIO

Keypad

MEM

I/FACE

ARM 7

2M RAM

VR3 - 2.9V

VR1 - 1.8V

VR2 - 2.9V

VR2B - 2.0V

BACKUP

HERCULES U1

OMEGA

IBIC

BUS

CNTL

Battery

USP

3V / 5V

LEVEL

SHIFTERS

TSP

AFC

APC

AFC

To U801

To U708

RAMP

X2

MIC

U14

RXDO

TXDO

U8

U10

I0

3

D

A

T

A

_

H

P

_

S

E

L

VR2B_SW

J3

Audio

Jack

VR3

IO13ACCIN

VCLKRX

VDX

VFSRX

VDR

To / From Hercules

SIM I/Face

SIM CONTACTS

U2

CLK

RST

I/O

VSIM

S_CLK

S_RST

S_IO

To / From Hercules

VCC1

VCC2

VCC3

VR2B

VR2

VR1

VR3

VBAT

BATTERY

CONNECTOR

JP1

NRESET

RTCINT

ON_OFF

PWON

(to Power Switch - S19)

J1

POWER JACK

F1

ICTL

Main Charge Path

G1

G2

Charger Overvoltage Protection

Battery Over Voltage Protection

VCHG

VBATBB

(To Omega Regulators)

ROW4

(To Hercules)

TCXOEN

ON_OFF

(To Hercules)

TX_ON

DCS_T/R

GSM_T/R

BS1

To RF Side

RTCINT

BQ3

VBAT

U13

ALERT

BU

b

e

c

BL

BL

TXDO

RXDO

(To Headset Jack)

LCD Connector

VLCD

12C_SCL

12C_SDA

NRSTOUT

VBAT

IO0VIBRATOR

M1

IO3DATA_HP_SEL

IO13ACCIN

FDP

DATA BUS

ADD BUS

FLASH

MEMORY

16Mbit

VR2

U5

ROW 0 - ROW 4

COL 0 - COL 4

13MOUT

E11

D6

E6

E9

B10

B13

H10

E10

A11

C2

B1

D2

D3

F4

C4

K11

A7

M6

J1

N8

L8

P6

M9

B3

F8

D7

B4

E1, F5

K3

D2

G3

D1

E1

H1

H10

F8

F9

E6

A5

A2

D4

B5

B4

C4

B3

B2

G6

G7

K7

H6

E4

E5

E3

D9

D8

C10

C9

1

3

2

4

Micro Proc.

Ser. Port

(TX Downlink)

(RX Downlink)

Charger. Int

Inter IC

Cntl.

S1

D1

S2

D2

D2

VCHG

CHARGER_IN

U12-1 U12-2

E

C

B

BQ5

DZ1

PNP

D3, D4

D5 - D10

VBATBB

D18

BQ2

E

B

C

D20

U7

E

C

B

SIM

JTAG

VOICEBAND

Interface

S_RST

S_IO

S_CLK

to / From Omega

NRESET

13Mhz

13MOUT

From U601

to Omega

VCLKRX

VDX

VDR

VFSRX

J13

K14

J14

G3

G14

L14

G11

H12

H13

H11

TIMER

( OLYSSE )

Revision Overview

Rev. 1.0: initial Drawing

VSS

VSS

12C_SCL

12C_SDA

NRSTOUT

VDD2,3

VDD1

GND

GND

1

2

3

4

5

6

7

8

9

10

D2

U11

3

1

E

C

B

BQ6

PNP

6

(Drive)

5

(Batt. Sense)

Charger

ICTL

(Charge Current

Control)

R62

VBAT

U21

U21

2

5

U6-1

U6-2

U16

U17

U18

2

2

2

1

1

1

VBAT>4.4

out = High

VBAT>4.1

out = High

VBAT<3.1

out = Low

1,4

6

U12-1 = off

4.1INV

(4.1 Inverse)

4.1INV=GND

GND

4.1INV

U11= On

4

6

1

3

4

R66

R68

7.5K

7.5K

VBATBB

1

2

3-5

ON/OFF

VR3

CHARGER_IN

( Sense)

(Program)

2

VBATBB

1

2

3

BATTEP

EARPHONE_IN

EARPHONE_IN

C6

Charger

Connector

D19

VCHG

E

D17

RPWON

U7

C

VCHG

RPWON

(to U7)

A4

VBAT

R24

0.2

Power

IC

Charge

Transistor

BASEBAND

UPLINK/

DOWNLINK

VOICE

VOICE

J8

K8

H7

H8

H9

J9

UPLINK

DOWNLINK

VRPC

B10 D10 D7 F6

Volt. Reg. and

Power up Ctnl.

A10

PORT

SERIAL

SPI

Int.

M

C

U

D

I

M

C

U

D

O

M

C

U

E

N

0

BASEBAND

PORT

SERIAL

BDR

/

BFSR

BDX

/

BFSX

DSP

Radio

Int.

ADC

Analog/Digital

Converter

U3

SPI

TCK, TMS, TDO, TDI,TXDO,RXDO,TXD1

DATA

CLK

LE

D14

E14

RX/TX

CNTL

B6

(to Display)

U19

E

B

C

IO9_CHR_LED

IO9 CHR_LED

A9

VR1

VR2

VR2B

VR3

(1,8V)

(2,9V)

(2,9V)

(2,9V)

Wyszukiwarka

Podobne podstrony:

więcej podobnych podstron