Krzysztof Filipek 3D6 (164333)

Sprawozdanie z laboratorium przedmiotu Wstęp do Techniki Cyfrowej i

Mikroelektroniki

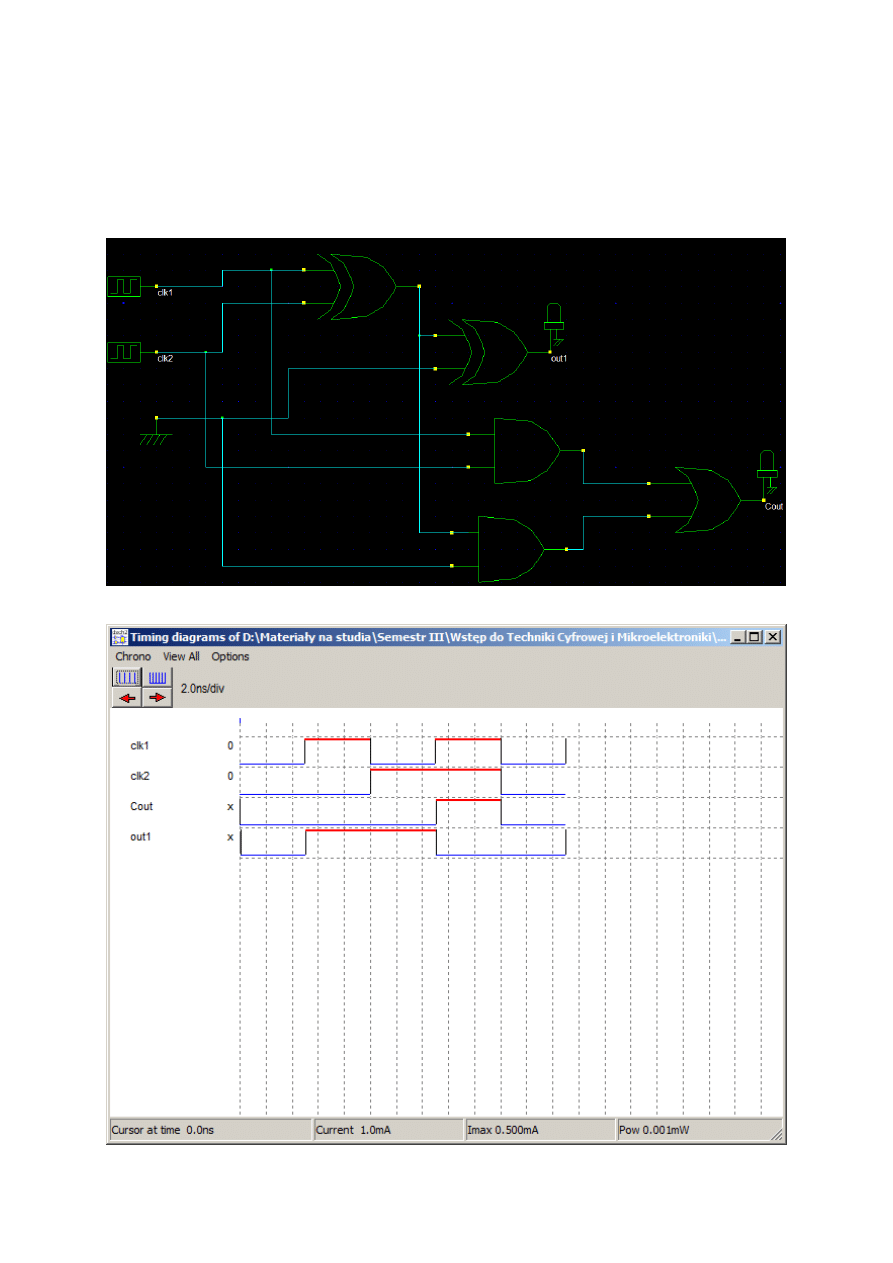

Sumator 1-bitowy:

Przebieg czasowy sumatora 1-bitowego:

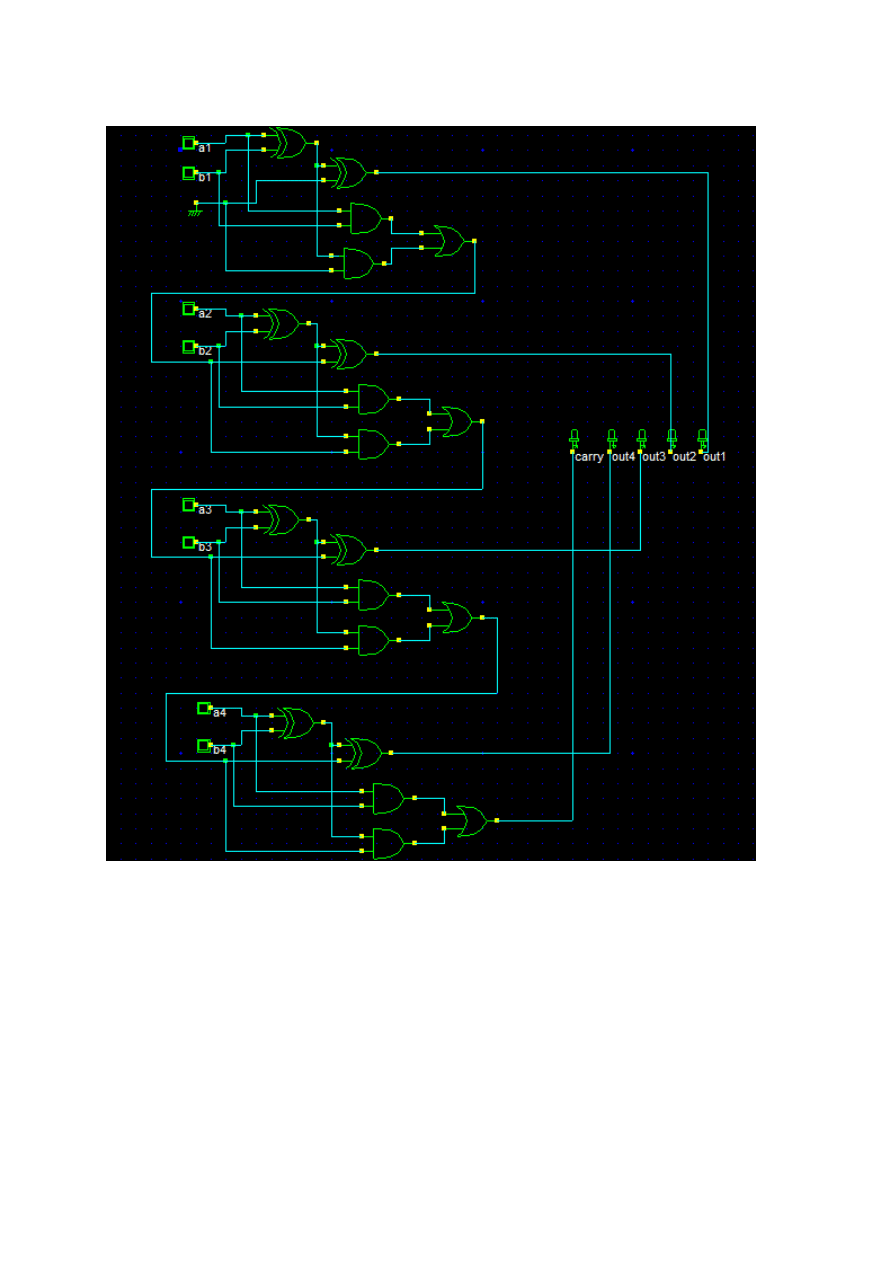

Sumator 4-bitowy:

Przebieg czasowy sumatora 4-bitowego:

Schemat synchronicznego licznika 3-bitowego zaprojektowanego z wykorzystaniem przerzutników

typu T:

Przebieg synchronicznego licznika 3-bitowego:

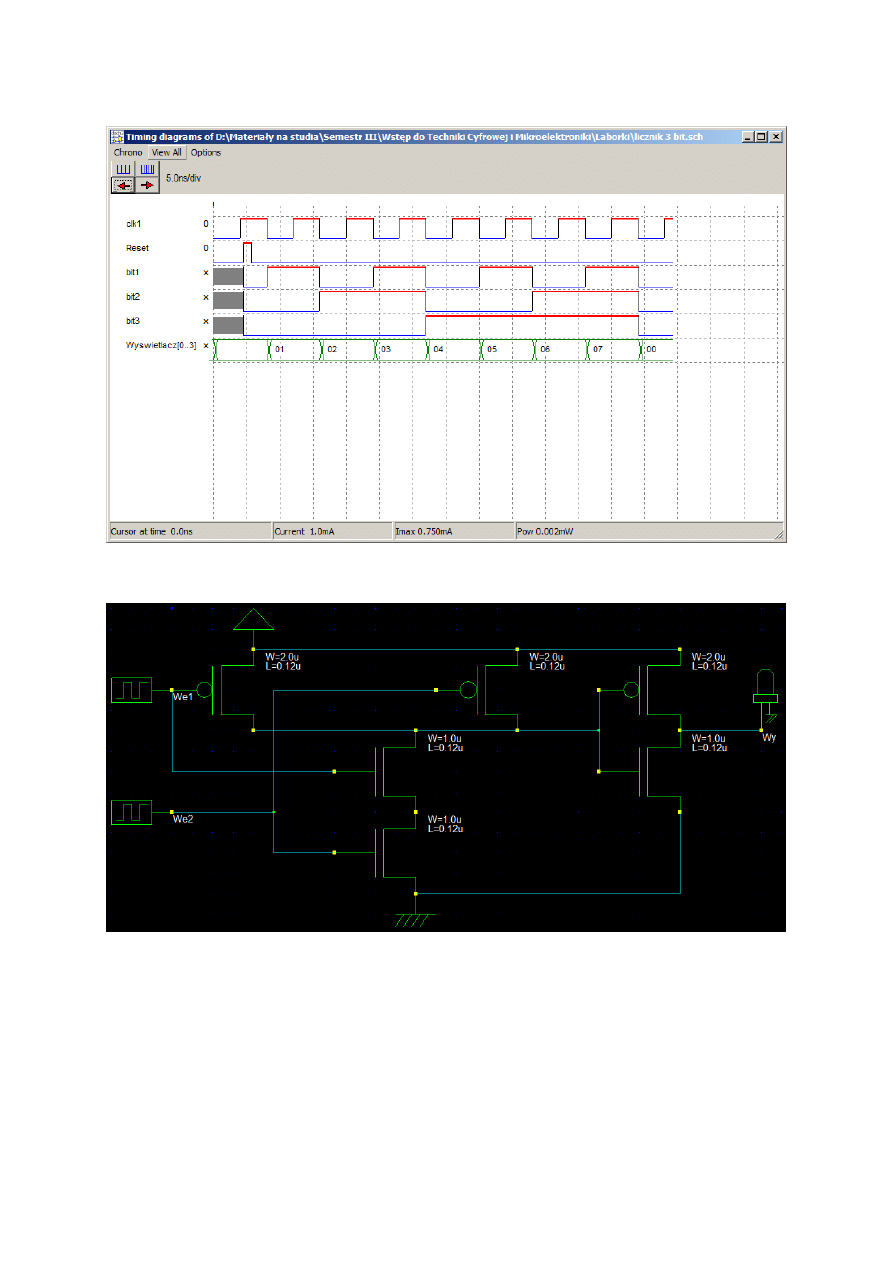

Schemat układów logicznych wykonanych z użyciem tranzystorów n-MOS i p-MOS:

Schemat bramki AND:

Przebieg czasowy bramki AND:

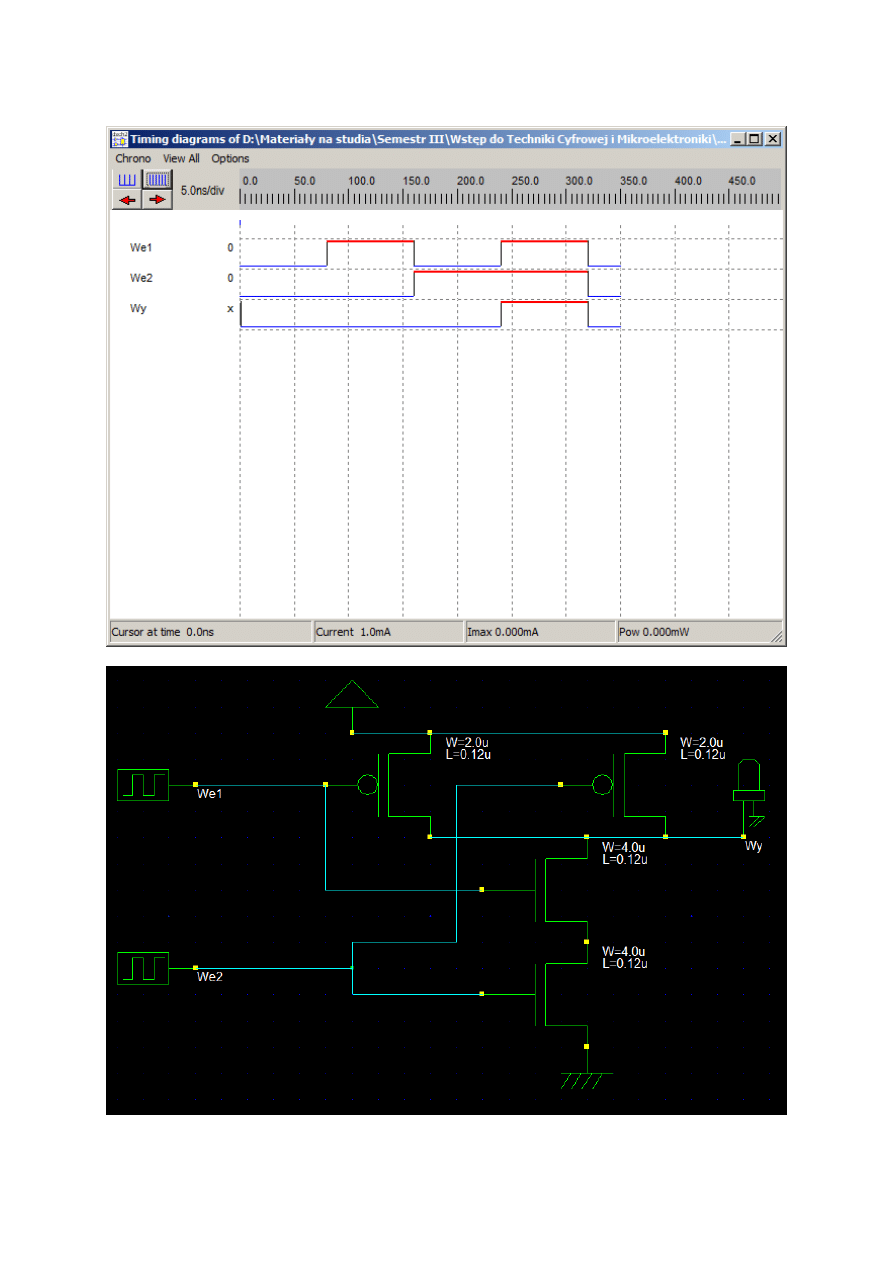

Schemat bramki NAND:

Przebieg czasowy bramki NAND:

Schemat bramki NOR:

Przebieg czasowy bramki NOR:

Schemat bramki OR:

Przebieg czasowy bramki OR:

Wykorzystanie programu PSpice do symulacji układów:

Inwerter statyczny:

*INWERTER STATYCZNY

.LIB I:\Spice\cmos7tm.mod

VDD 1 0 5

V1 2 0 DC 5

M1 3 2 1 1 MODP W=0.24u L=0.7u

M2 3 2 0 0 MODN W=0.24u L=0.7u

.DC V1 0 5 0.1

.PROBE

.END

.LIB I:\Spice\cmos7tm.mod

VDD 1 0 5

V1 2 0 DC 5

M1 3 2 1 1 MODP W=0.48u L=0.7u

M2 3 2 0 0 MODN W=0.48u L=0.7u

.DC V1 0 5 0.1

.PROBE

.END

.LIB I:\Spice\cmos7tm.mod

VDD 1 0 5

V1 2 0 DC 5

M1 3 2 1 1 MODP W=2.4u L=0.7u

M2 3 2 0 0 MODN W=2.4u L=0.7u

.DC V1 0 5 0.1

.PROBE

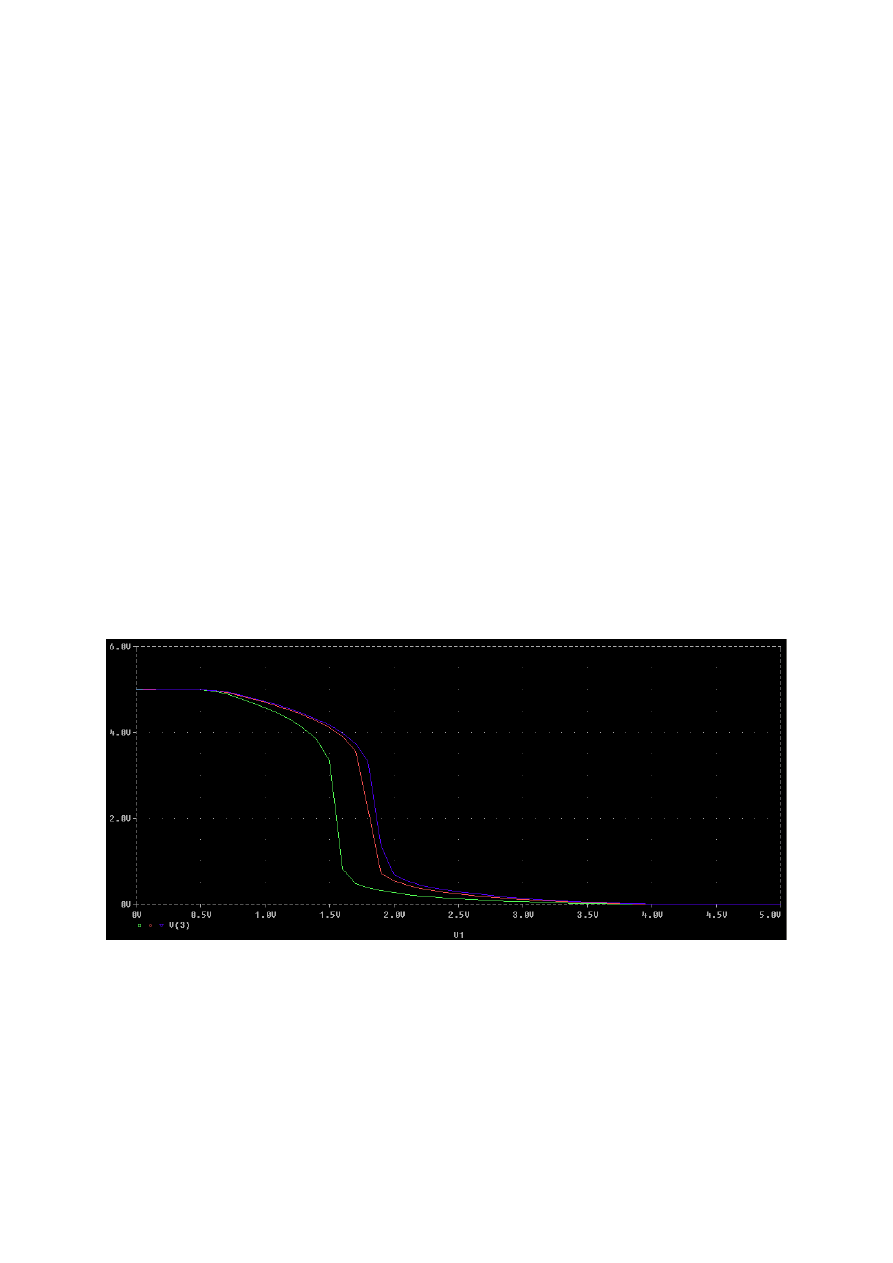

Wykres przedstawiający charakterystykę Inwertera statycznego dla trzech różnych szerokości

kanału V3(V1):

Width

= 0.24u

Width

= 0.48u

Width

= 2.4u

Inwerter dynamiczny:

*inwerter

.LIB I:\Spice\cmos7tm.mod

VDD 1 0 5

V1 2 0 PULSE(0 5 0 0.1n 0.1n 20n 40n)

M1 3 2 1 1 MODP W=2.4u L=0.7u

M2 3 2 0 0 MODN W=2.4u L=0.7u

.TRAN 1n 200n

.PROBE

.END

.LIB I:\Spice\cmos7tm.mod

VDD 1 0 5

V1 2 0 PULSE(0 5 0 0.1n 0.1n 20n 40n)

M1 3 2 1 1 MODP W=2.4u L=8u

M2 3 2 0 0 MODN W=2.4u L=8u

.TRAN 1n 200n

.PROBE

.END

.LIB I:\Spice\cmos7tm.mod

VDD 1 0 5

V1 2 0 PULSE(0 5 0 0.1n 0.1n 20n 40n)

M1 3 2 1 1 MODP W=2.4u L=15u

M2 3 2 0 0 MODN W=2.4u L=15u

.TRAN 1n 200n

.PROBE

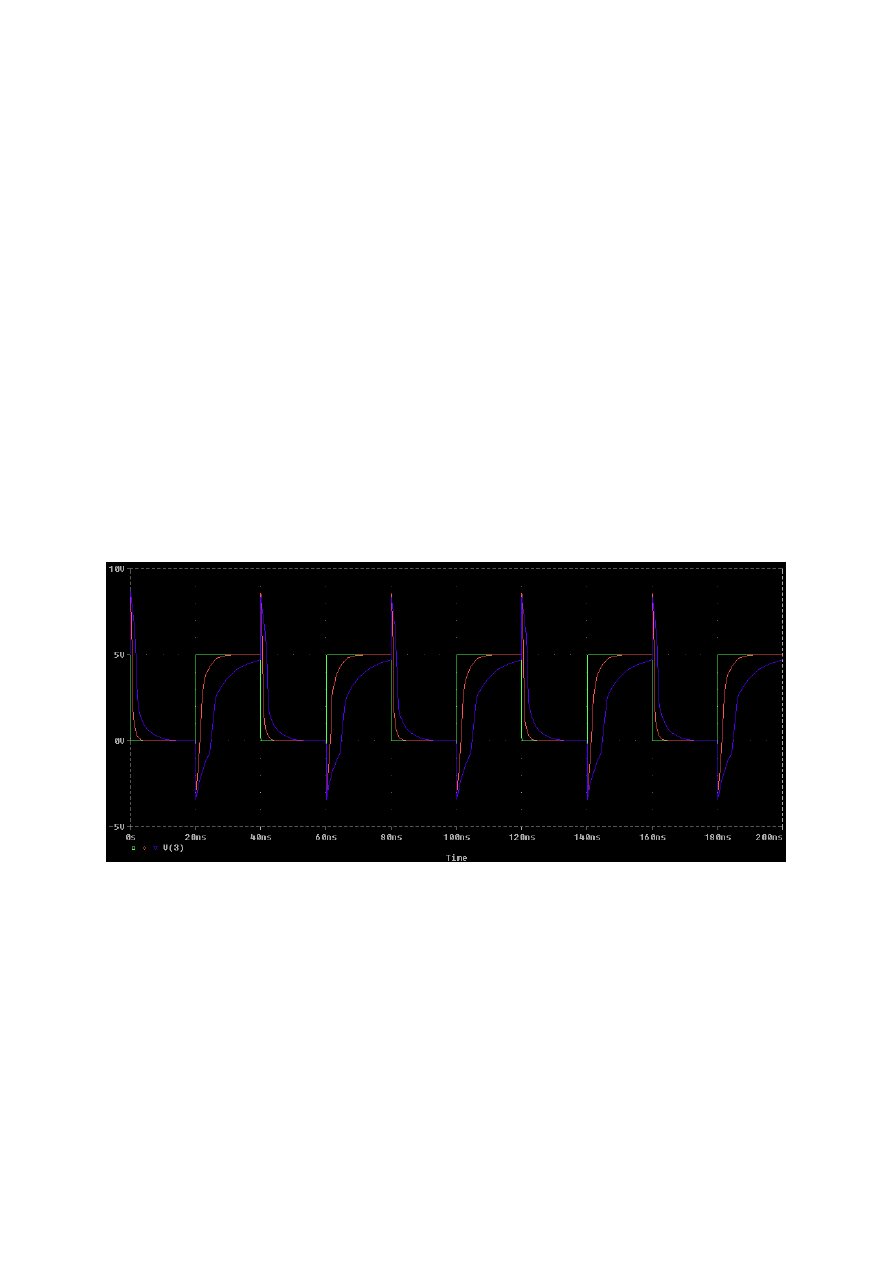

Wykres przedstawiający charakterystykę Inwertera dynamicznego dla trzech różnych parametrów

długości kanału w funkcji V3(V1):

Length

= 0.7u

Length

= 8u

Length

= 15u

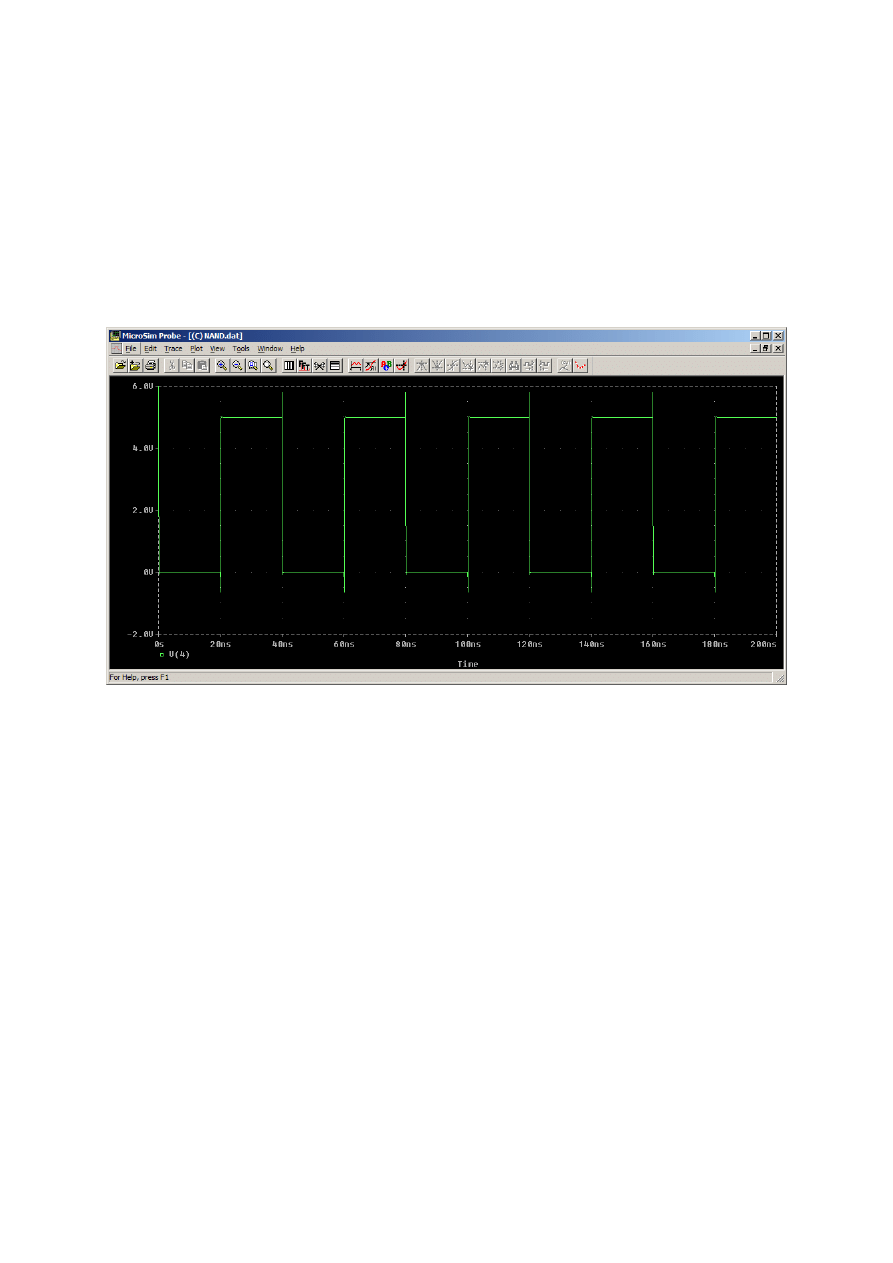

Symulacja bramki NOR (charakterystyka dynamiczna):

*BRAMKA NOR

.LIB I:\Spice\cmos7tm.mod

VDD 3 0 5

V1 1 0 PULSE(0 5 0 0.1n 0.1n 20n 40n)

V2 2 0 PULSE(0 5 0 0.1n 0.1n 20n 40n)

M1 4 2 3 3 MODP W=2.4u L=0.7u

M2 5 1 4 4 MODP W=2.4u L=0.7u

M3 0 2 5 5 MODN W=2.4u L=0.7u

M4 0 1 5 5 MODN W=2.4u L=0.7u

.TRAN 1n 200n

.PROBE

Wykres przedstawia charakterystykę dynamiczną bramki NOR:

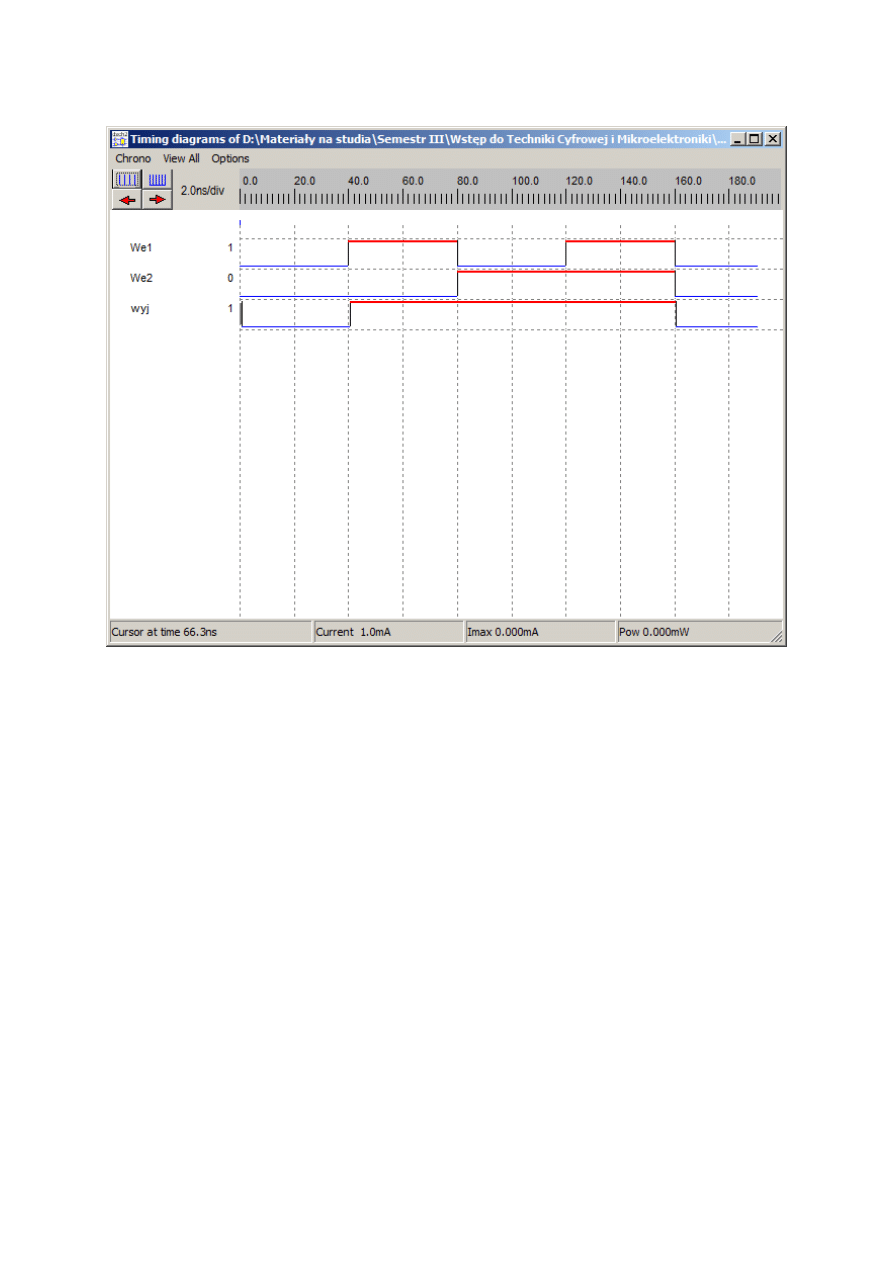

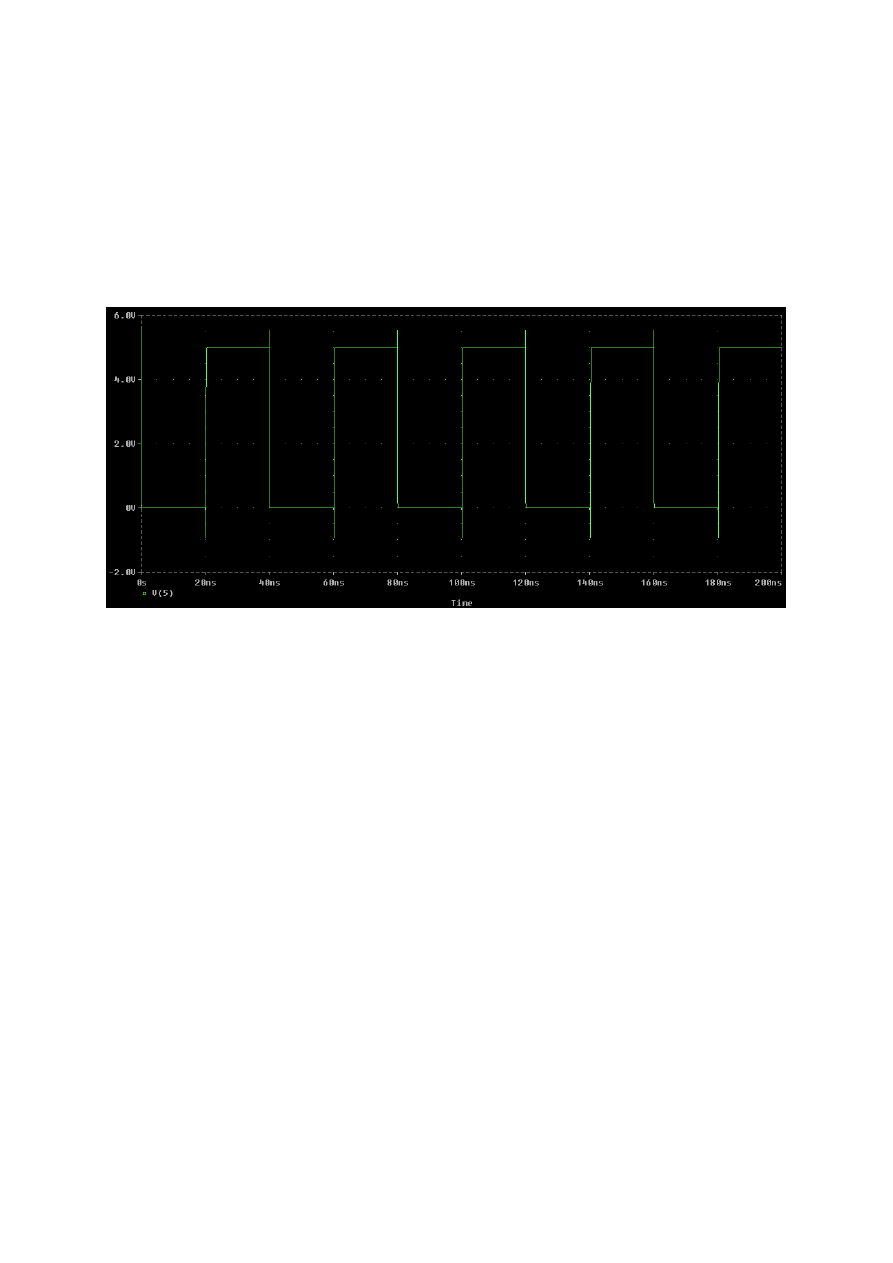

Symulacja bramki NAND (charakterystyka dynamiczna):

*BRAMKA NAND

.LIB I:\Spice\cmos7tm.mod

VDD 3 0 5

V1 1 0 PULSE(0 5 0 0.1n 0.1n 20n 40n)

V2 2 0 PULSE(0 5 0 0.1n 0.1n 20n 40n)

M1 4 1 3 3 MODP W=2.4u L=0.7u

M2 4 2 3 3 MODP W=2.4u L=0.7u

M3 5 1 4 4 MODN W=2.4u L=0.7u

M4 0 2 5 5 MODN W=2.4u L=0.7u

.TRAN 1n 200n

.PROBE

Wykres przedstawia charakterystykę dynamiczną bramki NAND:

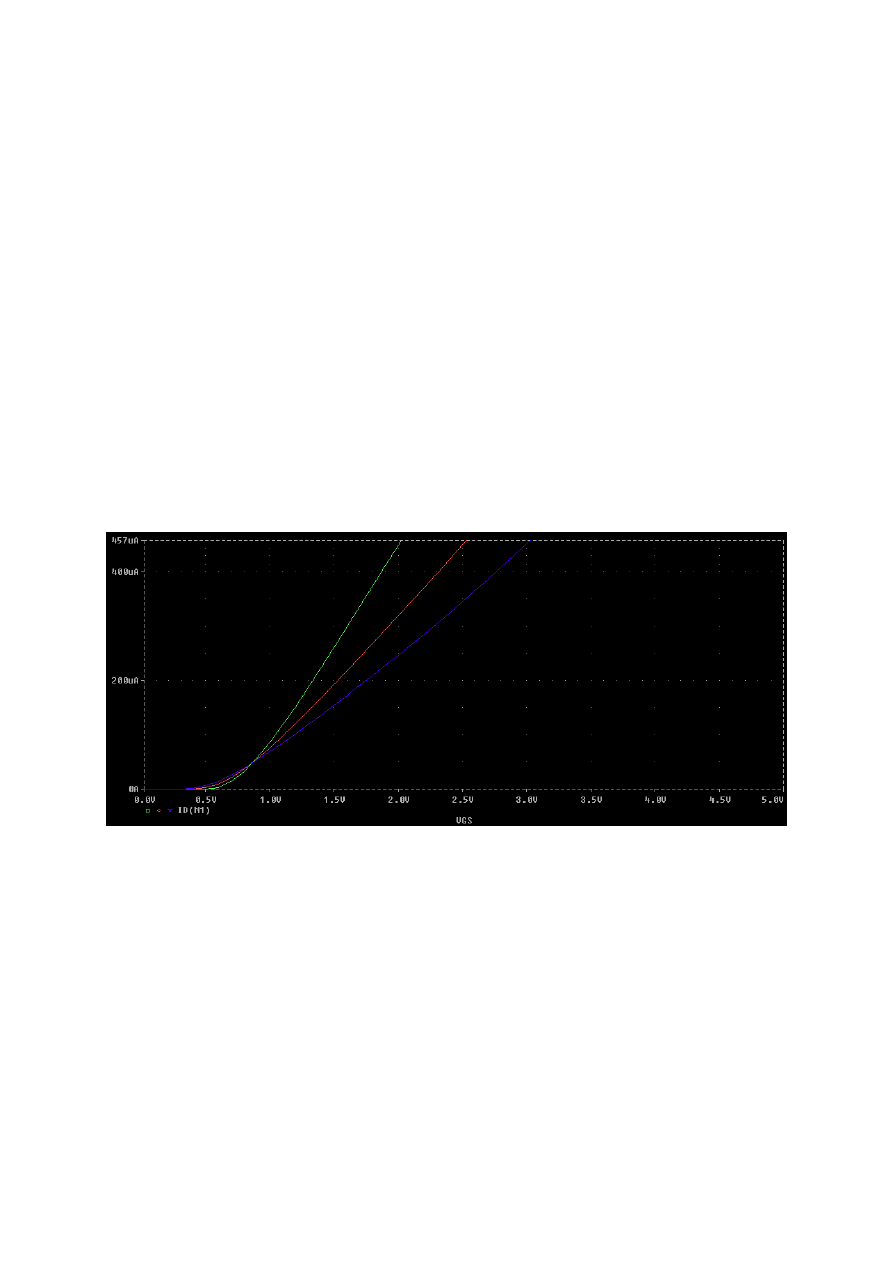

Charakterystyka wyjściowa NMOS:

*Symulacja N-MOS (wyj)

.LIB I:\Spice\cmos7tm.mod

VGS 2 0 DC 5

VDS 1 0 DC 5

M1 1 2 0 0 MODN W=2.4u L=0.7u

.TEMP 0

.DC VGS 0 5 0.1

.PROBE

.END

.LIB I:\Spice\cmos7tm.mod

VGS 2 0 DC 5

VDS 1 0 DC 5

M1 1 2 0 0 MODN W=2.4u L=0.7u

.TEMP 100

.DC VGS 0 5 0.1

.PROBE

.END

.LIB I:\Spice\cmos7tm.mod

VGS 2 0 DC 5

VDS 1 0 DC 5

M1 1 2 0 0 MODN W=2.4u L=0.7u

.TEMP 200

.DC VGS 0 5 0.1

.PROBE

Wykres Id(V

gs

) dla różnych temperatur:

Temp

= 0’C

Temp

= 100’C

Temp

= 200’C

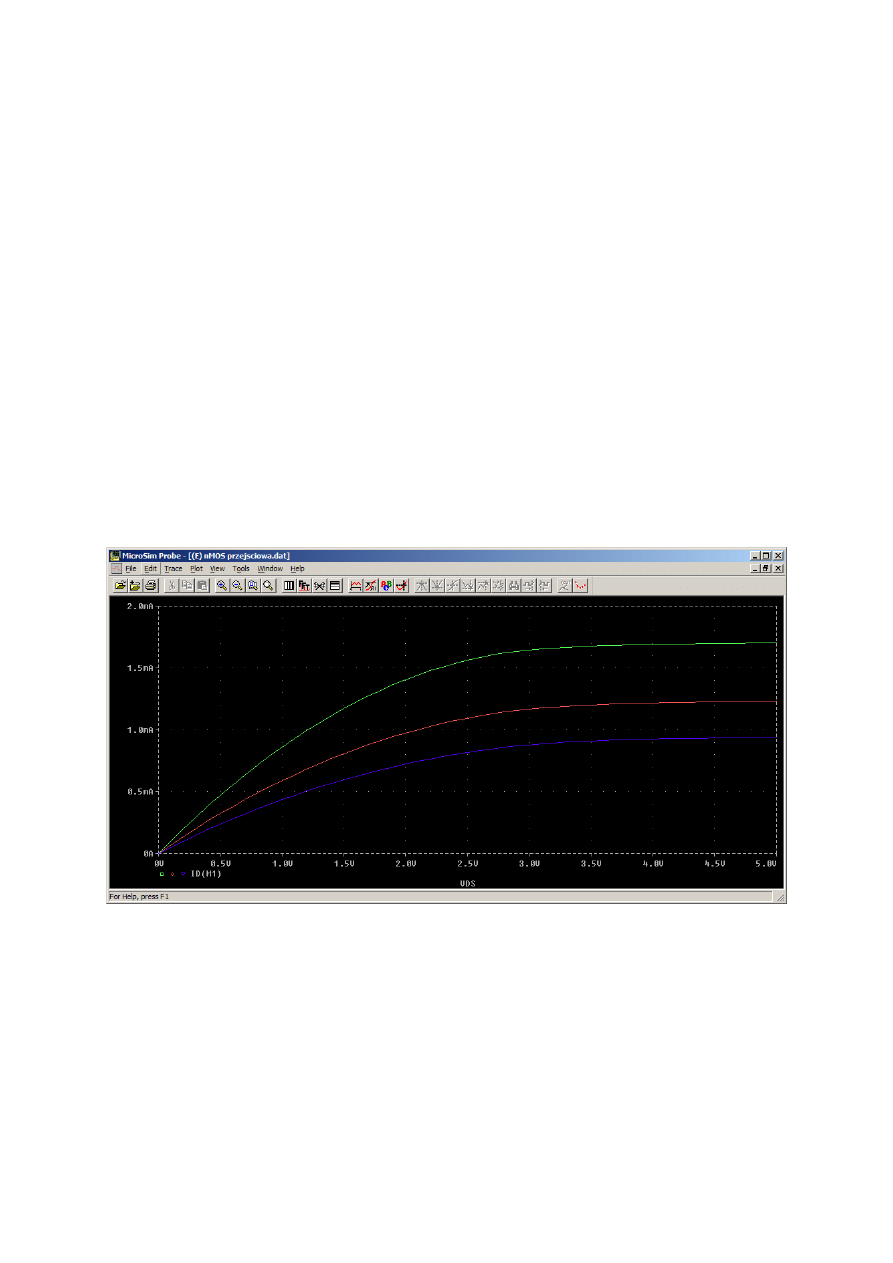

Charakterystyka wyjściowa NMOS:

*Symulacja n-MOS przej.

.LIB I:\Spice\cmos7tm.mod

VGS 2 0 DC 5

VDS 1 0 DC 5

M1 1 2 0 0 MODN W=2.4u L=0.7u

.temp 0

.DC VDS 0 5 0.1

.PROBE

.END

.LIB I:\Spice\cmos7tm.mod

VGS 2 0 DC 5

VDS 1 0 DC 5

M1 1 2 0 0 MODN W=2.4u L=0.7u

.temp 100

.DC VDS 0 5 0.1

.PROBE

.END

.LIB I:\Spice\cmos7tm.mod

VGS 2 0 DC 5

VDS 1 0 DC 5

M1 1 2 0 0 MODN W=2.4u L=0.7u

.temp 200

.DC VDS 0 5 0.1

.PROBE

Wykres Id(V

ds

) dla różnych temperatur:

Temp

= 0’C

Temp

= 100’C

Temp

= 200’C

Program Microwind:

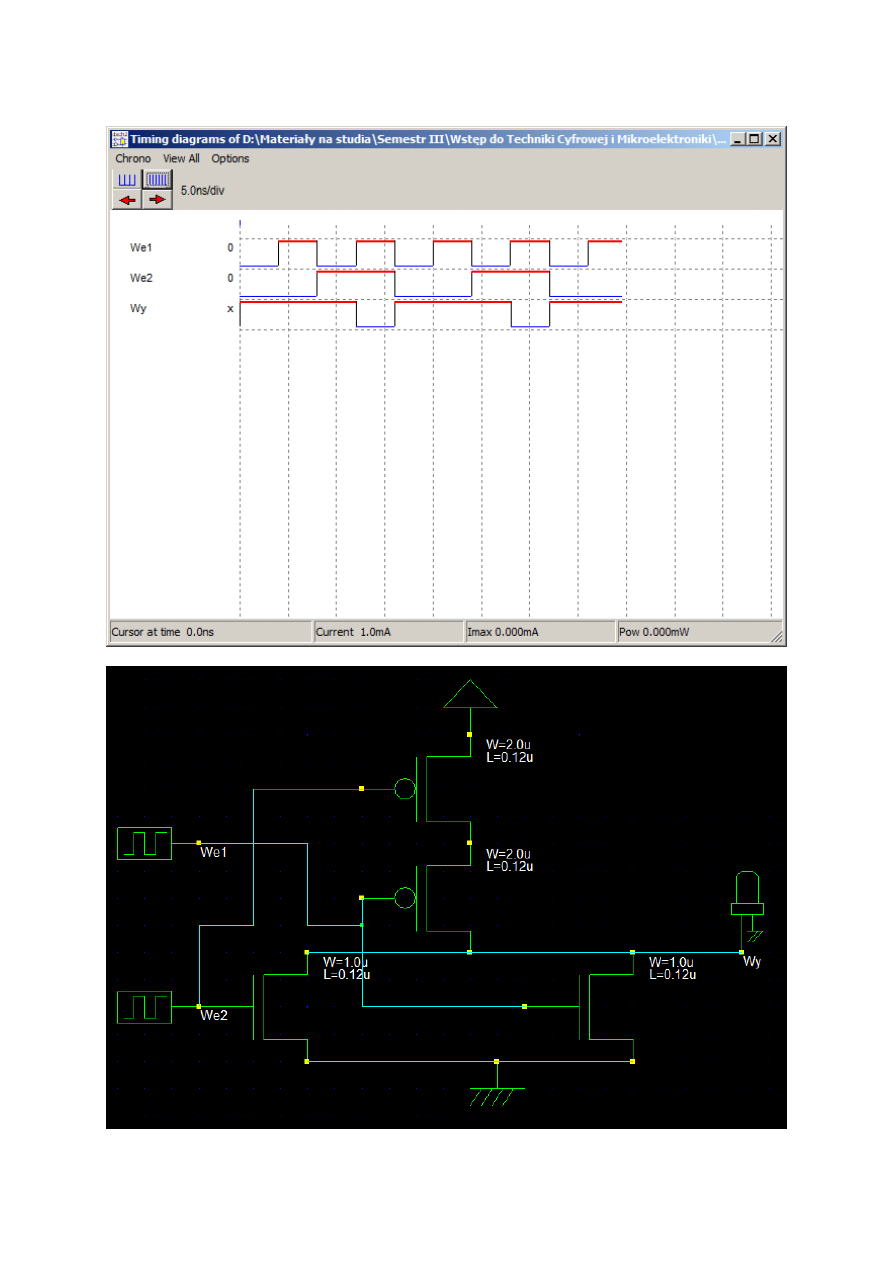

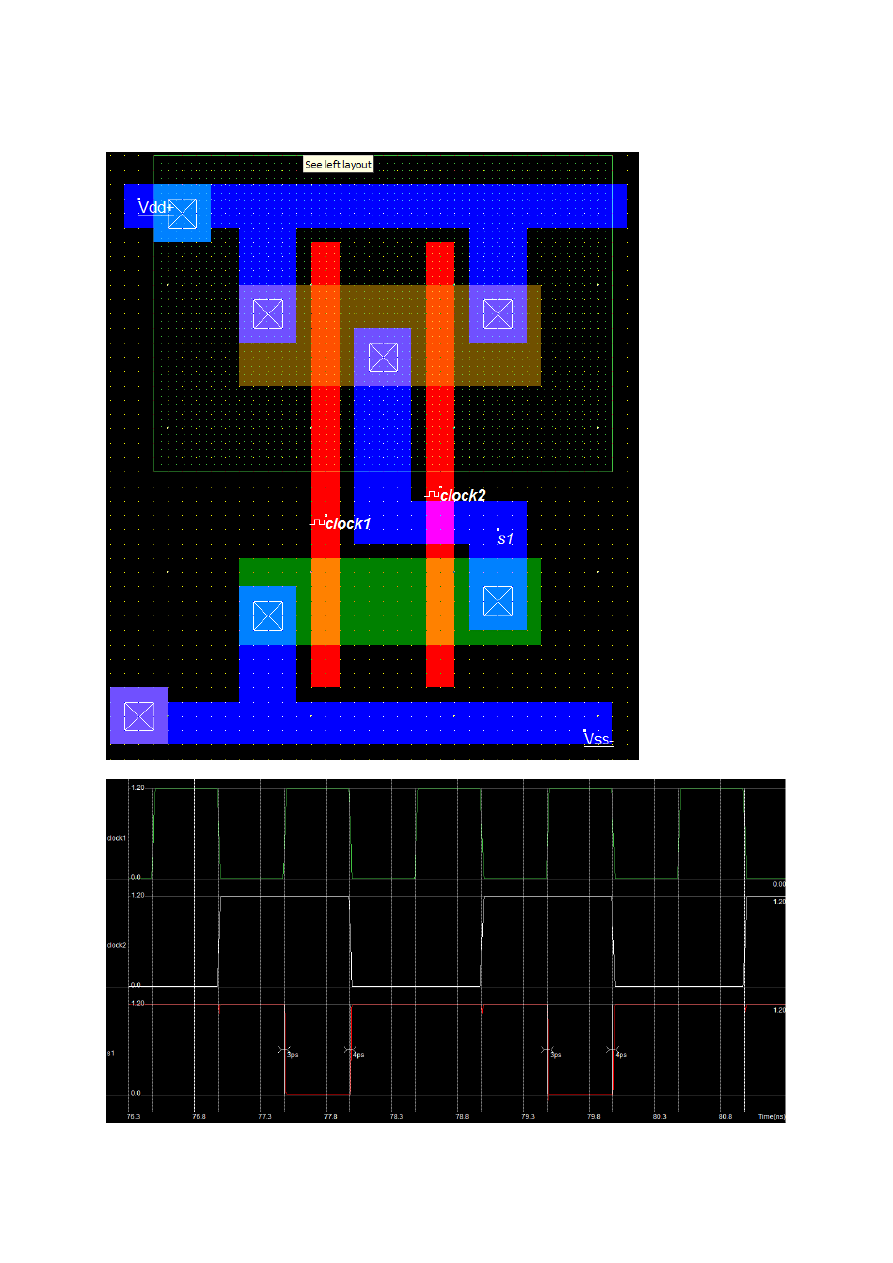

Topologia bramki NAND:

Przebieg dla bramki NAND:

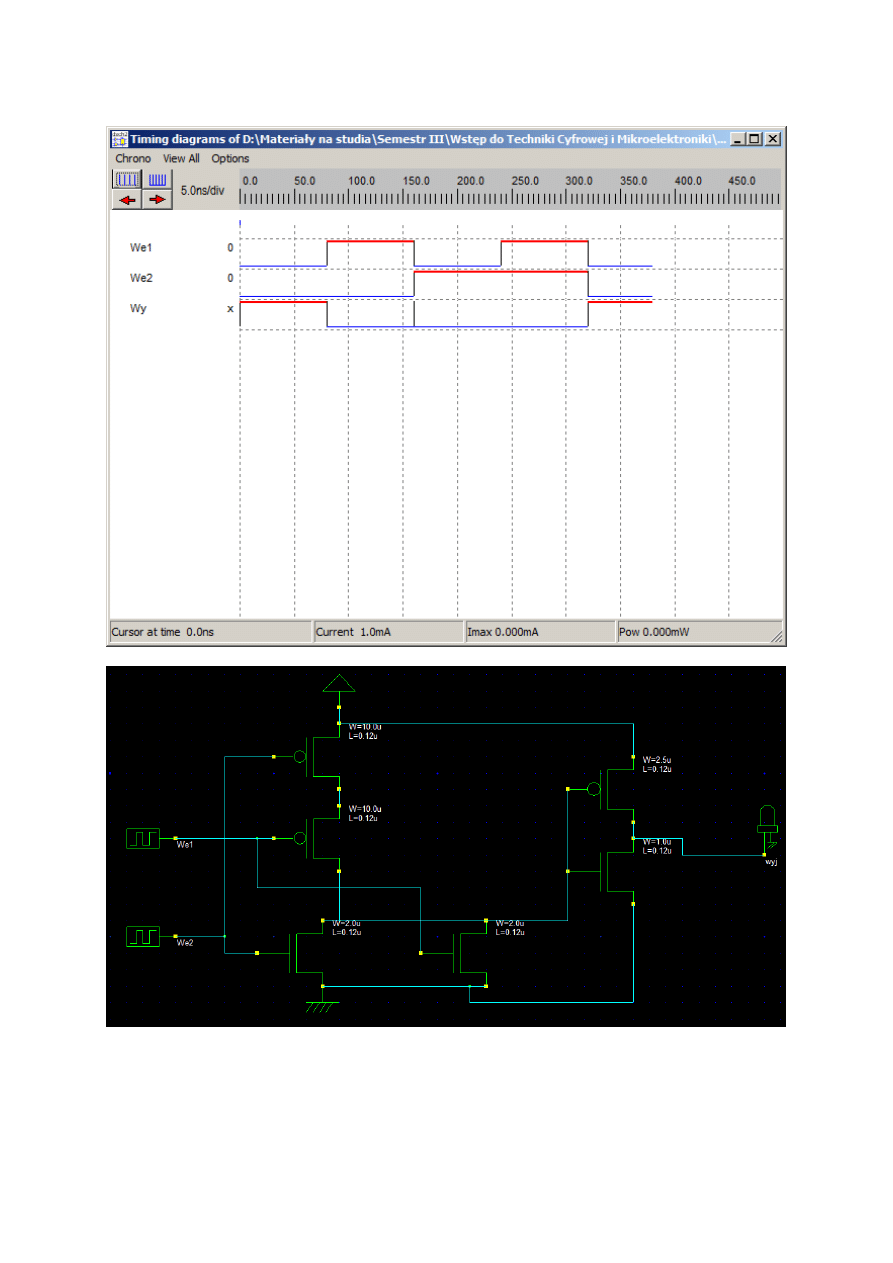

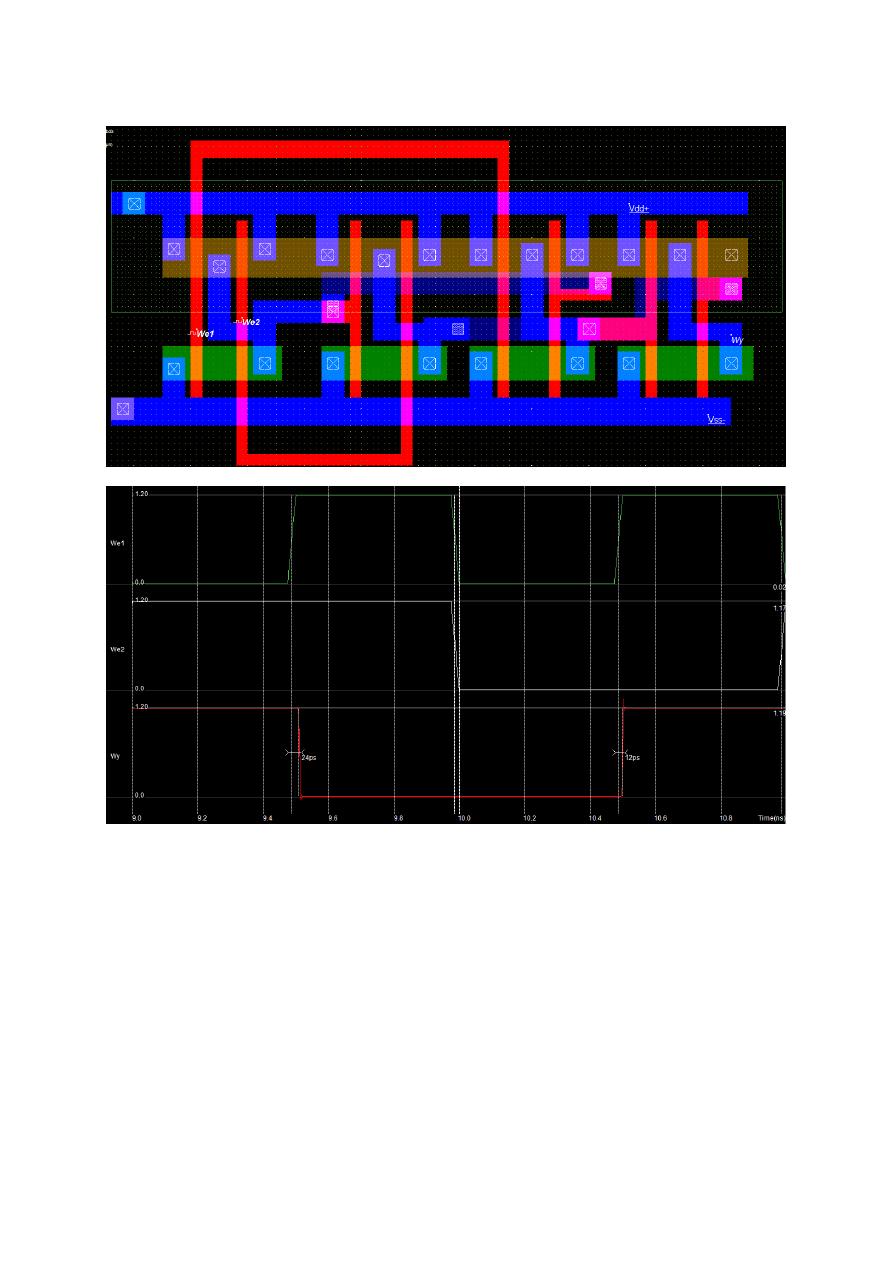

Topologia bramki NOR:

Przebieg czasowy dla bramki NOR:

Wyszukiwarka

Podobne podstrony:

więcej podobnych podstron