85

Elektronika Praktyczna 7/2002

K U R S

ì P r z e k o p y w a n i e î s i Í

przez dostÍpn¹ dokumenta-

cjÍ i†wybranie najwaøniej-

szych zagadnieÒ zajͳo mi

wiele dni. Niewiele przydat-

n y c h i n f o r m a c j i m o ø n a

znaleüÊ w†Internecie. Ta

niekorzystna dla konstrukto-

rÛw sytuacja sk³oni³a mnie

do napisania tego artyku³u.

Jest dla mnie pretekstem do

usystematyzowania wczeúniej

zdobytej wiedzy, niezbÍdnej do samo-

dzielnego przygotowania programu dla

mikrokontrolera steruj¹cego napÍdami

CD-ROM lub HDD. Mam nadziejÍ, øe

artyku³ bÍdzie pomocny wielu z†Was

podczas projektowaniu uk³adÛw tego

rodzaju.

Sygna³y steruj¹ce w†IDE

Schemat blokowy ilustruj¹cy budo-

wÍ typowego dysku twardego przedsta-

wiono na rys. 1. DziÍki temu, øe

w†napÍdzie zintegrowano zaawansowane

funkcjonalnie uk³ady steruj¹ce odczytem

i†zapisem danych, uøytkownik ma do

nich dostÍp poprzez stosun-

kowo ³atwy w†obs³udze 16-

bitowy interfejs IDE. W†zaleø-

noúci od aplikacji (kompute-

ry stacjonarne, przenoúne)

i†rozmiaru dysku twardego

(2,5î/3,5î) lub CD-ROM-u

wyrÛøniamy dwa rodzaje z³¹-

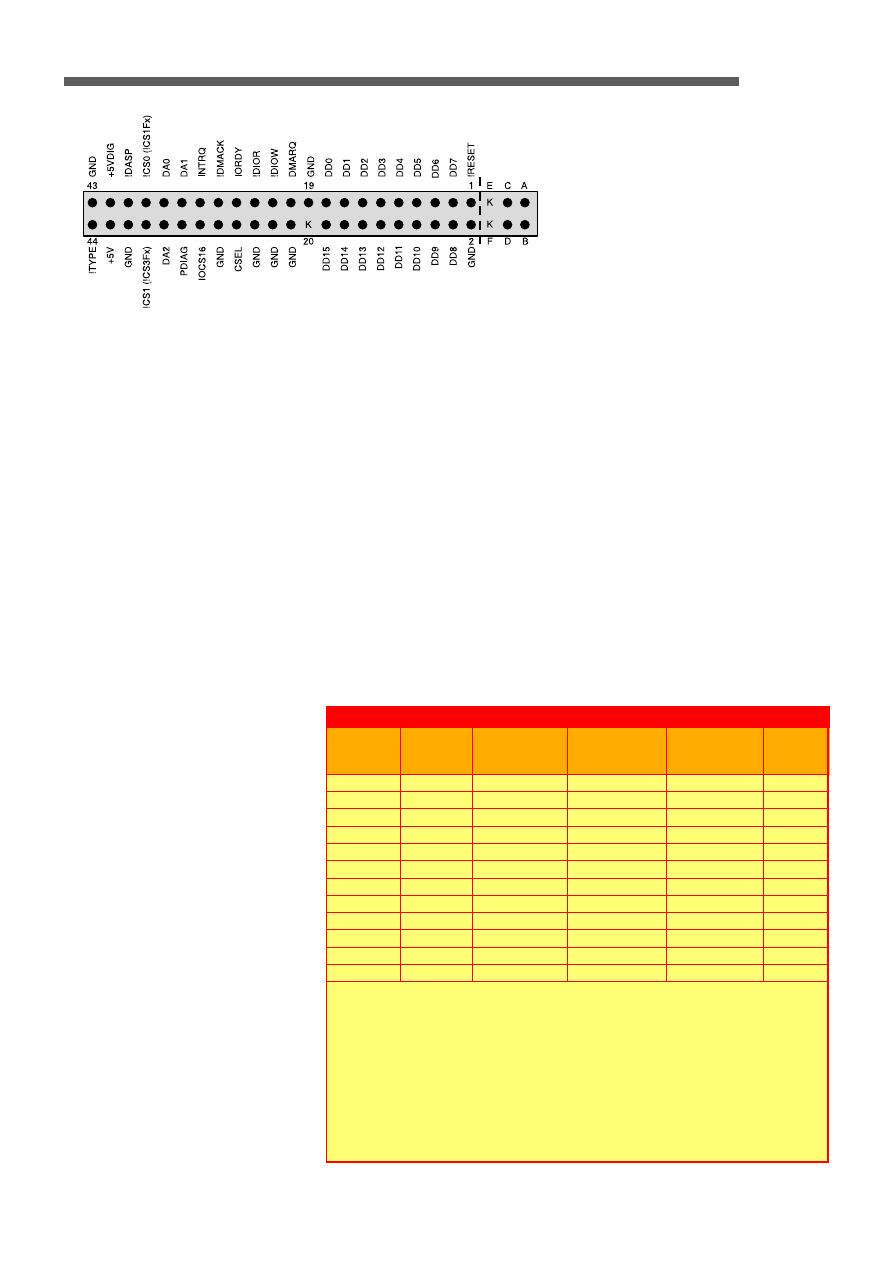

czy IDE (rys. 2):

- 40-pinowe o†rastrze 2,5mm,

- 44-pinowe o†rastrze 2,0 mm

(na pinach od 41 do 44 s¹

dodatkowe linie zasilania, sposÛb ich

pod³¹czenia zaleøy od typu dysku).

Maksymalna d³ugoúÊ kabla ³¹cz¹ce-

go kontroler z†napÍdem moøe wynosiÊ

46 cm.

Funkcje sygna³Ûw w†IDE

- CS0 - Chip Select 0†- s³uøy do wy-

boru rejestrÛw Command Block Re-

gisters.

- CS1 - Chip Select 1†- s³uøy do wy-

boru rejestrÛw Control Block Regis-

ters.

- DA1/2/3 - linie adresowe s³uø¹ do

wyboru jednego z rejestrÛw z†grupy

Command lub Control Block Registers

- moøliwy jest wiÍc dostÍp do 16

rejestrÛw (osiem z†grupy Control

i†osiem z†grupy Command).

- DASP - wyjúcie typu OC, do³¹czane

zazwyczaj do VCC poprzez rezystor

10k

Ω

(nie jest konieczny). Sygnalizu-

je aktywnoúÊ urz¹dzenia IDE, lub

obecnoúÊ urz¹dzenia pierwszego w†ka-

nale IDE. Moøna pod³¹czyÊ diodÍ

LED.

- DD0...15 - dwukierunkowa szyna da-

nych 8- lub 16-bitowa. Do wpisywa-

nia danych 8-bitowych wykorzystywa-

na jest mniej znacz¹ca czÍúÊ (tylko

do wpisywania danych do rejestrÛw).

Transmisja ìzwyk³ychî danych odby-

wa siÍ tylko w†trybie 16-bitowym.

- DIOR (Device I/O Read) - opadaj¹ce

zbocze sygna³u na tej linii powoduje

wyprowadzenie danych przez urz¹dze-

Od d³uøszego czasu obserwujÍ rosn¹ce zainteresowanie elektronikÛw wykorzystaniem napÍdÛw

CD i†dyskÛw twardych we w³asnych projektach. NajczÍúciej s¹ to pomys³y zbudowania

w³asnego odtwarzacza p³yt CD audio lub wykorzystanie dysku twardego jako noúnika dla

plikÛw MP3. Niestety, aby tego dokonaÊ, trzeba przebrn¹Ê przez obszern¹†dokumentacjÍ

standardu ATAPI oraz interfejsu IDE.

Sterowanie CD−ROM−ów i dysków

twardych w praktyce, część 1

IDE (Integrated Disc Electronics) oznacza

prosty interfejs umożliwiający dołączenie dysku

twardego do magistrali ISA komputera PC.

ATA (AT − Attachment) jest synonimem IDE,

obecnie powszechnie stosowanym przez

producentów dysków twardych.

Standard ATA opisuje sposób wymiany danych

pomiędzy sterownikiem i napędem.

K U R S

Elektronika Praktyczna 7/2002

86

nie IDE na magistralÍ DD0...15.

Natomiast narastaj¹ce zbocze na linii

powoduje akceptacjÍ danych po stro-

nie hosta. Host nie powinien reago-

waÊ na dane wystÍpuj¹ce na magist-

rali pomiÍdzy zboczami tego sygna³u.

- DIOW - (Device I/O Write) - narasta-

j¹ce zbocze tego sygna³u powoduje

zatrzaúniÍcie danych w†urz¹dzeniu.

DopÛki dane nie zostan¹†zatrzaúniÍte

sterownik napÍdu nie przywi¹zuje do

nich øadnej wagi.

- DMACK (DMA Acknowledge) - jest

sygna³em wykorzystywanym przy

transmisji danych z†udzia³em DMA.

Jest pozytywn¹ odpowiedzi¹ (potwier-

dzeniem) ze strony hosta na ø¹danie

DMARQ ze strony CD-ROM-u lub

HDD.

- DMARQ (DMA Request) - sygna³ jest

ustawiany przez CD-ROM lub HDD,

gdy jest gotowy do transmisji danych

w†trybie DMA. W†trybie DMA øaden

z†sygna³Ûw CS0/1/2 nie powinien byÊ

ustawiony. Dane s¹ transmitowane

z†wykorzystaniem ca³ej szerokoúci ma-

gistrali DD0...15 (w trybie 16-bito-

wym). Kierunek transmisji danych

jest ustalany za pomoc¹ sygna³Ûw

DIOR, DIOW.

- INTRQ (Interrupt Request) - zg³osze-

nie ø¹dania obs³ugi przerwania. Syg-

na³ ten jest ustawiony, gdy urz¹dze-

nie jest wybrane i†gdy uk³ad steruj¹-

cy (host) skasowa³ bit nIEN w†rejes-

trze Device Control. Oczywiúcie, do-

³¹czony napÍd musi ø¹daÊ obs³ugi

przerwania. عdanie przerwania na-

stÍpuje w†wyniku zakoÒczenia wyko-

nywania komendy i†gotowoúci do

transmisji danych w†trybie PIO (z

wyj¹tkiem pierwszego bloku). Wy-

czyúciÊ ø¹danie przerwania moøna za

pomoc¹ ustawienia (na ì1î) linii RE-

SET, ustawienia bitu SRST w†rejest-

rze Device Control, zapisanie do re-

jestru Command przez hosta lub od-

czytanie rejestru Status przez hosta.

- IORDY - sygnalizuje brak gotowoúci

urz¹dzenia do przes³ania danych do/

z rejestrÛw urz¹dzenia. Obs³uga tego

sygna³u jest wymagana w†trybie pra-

cy PIO3.

- PDIAG - wyjúcie typu OC, ktÛre na-

leøy ìpodpi¹Êî do +5V poprzez re-

zystor 10 k

Ω

. Sygna³ na wyjúciu syg-

nalizuje zakoÒczenie autodiagnostyki.

- RESET - stan niski zeruje sterownik

napÍdu.

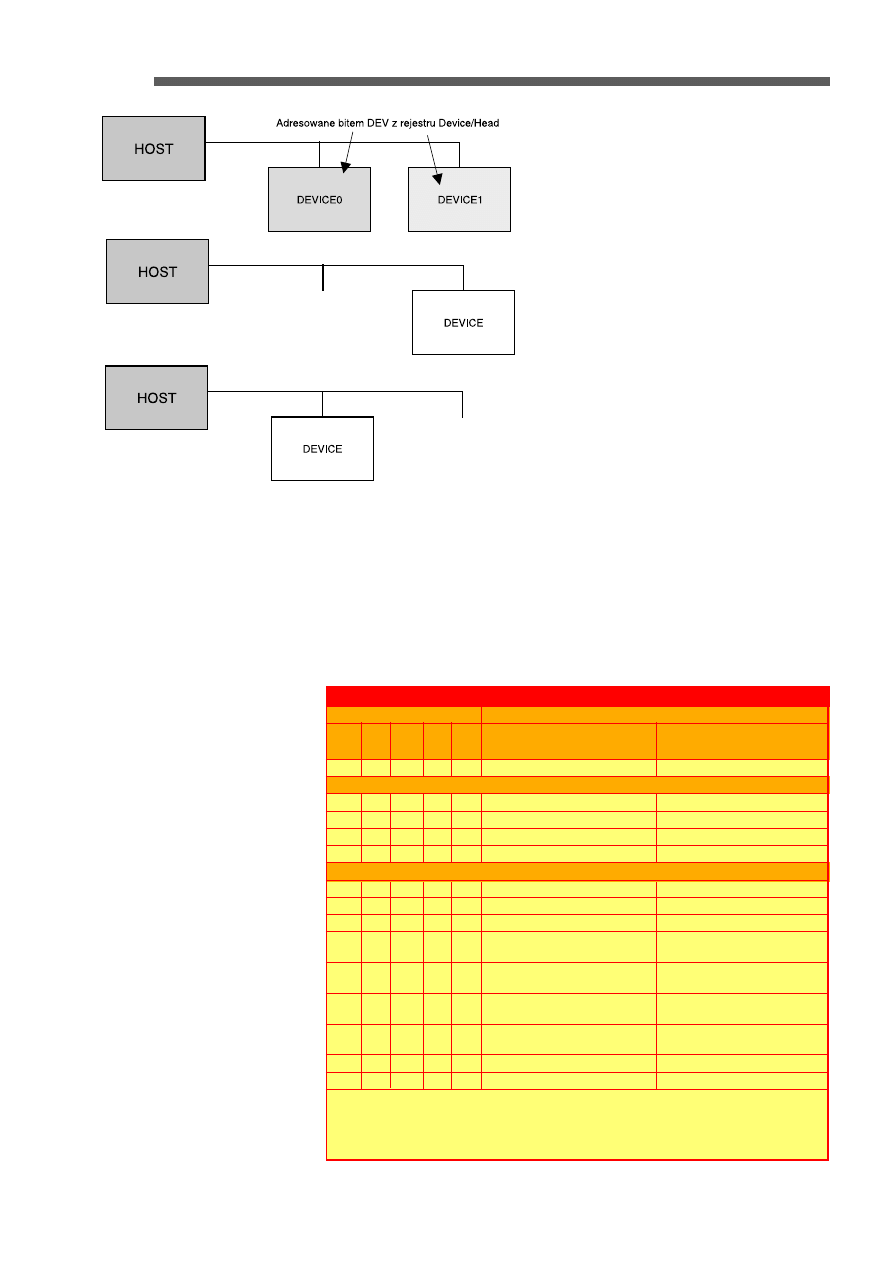

Adresowanie urz¹dzeÒ IDE

(Master/Slave)

Gdy do jednego kabla IDE s¹ do-

³¹czone dwa urz¹dzenia (np. dysk

twardy i†CD-ROM - rys. 3), to wpisy-

wanie danej do dowolnego rejestru

powoduje jednoczesne zapisanie rejes-

trÛw w†obydwu urz¹dzeniach. Wynika

to z†faktu, øe w†IDE nie wystÍpuj¹

specjalne linie adresowe do wyboru

jednego z†urz¹dzeÒ Master/Slave, do

lub z†ktÛrego chcemy odczytaÊ lub

wpisaÊ dane. Adresowanie odbywa siÍ

poprzez ustawienie lub wyzerowanie

bitu DEV w†rejestrze Device/Head.

Gdy DEV=0, komunikacja odbywa siÍ

z†Masterem, a†gdy DEV=1 to ze Sla-

vem.

Rejestry

Rejestry naleø¹ce do tzw. bloku

rejestrÛw poleceÒ (Command Registers)

s³uø¹ do wysy³ania komend dla ste-

rownika urz¹dzenia i†odczytywania

statusu urz¹dzenia. Rejestry naleø¹ce

do tzw. bloku rejestrÛw sterowania

(Control Registers) s³uø¹ do kontroli

parametrÛw urz¹dzenia, oraz do od-

czytywania alternatywnego statusu.

SposÛb adresowania rejestrÛw pokaza-

no w†tab. 4.

Rejestr Alternate Status

Adres 6hCS 1h

7

6

5

4

3

2

1

0

BSY

DRDY DF

DSC

DRQ

CORR

IDXERR

DostÍp - tylko odczyt.

Uwaga: gdy BSY = 0, moøna od-

czytywaÊ resztÍ bitÛw.

Uwagi dodatkowe: odczyt rejestru

nie powoduje skasowania przerwania

od urz¹dzenia IDE ani nie potwierdza

przyjÍcia przerwania.

Znaczenie poszczegÛlnych bitÛw -

takie samo jak dla rejestru Statusu.

Rejestr Command

Adres 7hCS 2h

7

6

5

4

3

2

1

0

DostÍp - tylko do zapisu. Gdy host

prÛbuje odczytaÊ rejestr, odczytywany

jest rejestr Statusu.

Uwaga: gdy BSY = 0, DRQ = 0

i†DMACK nie jest ustawiony, moøna za-

pisywaÊ do tego rejestru.

Uwagi dodatkowe: zapis do rejestru

powoduje skasowanie przerwania od

urz¹dzenia IDE.

Znaczenie poszczegÛlnych bitÛw -

brak.

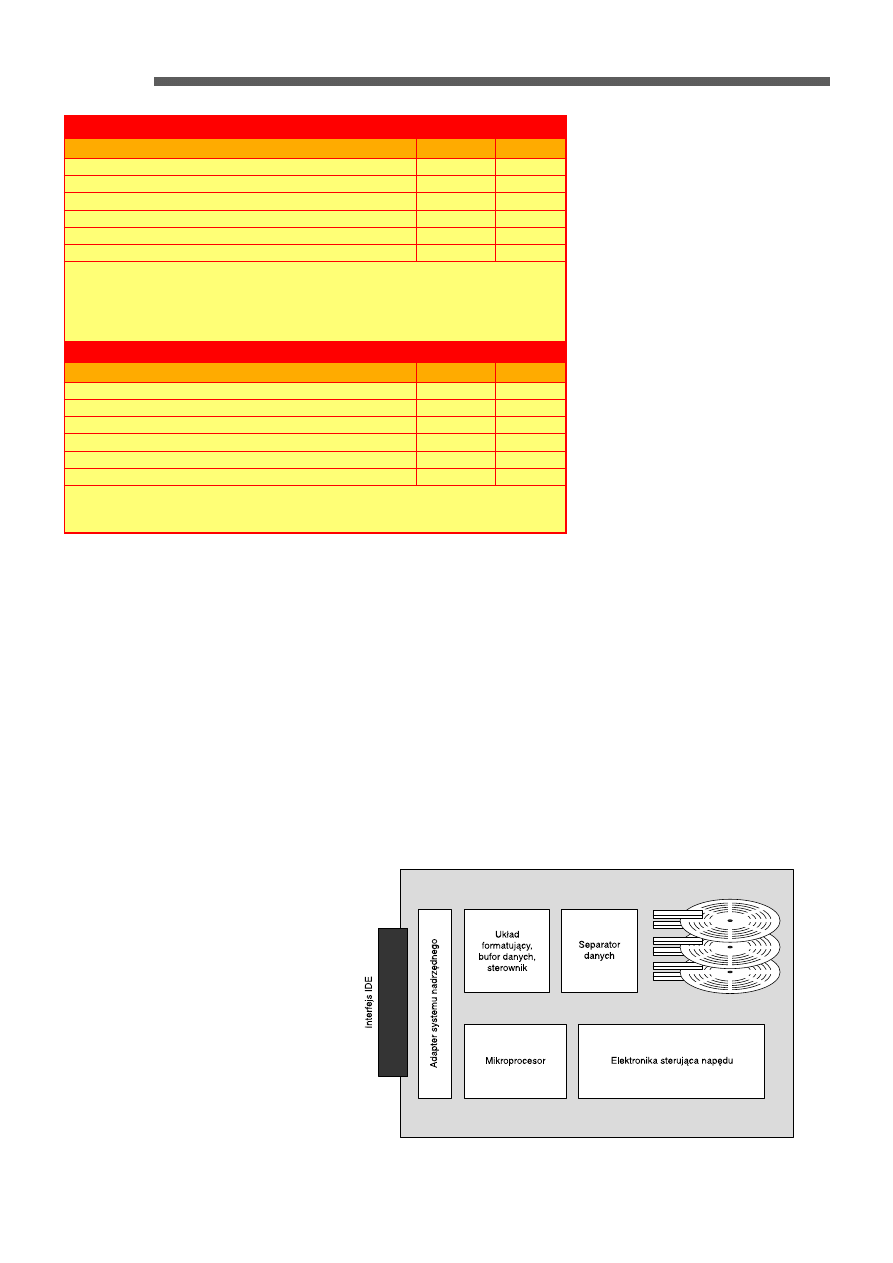

Tab. 1. Parametry statyczne IDE

Opis

Min

Max

I

oL

Prąd przyjmowany przez bufor wyjściowy (1)

4 mA

I

oH

Prąd oddawany przez bufor wyjściowy

400

µ

A

V

iH

Poziom napięcia traktowany jako stan wysoki

2,0 V

V

iL

Poziom napięcia traktowany jako stan niski

0,8 V

V

oH

Napięcie wyjściowe w stanie wysokim (I

oH

= −400

µ

A)

2,4 V

V

oL

Napięcie wyjściowe w stanie niskim (I

oL

= 12 mA)

0,5 V

Uwagi:

1. Prąd I

oL

dla DASP powinien wynosić min. 12 mA, aby zapewnić wymagane czasy narastania i opa−

dania zboczy.

2. Prąd I

oH

o wartości 400

µ

A jest niewystarczający w przypadku, gdy DMARQ jest typowo podłączo−

ny do masy przez rezystor 5,6 k

Ω

.

Tab. 2. Parametry dynamiczne IDE

Opis

Min

Max

t

rise

Czasy narastania zboczy sygnałów na złączu IDE (1)

5 ns

t

fall

Czasy opadania zboczy sygnałów na złączu IDE (1)

5 ns

C

in

Pojemność wejść urządzenia sterującego (HOSTa)

25 pF

C

out

Pojemność wyjść urządzenia sterującego (HOSTa)

25 pF

C

in

Pojemność obwodów wejściowych

20 pF

C

out

Pojemność obwodów wyjściowych

20 pF

Uwagi:

1. t

rise

i t

fall

są mierzone pomiędzy 10...90% pełnej amplitudy sygnału przy sumarycznym obciążeniu

pojemnościowym 40 pF.

Rys. 1. Budowa typowego dysku twardego

87

Elektronika Praktyczna 7/2002

K U R S

Rejestr Cylinder High

Adres 5hCS 2h

7

6

5

4

3

2

1

0

CHS(Cylinder(15:8)) LBA(Cylinder(23:16))

DostÍp - zapis/odczyt.

Uwaga: gdy BSY = 0, DRQ = 0

i†DMACK nie jest ustawiony, moøna za-

pisywaÊ do tego rejestru.

Uwagi dodatkowe: zapis do rejestru

powoduje skasowanie przerwania od

urz¹dzenia IDE.

Jeøeli w†rejestrze Device/Head bit

LBA = 0 (CD-ROM, HDD pracuje wte-

dy w†trybie CHS - Cylinder, Head, Sec-

tor), to w†tym rejestrze znajduje siÍ

startowy, starszy bajt adresu cylindra -

podawany jest przy dostÍpie do da-

nych. Jeøeli w†rejestrze Device/Head bit

LBA = 1 (CD-ROM, HDD pracuje w†try-

bie LBA - Logical Block Address, dane

adresowane s¹ w†sposÛb liniowy),

w†tym rejestrze znajduj¹ siÍ bity 23...16

adresu LBA.

Rejestr Cylinder Low

Adres 4hCS 2h

7

6

5

4

3

2

1

0

CHS(Cylinder(7:0)) LBA(Cylinder(15:8))

DostÍp - zapis/odczyt.

Uwaga: gdy BSY = 0, DRQ = 0

i†DMACK nie jest ustawiony, moøna

zapisywaÊ/odczytywaÊ do/z tego rejest-

ru.

Uwagi dodatkowe: zapis rejestru po-

woduje skasowanie przerwania od urz¹-

dzenia IDE.

Jeøeli w†rejestrze Device/Head bit

LBA = 0†(CD-ROM, HDD pracuje wtedy

w†trybie CHS - Cylinder, Head, Sector),

to w†tym rejestrze znajduje siÍ starto-

wy, m³odszy bajt adresu cylindra - po-

dawany jest przy dostÍpie do danych.

Jeøeli w†rejestrze Device/Head bit LBA

= 1 (CD-ROM, HDD pracuje w†trybie

LBA - Logical Block Address, dane s¹

adresowane liniowo), w†tym rejestrze

znajduj¹ siÍ bity 15...8 adresu LBA.

Rejestr Danych

Adres 4hCS 0h

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Data (15:0)

DostÍp - do zapisu i†do odczytu

Uwaga: gdy BSY = 0, DRQ = 0

i†DMACK nie jest ustawiony, moøna

zapisywaÊ/odczytywaÊ do/z tego rejest-

ru.

Uwagi dodatkowe: zawartoúÊ rejest-

ru nie jest waøna, gdy urz¹dzenie jest

w†trybie Sleep Mode. Rejestr jest 16-

bitowy.

Port Danych

Adres brak

CS brak

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Data(15:0)

DostÍp - zapis/odczyt.

Uwaga: zapis i†odczyt tego portu

powinien odbywaÊ siÍ przy ustawionej

linii DMACK.

Uwagi dodatkowe: rejestr 16-bitowy.

Rejestr Device Control

Adres 6hCS 1h

7

6

5

4

3

2

1

0

r

r

r

r

r

SRST

nIEN

0

DostÍp - rejestr tylko do zapisu,

w†przypadku odczytu zwracana jest za-

wartoúÊ rejestru Alternate Status.

Uwaga: zapis powinien odbywaÊ

siÍ, gdy DMACK nie jest ustawio-

ny.

Uwagi dodatkowe: SRST jest bitem,

ktÛrego ustawienie powoduje programo-

we zerowanie urz¹dzenia. Bit nIEN

jest odpowiedzialny za w³¹czenie syg-

nalizacji obs³ugi przerwania przez

hosta.

Rejestr Device/Head

Adres 6hCS 2h

7

6

5

4

3

2

1

0

Tryb CHS

1

LBA

1

DEV

HS3

HS2

HS1

HS0

Tryb LBA

1

LBA

1

DEV

LBA(27:24)

DostÍp - zapis/odczyt.

Uwaga: rejestr moøe byÊ zapisywa-

ny tylko, gdy BSY = 0, DRQ = 0

i†DMACK nie jest ustawiony.

Uwagi dodatkowe: DEV jest bitem

odpowiedzialnym za adres urz¹dzenia.

Gdy DEV=0 wybrane jest urz¹dzenie

Master, gdy DEV=1 wybrane jest urz¹-

dzenie Slave.

Gdy bit LBA=0 wybrany jest tryb

adresowania CHS, w†przeciwnym wy-

padku adresowanie odbywa siÍ za po-

moc¹ LBA.

Bit 5†powinien byÊ ustawiony ì1î -

kompatybilnoúÊ.

Rejestr Error

Adres 1h

CS 2h

7

6

5

4

3

2

1

0

r

UNC

MC

IDNF

MCR

ABRT

TK0NF AMNF

DostÍp - rejestr tylko do odczytu,

zapisywanie powoduje zapis do rejest-

ru Features.

Znaczenie poszczegÛlnych bitÛw:

- UNC (Uncorrectable Data Error) -

b³¹d niemoøliwy do skorygowania;

- MC (Media Change) - nowy noúnik

jest dostÍpny w†napÍdzie;

- IDNF (ID not found) - ø¹dany sektor

danych o†podanym ID nie zosta³ zna-

leziony;

- MCR (Media Change Request) - uøy-

wany przez urz¹dzenia z†wymiennym

noúnikiem. Ustawienie tego bitu syg-

nalizuje, øe urz¹dzenie wykry³o ø¹-

danie zmiany noúnika;

- ABRT (Aborted Command) - wykony-

Rys. 2. Sposób wyprowadzenia sygnałów na złącze IDC40

Tab. 3. Zestawienie sygnałów interfejsu IDE

Sygnał

Źródło

Typ

Pull−up

Pull−up

Uwagi

sterowania

na wyjściu hosta

przy urządzeniu

(patrz uwaga 1)

(patrz uwaga 2)

(patrz uwaga 2)

Reset

Host

TP

DD(15:0)

<−>

TS

3

DMARQ

Device

TS

5,6 k

Ω

PD

4

!DIOR/!DIOW

Host

TS

IORDY

Device

TS

1,0 k

Ω

5

CSEL

Host

GND

10 k

Ω

6

DMACK−

Host

TP

INTRQ

Device

TS

DA (2:0)

Host

TP

!PDIAG

Device

TS

10 k

Ω

!CS0 !CS1

Host

TP

!DASP

Device

OC

10 k

Ω

Uwagi:

1. TS = trójstanowy, OC = otwarty kolektor, TP = Totem−pole, PU = „podpięcie” do zasilania, PD =

„podpięcie” do masy, VS = zależne od producenta.

2. Wszystkie wartości rezystorów są minimalnymi, dopuszczalnymi.

3. Urządzenia nie powinny posiadać rezystora pull−up na DD7. Poleca się by host posiadał rezystor

o wartości 10 k

Ω

„podpięty” do masy. Pozwala to na wykrywanie braku urządzenia podczas inicjali−

zacji po włączenia zasilania.

4. Standard ATA−3 definiuje tę linię jako trzystanową, gdy urządzenie nie jest wybrane lub, gdy nie

obsługuje DMA. Gdy obsługuje transfer DMA linia powinna być ustawiana na poziomie wysokim lub

niskim.

5. Sygnał powinien być używany tylko podczas cyklu DIOR/DIOW w aktualnie wybranym urządzeniu.

6. Linia wykorzystywana jako CSEL. Powinna być podłączona do masy przez hosta. Oba urządzenia

(Master/Slave) wymagają rezystora o wartości 10 k

Ω

(pull−up) dołączanego do zasilania.

K U R S

Elektronika Praktyczna 7/2002

88

wana komenda zosta³a przerwana

z†powodu b³Ídnej instrukcji lub b³Íd-

nego parametru - w†przypadku trans-

misji danych, porcja danych powinna

zostaÊ odrzucona;

- TK0NF - úcieøka zerowa nie zosta³a

znaleziona podczas rekalibracji urz¹-

dzenia;

- AMNF - Address Mark Not Found,

znacznik adresu nie zosta³ znale-

ziony po znalezieniu pola o†poda-

nym ID.

Rejestr Features

Adres 1h

CS 2h

7

6

5

4

3

2

1

0

ZawartoúÊ zaleøna od komendy.

Uwaga: rejestr ten nie jest obecnie

wykorzystywany.

Rejestr Sector Count

Adres 2hCS 2h

7

6

5

4

3

2

1

0

DostÍp - zapis/odczyt.

Uwaga: rejestr powinien byÊ zapi-

sywany, gdy BSY = 0, DRQ = 0

i†DMACK nie jest ustawiony.

Uwagi dodatkowe: rejestr zawiera

liczbÍ sektorÛw, ktÛre maj¹ byÊ prze-

s³ane/odczytane. Gdy rejestr = 0†wtedy

bÍdzie przes³ane 256 sektorÛw. Gdy po

transmisji danych w†rejestrze b³ÍdÛw s¹

b³Ídy - w†rejestrze Sector Count znaj-

duje siÍ liczba sektorÛw potrzebnych

do dokoÒczenia transmisji ø¹danej

liczby sektorÛw.

Rejestr Sector Number

Adres 3hCS 2h

7

6

5

4

3

2

1

0

Tryb CHS

Sektor (7:0)

Sektor (7:0)

Sektor (7:0)

Sektor (7:0)

Sektor (7:0)

Tryb LBA

LBA(7:0)

LBA(7:0)

LBA(7:0)

LBA(7:0)

LBA(7:0)

DostÍp - zapis/odczyt.

Uwaga: rejestr powinien byÊ zapi-

sywany, gdy BSY = 0, DRQ = 0

i†DMACK nie jest ustawiony.

Uwagi dodatkowe: rejestr zawiera

pocz¹tkowy adres do medium. W†zaleø-

noúci od trybu - czy ustawiony, lub

skasowany bit LBA w†rejestrze Device/

Head - w†rejestrze Sector Number ma-

my 8†bitÛw danych CHS lub LBA.

Rejestr Status

Adres 7hCS 2h

7

6

5

4

3

2

1

0

BSY

DRDY DF

DSC

DRQ

CORR

IDXERR

DostÍp - tylko do odczytu, przy za-

pisie zapisywany jest rejestr Command.

Uwaga: gdy bit BSY jest ustawiony,

naleøy zignorowaÊ wartoúÊ pozosta³ych

bitÛw (z wyj¹tkiem BSY oczywiúcie).

Gdy BSY=0 moøna odczytywaÊ pozosta-

³e wartoúci bitÛw.

Uwagi dodatkowe: odczyt tego re-

jestru zeruje przerwanie.

- BSY - wskazuje na zajÍtoúÊ urz¹dze-

nia. Przed zapisem lub odczytem

wiÍkszoúci rejestrÛw powinniúmy

sprawdzaÊ stan tego bitu. Do tego ce-

lu zazwyczaj wykorzystywany jest re-

jestr Alternate Status, ktÛry jest zwier-

ciadlanym obrazem rejestru Status. Od-

czyt tego pierwszego nie powoduje

øadnych zmian w†urz¹dzeniu IDE.

- DRDY (Device Ready) sygnalizuje, øe

urz¹dzenie jest w†stanie przyjmowaÊ

komendy.

- DF (Device Fault) wskazuje na uszko-

dzenie urz¹dzenia.

- DSC (Device Seek Complete) g³owice

urz¹dzenia zosta³y ustawione na wy-

bran¹ úcieøkÍ.

- DRQ (Data Request), urz¹dzenie jest

gotowe do przes³ania porcji danych.

- CORR (Corrected Data) - wskazuje na

wyst¹pienie b³Ídu podczas transmisji da-

nych, ktÛry jesteúmy w†stanie poprawiÊ

(np. poprzez CRC). Ustawienie tego bitu

nie powoduje zakoÒczenia transmisji.

- IDX (Index) specyficzne dla produ-

centa.

- ERR (Error) wskazuje na wyst¹pienie

b³Ídu. B³¹d wyst¹pi³ w†wyniku wy-

konania poprzedniej komendy. Trans-

misja danych zostanie przerwana.

PrzyczynÍ wyst¹pienia tego b³Ídu do-

datkowo pokazuje rejestr Error.

Pawel Dienwebel

pelos@pelos.pl

Rys. 3. Możliwe sposoby dołączania napędów do sterownika

Tab. 4. Funkcje rejestrów I/O oraz przypisane im adresy

Adresy

Funkcje rejestrów

CS0

CS1 DA2 DA1 DA0

Magistrala danych dla

Magistrala danych dla

Read (DIOR)

Write (DIOW)

N

N

x

x

x

Wysoka impedancja

Nie używana

Rejestry Control Block

N

A

0

x

x

Wysoka impedancja

Nie używana

N

A

1

0

x

Wysoka impedancja

Nie używana

N

A

1

1

0

Alternate Status

Device Control

N

A

1

1

1

(uwaga 1)

Nie używana

Rejestry Command Block

A

N

0

0

0

Data

Data

A

N

0

0

1

Error

Features

A

N

0

1

0

Sector Count

Sector Count

A

N

0

1

1

Sector Number LBA (7:0)

Sector Number LBA (7:0)

(uwaga 2)

(uwaga 2)

A

N

1

0

0

Cylinder Low LBA (15:8)

Cylinder Low LBA (15:8)

(uwaga 2)

(uwaga 2)

A

N

1

0

1

Cylinder High LBA (23:16)

Cylinder High LBA (23:16)

(uwaga 2)

(uwaga 2)

A

N

1

1

0

Device/Head LBA (27:24)

Device/Head LBA (27:24)

(uwaga 2)

(uwaga 2)

A

N

1

1

1

Status

Command

A

A

x

x

x

Niedozwolony addres

Niedozwolony addres

Uwagi:

1. Ten rejestr nie jest stosowany we współczesnych sterownikach napędów.

2. Mapowanie rejestrów w trybie LBA.

Oznaczenia stanów na liniach adresowych:

A − sygnał ustawiony, N − sygnał zanegowany, x − bez znaczenia

81

Elektronika Praktyczna 8/2002

K U R S

Tryby adresowania

WyrÛøniamy dwa, wczeúniej juø

wspomniane, tryby adresowania:

1. CHS - adresowanie odbywa siÍ za

pomoc¹ trzech pÛl:

- Cylinder (1...255),

- Head (1...15),

- Sector (0...65535).

2. LBA, w†ktÛrym adres jest wylicza-

ny ze wzoru: LBA = ((cylinder *

heads_per_cylinder + heads) * sec-

tors_per_track) + sector - 1.

Gdy urz¹dzenie posiada mniej niø

16515072 sektorÛw, domyúlnym trybem

adresowania staje siÍ tryb CHS. W†prze-

ciwnym przypadku - LBA. Sterownik

wbudowany w†napÍd, bez wzglÍdu na

pojemnoúÊ noúnika danych, powinien

obs³ugiwaÊ oba tryby adresowania. Host

wybiera tryb adresowanie poprzez usta-

wienie bitu LBA w†rejestrze Device/He-

ad. Po w³¹czeniu zasilania urz¹dzenie

IDE przechodzi automatycznie na tryb

adresowania CHS.

Sterowanie CD-ROM-em

Sterowanie CD-ROM-em odbywa

siÍ za pomoc¹ 12-bajtowych ramek

zwanych rozkazami. Pierwszy bajt

w†ramce jest jednoczeúnie kodem roz-

kazu. Aby przes³aÊ 12-bajtow¹ ramkÍ

steruj¹c¹ naleøy przedtem - kaødora-

zowo - ustawiÊ odpowiednie rejestry.

Zaczynamy od sprawdzenie rejest-

ru Alternate Status i†stanu bitu BSY.

Odczytujemy cyklicznie w†pÍtli rejestr

dopÛki bit BSY nie bÍdzie rÛwny

ì0î. Odczytujemy rejestr Status -

spowoduje to skasowanie ewentualne-

go przerwania. Do rejestru Cylinder

Low wpisujemy wartoúÊ 12 (dziesiÍt-

nie) - jest to liczba danych, jak¹

chcemy przes³aÊ do urz¹dzenia. Ze-

rujemy rejestry Cylinder High, Featu-

res, Sector Count, Sector Number. Do

rejestrÛw Cylinder Low i†Cylinder

High wpisujemy liczbÍ bajtÛw, jak¹

jesteúmy w†stanie odebraÊ od napÍ-

du. Sprawdzamy wartoúÊ bitu w†re-

jestrze Alternate Status i†czekamy do-

pÛki bit BSY = 1. Odczytujemy re-

jestr Status - spowoduje to skasowa-

nie zadania obs³ugi przerwania.

Wpisujemy do rejestru Command

tzw. Atapi Packet Command - bajt

o†wartoúci 0xA0. Bajt ten informuje

urz¹dzenie, øe bÍdziemy przesy³aÊ

ramk͆steruj¹c¹, a nastÍpnie:

- odczytujemy zawartoúÊ rejestru Al-

ternate Status;

- czekamy, aø bit BSY bÍdzie rÛwny

ì0î;

- odczytujemy zawartoúÊ rejestru Sta-

tus;

- sprawdzamy wartoúÊ bitu ERR -

powinna byÊ rÛwna ì0î;

- sprawdzamy wartoúÊ bitu DRQ

w † r e j e s t r z e S t a t u s - p o w i n i e n

byʆteraz ustawiony.

- teraz moøemy wpisywaÊ 12-bajtow¹

ramkÍ steruj¹c¹;

- dane wprowadzamy na magistralÍ

danych DD0...15; bajty parzyste

ramki (0, 2, 4, 6, 8, 10) wpisuje-

W drugiej czÍúci artyku³u publikujemy resztÍ podstawowych informacji zwi¹zanych z

programow¹ obs³ug¹ urz¹dzeÒ do³¹czonych do interfejsu ATA. DziÍki nim samodzielne

przygotowanie oprogramowania dla mikrokontrolera wspÛ³pracuj¹cego z dyskiem twardym bÍdzie

znacznie ³atwiejsze niø dotychczas.

Sterowanie CD−ROM−ów i dysków

twardych w praktyce, część 2

K U R S

Elektronika Praktyczna 8/2002

82

my na mniej znacz¹c¹ czÍúÊ ma-

gistrali danych DD0...7 a†bajty nie-

parzyste (1, 3, 5, 7, 9, 11) na

bardziej znacz¹c¹ czÍúÊ magistrali

DD8...15; kaødorazowo musimy wpi-

saÊ dwa bajty, czyli sumarycznie

dokonujemy szeúÊ cykli zapisu;

obecnie tylko bardzo stare urz¹dze-

nia obs³uguj¹ transmisjÍ danych

w†trybie oúmiobitowym.

Gdy porcja danych jest juø goto-

wa na magistrali danych DD0...15, ze-

rujemy liniÍ DIOW. Odczekujemy ok.

1†

µ

s i†ustawiamy DIOW (po-

ziom wysoki). Dane wpisywa-

ne s¹†do urz¹dzenia zboczem

narastaj¹cym. Cykl zapisu po-

wtarzamy szeúÊ razy. Po wpi-

saniu 12 bajtÛw ramki urz¹-

dzenie ustawia bit BSY. Od-

czytuj¹c stan rejestru Alterna-

te Status czekamy, aø bit

BSY bÍdzie rÛwny zero. Gdy

tak siÍ stanie, odczytujemy rejestr Sta-

tus. Sprawdzamy czy bit ERR = 0

oraz czy bit DRQ = 1. NastÍpnie mu-

simy odczytaÊ ile bajtÛw danych ma

do przekazania CD-ROM. WartoúÊ ta

sk³adana jest z†m³odszego bajtu pobie-

ranego z†rejestru Cylinder Low, oraz

starszego bajtu z†rejestru Cylinder

High. Dane z†CD-ROM-u do hosta s¹

transmitowane w†trybie 16-bitowym.

Kaøde opadaj¹ce zbocze sygna³u na li-

nii D I O R powoduje wystawienie

dwÛch bajtÛw danych na magistralÍ

DD0...15. Po odczytanej liczbie bajtÛw

powinniúmy sprawdziÊ czy bit ERR

nie jest ustawiony w†rejestrze Status.

Gdy bit ERR=0 moøemy przyj¹Ê, øe

dane odebrano prawid³owo.

Wyøej wymienione czynnoúci po-

wtarzamy kaødorazowo, gdy chcemy

przes³aÊ porcje danych do CD-ROM-u.

Formaty ramek steruj¹cych

napÍdem

Eject CD - wysuniÍcie p³yty z†na-

pÍdu wymaga wys³ania nastÍpuj¹cej

sekwencji bajtÛw: 0x1B, 0x01, 0x00,

0x00, 0x02, 0x00, 0x00, 0x00, 0x00,

0x00, 0x00, 0x00.

Load CD - za³adowanie kr¹øka do

napÍdu wymaga wys³ania nastÍpuj¹-

cej sekwencji bajtÛw: 0x1B, 0x01,

0x00, 0x00, 0x03, 0x00, 0x00, 0x00,

0x00, 0x00, 0x00, 0x00.

Start CD - wystartowanie napÍdu

i†przeczytanie TOC wymaga wys³ania

nastÍpuj¹cej sekwencji bajtÛw: 0x1B,

0x01, 0x00, 0x00, 0x01, 0x00, 0x00,

0x00, 0x00, 0x00, 0x00, 0x00.

Stop CD - zatrzymanie napÍdu

wymaga wys³ania nastÍpuj¹cej sek-

wencji bajtÛw: 0x1B, 0x01, 0x00,

0x00, 0x00, 0x00, 0x00, 0x00, 0x00,

0x00, 0x00, 0x00.

Po wykonaniu powyøszych pole-

ceÒ CD-ROM nie zwraca øadnych da-

nych. Jak widaÊ kod komendy (naj-

m³odszy bajt) jest w†tych trzech przy-

padkach taki sam. Zmienia siÍ tylko

wartoúÊ czwartego bajtu. W†bajcie

pierwszym ustawiony jest bit zerowy

- oznacza to, øe Status ma byÊ

zwrÛcony natychmiast po tym, jak

s p r a w d z o n a b Í d z i e p o p r a w n o ú Ê

przes³anej ramki przez CD-ROM, sta-

nu tacki (czy wysuniÍta, czy nie)

oraz status p³yty. W†przeciwnym

przypadku Status jest zwracany po

skoÒczeniu ca³ej operacji.

TOC - Table of Contents - to bar-

dzo waøna tablica. Zawiera adresy

pocz¹tkowe poszczegÛlnych úcieøek,

sesji, itp. Jej odczyt przebiega nastÍ-

puj¹co:

Zatrzymanie odtwarzania p³yty CD

audio (Stop) wymaga wys³ania nastÍ-

puj¹cej sekwencji bajtÛw: 0x4E, 0x00,

0x00, 0x00, 0x00, 0x00, 0x00, 0x00,

0x00, 0x00, 0x00, 0x00.

Test gotowoúci urz¹dzenia wyma-

ga wys³ania nastÍpuj¹cej sekwencji

bajtÛw: 0x00, 0x00, 0x00, 0x00, 0x00,

0x00, 0x00, 0x00, 0x00, 0x00, 0x00,

0x00.

NastÍpnie wysy³amy komendÍ Re-

quest Sense Key, ktÛra sk³ada siÍ

z†nastÍpuj¹cej sekwencji bajtÛw:

0

0x03 W wyniku odpowiedzi na tę ramkę otrzymamy

z CD−ROM−u ASC i ASCQ.

Znajdują się one odpowiednio w bajcie 12 i 13.

ASC = 0x00 oznacza płytę CD w napędzie.

ASC = 0x3A brak płyty w napędzie.

ASC = 0x02 głowice nie ustawiły się jeszcze −

musimy czekać.

ASC = 0x04 brak gotowości napędu − musimy

czekać.

1

0x00

2

0x00

3

0x00

4

0x60

5

0x00

6

0x00

7

0x00

8

0x00

9

0x00

10

0x00

11

0x00

Odczyt TOC wymaga wys³ania na-

stÍpuj¹cej sekwencji bajtÛw:

0

0x43

1

0x00 CD zwróci informacje w LBA (0x00)− nie w MSF

(0x02)

2

0x00

3

0x00

4

0x00

5

0x00

6

0x01 Numer początkowej ścieżki od której CD−ROM ma

zwrócić informację

7

0x00

8

0x64 100 bajtów na dane z CD−ROM−u

9

0x00

10

0x00

11

0x00

Poniøej pokazano przyk³adow¹

ramkÍ wys³an¹ przez CD-ROM w†od-

powiedzi na zapytanie o†TOC. Pierw-

sze dwa bajty okreúlaj¹ iloúÊ

przes³anej informacji w†baj-

tach. Bajt czwarty okreúla

l i c z b Í u t w o r Û w † n a p ³ y c i e .

Bajty: 5, 13, 20 itd. s¹ znacz-

nikami pocz¹tku adresu - ma-

j¹ sta³¹ wartoúÊ 0x10. Maj¹

charakter czysto informacyjny.

Waøn¹ úcieøk¹ jest úcieøka

o†numerze 0xAA (tzw. Lead

Track) - adres tej úcieøki oznacza

ostatni sektor na p³ycie CD.

Numer utworu Adres utworu

MSB

...

...

LSB

1

0x00 0x00 0x20 0x00

2

0x00 0x20 0x38 0x1C

3

0x00 0x2C 0x3B 0x21

4

0x00 0x37 0x33 0x03

0xAA

0x00 0x4A 0x38 0x1C

Mamy, wiÍc odczytan¹ informacjÍ

o†adresach úcieøek. Teraz moøemy

przyst¹piÊ do odtwarzania utworÛw.

Przebiega to w†nastÍpuj¹cy sposÛb:

Nr bajtu

Wartość

Komentarz

0

0x00

MSB TOC Data Length

1

0x2A

LSB TOC Data Length

2

0x01

First Track Number

3

0x04

Last Track Number

4

0x00

Reserved

5

0x10

ADR (4 bity)|CONTROL (4 bity)

6

0x01

TrackNumber

7

0x00

Reserved

8

0x00

0x00

0x00

0x00

0x00

MSB

9

0x00

0x00

0x00

0x00

0x00

10

0x02

0x02

0x02

0x02

0x02

11

0x00

0x00

0x00

0x00

0x00

LSB

12

0x00

Reserved

13

0x10

ADR (4 bity)| CONTROL (4 bity)

14

0x02

TrackNumber

15

0x00

Reserved

16

0x00

0x00

0x00

0x00

0x00

17

0x20

0x20

0x20

0x20

0x20

18

0x38

0x38

0x38

0x38

0x38

19

0x1C

0x1C

0x1C

0x1C

0x1C

20

0x00

Reserved

21

0x10

ADR(4 bity)|CONTROL(4 bity)

22

0x03

Track Number

23

0x00

Reserved

24

0x00

0x00

0x00

0x00

0x00

25

0x2C

0x2C

0x2C

0x2C

0x2C

26

0x3B

0x3B

0x3B

0x3B

0x3B

27

0x21

0x21

0x21

0x21

0x21

28

0x00

Reserved

29

0x10

ADR(4 bity)|CONTROL(4 bity)

Napędy CD−ROM są wyposażone w interfejs

ATAPI, który jest rozwinięciem klasycznego

IDE (ATA). Charakteryzuje się on

zastosowaniem protokołu niemal identyczne−

go ze SCSI, przy zachowaniu mechanicznej

i elektrycznej kompatybilności z IDE.

83

Elektronika Praktyczna 8/2002

K U R S

30

0x04

Track Number

31

0x00

Reserved

32

0x00

0x00

0x00

0x00

0x00

33

0x37

0x37

0x37

0x37

0x37

34

0x33

0x33

0x33

0x33

0x33

35

0x03

0x03

0x03

0x03

0x03

36

0x00

37

0x10

38

0xAA

Lead OUT

39

0x00

40

0x00

0x00

0x00

0x00

0x00

41

0x4A

0x4A

0x4A

0x4A

0x4A

42

0x38

0x38

0x38

0x38

0x38

43

0x1C

0x1C

0x1C

0x1C

0x1C

Odtwarzanie p³yty CD audio wy-

maga wys³ania nastÍpuj¹cej sekwencji

bajtÛw:

0

0xA5

1

0x00

2

0x00

0x00

0x00

0x00

0x00

3

0x00

0x00

0x00

0x00

0x00

Adres początkowy utworu

(tutaj

track 1)

4

0x20

0x20

0x20

0x20

0x20

5

0x00

0x00

0x00

0x00

0x00

6

0x00

0x00

0x00

0x00

0x00

7

0x4A

0x4A

0x4A

0x4A

0x4A

Ilość danych − nie adres

końcowy!!!

8

0x38

0x38

0x38

0x38

0x38

Czyli do odtworzenia cała płyta

9

0x1C

0x1C

0x1C

0x1C

0x1C

10

0x00

11

0x00

Wstrzymanie lub wznowienie od-

twarzania (PAUSE) nastÍpuje po wy-

s³aniu nastÍpuj¹cej sekwencji bajtÛw:

0x4B, 0x00, 0x00, 0x00, 0x00, 0x00,

0x00, 0x00, xxx = 0x01 (odtwarzanie

lub wznowienie) xxx = 0x00 (odtwa-

rzanie wstrzymane), 0x00, 0x00,

0x00.

Zatrzymanie odtwarzania p³yty CD

audio (STOP) nastÍpuje po wys³aniu

nastÍpuj¹cej sekwencji bajtÛw: 0x4E,

0x00, 0x00, 0x00, 0x00, 0x00, 0x00,

0x00, 0x00, 0x00, 0x00, 0x00.

Odczyt danych z†sektorÛw

Dysk twardy w†trybie CHS

Sprawdzamy stan bitu Busy w†re-

jestrze Alternate status. Gdy BSY =

1, czekamy na BSY=0 i†odczytujemy

rejestr Status. W†rejestrze Device He-

ad zerujemy bity LBA (odczyt bÍdzie

w†trybie CHS) oraz bit DEV (gdy

chcemy odczytaÊ dane z†Mastera -

w†przeciwnym wypadku ustawiamy

ten bit). Bity 7 i†5 domyúlnie usta-

wiamy. Na mniej znacz¹ce bity tego

rejestru wpisujemy adres Head. W†re-

jestrze Alternate Status sprawdzamy

stan bitÛw DRDY i†BSY. Pierwszy

musi byÊ ustawiony, drugi wyzerowa-

ny. Odczytujemy rejestr Status. Do

rejestrÛw Cylinder High i†Cylinder

Low wpisujemy starszy bajt i†m³od-

szy bajt pocz¹tkowego adresu Cylin-

der. Do rejestru Sector Number wpi-

sujemy liczbÍ sektorÛw do odczytu.

Do rejestru Command wpisujemy

w a r t o ú Ê 0 x 2 0 - k o d k o m e n d y

ATA_READ_SECTS. NastÍpnie czeka-

my ok. 10

µ

s, odczytujemy rejestr

Alternate Status i†sprawdzamy bit

BSY. Czekamy aø bit BSY bÍdzie

wyzerowany. Odczytujemy rejestr Sta-

tus, aby skasowaÊ przerwanie. Spraw-

dzamy stan bitÛw: ERR (powinien

byÊ wyzerowany), DRQ (powinien

byÊ ustawiony - urz¹dzenie chce

przes³aÊ dla nas dane).

Dane odczytujemy jak w†poprzed-

nim przyk³adzie. Opadaj¹ce zbocze

na linii DIOR powoduje wystawienie

dwÛch kolejnych bajtÛw na magistra-

lÍ DD0...15. IloúÊ danych, ktÛre mu-

simy odebraÊ jest okreúlona liczb¹

sektorÛw, jak¹ wczeúniej wpisaliúmy

do rejestru Sector Number pomnoøo-

n¹ przez zmienn¹, ktÛra okreúla licz-

bÍ bajtÛw w†sektorze - tzw. BytesPer-

Sector. WartoúÊ ta moøe wynosiÊ

4096 lub 8192 B.

Dysk twardy w†trybie LBA

Dane odczytujemy bardzo podob-

nie jak w†trybie CHS z†t¹ rÛønic¹, øe

adres pocz¹tkowy podajemy w†LBA,

nastÍpnie sprawdzamy stan bitu BSY.

Gdy jest wyzerowany - ustawiamy bit

LBA w†rejestrze Device/Head. Do

mniej znacz¹cej po³owy rejestru wpi-

sujemy bity 27...24 adresu pocz¹tko-

wego w†trybie LBA. Do rejestru Cy-

linder High wpisujemy bity 23...16

adresu LBA, do rejestru Cylinder Low

bity 15...8, a do rejestru Sector Num-

ber bity 0...7. Do rejestru Sector

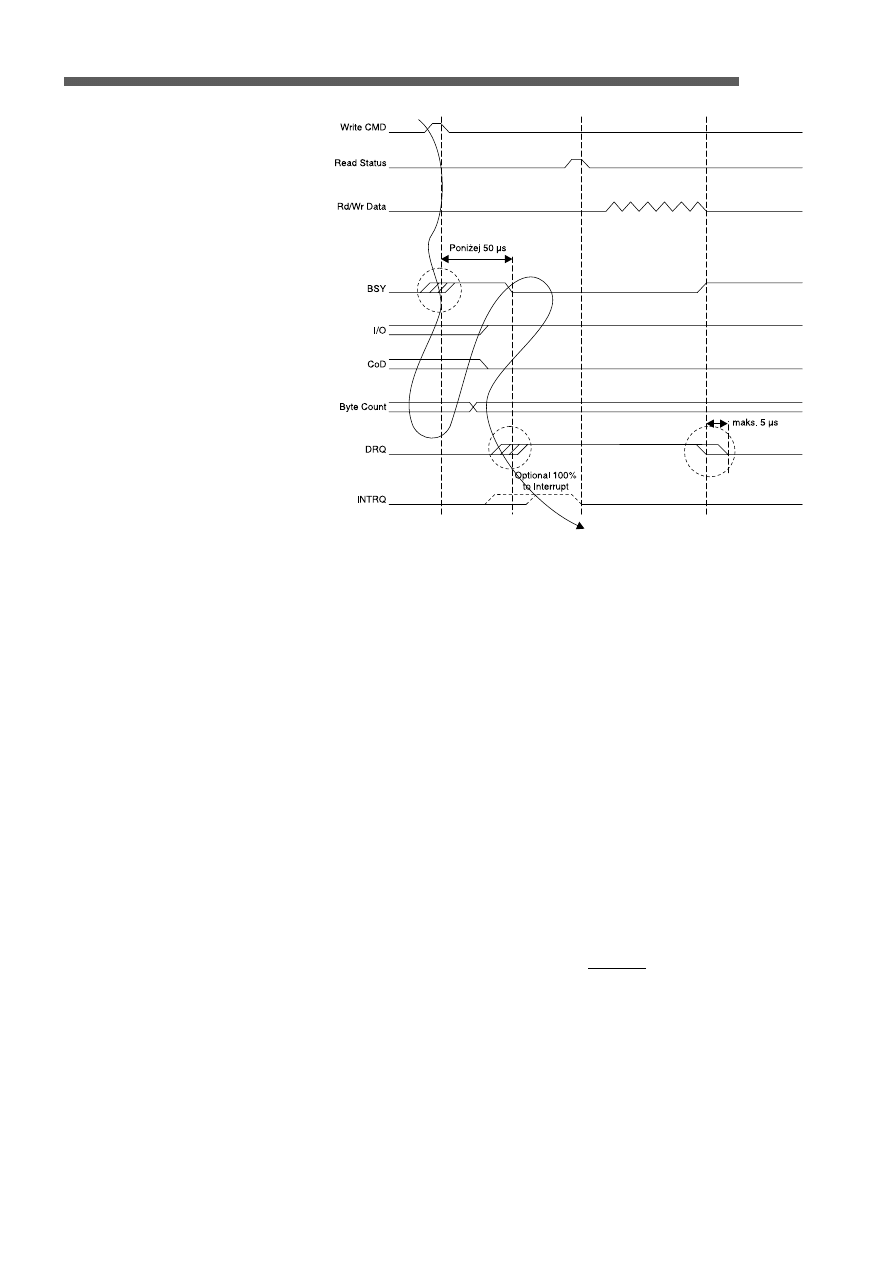

Rys. 4. Przebiegi czasowe charakterystyczne dla zapisu

polecenia do sterownika

Count wpisujemy liczbÍ sektorÛw do

odczytu.

Zaleønoúci czasowe

Na rys. 4 przedstawiono przyk³a-

dowe zaleønoúci czasowe przebiegu

sygna³Ûw na magistrali danych i†li-

niach steruj¹cych CD-ROM-u. Na ry-

sunku pominiÍto dok³adne specyfika-

cje czasÛw pomiÍdzy zmianami syg-

na³Ûw - ma to byÊ tylko ilustracja

dzia³ania interfejsu.

Aplikacja

Na podstawie przedstawionego

opisu przygotowa³em oprogramowanie

steruj¹ce zaimplementowane w†mikro-

kontrolerze z†rodziny AVR. Program

dla niego jest napisany w†C - wszyst-

kie ürÛd³a s¹ dostÍpne na stronie in-

ternetowej http://www.pelos.pl/cd_free/

oraz na p³ycie CD-EP8/2002B.

Pawel Dienwebel

pelos@pelos.pl

Literatura

[1] INF-8020.pdf - ÑATA Packet In-

terface for CDROM rev. 2.6 lub

wyøszeî

[2] CD3610 - Command Specification

[3] http://www.pelos.pl/cd_free/

[4] http://www.yampp.com

[5] Standard ECMA -130 ìData inter-

change on read-only 120 mm

optical data disks (CD-ROM)î

[6] SFF8090i v4 - Fuji Commands for

Multimedia Devices

[7] http://www.republika.pl/romek_by/

index.html

Wyszukiwarka

Podobne podstrony:

cd-rom, Coraz częściej napęd CD-ROM jest zastępowany urządzeniem DVD

Budowa komputera, Napędy CD-ROM DVD itp.

Katechizm WINDOWS, 13 CD-ROM

CD ROM

CD ROM Tester

YAMAHA TYROS 4 ACCESSORY CD ROM

Specyfikacja do sterownika gprs

więcej podobnych podstron