Państwowa Wyższa Szkoła Zawodowa Instytut Informatyki Stosowanej Prowadzący: dr inż. Stanisław Witkowski |

Wykonawcy ćwiczenia: 1. Kierownik 2. 3. 4. |

IIS PWSZ Rok - Grupa - Rok akademicki - |

||

LABORATORIUM Techniki Cyfrowej i Mikrokomputerów |

||||

Data ćwiczenia:

Nr ćwiczenia - VII |

Temat: Multipleksery i demultipleksery |

Ocena: |

||

Cel ćwiczenia.

Celem ćwiczenia jest poznanie podstawowych zagadnień związanych z cyfrowy multiplekserami i demultiplekserami.

Wymagane wiadomości:

Ogólne wiadomości: Dultipleksery i demultipleksery

Multipleksery - wiadomości ogólne

Multiplekser - jest układem posiadającym: wejścia danych, wejście adresowe oraz wyjście. Za pomocą wejścia adresowego można dokonać wyboru, które z wejść ma zostać przekazane na wyjście, najczęściej używanym formatem adresu jest naturalny kod binarny lub „1 z N”. Multipleksery mają często dodatkowe wejście sterujące, zwane wejściem strobującym lub zezwalającym. Jeśli wejście to jest w stanie niskim, to multiplekser działa tak jak określono powyżej, natomiast gdy jest w stanie wysokim, to niezależnie od wejść stan wyjścia jest stały i równy „0”.

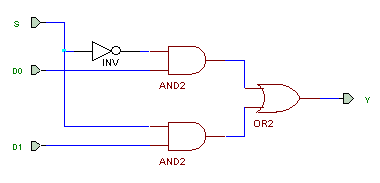

Najprostszym przykładem multipleksera jest multiplekser 2:1. W zależności od stanu na wejściu adresowym S, przekazuje on na wyjście stan z wejścia D0 lub D1.

Jego działanie można opisać funkcją:

lub zapisując inaczej:

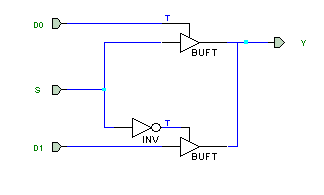

Poniżej przedstawiono układ złożony z bramek trójstanowych, spełniający identyczną funkcję. Połączenie wyjść bramek trójstanowych, jest możliwe ponieważ, nigdy nie są one jednocześnie w wstanie aktywnym (zawsze jedna z nich jest w stanie wysokiej impedancji). Pozwala to na uproszczenie całego układu.

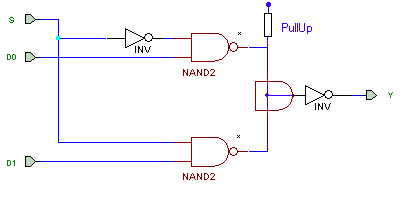

Identycznie działający układ można utworzyć używając bramek NAND z wyjściami typu open colector. Układ ten umożliwia utworzenie tzw. sumy montażowej.

Potencjał wyjścia przyjmuje stan wysoki tylko wówczas, gdy wyjścia wszystkich bramek są w stanie wysokim, co w logice dodatniej odpowiada funkcji AND. Korzystając z prawa de Morgana można postać ilorazową przekształcić w sumę.

jeżeli zanegujemy to wyrażenie to otrzymamy funkcję logiczną:

czyli identyczną jak dla poprzednich dwóch układów.

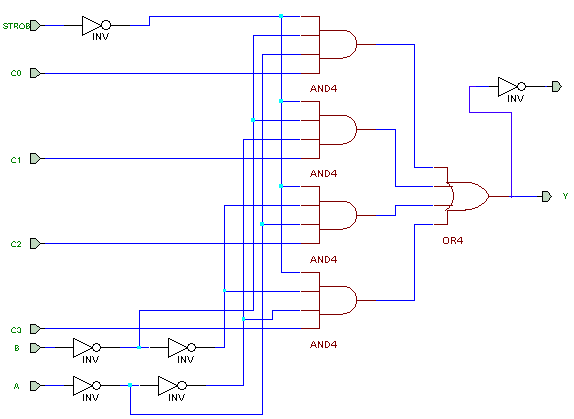

Multiplekser 4:1

Zbudowany multiplekser ma 4 wejścia i 2 wyjścia (wyjście Y oraz jego negacja). Zapiszmy tabele możliwych stanów.

wejścia |

Wyjścia |

|

Adresowe |

Strob. S 1 0 0 0 0 |

Y 0 X0 X1 X2 X3 |

XX 00 01 10 11 |

|

|

D0\AB |

00 |

01 |

11 |

10 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

Analogicznie rozpatrując wszystkie wyjścia otrzymujemy :

;

;

Uwzględniając także wejście strobujące S otrzymujemy

;

;

Wyjście W jest sumą logiczna stanów Yn.

A zatem funkcja uzyskuje postać:

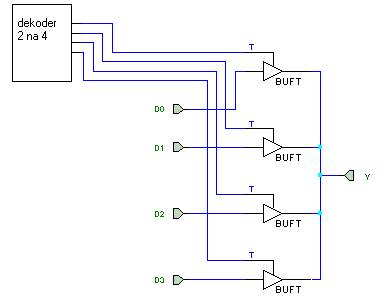

Poniższy układ wykonuje tą funkcję na bramkach trójstanowych.

Takie uproszczenie układu umożliwia budowa bramek trójstanowych. Sterowanie powoduje, że w danym momencie tylko jedna bramka jest aktywna, a pozostałe pozostają w stanie wysokiej impedancji. Pozwoliło to na połączenie ich wyjść.

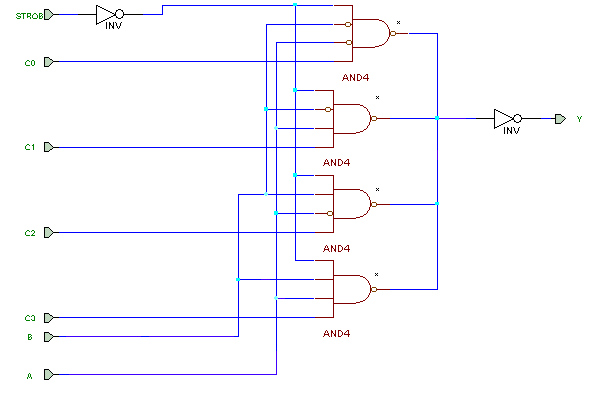

Układ przyjmuje jeszcze inną formę gdy użyjemy bramek typu open colector.

Demultiplekser 1:n

Demultiplekser przekazuje daną wejściową C na tylko jedno z wyjść, które jest określone przez wejście adresowe. Często jest wyposażony w wejście strobujące.

Działanie najprostszego demultipleksera 1:2 można przedstawić za pomocą funkcji:

Tabela stanów demultipleksera 1:4

B |

A |

S |

C |

Y0 Y1 Y2 Y3 |

X |

X |

1 |

X |

1 1 1 1 |

0 |

0 |

0 |

1 |

0 1 1 1 |

0 |

1 |

0 |

1 |

1 0 1 1 |

1 |

0 |

0 |

1 |

1 1 0 1 |

1 |

1 |

0 |

1 |

1 1 1 0 |

X |

X |

X |

0 |

1 1 1 1 |

Zapiszmy tablice Carnaughta dla Y0;

AB SC |

00 |

01 |

11 |

10 |

00 |

1 |

1 |

1 |

1 |

01 |

0 |

1 |

1 |

1 |

11 |

1 |

1 |

1 |

1 |

10 |

1 |

1 |

1 |

1 |

Skąd otrzymujemy:

;

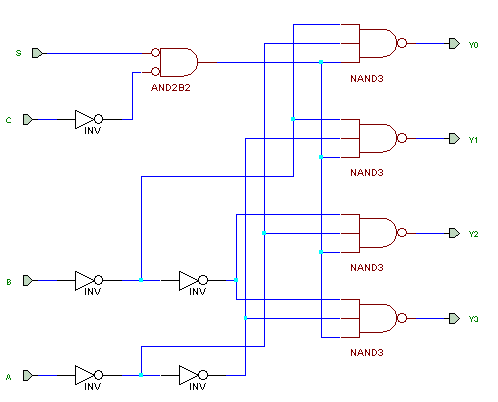

Rozpatrując analogicznie z kolejnymi wyjściami A n konstruujemy układ:

Literatura

J.Pieńkos, J. Turczyński: Układy scalone TTL w systemach cyfrowych. Wydawnictwo komunikacji i Łączności. Warszawa 1986.

M. Nadachowski, Z. Kulka Analogowe układy scalone.

Paweł Sadowski - Praca licencjacka Pomiar napięcia i prądu z zastosowaniem komputera. UMK WFiA.

Craig M., Gillian E.: Zarys cyfrowego przetwarzania sygnałów. Wydawnictwa Komunikacji i Łączności, Warszawa 1999.

Szabatin J.: Podstawy teorii sygnałów. Wydawnictwa Komunikacji i Łączności, Warszawa 2000.

Barbara i Marek Pióro „Podstawy elektroniki 2”

Wyszukiwarka

Podobne podstrony:

multip

Goshman Multiplying Sponge Balls

Multiplekser demultiplekser

funkcja na multiplekserze

Multiple Intelligences in the Elementary Classroom

multiply0 12

multiply0 3

fiat multipla Nawigator connect nav 60360855 09 2004

multiplication table

How To Multiply Your Baby vol 1D a4

Verb Forms Multiple2

multiplekser przebieg dośw

fiat multipla nieszczelne przylacze osuszacza

circle multiplication12s

How To Multiply Your Baby vol 1C a4

8 4 multipleksery id 46830 Nieznany (2)

multiply0 9

Multiplex Communication System

Katalog MultiPlate

więcej podobnych podstron