Który z wymienionych przerzutników ma zabronioną kombinację dwóch jedynek?

Przerzutnik typu JK

Przerzutnik typu DT

Przerzutnik typu 2T

Każdy typu Master-Slave

Przerzutnik typu RS

Przerzutnik typu T

Pierwszym krokiem w procesie projektowania automatu synchronicznego jest:

wybór typu przerzutników

znalezienie funkcji wzbudzeń przerzutników

wyznaczenie tablic przejść i wyjść

kodowanie tablicy przejść

wyznaczenie funkcji realizujących tablice przejść i wyjść

minimalizacja liczby stanów automatu

Układy sekwencyjne zwane są inaczej:

Automatami

Grafami

Złożonymi układami kombinacyjnymi

Układami logicznymi

Aparatami Moore'a

Tablicami przejść

Przerzutniki to:

elementarne trzystanowe układy sekwencyjne typu Moore'a

elementarne dwustanowe układy sekwencyjne typu Moore'a

elementarne jednostanowe układy sekwencyjne typu Moore'a

elementarne trzystanowe układy sekwencyjne typu Mealy'ego

elementarne dwustanowe układy sekwencyjne typu Mealy'ego

elementarne jednostanowe układy sekwencyjne typu Mealy'ego

Każdą funkcję boolowską można zrealizować technicznie wyłącznie za pomocą:

bramek logicznych NOR

bramek logicznych EX-OR

bramek logicznych AND

bramek logicznych NAND

bramek NOR lub NAND

dowolnej z powyższych bramek

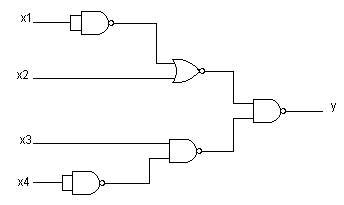

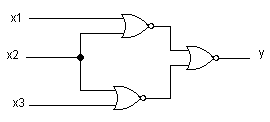

Poniższy układ realizuje funkcję:

~x2+x1+x3~x1+x2+x3~x4

x1+x2+x3~x4

x2+~x3~x4

x1+x3+x2x4

x1+~x2+~x3x4

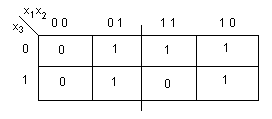

Minimalna postać normalna sumy dla poniższej siatki Karnaugha jest następująca:

~x1x2+x1~x3+x1~x2x1~x2+~x1x3+~x1x2

x1~x2+~x1x2+~x2x3

~x1x2+x1~x2+x2x3

~x1x2+x1x2~x3+x1~x2

~x1~x2+x1x2x3

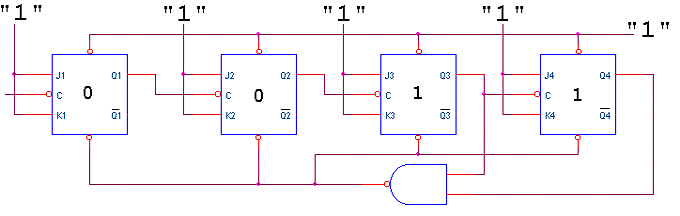

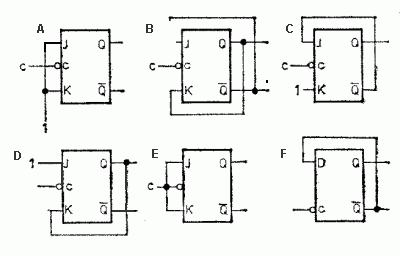

Poniższy rysunek przedstawia licznik

modulo 2modulo 3

modulo 4

modulo 8

modulo 12

modulo 16

Przerzutnik realizujący funkcję Qt+1=~Qt to:

przerzutnik asynchroniczny typu t

"dwójka licząca"

licznik modulo 2

dzielnik częstotliwości przez 2

wszystkie z powyższych

tylko b, c ,d

Dysponując przerzutnikiem JK można wykonać z niego przerzutnik D gdy:

na wejście K będzie podawane 0

na wejście K będzie podawane 1

do wejścia K dołączymy negator

do wejścia K dołączymy bramkę NAND

połączymy wejścia J i K

żadne z powyższych

Przy projektowaniu układów typowo synchronicznych nie powinno się stosować przerzutników:

synchronizowanych zboczem narastającym

synchronizowanych zboczem opadającym

synchronizowanych poziomem

można stosować wszystkie!

master-slave

przerzutników złożonych

Jedną z różnic pomiędzy synchronicznym przerzutnikiem RS a JK jest:

nie ma różnic

różne "zachowanie się" przy podaniu na wejścia dwóch "jedynek"

odmienne "zachowanie się" przy podaniu na wejścia dwóch "zer"

różne "zachowanie się" przy podaniu na wejścia "zera" i "jedynki"

różne "zachowanie się" przy podaniu na wejścia "jedynki" i "zera"

różne zachowanie się niezależnie od wartości wejść

Wskaż wyrażenie fałszywe :

( a * b ) + c = a * ( b + c )a * 1 = a

~ ( a * b ) = ~a + ~b

a * ( a + b ) = a

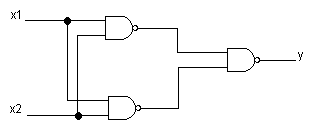

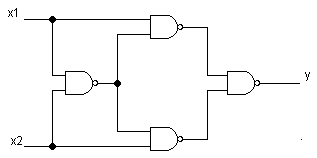

Poniższy układ realizuje funkcję boolowską:

x1+x2

x1+ ~x2

2x1x2x1x2

Poniższy układ realizuje funkcję boolowską:

x1+x2(x1+x3)

x1x2+x3x2

(x1+x2)x3(x1+x2)(x2+x3)

Poniższy układ realizuje funkcję boolowską:

x1 ~x2 + ~x1 x2

x1x2

x1 ~x2

x1 x2+ ~x1 x2

Wskaż najbardziej precyzyjne zdanie: "Kombinacyjny układ logiczny to taki, w którym..."

...stan wyjść zależy od stanu wejść w danej chwili

...stan wyjść zależy tylko i wyłącznie od stanu wejść w danym momencie

...informacja z wejścia podawana jest po czasie 't' na wyjście

...informacja z wejścia podawana jest na wyjście w krótkim czasie

Wynikiem równości ~w + ~z + (x+wz)(v+z) jest ostatecznie:

z

0

1

x

Zapis ab+ ~a ~b + bc jest równoważny zapisowi:

ab + ~a~b + ~ac

c + b * ~a

(a+b)c

a + a ~b + ~ac

Zapis ab+~ab~c+bc równy jest:

0

1

~b

b

Podstawowy przerzutnik RS (asynchroniczny) zbudowany jest z:

dwóch bramek OR

dwóch bramek NOR

trzech bramek AND

dwóch bramek NAND

Hazardem w technice cyfrowej zwykło się nazywać :

przypadek wystąpienia na wyjściu US (układu synchronicznego) licznej grupy "jedynek"

wykorzystanie układów scalonych w produkcji gier liczbowych

fizyczne opóźnienia "wnoszone" przez bramki logiczne

"stany zabronione" w przerzutnikach typu JK

Zapis a~b+c+(~a+b)~c jest równy:

0

1

ac

bc

Zapis (a~b+c)(~a+b)~c jest równy:

0

1

ac

bc

Zapis (ab) c równoważny jest zapisowi:

abc

~c (ab)

(ac)b

(bc)~a

Mając do dyspozycji przerzutnik synchroniczny JK, chcąc na wyjściu przerzutnika w dalszym ciągu mieć 0 należy "przypisać" następujące wartości parametrom:

Cl=Pr=0 J,K dowolne

Cl=Pr=1 J,K dowolne

Cl=Pr=0 J=0 , K=1

Cl=Pr=1 J=0 , K dowolne

Jeżeli na wejście przerzutnika asynchronicznego RS podamy wartość 0, to na wyjściach Q i ~Q otrzymamy wyłącznie:dwie jedynki

dwa zera

0 i 1 lub 1 i 0

jest to "stan logicznie zabroniony"

Konfiguracja układu "dwójki liczącej" (gdzie Pr=Cl=1) jest pokazana na rysunku:

A, B, C, D

A, C, D

tylko C

na każdym

Wejścia zegarowe posiadają:

tylko przerzutniki asynchroniczne

wyłącznie przerzutniki synchroniczne

przerzutniki RS zbudowane z bramek NOR

przerzutniki zbudowane z bramek NAND

Jeśli na wejście przerzutnika RS podamy odpowiednio 0 i 1 to na wyjściach Q i ~Q otrzymamy na przykład:

odpowiednio 1 i 0odpowiednio 0 i 1

wyłącznie same zera

tylko same jedynki

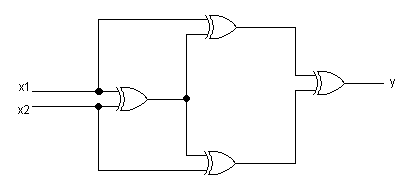

Poniższy układ realizuje funkcję:

x1+x2

x1x2

x1x2

x1-x2

Jeżeli na przerzutnik asynchroniczny

o dwóch wejściach podamy dwa zera to na wyjściu otrzymamy:również dwa zera

tylko dwie jedynki

0 i 1 lub 1 i 0

jest to "stan logicznie zabroniony"

Tzw. składowe obojętne funkcji oznaczane najczęściej poprzez "-" podczas minimalizacji formuł boolowskich należy:

zawsze pomijać

uwzględniać tylko wtedy, gdy jest to korzystne

dać sobie spokój z minimalizacją - w tym konkretnym przypadku jest ona niewykonalna!

wszystkie uwzględnić, tzn. każdą zaliczyć do jakiejś utworzonej grupy

Tworząc grupę o ośmiu kratkach w siatce Karnaugha czterech zmiennych możemy wyrugować w opisie tej grupy:

jedną zmienną

dwie zmienne

trzy zmienne

cztery zmienne

Bramka EXOR dwuwejściowa, na której wejściach jest sygnał x oraz stała 1 realizuje:

stałą 1

~x

x

stałą 0

Multiplekser służy do:

wyboru jednego z kilku sygnałów wejściowych i przekazania go na wyjście układu

przenoszenia sygnałów z wejścia na wyjście bez jakichkolwiek opóźnień

"wielokanałowego" przesyłu informacji z wejścia na wyjście danego układu

przenoszenia sygnału z wejścia na jedno wyjść układ

W przypadku licznika, w którym na każde 10 impulsów na wejściu otrzymujemy 3 impulsy na wyjściu, otrzymujemy:

licznik modulo 0.3

dzielnik częstotliwości przez 3

podzielnik 0.3

dzielnik 0.3

Dekoder jest układem:

zmieniającym dowolny kod na kod "1 z n"

zmieniającym kod "1 z n" na kod dziesiętny

zmieniającym dowolny kod na inny, dowolny kod

przekazującym informacje z jednego wejścia na kilka wyjść

USB pozwala:

podłączyć dokładnie jedno urządzenie

podłączyć dokładnie dwa urządzenia

połączyć ze sobą wiele komputerów szeregowo

podłączyć wiele urządzeń w strukturę drzewiastą

podłączyć wiele urządzeń w strukturę łańcuchową

podłączyć wiele urządzeń Plug & Play

Kontroler przerwań IRQ obsługuje:

przerwania zewnętrzne

przerwania wewnętrzne

obydwa powyższe

przerwania programowe

wszystkie trzy

przerwania niemaskowane

W komputerach PC procesor uzyskuje dostęp do danych zawartych w pamięci DRAM w pakietach o długości:

1-bita

2-bitów

4-bitów

8-bitów

16-bitów

32-bitów

Podstawowa prędkość (1x) odczytu i zapisu danych w dyskach CD-ROM to:

100 KB/s

150 KB/s

200 KB/s

300 KB/s

500 KB/s

1 MB/s

W którym roku powstał pierwszy mikroprocesor?

1967

1969

1971

1972

1975

1976

Rejestry segmentowe są:

8-bitowe

12-bitowe

16-bitowe

32-bitowe

48-bitowe

64-bitowe

Liczba (234)8 po zamianie na NKB ma postać:

1011 1100

1011 0100

1001 1100

1101 0101

0111 0001

1110 0101

Do realizacji UK o czterech wejściach i czterech wyjściach należy zastosować pamięć ROM o pojemności:

8 słów 4-bitowych

16 słów 64-bitowych

16 słów 8-bitowych

8 słów 16-bitowych

4 słowa 4-bitowe

16 słów 4-bitowych

Układ 8051 ma portów:

1

2

3

4

5

8

Układ przerwań 8051 obsługuje w sumie przerwań:

1

2

3

4

5

8

Układ przerwań 8051 obsługuje przerwania na poziomach priorytetu:

1

2

4

8

16

64

Cykl maszynowy 8051 składa się z taktów fXTAL2

2

4

8

12

16

64

W jednym cyklu maszynowym 8051 odczyt pamięci programu następuje:

raz

2 razy

4 razy

8 razy

16 razy

64 razy

Port szeregowy może pracować

tylko w jednym trybie

w jednym z dwóch możliwych trybów

w jednym z trzech możliwych trybów

w jednym z czterech możliwych trybów

w jednym z ośmiu możliwych trybów

w żadnym z powyższych

Wskaż prawdziwe zdanie:

aby wyzerować mikrokomputer w czasie pracy trzeba utrzymać sygnał zerujący przez 4 cykle maszynowe

po włączeniu zasilania konieczne jest utrzymanie stanu wysokiego na wejściu RST/VPD co najmniej 20ms od chwili osiągnięcia przez napięcie zasilania wymaganego poziomu

w czasie zerowania systemu zawartość pamięci danych nie zostaje wyzerowana

po włączeniu zasilania konieczne jest utrzymanie stanu niskiego na wejściu RST przez czas potrzebny do ustabilizowania się generatora

a,b,c,d są fałszywe

a,b,c,d są prawdziwe

Wskaż fałszywe zdanie: W rozkazach skoków 8051 możliwe jest adresowanie:

bezpośrednie, z adresem 16-bitowym

bezpośrednie, z adresem 11-bitowym

względne, względem PC

pośrednie, sumą zawartości akumulatora i rejestru DPTR

jedno z a,b,c,d jest fałszywe

a,b,c,d są prawdziwe

Liczbę 5 na trzech bitach w kodzie Gray'a zapisujemy jako:

101

110

111

001

100

010

Wyszukiwarka

Podobne podstrony:

Test 28

TEST 28

28 Test „bolesny łuk”, test Lift off, test Yergasona, test “pustej puszki” – wykonanie i

Test A Rachunek kosztow (dr M Rowinska) [28 01 11]

28 Test „bolesny łuk”, test Lift off, test Yergasona, test “pustej puszki” – wykonanie i

2011 10 28 test oxford angielski podstawowa 4

p 28 test 2 listening part 4 a

2011 10 28 test oxford angielski podstawowa 2

2011 10 28 test oxford angielski ponadpodstawowa 3 4

2011 10 28 test oxford angielski ponadpodstawowa 1 2

Test samokształcenie KP 4 9 28 2

2011 10 28 test oxford angielski ponadpodstawowa 5 6

2011 10 28 test oxford angielski podstawowa 3

Kosci, kregoslup 28[1][1][1] 10 06 dla studentow

TEST NR 5

więcej podobnych podstron