LABORATORIUM UKŁADÓW ELEKTRONICZNYCH

Ćwiczenie 7

DEKODERY , MULTIPLEKSERY I KONWERTERY KODU

Gdynia 2001-11-24

ĆWICZENIE 7 / WKŁADKI DD231A, DD231B DD231C/

DEKODERY, MULTIPLEKSERY I KONWERTERY KODU

7.1 Wstęp

Niniejsze ćwiczenie poświęcone jest cyfrowym układom kombinacyjnym służącym do zmiany kodów tzw. Konwerterom kodu. W ćwiczeniu badane są konwertery kodów zbudowane z bramek logicznych TTL oraz scalonych układów TTL - multipleksera i demultiplekserów.

Celem ćwiczenia jest zaznajomienie z budową i działaniem wybranych realizacji układowych prostych konwerterów kodu.

7.2. OPIS TECHNICZNY UKŁADÓW BADANYCH

Układy konwerterów kodu / wkładka DD231A /

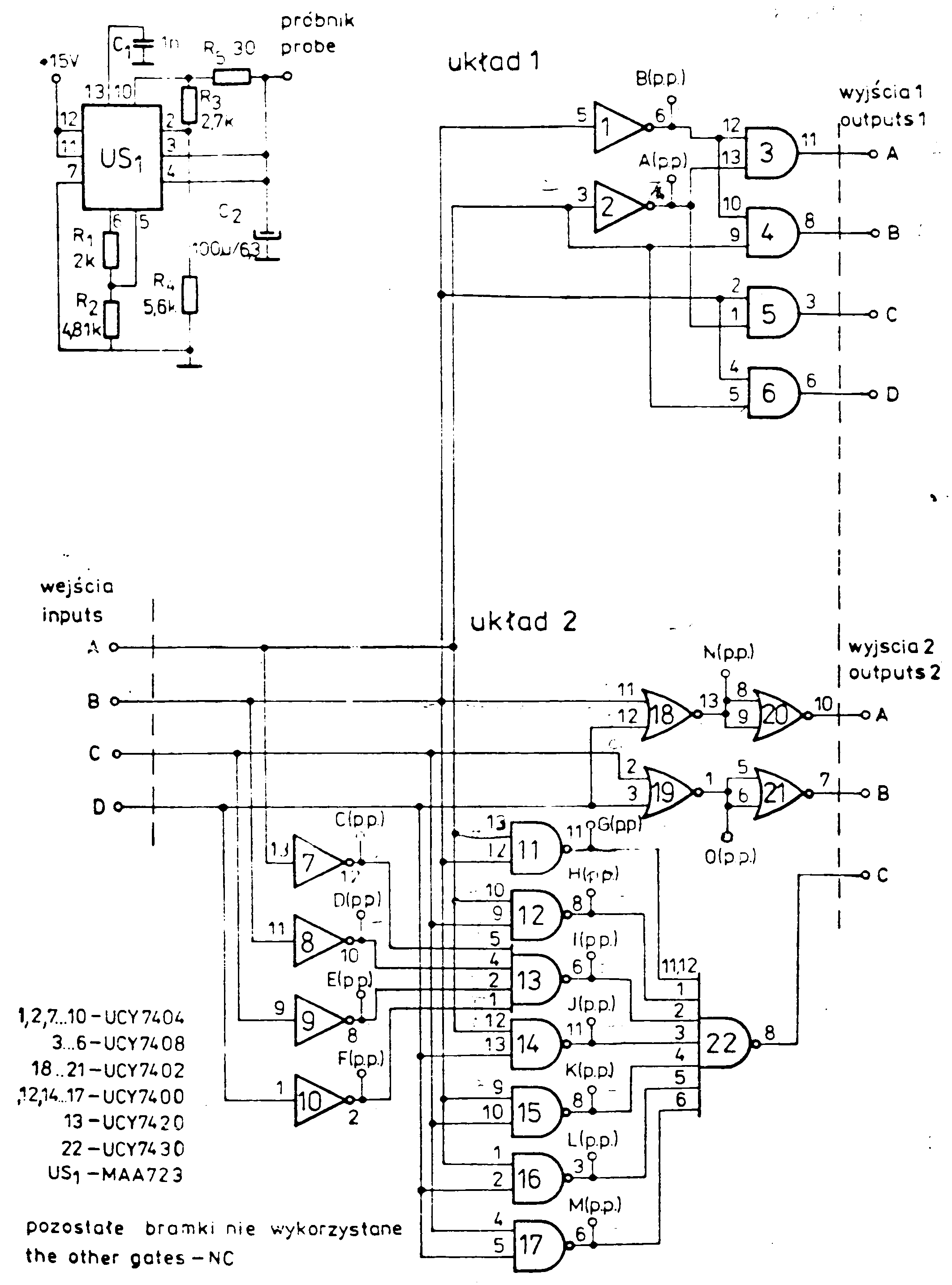

Wkładka DD231A zawiera dwa konwertery kodów / układ 1 i 2 / zbudowane z bramek typu NAND / rys. 7.1 /. Układ 1 stanowi dekoder dwubitowego naturalnego kodu binarnego na kod 1 z 4 . Układ 2 jest dekoderem kodu 1 z 4 na dwubitowy naturalny kod binarny i realizowany jest na bramkach B18-21 układu 7402.

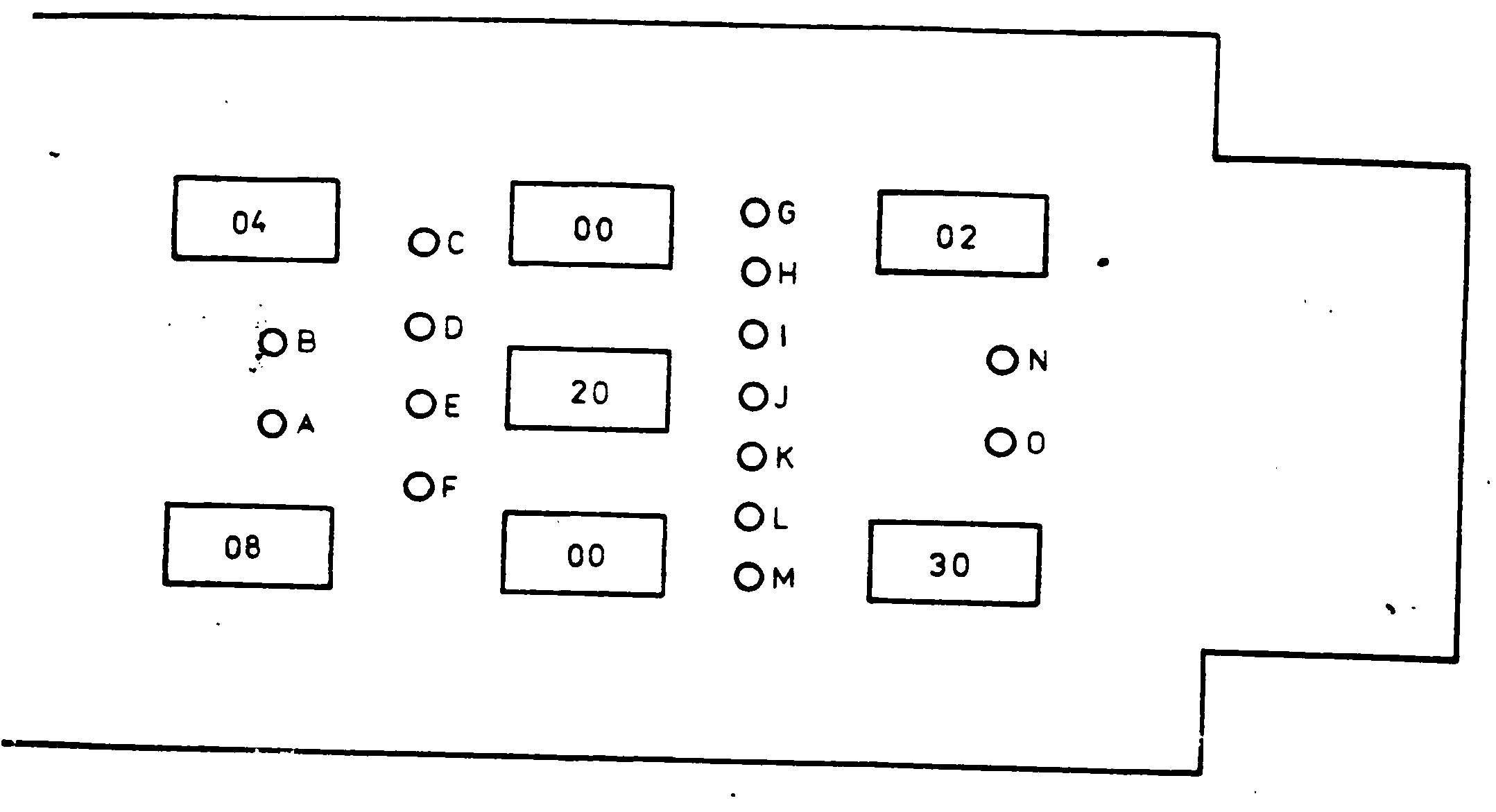

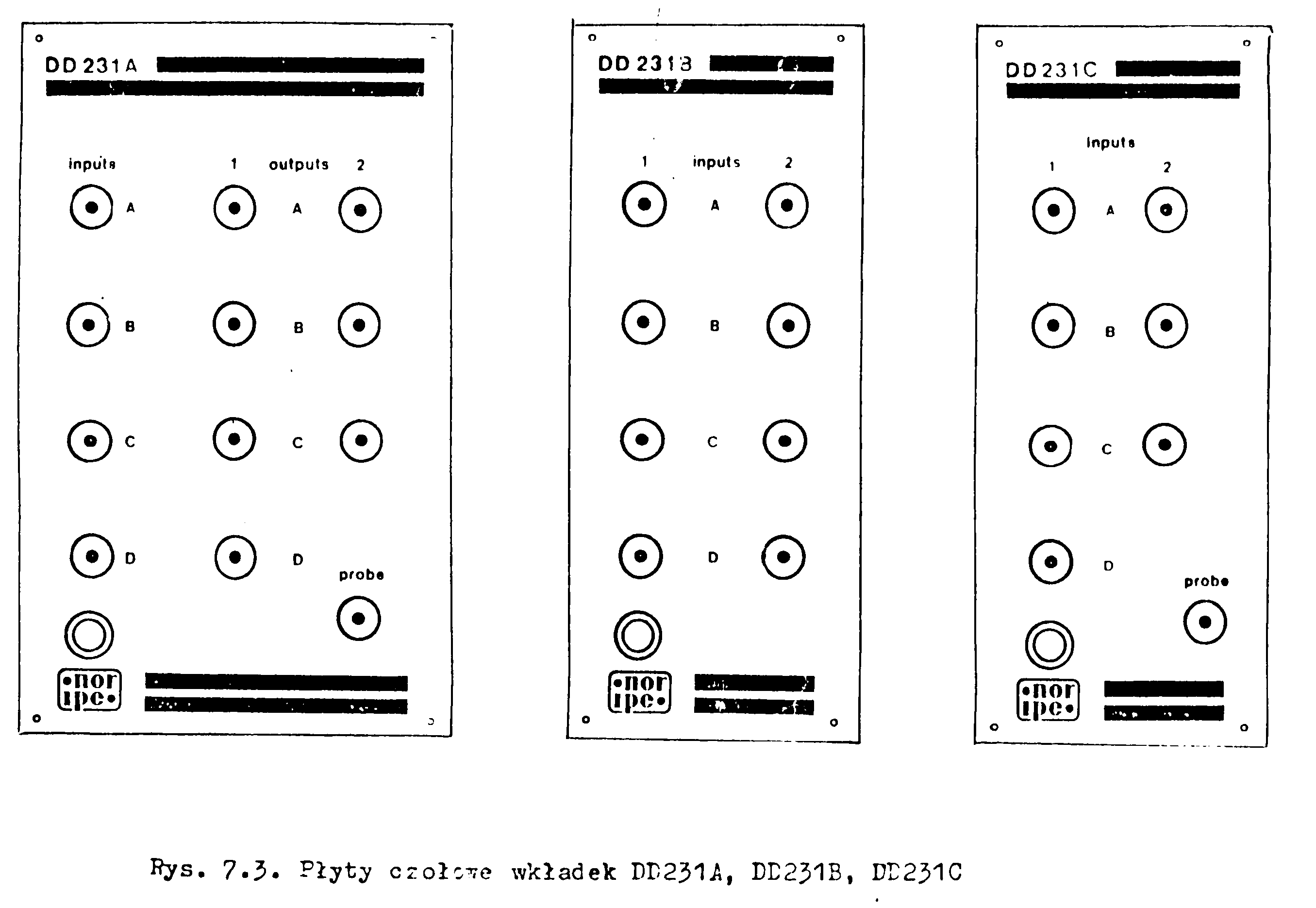

Punkty pomiarowe od A / p.p / do O / p.p / umożliwiają sprawdzenie poziomów logicznych w charakterystycznych miejscach układów przy pomocy sondy logicznej- próbnika. Rozmieszczenie głównych elementów układów wraz z punktami pomiarowymi przedstawiono na rys. 7.2. Poziomy logiczne na wejściach / rys. 7.3. / badanych układów ustala się za pomocą wkładki SN1222. Wyjścia układów badanych należy połączyć z wkładkami SN9111.

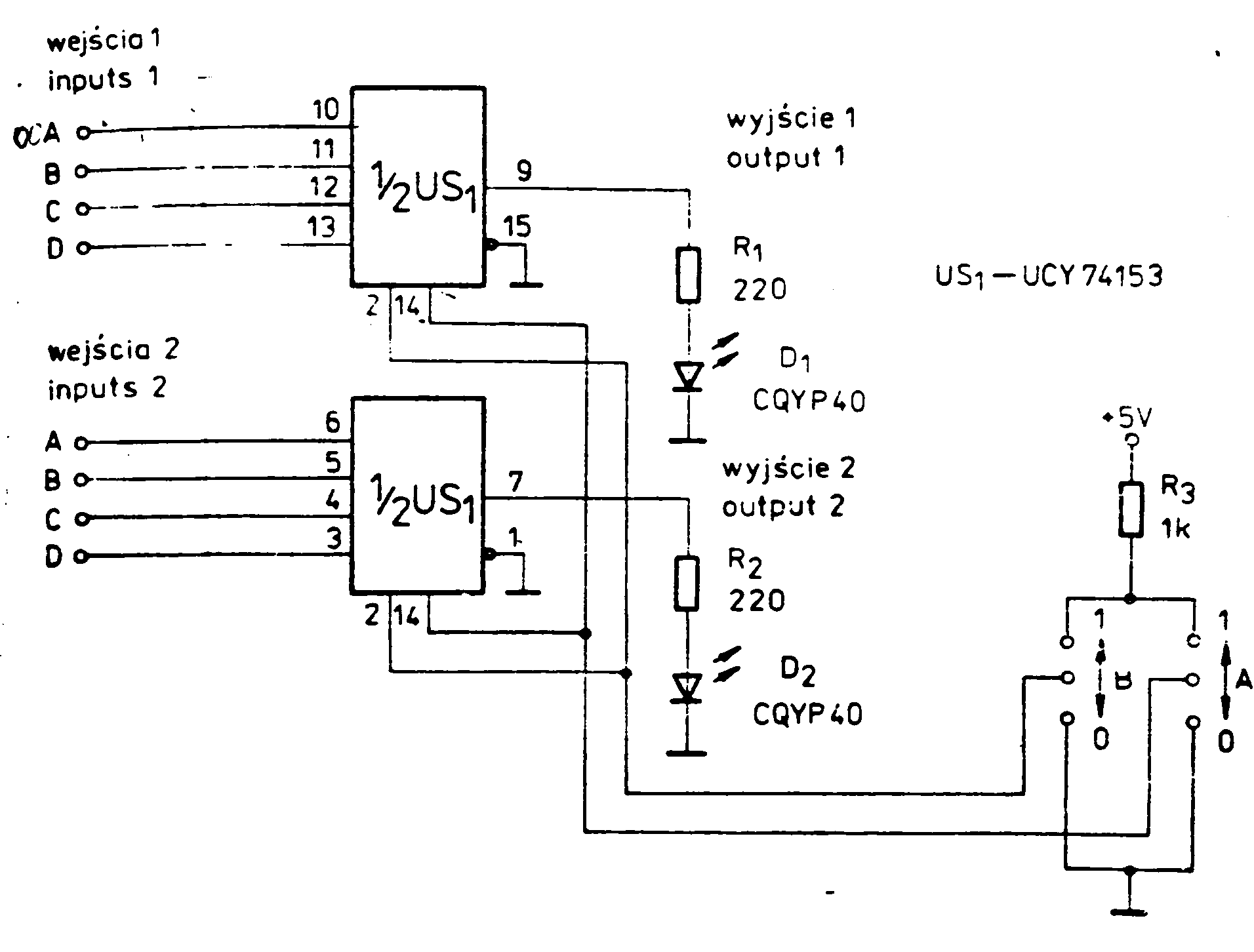

Układ programowanego konwertera kodów / wkładka DD231B /

Wkładka DD231B zawiera scalony podwójny multiplekser o wspólnych wejściach adresowych A i B / rys. 7.4 /. Stany na tych wejściach ustawione są za pomocą przełączników suwakowych umieszczonych na płytce / rys. 7.5 /. Wejścia informacyjne wyprowadzone są na płytę czołową / rys. 7.3 /. Do wyjść multipleksera dołączone są diody elektroluminescencyjne sygnalizujące wysoki poziom logiczny.

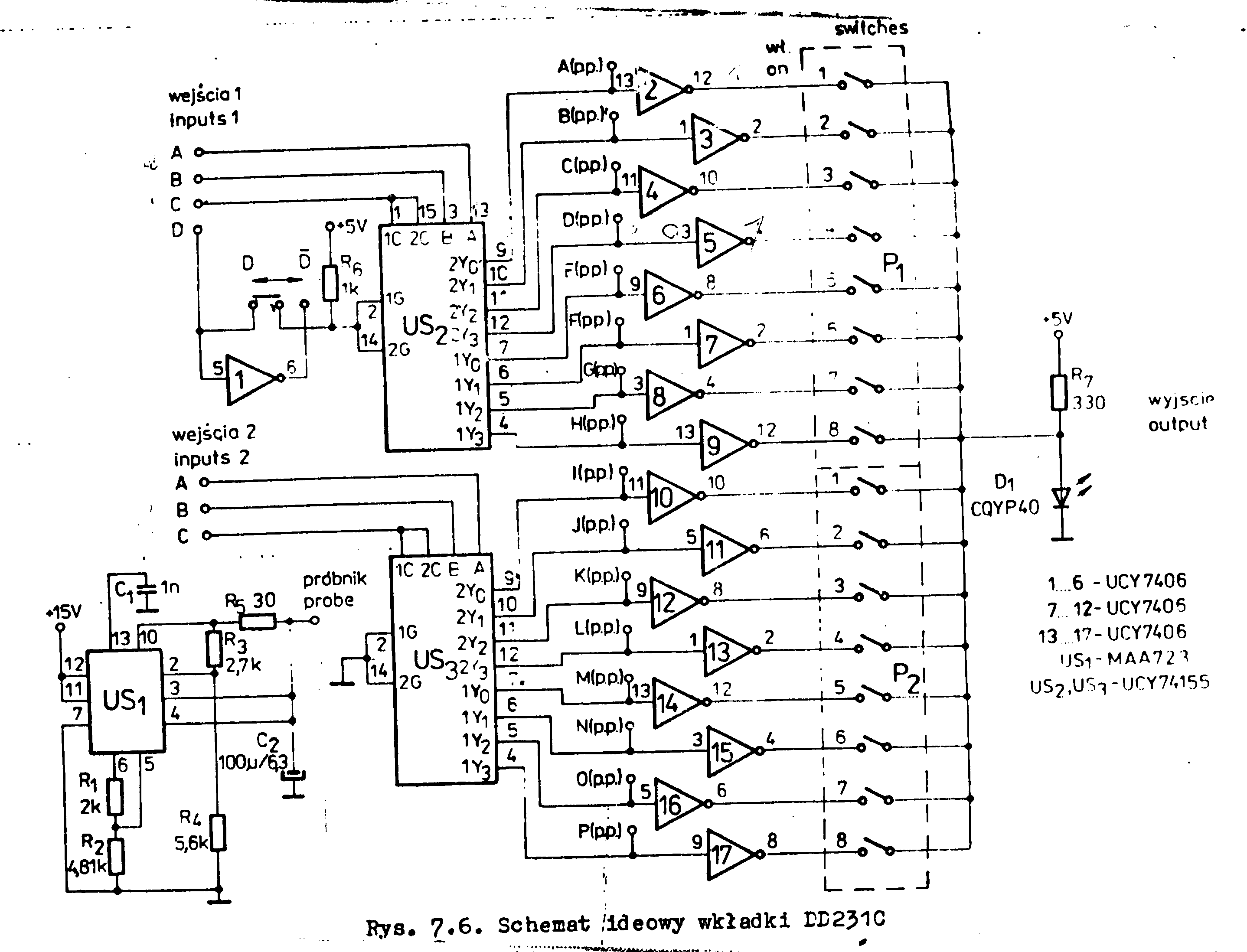

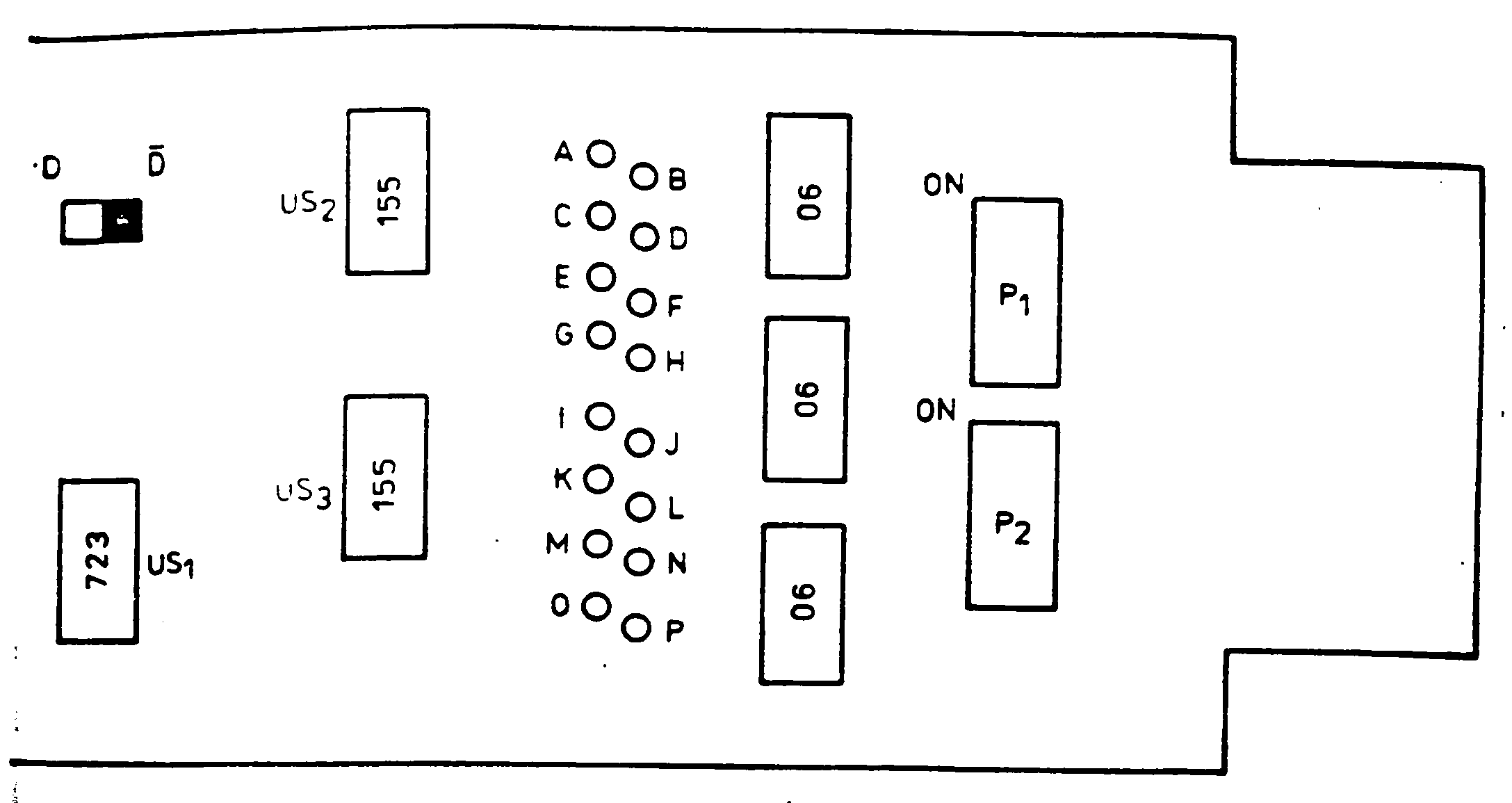

Układ programowanego dekodera komunikatów standardu IEC-625 / wkładka DD231C /.

Wkładka DD231C zawiera dwa podwójne 4-wyjściowe scalone demultipleksery 74155 / rys. 7.6 /. Spełniają one rolę dwóch 8-wyjściowych demultiplekserów, dzięki połączeniu wejść adresowych 1C i 2C.

Na wejście demultipleksera U2 można podawać - za pomocą przełącznika suwakowego / rys. 7.7 / - sygnał z wejścia 1-D / rys. 7. 3 / wprost lub zanegowany. Wejście układu U3 jest na stałe połączone z masą . kombinacje poziomów logicznych na wejściach adresowych 1-A,B,C,D oraz wejściach 2-A,B,C, powodują więc pojawienie się zera logicznego na jednym z wyjść układu U3 . Natomiast na jednym z wyjść układu U2 pojawia się poziom logiczny wynikający z położenia przełącznika suwakowego oraz poziomu na wejściu 1-D.

Do wyjść układów U2 i U3 dołączone są inwertery z otwartym obwodem kolektora tranzystora wyjściowego. Poziomy logiczne na tych wyjściach można sprawdzać za pomocą próbnika poprzez badanie

Rys.7.1. schemat ideowy wkładki DL 231 A

Rys.7.2. Rozmieszczenie głównych elementów oraz punktów pomiarowych na płytce wkładki DD 231 A

poziomów logicznych w punktach pomiarowych: A / p.p / do O / p.p /.

Mikroprzełączniki P1 i P2 umożliwiają wybranie odpowiednich wyjść inwerterów, a tym samym wyjść układów U2 i U3. W momencie wystąpienia na wyjściach wybranych inwerterów jedynek logicznych zapala się dioda elektroluminescencyjna.

Ustawienie wszystkich mikroprzełączników w pozycji przeciwnej niż „ on „ powoduje świecenie się diody niezależnie od kombinacji poziomów logicznych na wejściach 1-A,B,C,D i wejściach 2-A,B,C,D. Należy o tym pamiętać , by nie wyciągać niesłusznych wniosków.

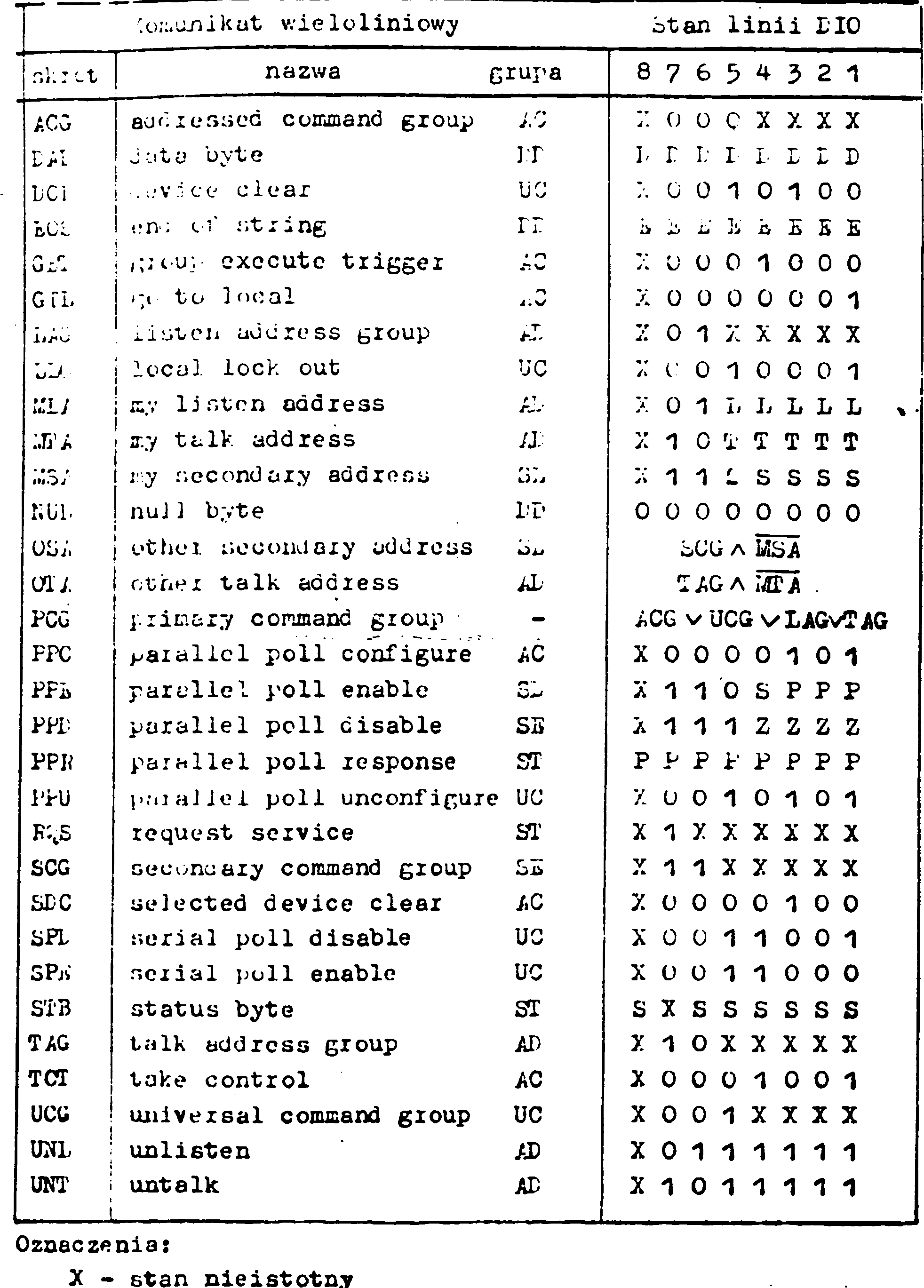

Poziomy logiczne na wejściach wkładki DD231C odpowiadające odpowiedniemu komunikatowi w standardzie IEC-625 / tab. 7.1 / należy ustawiać za pomocą dwóch wkładek SN1222.

APARATURY POMIAROWEJ

Do wykonania ćwiczenia potrzebne są następujące przyrządy pomocnicze

-generatory stanów logicznych TTL 2 x SN1222

-generator impulsów zegarowych TTL SN3311

-wskaźniki stanów logicznych 2 x SN9111

-sonda logiczna

ZAGADNIENIA WSTĘPNE I PROJEKTOWE

Opracować i narysować tablice prawdy dla dekoderów wkładki DD231A

Opracować i narysować tablice Karnaugha dla funkcji NAND, NOR, AND, EX-OR, EX-NOR 2 i 3 argumentowej.

Zastanowić się w jaki sposób można zrealizować te funkcje za pomocą wkładki DD231B

3. opracować układ połączeń wkładek SN1222 z wkładką DD231C oraz ustawienia przełączników na płytce wkładki DD231C w przypadku dekodowania komunikatów standardu IEC-625 DCL, / patrz tab.7.1 /.

opracować i narysować schematy połączeń układów badanych i aparatury pomocniczej do wszystkich eksperymentów wykonywanych w ćwiczeniu.

Rys .7.4.schemat ideowy wkładki DD 231 B

Rys.7.5. Rozmieszczenie głównych elementów na płytce wkładki DD231B

Rys .7.7. rozmieszczeniie głównych elementów na płytce wkładki DD 231C

7.5 OBSERWACJA I POMIARY

Określenie tablic prawdy układów wkładki DD231A

Podając różne kombinacje poziomów napięcia na wejścia A,B,C,D, wkładki DD231A sprawdzić poziomy logiczne na wyjściach i we wszystkich punktach pomiarowych. Narysować tablice prawdy, w których wypisane będą dla wszystkich możliwych kombinacji logicznych na wejściach A,B,C,D, odpowiadające im kombinacje logiczne na wyjściach układów wkładki DD231.

sprawdzić doświadczalnie poprawność opracowania zagadnienia wstępnego 1 dla układu 1 oraz podać czy badany układ 1 jest dekoderem pełnym czy niepełnym.

podać jaką funkcję spełnia wyjście C2 układu badanego 2.

Tablica .7.1. Kody komunikatów wieloliniowych w standardzie LEC - 625

Oznaczenia:

X - stan nieistotny

D - bity informacyjne, zależne od urządzenia

W - bity kodu zależnego od urządzenia, służącego do identyfikacji komunikatu EOS

L - bity kodu adresu odbiorcy

T - bity kodu adresu nadawcy

S - bity kodu adresu wtórnego / w komunikacie MSA / lub

bit określający wartość logiczną odpowiedzi w kontroli równoległej / w komunikacie PPŁ /lub

bity zależne od urządzenia, niosące informację o jego stanie / w komunikacie STB /

P - bity za pomocą których kodowany jest numer linii DIO,

przypisanej danemu urządzeniu podczas kontroli równoległej / w komunikacie PPE /lub

bity odpowiedzi podczas kontroli równoległej / w komunikacie PPR /

Z - bity nie niosące informacji, nie dekodowane , wszystkie

jednak powinny mieć wartość logiczną zero.

c/ wyjaśnić dlaczego w przypadku nie korzystania z wyjścia C2 układu 2 informacja o poziomie logicznym na wejściu A nie jest dekodowania; wskazać wady i zalety takiego rozwiązania.

7.5.2. Obserwacja pracy multipleksera realizującego wybrane funkcje logiczne / wkładka DD231B /

sprawdzić doświadczalnie poprawność rozwiązywania zagadnienia wstępnego z punktu 2.

zrealizować dowolną 3-argumentową funkcję o 2 wyjściach o podanej poprzez prowadzącego tablicy Karnaugha.

Zagadnienie;

Opisać czynności projektowe przy realizacji funkcji „ n” zmiennych za pomocą multiplekserów o n-1 - wejściach adresowych.

7.5.3. Obserwacja pracy dekodera komunikatów standardu IEC-625 / wkładka DD231C /

1.korzystając z tablicy 7.1. sprawdzić doświadczalnie poprawność rozwiązywania zagadnienia wstępnego z punktu 3.

2.zdekodować wszystkie pozostałe komunikaty wieloliniowe.

Zagadnienia;

A/ podczas dekodowania niektórych komunikatów za pomocą wkładki DD231C pomocna jest zmiana położenia przełącznika sówakowego na płytce: podać które to komunikaty,

B/ wybrać z tab. 7.1 komunikaty, których nie da się zdekodować za pomocą wkładki DD231C, podać uzasadnienie.

Wyszukiwarka