Cyfrówka - wykład 1 (24. luty 2003)

Organizacja komputerów:

SISD (single instruction stream, single data stream - jeden strumień instrukcji, jeden strumień danych), lata 40te, później Commodore, ZX Spectrum, wykonywanie tylko 1 programu w określonej chwili czasu.;

SIMD (single instruction, multiple data) - jeden strumień instrukcji, wiele strumieni danych). Układy dobre do wykonywania określonego zadania, np. mnożenie 2 macierzy przez siebie („w kółko to samo, zmieniają się dane”), sieci neuronowe. SIMD są uzupełnieniem SISD lub MIMD, nie działają samodzielnie;

MISD - układy istniejące tylko w teorii;

MIMD - wiele instrukcji, wiele danych - środowisko wielozadaniowe.

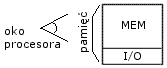

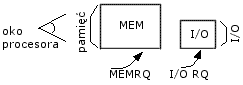

Elementy komputera:

jednostka centralna ALU (arithmetical logic unit),

pamięć,

urządzenia wejścia/wyjścia.

Elementy te połączone są magistralami (przewodami); rodzaje magistral:

danych,

adresowe (odwoływanie do określonego elementu),

sterująca (czuwająca nad poprawnością przepływu informacji).

PROCESOR - budowa

arytmometr (=liczydło)

+, -, : ,* - podstawowe działania na liczbach stało- i zmiennoprzecinkowych, więcej z koprocesorem arytmetycznym,

OR, AND...,

słowo procesora - maksymalny pakiet danych który może przetworzyć arytmometr,

rejestr flagowy, statusowy, PSW. Rejestr flagowy niesie informację z jakim skutkiem wykonała się operacja, działa tutaj sprzężenie zwrotne - może nakazać powtórzenie operacji; rozgałęzienia w programie zależą od rejestru flagowego.

rejestry:

ogólnego przeznaczenia - pamiętanie danych, informacje o adresach wskazujących np. na komórki pamięci lub urządzenia I/O (we/wy). Jest ich dużo (około 100) - im więcej rejestrów tym lepiej, szybsze przekazywanie danych, szerokość rejestru dopasowana do słowa procesora (np. słowo 16-bitowe -> rejestr 16-bit albo więcej).

specjalne - czuwanie nad prawidłowością pracy procesora.

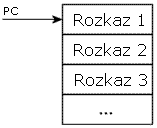

PC - program counter - licznik programów, czuwanie nad poprawną realizacją zadań wykonywanych przez procesor. PC wskazuje który rozkaz ma być wykonany, potem wskazuje na następny,

IR - instruction register - rejestr instrukcji - przechwycenie rozkazu pobranego z pamięci i trafia do IR - dekodowanie rozkazu („co jest do zrobienia”),

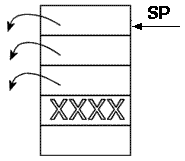

SP - wskaźnik stosu. Stos - fragment pamięci operacyjnej, dostępny w specyficzny sposób - dane są ułożone „jedna na drugiej”, możliwy jest tylko dostęp do szczytu stosu, a na szczyt wskazuje właśnie SP. Na stosie: 1. odkładamy stan procesora, 2. służy do wywołania przerwania, 3. służy do trzymania danych.

magistrale wewnętrzne - łączenie elementów ze sobą

procesor 8051

ALU - 8-bitowa, wykonuje operacje arytmetyczne i logiczne (XOR, inne podstawowe) stałoprzecinkowe, operacje logiczne również na pojedynczych bitach.

PSW - słowo stanu procesora - 8 bitów

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

CY |

AC |

F0 |

RS1 |

RS0 |

OV |

- |

P |

D7 (MSB): CY - przepełnienie

D6: AC - przeniesienie połówkowe (przy kodzie BCD)

D5: programowalny

D4, D3: do wyboru jeden z czterech banków rejestru

D2: OV - znacznik nadmiaru (w kodzie U2)

D0: parzystość - parzysta lub nieparzysta liczba jedynek w akumulatorze

PC - 16-bitowy

SP - ograniczony

ACC - akumulator - 8-bitowy, operacje arytmetyczne i logiczne

B - rejestr B - mnożenie i dzielenie (dzielnik albo mnożnik), reszta z dzielenia

R0...R7 - 8-bitowe, rejestry ogólnego przeznaczenia, R0 i R1 mogą służyć do adresowania. Cztery zestawy tych rejestrów, tylko jeden może być aktywny.

Pamięć: 128 komórek RAM, 4k ROM

4 porty: P0, P1, P2, P3 - porty równoległe, P0 jako magistrala danych i część magistrali adresowej (młodsza część), P2 jako starsza część magistrali adresowej.

Dodatkowo rejestry specjalne, układy czasowo-licznikowe (3 sztuki).

LISTA ROZKAZÓW PROCESORA

Jest funkcjonalnie pełna - nie ważna jest budowa listy rozkazów, ile jest rozkazów ani jakie są, ale każdy program da się opisać i wykonać tym procesorem - co byśmy nie wymyślili, da się zrobić, ograniczenia to głównie czas wykonania i brak pamięci.

Podział ze względu na budowę listy rozkazów:

CISC, idea - jak najwięcej rozkazów (300, 500...), sporo działań na danych -> wykonanie trwa długo;

RISC - lista okrojona - mało rozkazów (około 30), rozkazy proste i szybko się wykonują -> lepsze od CISC.

W 8051 jest 111 rozkazów.

GRUPY ROZKAZÓW

rozkazy przesłań - rejestr -> rejestr, pamięć -> rejestr, ... - przemieszczanie danych

rozkazy arytmetyczne

rozkazy logiczne

rozkazy sterujące

Wykonanie rozkazów w procesorze:

pobranie rozkazu z pamięci (FETCH) - PC wskazuje, który rozkaz i pobieramy do procesora;

dekodowanie - co do zrobienia, skąd wziąć dane, gdzie przesłać wyniki;

liczenie adresu efektywnego, może być dostęp do pamięci albo układów I/O, powiązane z trybami adresowania procesora - sposób dostępu do danych (zasobów):

tryb rejestrowy - dane są w rejestrach ogólnego przeznaczenia, wynik może trafić do rejestru - b. szybki,

tryb rejestrowy pośredni - w rejestrze jest adres, spod którego trzeba pobrać dane, nie trzyma adresu wprost, wynik tak samo - adres, gdzie umieścić wynik,

tryb bezpośredni - adres podany po kodzie rozkazu, mamy dany adres efektywny, nie trzeba go liczyć, ale odwołujemy się do innych elementów systemu -> dłużej to trwa niż w trybie rejestrowym,

tryb natychmiastowy - dane zawarte wprost w rozkazie (dane szczątkowe)

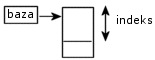

tryb bazowo-indeksowy - jest odmianą trybu rejestrowego pośredniego, przydaje się, gdy konstrukcje programistyczne są tak poukładane (np. tablica).

pobranie operandów (operands fetch);

wykonanie (execute);

przechowanie rezultatów (results store).

Ile czasu jest potrzebne na wykonanie rozkazu? Tam, gdzie jest kontakt z pamięcią, I/O - 3*T. W sumie około 14*T.

Jak to przyspieszyć?

S1 |

S2 |

S3 |

S4 |

S5 |

S6 |

S1 |

S2 |

S3 |

S4 |

S5 |

S6 |

rozkaz 1 |

rozkaz 2 |

||||||||||

|

|

S1 |

S2 |

S3 |

S4 |

S5 |

S6 |

3T |

|

S1 |

S2 |

S3 |

S4 |

S5 |

S6 |

|

3T |

|

S2 |

S3 |

S4 |

S5 |

S6 |

|

|

18T |

Wady - niektóre S trwają T, a inne 3T. Rozwiązanie - wszystko po 3T. Wada - wykonanie po 18T, ale za to kolejne rozkazy są wykonywane po 3T, a to już całkiem nieźle :)

Inny problem - PC jest tylko jeden, skąd wziąć kolejne?

Cyfrówka - wykład 2 (3. marzec 2003)

|

|

S1 |

S2 |

S3 |

S4 |

S5 |

S6 |

3T |

|

S1 |

S2 |

S3 |

S4 |

S5 |

S6 |

|

3T |

|

S2 |

S3 |

S4 |

S5 |

S6 |

|

|

18T |

Rozkaz następny - ten po bieżącym wykonywanym, wtedy 1 licznik PC wystarcza (jeśli program jest wykonywany liniowo). Jest to przetwarzanie potokowe.

Liniowość może być zachwiana - poprzez:

skoki:

bezwarunkowe - jeśli trzeba zmienić porządek programu, to to się stanie

warunkowe - zmiana porządku programu zależy od warunku (np. overflow)

wysyłanie procedur funkcji:

warunkowe (testowanie flag, znaczników).

Skoki - kiedy znamy nowe miejsce wykonania? 3. etap - liczenie adresu efektywnego, dla skoku warunkowego - w 5. etapie (wykonanie), najpierw testowanie warunków.

Jeśli wystąpi skok to procesor może:

przeczekać - dla skoku bezwarunkowego czekamy do S3, dla warunkowego do S5 (i tracimy takt procesora jeśli skoku nie ma);

nie martwię się - pobieramy dalsze rozkazy „bez zastanowienia”, bo dla >0,5 przypadków skoków nie ma, poza tym jak jednak będzie skok i kilka taktów pójdzie na marne to nic strasznego się nie stanie. Jednak w tym podejściu następuje przepływ bezużytecznych informacji;

ORMO czuwa :) - wymagana specjalna konstrukcja procesora, procesor wykonuje działania potokowe i jeszcze jak pozna miejsce nowego działania programu to buforuje te rozkazy bez przetwarzania ich. Jeśli skok się wykonał - to już mamy te rozkazy i je dekoduje, itd. - przyspieszone działanie.

Przetwarzanie potokowe - wiele kolejnych rozkazów realizowanych nie do końca równolegle („na zakładkę”).

SYSTEM PRZERWAŃ PROCESORA

System przerwań - „skrzynka pierwszej pomocy”. Zjawiska nieprzewidziane:

zagrożenie natury sprzętowej (awarie elementów);

zagrożenie programowe (np. dzielenie przez zero);

usługi dla użytkownika.

Jak sobie poradzić?

wyłączenie sprzętu, zapisanie danych

użytkownik zleca systemowi wykonanie czegoś.

„Recepty” - procedura, procesor porzuca to co robił i ją wykonuje:

napisana przez twórców, konstruktorów, nie można jej zmieniać;

napisana przez twórców, konstruktorów, można dołączyć własną (zmodyfikować);

miejsce puste, można stworzyć własny system przerwań.

Działanie systemu przerwań:

procesor sprawdza stabilność systemu przerwań po wykonaniu rozkazu (dość często),

urządzenie zgłasza usterkę, wtedy procesor reaguje;

zgłoszenie przerwania - procesory mają:

linie zgłoszenia przerwania (jest ich kilka): Int Req (interrupt request),

albo rejestry ze znacznikami, że są zgłoszone przerwania.

Kiedy jest przerwanie, to:

procesor sprawdza zgłoszenie przerwania;

wyłącznie systemu przerwań (opcjonalnie) - procesor przyjmuje jedno przerwanie do obsługi (i tylko 1), inne nie są realizowane - muszą poczekać. Jest to funkcja opcjonalna, ponieważ jeśli pojawi się sprawa poważniejsza to procesor się nią zajmuje;

zachowanie stanu procesora (zapamiętanie tego co się to tej pory działo):

przełączanie danych - istotne dane są w bezpiecznym miejscu (na stosie) - rejestry PC i inne ważne rejestry,

przełączanie kontekstu - jeśli procesor ma kilka zestawów rejestrów - wykorzystywany jest ten wolny (szybsze, nie ma transmisji danych).

Zachowanie stanu może być realizowane:

automatycznie - procesor bierze na siebie zachowanie danych;

programowo - programista musi zachować to co może być zniszczone, procesor nie wykona tego automatycznie

kombinowane - automatycznie: licznik rozkazów, rejestry specjalne; programista: rejestry wspólnego przeznaczenia.

4) identyfikacja przerwania - procesor uaktywnia linie odpowiedzi na przerwanie (Int Ack - interrupt acknowledge).

Do procesora:

numer przerwania (procesor prześle go magistralą danych),

adres przerwania.

ARBITRAŻ PRZERWAŃ (określa kolejność wykonywania przerwań).

sprzętowy

1. równoległy 2. szeregowy 3. równoległo - szeregowy

1. - wszystkie urządzenia są przypięte do dekodera przerwań, który ustala kolejność zgłoszenia przerwania do procesora. Numeracja wejść decyduje o priorytecie przerwań. Priorytet może być wędrujący - obsłużony idzie na koniec kolejki

2. - podaj dalej - urządzenia zgłaszające Int Req są łączone w jeden sygnał

3. - połączenie 1. i 2. - dekodery przerwań są przypięte w sposób szeregowy - rozwiązanie dobre dla wielu urządzeń.

programowy

skok do procedury obsługi przerwania,

powrót z obsługi przerwania - to co w 2) i 3), tylko w odwrotnej kolejności:

odtworzenie stanu procesora,

włączenie systemu przerwań.

SYSTEM PRZERWAŃ W 8051

5-6 źródeł przerwań:

2 zewnętrzne INT0, INT1 (linie typu Int Req),

2 od układów czasowo - licznikowych #0, #1,

1 przerwanie od portu szeregowego

szóste przerwanie od dodatkowego układu czasowo - licznikowego #2

przerwania mogą być maskowane (wyłączane) - w 8051 w sposób programowy (w 8-bitowym rejestrze IE)

|

EA |

- |

ET2 |

ES |

ET1 |

EX1 |

ET0 |

EX0 |

Nr bitu |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

EA - pozwala zamaskować wszystkie przerwania (1=wszystko włączone, 0=wszystko wyłączone)

ET2 - WŁ/WYŁ #2

ES - port szeregowy

ET1 - #1

EX1 - przerwania zewnętrzne zgłaszane linią INT1

ET0 - #0

EX0 - INTO

Cyfrówka - wykład 3 (10. marzec 2003)

Słowa sterujące i kontrolne SFR

Maska przerwań

Nr bitu (hex) |

AF |

AE |

AD |

AC |

AB |

AA |

A9 |

A8 |

|

EA |

- |

ET2 |

ES |

ET1 |

EX1 |

ET0 |

EX0 |

|

MSB |

|

|

|

|

|

|

LSB |

Przerwania od:

portu szeregowego - rejestr SCON (obsługuje port szeregowy), bity TI, RI (najmłodsze). TI - przerwanie od nadajnika - nadajnik wyśle i to sygnalizuje; RI - przerwanie od odbiornika (odebranie bajtu = zgłoszenie przerwania)

licznika #2 - w rejestrze T2CON (tylko dla 8051). TF2 - najstarszy - ślad o zgłoszeniu przerwania.

PRIORYTET PRZERWAŃ - dwuetapowy:

użytkownik może ustalić - definiuje programowo posługując się rejestrem IP:

- |

- |

PT2 |

PS |

PT1 |

PX1 |

PT0 |

PX0 |

MSB |

|

|

|

|

|

|

LSB |

PT2, PT1, PT0 - od układów czasowo - licznikowych

PS - od portu szeregowego

PX1 - priorytet przerwania zewnętrznego zgłaszanego linią INT1

PX0 - priorytet przerwania zewnętrznego zgłaszanego linią INT0

Dwa poziomy - wyższy i niższy. Użytkownik może ustawić priorytety dowolnie.

Przyjście przerwania o wyższym priorytecie powoduje przerwanie przerwania o niższym priorytecie :).

Przyjście przerwania o niższym priorytecie nie powoduje przerwania przerwania o wyższym priorytecie :)).

Jak przyjdą 2 przerwania o tym samym priorytecie, to wtedy obowiązuje następująca kolejność:

INT0#0

INT1

#1

PS

#2

Ta sekwencja jest niezmienna, spadek priorytetu uaktywnia się wtedy, gdy przychodzi kilka przerwań o tym samym priorytecie.

PROCEDURY OBSŁUGI PRZERWAŃ

Adresy stałe:

INT0 -> 3 hex

INT1 -> 13 hex

#0 -> B hex

#1 -> 1B hex

PS -> 23 hex

#2 -> 2B hex

Gdy był dostęp do rejestrów IE, IP to system nie sprawdza przerwań (dopiero po wykonaniu następnego rozkazu).

Gdy procesor wraca z procedury przerwania - odtwarza swój stan i powraca do wykonania programu zaleconego, wtedy też nie sprawdza przerwań - dopiero po wykonaniu następnej instrukcji w programie.

DMA - układ bezpośredniego dostępu do pamięci (Direct Memory Access)

Kiedy procesor za bardzo zajmuje się obsługą urządzeń WE/WY ,a nie programem, DMA ma odciążyć procesor, czyli pobiera od układu WEJ do pamięci i z pamięci do układu WYJ. Można też skopiować fragment pamięci z jednego miejsca w drugie.

Komunikacja za pomocą magistral -> procesor zarządza magistralami, ale DMA też potrzebuje do nich dostępu na poziomie procesora.

Zarządzanie magistralami - tryby pracy DMA:

blokowy

z wykradaniem taktów.

1. Tryb blokowy - jak DMA przejmie magistralę od procesora, to prowadzi transmisję od początku do końca - jest właścicielem magistrali na cały czas trwania transmisji.

DMA upora się tak szybko jak to możliwe - cenne, gdy układ WE przesyła dużo danych (np. skaner).

Procesor nie ma wtedy dostępu do magistrali - nie może pobierać argumentów, nie może wysyłać rezultatów, nie może pobrać następnego rozkazu, itp.

Wniosek - DMA działa sprawnie, procesor nie.

2. Tryb z wykradaniem taktów - właścicielem magistrali jest procesor, DMA dostaje magistralę tylko wtedy, gdy procesor jej nie potrzebuje.

Wniosek - DMA przesyła dane „kawałek po kawałku”, procesor działa bez zakłóceń.

To procesor programuje układy DMA.

Rejestry DMA:

adresowy - RA - procesor zapisuje początek adresu pamięci wykorzystywany przez DMA

licznika - RL - ilość słów, które DMA ma przyjąć albo wysłać, czyli system „początek i ile”

sterujący - RS - definiowane parametry transmisji: czy to odczyt, zapis czy kopiowanie pamięci

statusowy - RStat. - raport z działania DMA. Jeśli DMA zgłosi przerwanie - jak jest błąd lub problem, RStat. podpowie rodzaj błędu.

PROCESOR:

RD, WR (aktywne poziomem niskim) - linie odczytu i zapisu

MREQ, IOREQ - linie żądań dostępu do pamięci i układów WE/WY

BUSRQ - żądanie dostępu do magistrali

BUSACK - potwierdzenie zwolnienia magistrali

DMA:

Adres bo mamy magistralę, czyli = procesor

IOREQ bo układ wejściowy w trybie programowania

INT zgłoszenie przerwania do procesora

HOLDRQ - linie WYJ - chce się skontaktować z BUSACK

HOLDACK - kontakt z BUSACK

DMARQ - wejściowa linia

DMAACK - linia wyjściowa

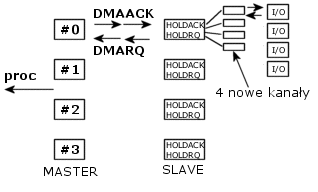

Przykład układu DMA - INTEL 8257 (8237A)

- ma 4 niezależne kanały DMA (możliwe są 4 transmisje przez kanały DMA),

- układ wyboru priorytetu (bo są 4 kanały): #0 ma najwyższy priorytet ↑↑ .......... #3 ↓↓; obsłużony na koniec kolejki,

- umożliwia hierarchiczne podłączanie kilku układów DMA,

- układ może pracować w trybie zgodnym z zapotrzebowaniem - np. w deklaracji transmisji „nie więcej niż...”

Cyfrówka - wykład 4 (17. marzec 2003)

Pamięci

Podstawowe parametry:

pojemność - ilość informacji cyfrowej jak może być zgromadzona

długość (szerokość) pamiętanego słowa. Organizacja struktury pamiętającej inf. - ilość bitów możliwych do obsłużenia naraz w procesie zapisu/odczytu. Ilość tych słów wyznacza pojemność

czas dostępu - czas od rozpoczęcia operacji do zakończenia (od odczytu pamięci do zapisania danych na magistrali danych).

Dodatkowe linie:

RAS ← (Row Address Select) - pomagają wybierać wiersz

CAS ← (Column Address Select) - pomagają wybierać kolumnę

Klasyfikacja pamięci:

ROM - Read Only Memory (tylko do odczytu)

RAM - Random Access Memory - dostęp swobodny (zapis/odczyt)

ROM:

Mask ROM

PROM

EPROM

EEPROM

EAPROM

Mask ROM - tylko do odczytu, w niej jest inf. o procesie produkcji, dostęp do inf. zaraz po włączeniu. Dane nie ulegają utracie po wyłączeniu zasilania, duża szybkość, niewielka pojemność

PROM - programowalna - sprzedawana jako czysta, programowanie tylko raz poza układem cyfrowym, w którym ma pracować, działa jak MaskROM, bardzo szybkie, niewielka pojemność

EPROM - Erasable Programmable ROM - możliwy zapis i kasowanie wielokrotne, zmiana struktury poza systemem, na drodze elektrycznej. Tranzystory z pływającą bramką, w stanie czystym same jedynki. Kasowanie - naświetlanie UV - zjawisko fotoelektryczne zewnętrzne w tranzystorach, kasowanie całości. Programowanie - setki/tysiące razy. Mogą mieć duże pojemności, nie są zbyt szybkie

EEPROM - elektrycznie kasowalne EPROMy, własności jak wyżej

EAPROM - możliwość wybiórczego kasowania i programowania, kasowanie elektryczne

RAM:

DRAM

SRAM

DRAM - elementy pamiętające - wartość ładunku na kondensatorach. Samo zasilanie nie wystarczy, kondensatory tracą ładunek - jest konieczne odświeżanie informacji, inaczej na kondensatorach mogą odłożyć się dowolne ładunki

SRAM - przerzutnik - element pamiętający - musi być utrzymana wartość logiczna ⇒ konieczne zasilanie

Odczyt i zapis

Odczyt z ROM (lub SRAM):

ustawienie adresu (odwołanie się do pamięci) - linie adresowe (np. A0 ... A14), ile linii - zależy od tego ile pamięci jest w systemie. Na podstawie adresu zostaną zaktywowane linie MREQ lub im odpowiadające

CE/ (Chip Enable) - linie wyboru określonego układu pamiętającego, aktywne stanem niskim

OE/ albo RD/ - Output Enable/Read - linie odczytu - ustawia akcję odczytu

to wszystko wysyłane do układu pamiętającego na linię adresową (np. D0 ... D7)

Zapis do SRAM

Wybór adresu i układu jak poprzednio, zmiana linii WRITE - dane z pamięci muszą być ustawione przed ustawieniem linii WRITE w stan aktywny (przez procesor lub układ DMA). Procesor lub DMA musi utrzymać dane przez czas wymagany dla pamięci, ale bez zwrotu informacji o tym, że zapis się udał czy nie.

Odczyt z DRAM:

Pojawiają się linie RAS i CAS

na magistrali adresowej jest podawany adres wiersza - jak się adres ustawi, to

linia RAS przechodzi w stan aktywny (poziom niski) - potwierdzenie, że na magistrali jest adres wiersza

na magistrali adresowej przełączanie adresu (stan niestabilny) - żeby pojawił się adres kolumny - linia CAS przechodzi w stan aktywny (poziomem niskim)

Po zakończeniu adresacji - wskazanie linii MREQ.

Gdy RAS i CAS są w stanie aktywnym, linia READ przechodzi w stan aktywny - zaczynamy realizować odczyt.

Na magistrali danych dane są odczytywane (pobierane).

Czas dostępu - od momentu rozpoczęcia adresacji do odczytu danych (tACC) - maksymalny. Można też wymyślać inne, ale po co . Koniec odczytu - linie RAS i CAS przechodzą w stan nieaktywny.

Zapis

Zmiany:

adres wiersza, aktywna linia RAS (do końca procesu zapisu)

adres kolumny, aktywna linia CAS (do końca procesu zapisu)

Ukształtowanie danych na magistrali danych, linia WR uaktywnia się.

Odświeżanie DRAM

w trybie skupionym. Dla każdego elementu odczyt i zapis. Tryb prosty, ale: fragment pamięci zawsze nieaktywny, mocne obciążenie dla systemu - ruch na magistrali, lepsze jest odświeżanie wyrywkowe (pojedynczych komórek), typy:

odświeżanie sygnałem RAS/ (RAS only refresh): - nie jest podawany adres kolumny, tylko adres wiersza. Jest specjalny licznik, który wybiera kolumny - i z tego licznika jest pobierana ta wartość (po upływie timeout-u) i ta komórkę odświeżamy (i tylko tą). Małe obciążenie dla procesora - adres wiersza i odświeżenie tylko jednej kolumny. Procesor musi sensownie wybierać adresy wiersza

odświeżanie ukryte. Odczyt/zapis kończy się kiedy linia RAS jest nieaktywna, ale CAS jest aktywna - mamy adres kolumny, potem RAS znowu aktywna, itd. Zaleta: odświeżanie wyrywkowe, przy okazji odczytu/zapisu, procesor raz podał adresy i sprawa załatwiona, adres sam się wygeneruje. Zawsze zdążymy z odświeżeniem, nic nie będzie pominięte

CAS/ przed RAS/ - najpierw w stan aktywny linia CAS, potem RAS, magistrala adresowa nie transportuje adresu, adresy wybierane z liczników. Na końcu odświeżania przechodzimy do normalnego zapisu/odczytu. Odświeżanie wybiórcze, minimalnie angażuje procesor (musi uaktywnić RAS i CAS, nic poza tym)

Odświeżanie automatyczne - układ pamięci odświeża się sam, procesor nie jest angażowany

Specjalne tryby pracy układów DRAM (kiedy chcemy zminimalizować czasy dostępu)

odczyt - modyfikacja - zapis. Zapis jest w to samo miejsce, co odczyt - jedna operacja, oszczędzamy na adresacji. Wstrzymanie pracy magistrali - np. DMA nie może pracować

tryb stronicowy - ograniczenie ilości adresowania. Adres wiersza jest stały, kolumny odczytywane z jednego wiersza (adres kolumny się zmienia)

tryb półbajtowy, RAS aktywna, CAS się zmienia (następne kolumny z tego samego wiersza)

Cyfrówka - wykład 5 (24. marzec 2003)

Tworzenie bloków pamięciowych

2 akcje:

- zwiększanie szerokości pamiętanego słowa (k-bloków o organizacji 2m słów*n, chcemy zrobić szerokość słowa n*k)

wszystkie układy jednocześnie włączone, chcemy odczyt/zapis w każdym z układów

- zwiększanie ilości pamiętanych słów. Linie danych - do każdego z układów pamiętających; linia adresowa - też, ale wyodrębnione (o adresach An ... An+1 - najstarsza część adresu) do dekodera. W danej chwili wybranie 1 układu pamiętającego odczyt/zapis też tylko w tym układzie; wiele układów odczyt/zapis taki jak w pojedynczym układzie

Współadresowanie i adresowanie izolowane pamięci i układów WE/WY

współadresowanie - z punktu widzenia procesora, pamięć + I/O to jeden blok - pamięć;

zalety:

- w liście programów danego procesora jest więcej instrukcji odnoszących się do pamięci niż do I/O ⇒ wygodna obsługa I/O

- zanika I/OREQ, MEMRQ - do zaadresowania wystarczą linie adresujące

wady:

- nie możemy użyć max. pamięci operacyjnej - ograniczona przestrzeń związana z pamięcią

- mała szansa reorganizacji

- wolniejszy dostęp (potencjalnie) do układów I/O

podsumowanie:

- układy dedykowane do obsługi określonego zadania (np. w silniku)

- dla komputera ogólnego przeznaczenia to nie ma sensu

adresowanie izolowane - 2 odrębne zasoby, bloki się nie nakładają, ale te same adresy odpowiadają MEM i I/O dla pewnego zakresu

wady:

- muszą być linie MEMRQ i I/ORQ - żeby rozgraniczyć

- dostęp do I/O jest nie zawsze wygodny

zalety:

- brak ograniczeń na ilość pamięci i adresów I/O

- brak problemów z rozbudową

podsumowanie:

- sprawdza się w komputerach ogólnego przeznaczenia, tak są zbudowane PC-ty

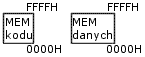

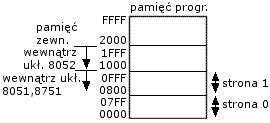

Konstrukcja pamięci w 8051

- architektura harwardzka - odseparowanie pamięci programu od pamięci danych:

MEM kodu - max. 64 kilobajty pamięci

+ pamięć zewnętrzna

+ pamięć wewnętrzna

Strony - po 2 kilobajty; odwoływanie do pamięci - PC. Pamięć kodu - adresowanie w sposób rejestrowy pośredni, rejestr pośredni - PC. MOVC - kontakt z pamięcią, zaczerpnięcie danych.

PC 16 bitowy, bity 11-15 (najstarsze) - wskazują stronę (blok 2-kilowy), bity 0-10 - adres.

Pamięć danych

- max. 64 kb

+ wewnętrzna - max. FF (245 bajtów) albo 128 bajtów

+ zewnętrzna - reszta

- odwołania

+R0 i R1 - odwołanie do pamięci danych - adresowanie rejestrowe pośrednie

MOV A,@R0 - pobranie do A z wewn. pamięci danych, zawartość R0 jest adresem wskazującym na wewn. pamięć danych

MOVX A,@R0 - pobranie do A z zewn. pamięci danych, tu 8 bitów nie wystarczy - potrzebny jest rejestr DPTR

DPTR - rejestr. pośrednie przez DPTR, np. MOVX A,@DPTR

- pamięć wewnętrzna:

+ adresy 0 do 31 - zestawy rejestrów od R0 do R7

+ od 32 do 47 - obszar adresowany bitowo

+ od 48 do 127 (7FH)

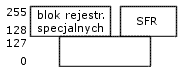

+ 80H (128) - 255 (FFH) - rejestry specjalnego przeznaczenia - blok SFR

Cała pamięć wewnętrzna może być adresowana w trybie bezpośrednim.

Stos znajduje się pod adresem 07 (po restarcie).

Podsumowanie: obszar pamięci użytkowej: od 0 do 127, rejestry specjalne: od 128 do 255

Dla procesorów 8052 - modyfikacja

SFR - rejestry specjalne, tryb adresowania bezpośredniego

Blok rejestrów specjalnych - pośredni tryb adresowania

Przyłączanie zewnętrznych pamięci

8 linii adresowych, 8 linii danych. Magistrala danych - linie portu od P00 do P07, linie te pełnią też rolę młodszej części magistrali adresowej (multipleksowana (przełączana) linią ALE).

Port 7: P3.7 - read, P3.6 - write. Wykorzystanie starszej części adresu. P2 - starsza część magistrali adresującej.

Przyłączanie zewnętrznej pamięci programu.

Linia PSEN (budowa - bramka AND razem z READ) - sygnalizuje dostęp do zew. pamięci programu. Można połączyć pamięć programu i danych

Pamięć podręczna - CACHE

Ma lepsze parametry niż zwykła pamięć, niewielka, zawarte są w niej instrukcje często potrzebne procesorowi.

Cechy:

+ współczynnik trafienia (hit ratio) - prawdopodobieństwo, że dana potrzebna procesorowi jest w pamięci cache

+ miss ratio - danej nie ma w cache

Które dane usunąć z cache? Algorytmy usuwania danych:

+ uwzględnianie informacji statusowej

- LRU (+)

- MIN (-)

+ bez uwzględniania informacji statusowej

- FIFO (+) (first in first out) - usunięta ta, która jest najdłużej pod względem czasu trwania

- RANDOM (+)

LRU - usuwa się daną, która najdłużej nie była w użyciu

MIN - usuwa tę, która najdłużej w przyszłości nie będzie potrzebna (bardzo fajnie, ale jak to zrobić?)

Cyfrówka - wykład 6 (31. marzec 2003)

Oprócz tych 4 mechanizmów, są jeszcze mechanizmy uaktualniania pamięci podstawowej:

+ każdy zapis do cache automatycznie do pamięci podstawowej - na wypadek awarii cache, ale spada prędkość działania cache => rzadko stosowane

+ dane do pamięci podstawowej - tylko wtedy, gdy mają być skasowane z cache - wydajniejszy sposób

+ kopiowanie danych przed usunięciem i jeszcze dodatkowo badani czy dane uległy zmianom

Organizacja pamięci cache

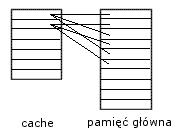

+ cache o bezpośrednim mapowaniu (direct mapping) - dane z pamięci głównej brane są z pewnym krokiem

ZALETA: oszczędność w czasie przeszukiwania pamięci cache

WADA: zapotrzebowanie procesora może być takie, że będzie potrzebował dużo danych z pamięci głównej, a cache jest mała => cache mało przyspiesza działanie procesora

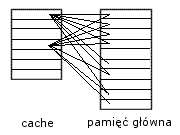

+ cache w pełni asocjacyjna - w danej komórce cache może być dana z dowolnego obszaru pamięci głównej, dane z każdej komórki pamięci podstawowej

ZALETA: unikamy poprzedniej wady, można odwzorować duży fragment pamięci głównej w cache

WADA: trudno znaleźć daną w pamięci głównej

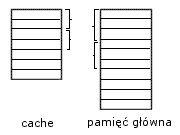

+ pamięć cache zbiorowo - asocjacyjna

Cache dzielone na mniejsze bloki, które są odpowiedzialne za bloki pamięci głównej. Obszary pamięci są ze sobą powiązane.

ZALETY:

- wstępne uporządkowanie

- dość duża elastyczność

Każde z tych 3 rozwiązań możemy spotkać - nie ma „lidera”

Zarządzanie pamięcią operacyjną

Pamięć główna:

- podrzędna - często tworzona też z innych urządzeń, np. fragmentów dysku

- nadrzędna - zawsze pozostaje pamięcią półprzewodnikową

Pamięć podrzędna - nie powinna być pamięcią, do której system często się odwołuje, raczej do składowania informacji

Pamięć nadrzędna jest dzielona na mniejsze struktury:

- stronicowanie - podział na bloki o jednakowej wielkości. Blok - najmniejsza jednostka jaka może być przydzielona np. programowi. Stronicowanie - wygodniejsze z punktu widzenia sterowania pamięcią, po zakończeniu np. programu nowa strona może zastąpić stare „cegiełki”. Wada - często zadanie nie potrzebuje całego bloku (np. tylko parę bitów)

- segmentacja - zmiana wielkości bloku. Po zakończeniu programu mogą zostać luki po przydzieleniu bloku innemu procesowi

Cechy pamięci:

+ protekcja (zabezpieczenie)

+ udostępnianie (współdzielenie)

Mechanizmy alokacji/relokacji stron (segmentów):

+ sposób statyczny - przydzielenie zasobów w momencie uruchomienia programu, później bez zmian aż do końca

+ dynamiczny - uruchomienie nowego programu powoduje przydzielenie zasobów, natomiast zakończenie programu powoduje analizę rozdzielenia stron/segmentów

Dla mechanizmu dynamicznego:

- lokalność danych:

+ czasowa - warto rozmieścić dane w pobliżu, ale działania na tych danych będą ustawiane w określonym porządku (np. dla pętli niekoniecznie po kolei w komórkach)

+ przestrzenna - warto, żeby dane znalazły się w kolejnych strukturach/komórkach pamięci, np. tablica

Zbiór pracujący - lokalność i czasowa i przestrzenna

Koprocesor arytmetyczny

Jest wyodrębnioną częścią procesora, nie jest w stanie pełnić funkcji procesora podstawowego.

Procesor jest odpowiedzialny za wykonanie programu, koprocesor śledzi wykonanie programu i pozostaje „w gotowości”. Koprocesor posiada własną listę rozkazów, niemożliwych do wykonania przez procesor podstawowy. Koprocesor „wkracza do akcji”, gdy procesor podstawowy napotyka rozkaz koprocesora.

Rozkaz jest pobierany do rejestru IR → dekodowanie rozkazu → wykrycie, że jest to rozkaz dla koproc. → „ciało” rozkazu przesłane do koproc. (do odpowiednika rejestru IR koproc.).

Koproc. jest pozbawiony możliwości:

- pobrania adresu czerpania danych, wysłania rezultatów (wyznaczenie adresu efektywnego)

- pobrania rozkazu.

Koproc. wywalcza dostęp do magistrali i pobiera argumenty rozkazów, które ma wykonać. Oba procesory „walczą” o magistralę - koproc. pracuje w trybie „wykradania taktów”.

Rejestr znaczników - 2 bity:

00 - liczba zwykła

01 - liczba zero

10 - zawartość specjalna

11 - rejestr „pusty”

Procesory mogą pracować na liczbach stałoprzecinkowych.

Formaty liczb stałoprzecinkowych:

słowowy całkowity (word integer) - U2, 16 bitów

krótki całkowity (short integer) - U2, 32 bity

długi całkowity (long integer) - U2, 64 bity

BCD upakowany (packed BCD) - 16 bitowy BCD. BCD - 18 cyfr+znak ⇒ zajętych 80 bitów (cały rejestr)

Formaty zmiennoprzecinkowe:

format krótki rzeczywisty (short real). 1 bit na znak, 8 bitów na część wykładniczą, 24 bity na cz. ułamkową

format długi rzeczywisty. 11 bitów na wykładnik, 53 bity na cz. ułamkową - lepsza precyzja

format rzeczywisty rozszerzony - 16 bitów na wykładnik, 64 bity na część ułamkową - maksymalne wykorzystanie 80 bitów

Formaty danych:

znak (0=+) S |

wykładnik E |

ułamek F |

Obiekt |

0 |

MAX |

≠0 |

Plus nieliczba (+NAN) |

0 |

MAX |

0 |

+∞ |

0 |

0<E<MAX |

≠0 |

Liczba dodatnia |

0 |

0 |

≠0 |

Liczba dodatnia w postaci nieznormalizowanej |

0 |

0 |

0 |

+0 |

1 |

0 |

0 |

-0 |

1 |

0 |

≠0 |

Liczba ujemna w postaci nieznormalizowanej |

1 |

0<E<MAX |

≠0 |

Liczba ujemna |

1 |

MAX |

0 |

-∞ |

1 |

MAX |

≠0 |

Minus nieliczba (-NAN) |

Ograniczanie precyzji:

IC (infinity control) - np. możemy ustawić tylko +∞ (-∞ nie ma)

PC (precision control):

00 24 bity

10 53 bity

11 64 bity

01 zarezerwowane

RC - zaokrąglanie:

00 - do liczby najbliższej

01 - w dół

10 - w górę

11 - w kierunku zera

Przyczyny przerwania:

PE - precission - utrata dokładności

UE - underflow - niedomiar

OE - overflow - nadmiar

ZE - zero divide

DE - denormalized operand - argument w postaci niunormowanej

IE - invalid operation - błędna operacja

Wszystkie przerwania mogą być maskowane (wyłączone) przez użytkownika

Lista rozkazów:

- przesłań (wymiany danych)

- arytmetyczne

- porównania i testowania

- wykonywanie funkcji przestępnych (new!)

- ładowanie stałych (new!)

- operacje sterujące

Cyfrówka - wykład 7 (7. kwiecień 2003)

Lista rozkazów koprocesora - uzupełnienie:

- rozkazy przesłań

- rozkazy arytmetyczne

- porównywanie i testowanie

- funkcje przestępne - gotowe rozkazy do wyznaczania wartości funkcji, np. trygonometrycznych:

FPTAN FPATAN F2XM1 (2x-1) FYL2X (ylog2x) FYL2XP1 (ylog2(x+1))

- ładowanie stałych - np. dla liczby Π - określona precyzja liczby, np.:

FLD2 (0) FLDPI (Π) FLDL2E (log2e) FLD1 (1) FLDL2T (log210)

- sterowanie

Układy I/O (WE/WY) procesora 8051

Port szeregowy - wprowadzenie i wyprowadzenie danych szeregowo w czasie - w kolejnych taktach zegara, kolejno „bit po bicie”. Co najmniej 3 przewody - we, wy, GND (masa)

bufor szyny danych - pośredniczy w wymianie danych (magazynowanie), zamiana postaci danych z równoległej na szeregową

bufor nadajnika - tu jest gromadzone słowo do wysłania i wysyłane bit po bicie przez linię TxD razem z informacją zabezpieczającą

sterowanie nadajnika - powoduje właściwą transmisję

TxC - przebieg taktujący pracę nadajnika

TxE i TxRDY - świadczą o gotowości nadajnika

TxE - Transmiter Empty - ustawia się później, gdy nadajnik skończy pracę

TxRDY - ustawia się wcześniej niż TxE

bufor odbiornika - RxD - dane odbierane poprzez bufor szyny danych do systemu

RxC - taktowanie, RxRDY - gotowość odbiornika, SYNDET - linia nadzorująca transmisję synchroniczną

Tryby pracy:

+ tryb asynchroniczny - nie oznacza braku sygnału taktującego (jest zegar)

+ tryb synchroniczny

Asynchroniczny:

- musi być to samo taktowanie,

- dane obudowywane ramką - wymagana taka sama budowa ramek w nadajniku i odbiorniku

bity startu |

|

(opcja) |

bity stopu |

1 |

dane |

|

1, 1 ½, 2 |

|

5,6,7,8 bitów |

bit parzystości |

|

Między grupami danych mogą wystąpić dowolnie długie przerwy.

Strona odbiorcza szuka bitów startu

Tryb synchroniczny

Zmienia się ramka, kształt umowny

słowo synchronizacji |

dane (słowo danych) |

część kontrolna |

Słowo synchronizacji - w odbiorniku i nadajniku musi być ustawione tak samo; jedno - monosynchron., dwa - bisynchron.

Wysłanie słowa, później sygnał, że słowo jest prawidłowo rozpoznane (zgłasza to SYNDET)

Dla trybu synchronicznego dalej są zaczepiane dane, część kontrolna, dane, cz. kontrolna itd.

Dla trybu bisynchronicznego: słowo synchron., dane, cz. kontrolna, słowo synchr.2, dane, cz. kontrolna, itd.

Przez cały czas transmisji danych linia SYNDET jest aktywna - dane przychodzą prawidłowo

Wielomiany - to, co wyjdzie przez dzielenie danych przez ten wielomian to część kontrolna

Np. CRC16 ma wielomian x16+x15+x2+1

W celu zawieszenia transmisji układ wysyła słowo synchronizacji

Port szeregowy w 8051

W 8051 mamy jeden port szeregowy obsługiwany 2 rejestrami:

- SCON - rejestr sterujący, opisuje warunki pracy portu szeregowego

- SBUF - rejestr danych

SCON:

9F |

9E |

9D |

9C |

9B |

9A |

99 |

98 |

SM0 |

SM1 |

SM2 |

REN |

TB8 |

RB8 |

TI |

RI |

MSB |

|

|

|

|

|

|

LSB |

SM0, SM1 - definiują tryb pracy portu:

SM0 SM1 = 00 - tryb zerowy transmisji, tryb synchroniczny, znaki 8-bitowe, taktowane fXTAL/12, bez części kontrolnej i słowa synchronizacji, prędkość wysyłania/odbioru danych = 1/12 taktu zegara

SM0 SM1 = 01 - tryb 1, asynchroniczny, znaki 8-bitowe, szybkość określona programowo (za szybkość odpowiada licznik T1), budowa ramki:

bit startu |

8 bitów danych |

bit stopu |

SM0 SM1 = 10 - tryb 2, asynchroniczny, znaki 9-bitowe, szybkość fXTAL/64 lub fXTAL/32, ramka:

|

|

TB8/RB8 ↓ |

|

bit startu |

8 bitów danych |

|

bit stopu |

|

|

↓ RB8 |

|

Bity TB8/RB8 to 9. bit danych, który można ustawić jako bit parzystości

SM0 SM1 = 11 - tryb 3, asynchroniczny, znaki 9-bitowe, licznik T1 określa prędkość transmisji

Bit SM2 - bit sterujący - akceptacja danych z potencjalnym błędem (ustawiony na 1):

- jeśli RB8=0 to ramki odrzucane (SM2=0)

- jeśli SM2=1 - ramki akceptowane, nawet jeśli RB8=0

REN - programowe wł/wył odbiornika

Układ czasowo - licznikowy

Odmierzanie określonego odcinka czasu i sygnalizacja o tym, niezależnie od obciążenia procesora

- rejestr słowa sterującego - tu są wpisywane słowa określające zachowania układu

- CLK - wejście sygnału zegarowego

- GATE - sygnalizacja upływu czasu te linie pozwalają na programowe sterowanie pracą licznika

- OUT

Liczniki są negatywne - zliczają „w dół” - zmniejszają swój stan o 1

2 tryby: - liczniki binarne

- liczniki dziesiętne (w kodzie BCD)

Stałe definiujące prace liczników są 16-bitowe

Mamy 6 trybów pracy liczników

Cyfrówka - wykład 8 (14. kwiecień 2003)

Tryby pracy liczników

Tryb 0

+ akcja jednokrotna

+ podanie nowej stałej nie powoduje zmiany w procesie odliczania (chyba, że linia GATE się zmieni z 0 na 1)

+ przerwanie po procesie odliczania

+ linia GATE może wstrzymać odliczanie na pewien czas

Tryb 1

+ układ do generowania impulsu o określonej szerokości

+ zapisanie stałej nie powoduje automatycznego włączenia

+ włączenie powoduje przejście linii GATE z 0 na 1, wtedy na OUT pojawia się 0, co inicjuje proces zliczania

+ pod koniec linia OUT =>1 i tak pozostaje

+ tryb jednokrotny

+ linia GATE z 1 na 0 - nic się nie dzieje, z 0 na 1 (powrót) - reset licznika

+ podanie nowej stałej nie powoduje zmiany w procesie odliczania (chyba, że linia GATE się zmieni z 0 na 1)

Tryb 2 (dzielnik częstotliwości)

+ wpisujemy stała, rusz odliczanie (niezależnie od linii GATE). Po zakończeniu zliczania, na OUT jest 0

+ repetycja - stan 0 na OUT na 1 impuls CLK. Opisanie nowej stałej - reakcja od nowego cyklu odliczania

+ w trakcie pracy - GATE z 1 na 0 - wstrzymanie (OUT ⇒ 1), zawieszenie aż GATE ⇒ 1, wtedy wznowienie od bieżącej wartości stałej

Tryb 3 (generator fali prostokątnej - autorepetycja)

+ na podstawie sygnału na WE (CLK) jest generowany przebieg prostokątny o innej częstotliwości. Wartość stałej/2 powoduje wyznaczenie nowego przebiegu. Jeśli stała jest nieparzysta - zero trwa krócej, 1 jest o jednostkę dłuższa

+ linia GATE nie wpływa na pracę

Tryb 4 (generowanie pojedynczego impulsu strobującego)

+ odliczanie do 0 - na jeden takt - koniec

+ linia GATE jest niepotrzebna, tryb rusza po wpisaniu stałej

+ linia GATE może ingerować (jeśli zmieni się na 0) - wstrzymanie odliczania. GATE ⇒ 1 - wznowienie odliczania

+ tryb jednokrotny, bez repetycji

Tryb 5 (modyfikacja trybu 4 - inaczej się uruchamia)

+ GATE potrzebna do uruchomienia procesu (z 0 na 1)

+ jeśli GATE później przechodzi z 0 na 1 - reset

Układy czasowo - licznikowe w 8051

1

17

PC

?

?

PC

Wyszukiwarka