Ćwiczenie 10

PODSTAWOWE BRAMKI LOGICZNE

10.1. WSTĘP

Tematem ćwiczenia są podstawowe właściwości elementarnych bramek logicznych TTL i ECL. Układ badany umożliwia określenie tablic stanów logicznych dwuwejściowych bramek NAND i NOR, obserwacje statycznych charakterystyk przejściowych uwy (uwe) podstawowej bramki TTL, bramki z otwartym kolektorem oraz bramki z histerezą (tzw. Schmitt NAND), a także obserwacje przebiegów czasowych na wyjściu bramek NAND i NOR sterowanych impulsowo. Końcowa faza ćwiczenia polega na obliczeniu i zmierzeniu poziomów napięciowych w węzłach dyskretnego układu bramki typu ECL, odpowiadającym scalonym bramkom podstawowym z serii MECL 10000.

Celem ćwiczenia jest zilustrowanie zasad działania, budowy i właściwości podstawowych funktorów logicznych wykonywanych w najbardziej rozpowszechnionych technikach realizacji.

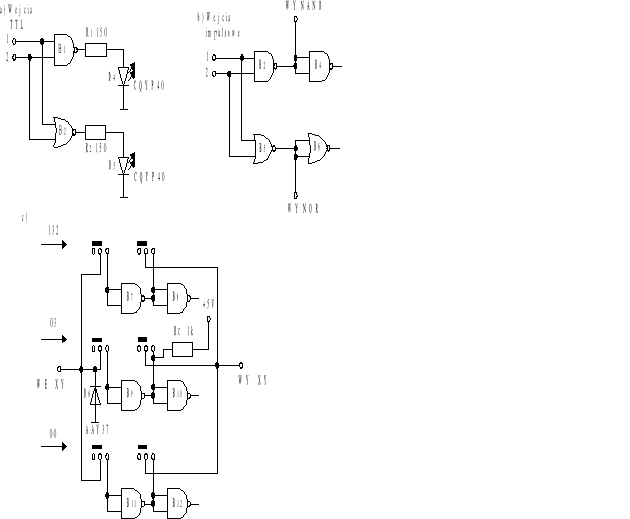

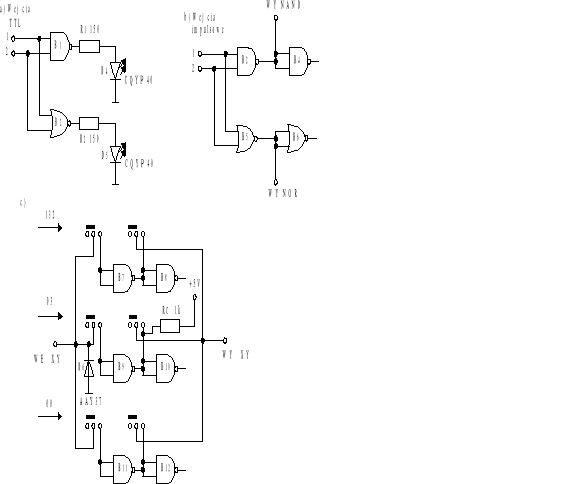

Rys.10.1. Schemat wkładki DN101A

10.2. OPIS TECHNICZNY UKŁADU BADANEGO

(WKŁADKA DN101A)

Wkładka DN101A zawiera kilka niezależnych układów, badanych w poszczególnych eksperymentach. Układ przedstawiony na rys.10.1a służy do określania tablicy stanów bramek NAND i NOR. Wskaźnikiem stanu wysokiego są diody świecące o barwie czerwonej, umieszczone na płytce drukowanej w pobliżu odpowiedniego układu scalonego.

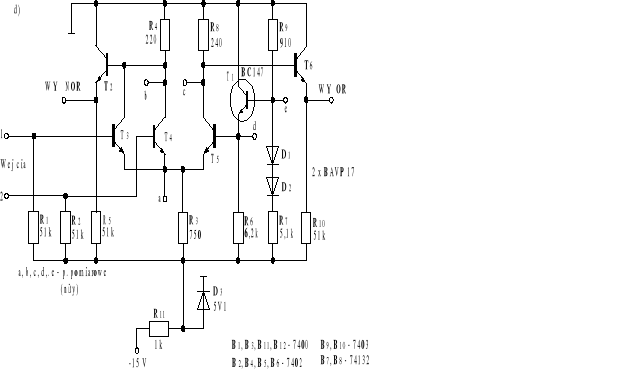

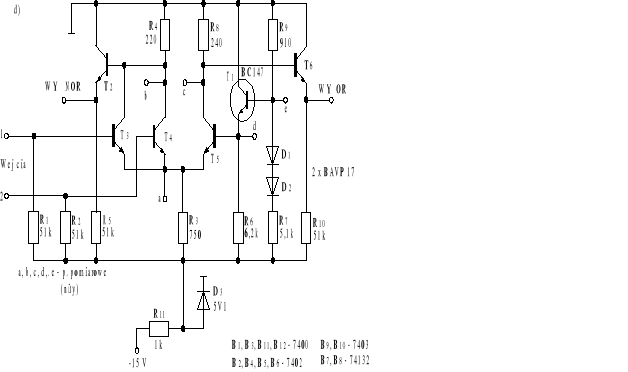

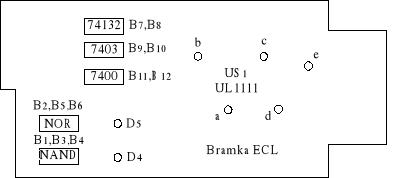

Obserwacje przebiegów czasowych na wyjściach bramek NAND i NOR, sterowanych przebiegami impulsowymi, przeprowadza się w układzie pokazanym na rys.10.1.b. Bramki B4 i B6 stanowią obciążenie bramek badanych B2 i B5. Na rys.10.1.c przedstawiono schemat układu, w którym dokonuje się obserwacji charakterystyk przejściowych trzech rodzajów bramek TTL. Do wyboru jednej z badanych bramek - standardowej 7400, z otwartym kolektorem 7403 lub z charakterystyką histerezową 74132 - służy przełącznik klawiszowy. Schemat dyskretnego modelu typowej bramki NOR / OR z serii MECL 10000 przedstawia rys.10.1.d. Model ten zbudowany jest przy użyciu pięciu tranzystorów scalonych układu UL1111 oraz jednego tranzystora dyskretnego. Rezystory R5 i R10 nie występują w schemacie oryginalnym; tu reprezentują rezystancję wejściową bramki obciążającej. Literami a - e oznaczono na schemacie punkty pomiarowe (nity) dostępne na płytce drukowanej. Dioda D3 i rezystor R11 tworzą układ zasilania bramki napięciem ok. -5V.

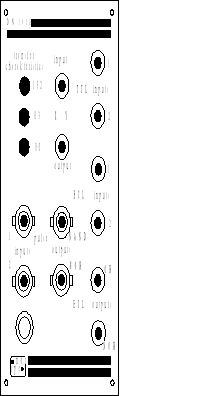

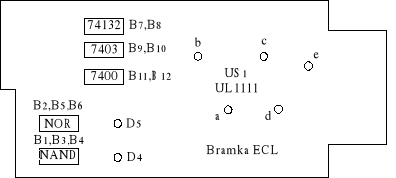

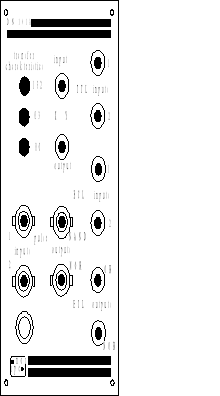

Płytę czołową układu badanego przedstawiono na rys.10.2, punkty pomiarowe - na rys.10.3.

Rys.10.2. Płyta czołowa układu badanego DN101A

Rys.10.3. Schemat rozmieszczenia punktów pomiarowych na płycie wkładki DN101A

10.3. WYKAZ APARATURY POMOCNICZEJ

Do wykonania ćwiczenia potrzebne są następujące przyrządy pomocnicze:

- generator stanów logicznych dwuwyjściowy SN1211,

- translator stanów logicznych TTL - ECL SN9211,

- wkładka charakterograficzna dwukanałowa SN7212,

- podwójny generator impulsów TTL SN3212,

- sonda.

10.4. ZAGADNIENIA WSTĘPNE I PROJEKTOWE

Określić i narysować charakterystykę przejściową bramki TTL z otwartym kolektorem dołączonym do napięcia +5 V.

Na podstawie schematu bramki typu Schmitta (132), obliczyć napięcia progowe pętli histerezy.

Obliczyć wartości napięć we wszystkich węzłach układu bramki ECL - rys.10.1.d - dla obu stanów logicznych. Założyć liniowo - odcinkowy model tranzystora (UBEP = 0,7 V)oraz przyjąć, że bramka pracuje w kaskadzie identycznych bramek.

Opracować schematy pomiarowe do punktu 10.5.

Należy pamiętać o wyzwalaniu podstawy czasu oscyloskopu zewnętrznym przebiegiem synchronizującym (p.10.5.1). Opracowane schematy powinny być narysowane w protokole przed rozpoczęciem ćwiczenia.

10.5. OBSERWACJE I POMIARY

10.5.1. Obserwacja przebiegów czasowych na wyjściu bramek NAND i NOR

sterowanych impulsowo

Wykorzystując różne kombinacje sygnałów impulsowych, jakie można uzyskać z podwójnego generatora impulsów TTL SN3212, zrealizować za pomocą bramki NOR lub NAND kilka przebiegów czasowych różnych od podawanych na wejście (np. dwa kolejne impulsy o takim samym lub różnym czasie trwania, pojedynczy impuls krótszy od któregokolwiek z wejściowych o dowolnej polaryzacji itd.). Uzyskane przebiegi przerysować do protokołu łącznie z przebiegami wejściowymi.

Zagadnienia:

wykazać związek uzyskanych przebiegów z tablicą stanów funkcji, NOR lub NAND, np. przez opisanie stanów wejść i wyjścia bramki na narysowanych przebiegach w poszczególnych odcinkach czasu;

podać, w jaki sposób proste bramki logiczne mogą być wykorzystywane do kształtowania przebiegów impulsowych lub selekcji czasowej impulsów. Narysować przykłady schematów takich układów.

10.5.2. Obserwacja charakterystyk przejściowych bramek TTL

Obejrzeć na ekranie oscyloskopu i przerysować do protokołu charakterystyki przejściowe bramek logicznych TTL typu 7400, 7403 i 74132. Na podstawie dokonanych rysunków oszacować amplitudy logiczne oraz marginesy szumowe w obu stanach. Obserwacji charakterystyk należy dokonać za pomocą wkładki charakterograficznej SN7212.

Zagadnienia:

z czego wynika in w jaki sposób drogą modyfikacji schematu może być usunięte obcięcie rogu charakterystyki przejściowej, występujące w bramce 7400. Na jakie parametry robocze ma wpływ to obcięcie?

z czego wynika wartość napięcia progowego bramki TTL?

narysować charakterystykę przejściową bramki z otwartym kolektorem bez rezystora RC oraz z rezystorem RC dołączonym do napięcia +15 V (należy przy tym pamiętać o wpływie bramki obciążającej);

porównać obliczone i zmierzone wartości napięć progowych pętli histerezy bramki 132; skomentować to porównanie.

10.5.3. Analiza stałoprądowa bramki ECL w obu stanach logicznych

Zmierzyć napięcia stałe na wejściach, wyjściach i w pozostałych punktach pomiarowych (nity) układu bramki ECL w obu stanach logicznych. Wejścia bramki należy wysterować odpowiednimi poziomami logicznymi, korzystając z generatora stanów logicznych SN1211 oraz translatora stanów logicznych TTL - ECL (wkładka SN9211). Na podstawie dokonanych pomiarów obliczyć wszystkie prądy gałęziowe i moc pobieraną przez bramkę w obu stanach logicznych.

Zagadnienia:

jak można uzasadnić przyjęcie w technice ECL wartości amplitudy logicznej około 0,8 V?

jaki jest główny powód zastosowania wtórników T2, T6?

dlaczego bramki ECL zasilane są zwykle z napięcia ujemnego, przy dołączonych do masy rezystorach kolektorowych R4, R8?

dlaczego w bramkach ECL zastosowano stosunkowo złożony układ napięcia odniesienia (T1, D1, D2, R6, R7, R9)? Czy układ ten mógłby być zastąpiony dzielnikiem oporowym?

10.5.4. Obserwacja charakterystyk przejściowych bramki ECL

Obejrzeć na ekranie oscyloskopu i przerysować do protokołu obie (na wyjściu OR i NOR) charakterystyki przejściowe bramki ECL. Obserwacji dokonać za pomocą wkładki charakterograficznej SN7212.

Zagadnienia:

uzasadnić kształt obu charakterystyk, korzystając ze schematu ideowego bramki;

określić amplitudę logiczną oraz marginesy szumowe bramek ECL;

uzasadnić różnicę wartości rezystorów kolektorowych R4, R8.

10.6. LITERATURA

[1] R.23 (23.3, 23.4)

[2] R.12

[8] R.4

[9] R.7

[12] R.4 (zad 4.3, zad 4.6)

[13] R.4 (4.1)

[14] R.2, R.3 (3.1, 3.2, 3.3, 3.4), R.4 (4.1, 4.2)

Wyszukiwarka

Podobne podstrony:

SYNTEZEAUTOMATU, ☆☆♠ Nauka dla Wszystkich Prawdziwych ∑ ξ ζ ω ∏ √¼½¾haslo nauka, Logika, układy LOGI

ZADANIE 81, ☆☆♠ Nauka dla Wszystkich Prawdziwych ∑ ξ ζ ω ∏ √¼½¾haslo nauka, Podstawy konstrukcji mas

pb temat, ☆☆♠ Nauka dla Wszystkich Prawdziwych ∑ ξ ζ ω ∏ √¼½¾haslo nauka, budownictwo, Podstawy budo

Wymiary kotła, ☆☆♠ Nauka dla Wszystkich Prawdziwych ∑ ξ ζ ω ∏ √¼½¾haslo nauka, budownictwo, Podstawy

pb karta, ☆☆♠ Nauka dla Wszystkich Prawdziwych ∑ ξ ζ ω ∏ √¼½¾haslo nauka, budownictwo, Podstawy budo

projekt domu jednorodzinnego, ☆☆♠ Nauka dla Wszystkich Prawdziwych ∑ ξ ζ ω ∏ √¼½¾haslo nauka, budown

spr 2 - wizualizacja, ☆☆♠ Nauka dla Wszystkich Prawdziwych ∑ ξ ζ ω ∏ √¼½¾haslo nauka, mechanika płyn

!Spis, ☆☆♠ Nauka dla Wszystkich Prawdziwych ∑ ξ ζ ω ∏ √¼½¾haslo nauka, hacking, Hack war, cz II

TEST3(BONUS), ☆☆♠ Nauka dla Wszystkich Prawdziwych ∑ ξ ζ ω ∏ √¼½¾haslo nauka, Matematyka statystyka

Akumulatory, ☆☆♠ Nauka dla Wszystkich Prawdziwych ∑ ξ ζ ω ∏ √¼½¾haslo nauka, Elektronika

odlew i spaw wyk, ☆☆♠ Nauka dla Wszystkich Prawdziwych ∑ ξ ζ ω ∏ √¼½¾haslo nauka, Spawalnictwo i Od

B, ☆☆♠ Nauka dla Wszystkich Prawdziwych ∑ ξ ζ ω ∏ √¼½¾haslo nauka, hacking, Hack war, cz I

D, ☆☆♠ Nauka dla Wszystkich Prawdziwych ∑ ξ ζ ω ∏ √¼½¾haslo nauka, hacking, Hack war, cz I

dodatek A, ☆☆♠ Nauka dla Wszystkich Prawdziwych ∑ ξ ζ ω ∏ √¼½¾haslo nauka, hacking, Hack war, cz II

Skorowidz, ☆☆♠ Nauka dla Wszystkich Prawdziwych ∑ ξ ζ ω ∏ √¼½¾haslo nauka, hacking, Hack war, cz I

Spis tre ci, ☆☆♠ Nauka dla Wszystkich Prawdziwych ∑ ξ ζ ω ∏ √¼½¾haslo nauka, hacking, Hack war, cz I

1Wyznaczanie krytycznej liczby Reynoldsa, ☆☆♠ Nauka dla Wszystkich Prawdziwych ∑ ξ ζ ω ∏ √¼½¾haslo n

więcej podobnych podstron