ZAGADNIENIA EGZAMINACYJNE Z PRZEDMIOTU

„ARCHITEKTURA SYSTEMÓW KOMPUTEROWYCH”

1. Przekształć, dla podanego przykładu kod NKB w kod Gray`a.

KOD NKB GRAYA

0000=0

0001=1

0010=2

0011=3

0100=4

0101=5

0110=6

0111=7

1000=8

2. Zapisz podaną liczbę w systemie:

* znak-moduł,

8=1000=0(ZM)

4=0100=(-1)0+(2) 2=4(ZM)

6=0110=(-1) 0+(2)2+(2)1=6(ZM)

10=1010=(-1)1+(2)2=-4(ZM)

12=1101=(-1)1+(2)2 +(2)1=-5(ZM)

15=1111=(-1)1+(2)2+(2)1+(2)0=-7(ZM)

0=0000=0(ZM)

* U1, (NORMALNIE ZAPISUJEMY JAK W NKB A ŻEBY OTRZYMAC Z MINUSEM NEGUJEMY WSZYSTKIE BITY)

1=0001(U1)

-1=1110(U1)

5=0101(U1)

-5=1010(U1)

7=0111(U1)

-7=1000(U1)

Liczba (-113) jest ujemna. Jej moduł wynosi 113. Wyznaczamy zapis dwójkowy modułu:

113(10) = 1110001(2)

Otrzymany zapis uzupełniamy bitami 0 do długości 8 bitów. Następnie negujemy wszystkie bity i otrzymujemy w ten sposób zapis U1 liczby -113:

-113(10) = NOT 01110001 = 10001110(U1).

Wyznaczyć 8-mio bitowy zapis U1 liczby dziesiętnej 76.

Liczba 76 jest dodatnia, zatem wyznaczamy jej zapis w naturalnych systemie dwójkowym:

76(10) = 1001100(2)

Otrzymaną liczbę dwójkową uzupełniamy bitami o wartości 0 do długości formatu otrzymując:

76(10) = 01001100(U1).

* U2.

Wyznaczyć 8-mio bitowy kod U2 dla liczby dziesiętnej 27(10).

27(10) = 16 + 8 + 2 + 1 = 11011(2) = 00011011(U2).

Wyznaczyć 8-mio bitowy kod U2 dla liczby dziesiętnej (-45)(10).

28 + (-45) = 256 - 45 = 211 = 11010011(2).

Stąd (-45)(10) = 11010011(U2).

Przykład z wykładów.

57=111001 = 0111001 - KOD NKB

-57 1111001 - ZNAK-MODUŁ JEŻELI LICZBA Z DODAJEMY 1

= 1000110 - U1 NEGACJA BITOW I DOPISANIE 1

+1

1000111 - U2 NEGACJA BITOW I DODANIE 1

0,1 - BIT ZNAKU

3. Wykonaj odejmowanie dwóch liczb całkowitych zapisanych

w kodzie U2.

3 + 3

0011

+ 0011

0110

6 |

|

5 + (-4)

0101

+ 1100

1 0001

1 |

|

(-3) + (-2)

1101

+ 1110

1 1011

(-5) |

|

5 - 4

0101

- 0100

0001

1 |

|

(-2) - 3

1110

- 0011

1011

(-5) |

|

(-7) - (-6)

1001

- 1010

1 1111

(-1) |

4. Przedstaw w systemie dwójkowym określoną liczbę rzeczywistą

- dodatnią i ujemną.

Np. 20

20:2 = 10 reszta 0

10:2= 5 reszta 0

5:2=2 reszta 1

2:2=1 reszta 0

1:2=0 reszta -1 (1)

Odczytujemy z reszty czytając od dolu

20(10)=10100(2)

5.

6. Przedstaw na wykresie przebieg wszystkich sygnałów dowolnego

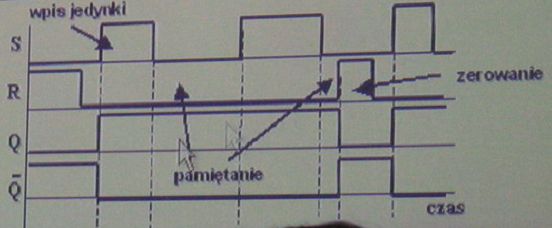

przerzutnika synchronicznego i asynchronicznego.

Asynchroniczny przerzutnik RS

Synchroniczny przerzutnik RS

7. Wymień podstawowe elementy jednostki wykonawczej i sterującej

procesora oraz scharakteryzuj ich funkcje.

Jednostka wykonawcza

- Zadaniem jednostki wykonawczej jest wykonywanie operacji arytmetycznych i logicznych w zależności od wewnętrznych sygnałów sterujących.

- Składa się z rejestru części wykonawczej oraz z bloku arytmetyczno-logicznego (ALU)

ALU - uniwersalny układ kombinacyjny, który realizuje operacje matematyczne i logiczne w zależności od zaprogramowanej operacji -> rozkazy umieszczonego w programie

Rejestr części wykonawczej - (tu moje wypociny) zbiór rejestrów ogólnego przeznaczenia, segmentowych, wskaźnikowych i indeksowych, które są potrzebne zarówno dla ALU jak i dla Układu Sterowania znajdującego się w jednostce sterującej procesora.

Jednostka sterująca po pobraniu z pamięci kodu rozkazu dekoduje ten rozkaz i na jego podstawie generowane są wewnętrzne i zewnętrzne sygnały sterujące. Jednostka sterująca składa się z:

Rejestru rozkazów - (moje domysły) w rejestrach tych są przechowywane rozkazy bądź adresy rozkazów

Dekodera rozkazów - (moje domysły) tutaj rozkaz zostaje zdekodowany, czyli przetłumaczony dla układu sterowania.

Układ sterowania - złożony automat sekwencyjny, generujący odpowiednie ciągi słów podawanych na wejścia sterujące układu ALU. Cechy:

- konieczność posiadania dużej liczby stanów dostosowanych do wymaganej liczby wykonywanych rozkazów

- konieczność zapewnienia synchronizacji pracy układu sterowania i wykonawczego

Układy sterowania są to w praktyce generatory sekwencyjne oraz układy mikroprocesorowe.

8. Scharakteryzuj rejestry procesora - rodzaje i przeznaczenie.

Rejestry procesora dzielą się na:

- Rejestry powszechnego stosowania - przeznaczone do przechowywania dowolnych danych i wykonywania operacji (arytmetycznych i logicznych). Rodzaje:

- AX - akumulator

- BX - rejestr bazowy

- CX - licznik odliczający rozkazy

- DX - wskaźnik adresów w rozkazach wej/wyj

- Rejestry segmentowe - zbiór wskaźników do miejsc , w których znajduje się dany rozkaz, argument, rej. te są użyteczne przy obsłudze stosów. Rodzaje:

- Rejestr CS - wskazanie bloku pamięci, w którym znajduje się kolejny do wykonania rozkaz

- Rejestr DS. - wskazuje argumenty

- Rejestr ES - stosowany do różnych pojawiających się otrzeb

- Rejestr SS - obsługa stosów

- Rejestry wskaźnikowe i indeksowe - główne zastosowanie to wskazywanie obszarów pamięci. Rodzaje:

- SI - rejestr indeksowy źródła

- DI - rejestr indeksowy przeznaczenia

- BP - wskaźnik bazy

- SP - wskaźnik stosu

9. Dla rozkazu dodawania dwóch argumentów(wykluczając tryb

adresowania natychmiastowego) opisz wszystkie fazy

wykonywania rozkazu i zmiany zachodzące w rejestrach, pamięci

oraz szynach danych i adresowych.

10. Przedstaw model pamięci RAM (4x4) z jednym i dwoma wejściami wybierającymi. Opisz wady i zalety obu rozwiązań

11. Opisz proces bezpośredniego sterowania przez procesor

operacjami wej-wyj z jednoczesnym przerwaniem programu

głównego. Scharakteryzuj przeznaczenie i funkcje Stosu

Procesor wykonuje program główny oczekując na zgłoszenie gotowości. Zgłoszenie powoduje przerwanie wykonywania programu głównego i zapamiętanie informacji potrzebnej do późniejszego powrotu. Procesor przechodzi do wykonana programu obsługi przerwań (ISR) - wymiana info z układem I/O, po zakończeniu wymiany procesor kontynuuje program główny.

W przypadku pojawienia się jednocześnie kilku zgłoszeń stosuje się sterownik przerwań. Jego zadania to:

- pośredniczenie w przyjmowaniu zgłoszeń przerwań pomiędzy procesorem i układami I/O

- przyjmowanie zgłoszeń od wielu układów I/O (procesor ma tylko 1 wejscie zgłoszeń przerwań)

- sygnalizowanie wyboru przez podanie adresu układu I/O, z którym zostanie dokonana wymiana, czyli adres programu obsługi przerwania realizującego tę wymianę, a właściwie numer pozycji w tablicy wektorów przerwań

- wygenerowanie sygnału zgłoszeń przerwania bezpośrednio do mikroprocesora

Stos jest to wyróżniony obszar w pamięci używany według reguł:

- informacje zapisywane są na stos do kolejnych komórek (pod kolejnymi adresami), żadnego adresu nie wolno pominąć

- odczyt w kolejności odwrotnej do zapisu

- informacje odczytujemy z ostatnio zapełnionej komórki a zapisujemy do pierwszej wolnej.

Reguła LIFO - Last-in-first-output -> ostatni wchodzi pierwszy wychodzi

12. Przyjmując, że w procesorze X bitowym mamy:

* rejestry X bitowe,

* magistrale danych Y bitowe,

* szynę adresową Z bitową

Wyjaśnij jakie relacje powinny zachodzić ww, wielkościami, żeby procesor pracował efektywnie.

13. Opisz istotę pamięci wirtualnej. Przedstaw mechanizm

tłumaczenia adresu wirtualnego na rzeczywisty.

Adres rzeczywisty sklada sie z CS i TP(czesc segmentowej i wskaznikowej). Adres wirtualny jest podobny do rzeczywistego, tylko czesc segmentowa ma wieksza zawartosc; jest dluzszy od rzeczywistego. W adresie wirtualnym czesc segmentowa zawiera odwolanie do tabeli deskryptorow, gdzie opisywane sa bloki, ktore musza sie znalezc w pamieci .Sa one sciagane i przetlumaczane z wirtualnego na fizyczny.

14. Scharakteryzuj architekturę i funkcjonowanie pamięci

CACHE drugiego poziomu. Czy cała zawartość pamięci

operacyjnej może być ładowana do pamięci CACHE?

Uzasadnij każdą z odpowiedzi.

System pamięci kieszeniowej cache składa się z trzech zasadniczych elementów:

- banku danych pamięci cache (pamięci danych) przeznaczonego do przechowywania zapisywanej i odczytywanej informacji,

- katalogu pamięci cache (tzw. TAG-RAM) służącego do szybkiego sprawdzania, czy poszukiwana informacja znajduje się w pamięci danych,

- sterownika pamięci cache, którego zadaniem jest zapewnienie współpracy pamięci kieszeniowej z systemem, a przede wszystkim zapewnienie zgodności zawartości pamięci cache z pamięcią główną.

Pamięci typu CACHE są wyspecjalizowanymi pamięciami współpracującymi z pamięcią operacyjną i procesorem. Służą one buforowaniu generowanych z procesora instrukcji i optymalizacji wykonywania zadań. Jest to pamięć o najszybszym dostępie, ale o najmniejszej pojemności.

W celu zapewnienia możliwości szybkiego sprawdzenia, czy komórka pamięci, na której ma być wykonana operacja, jest odwzorowana w pamięci cache, bank danych i katalog, tworzą tzw. jednoblokową pamięć asocjacyjną.

Pamięć cache stanowi jeden blok, który jest dzielony na zestawy. Pamięć główna dzielona jest na strony o rozmiarze równym rozmiarowi bloku pamięci cache. Strony są z kolei również dzielone na zestawy, przy czym ilość zestawów w stronie jest identyczna jak w bloku pamięci cache. Każdy zestaw w pamięci cache ma swoją pozycję w katalogu TAG-RAM. Zawiera ona adres strony z którego pochodzi dany zestaw. Każdy zestaw jest wpisywany na miejsce w pamięci cache do zestawu o numerze zgodnym z numerem zestawu na stronie. Umożliwia to szybkie sprawdzenie obecności zestawu poprzez sprawdzenie adresu bloku w określonej pozycji katalogu.

W architekturze Look-aside, w przeciwieństwie do architektury Look-through, procesor nie jest odizolowany od reszty układów. Dostęp do pamięci cache oraz pamięci głównej realizowany jest poprzez magistralę główną co powoduje, że nawet w przypadku trafienia magistrala jest niedostępna dla innych zarządców. Niewątpliwą jednak zaletą tej architektury jest prostsza konstrukcja, niższy koszt i nieco szybsza realizacja operacji w przypadku chybienia.

to nie można zawartości całej pamięci operacyjnej załadować do pamięci podręcznej, ponieważ zwyczajnie by się nie zmieściła - pamięć operacyjna jest z reguły znacznie pojemniejsza od podręcznej.

Zaletą pamięci podręcznej jest to, że jest bez porównania szybsza od pamięci operacyjnej, w związku z czym system może znacznie skrócić czas docierania do tych danych.

Sama idea pamięci podręcznej polega na tym, że z doświadczeń wynika, że procesor statystycznie najczęściej potrzebuje tych danych z pamięci operacyjnej, które znajdują się w bliskim sąsiedztwie danych, z których korzystał wcześniej.

Wyobraź sobie, że pamięć operacyjna to taka plansza do gry w statki 10x10, a pamięć podręczna to taki kwadracik 3x3. Procesor potrzebował właśnie danych z pola C3 pamięci operacyjnej, w związku z czym do pamięci podręcznej załadowane zostaną dane z pól najbliższych C3 (B2, B3, B4, C2, C3, C4 i D2, D3, D4). Jeśli teraz procesor będzie potrzebował danych z pola np. B4, to nie będzie musiał sięgać już do pamięci operacyjnej, bo dane te znajdzie już w pamięci podręcznej.

W tym momencie dane z pamięci podręcznej nie zostaną jeszcze przeładowane na te, które sąsiadowały bezpośrednio z polem B4! Procesor może bowiem potrzebować danych na przykład z pola B3 lub C3, a te już w pamięci ma. Pamięć podręczna jest przeładowywana dopiero, gdy procesorowi nie uda się znaleźć w niej potrzebnych danych (na przykład, gdyby po polu B4 potrzebował danych z pola B5).

15. Opisz istotne cech architektury komputerów typu

Von Neumana i Hardvard oraz CISC i RISC.

RISC - ograniczenie listy instrukcji do grupy rozkazów operujących na rejestrach procesora oraz rozkazów przesłań do pamięci i pobrań z niej

-dostarcza małą ilość prostych, bardzo szybkich i krótkich rozkazów mających niewiele formatów i trybow adresowania

-posiada nadmiarową ilość kodu instrukcji co pozwala na włączenie do kodu już na etapie kompilacji wskazówek do jego wykonania

CISC - przetwarzanie na komputerze z rozbudowana lista rozkazow

- duża ilość elementow rozkazow (dochodzaca do 300) i trybow adresowania przy niewielkiej liczbie rejestrow uniwersalnych

- umożliwia dokonywanie operacji na złożonych strukturach danych stosując wiele trybow adresowania

- upraszcza implementacje jezykow wysokiego poziomu i systemow operacyjnych oraz probuje za pomoca jednego rozkazu wykonac jak najwieksza liczbe zadana nie kładąc nacisku na szybkość z jaka wykonwyne sa instrukcje

HARVARD - oparty jest na rozdzielonych przestrzeniach adresowych dla programu i dla danych

- rozdziela dane i instrukcje w fazie pobierania z pamięci realizowane zwykle przez podział pamięci podręcznej na cache instrukcji i cache danych

VON Neumana

- każde działanie wykonywane przez system jest wynikiem realizacji określonego programu bądź jego fragmentu, program umieszcza się w pamięci wczytując go z odpowiednich nośników za pomocą odpowiednich urządzeń wejściowych

- po zapisaniu programu do pamięci może on zostać wywołany do wykonania w dowolnym momencie

16. Scharakteryzuj czynniki wpływające na szybkość

wykonywania rozkazów przez procesor.

Pobieranie instrukcji z rejestru instrukcji IR do dalszego przetwarzania (dekodowania, wykonania) odbywa się z różna prędkością w zależności od:

trybu adresowania,

liczby argumentów,

czasu ich pobierania z pamięci,

liczby taktów zegara w jakich wykonywana jest instrukcja.

Również w różnym tempie odbywa się dostarczanie instrukcji do rejestru rozkazów IR w zależności od obciążenia szyny danych. Mogą zatem powstawać sytuacje, w których dekoder instrukcji czeka na instrukcję w IR a układ pobierania instrukcji nie może jej na czas dostarczyć bo szyna danych jest akurat zajęta innymi transmisjami albo sytuacje w których szyna i pamięć są gotowe i mogą dostarczyć instrukcję, natomiast procesor jest jeszcze zajęty przetwarzaniem instrukcji poprzedniej.

W obu przypadkach jest konieczność wstrzymania pracy bloków nie mających i trzeba wygenerować martwe cykle ich pracy, tzn. czynności polegające na nie zrobieniu nic w danym cyklu zegara.

Aby martwych cykli pracy pamięci i ALU było jak najmniej stosuje się kolejkę instrukcji.

Jeżeli przemieszczenie wypadnie większe od wielkości segmentu to procesor automatycznie wykryje błąd przekroczenia segmentu i przejdzie w tryb obsługi tego błędu (tzw. wyjątek).

17. Jaki wpływ na efektywność pamięci wirtualnej ma

wielkość/pojemność/ części offsetowej adresu wirtualnego?

Uzasadniając swoje analizy odnieść się także do zawartości tabeli

deskryptorów.

Zbyt mała wielkość/pojemność części offsetowej adresu wirtualnego powoduje ograniczenie przestrzeni, którą może zaadresować.

18.

MOV byte ptr AX, 'm' (byte ptr oznacza, że pracujemy na danej typu bajt)

MOV ES, AX

MOV byte ptr AX, 'a'

MOV [ES+1],AX

MOV byte ptr AX, 'r'

MOV [ES+2], AX

MOV byte ptr AX, 'c'

MOV [ES+3], AX

MOV byte ptr AX, 'i'

MOV [ES+4], AX

MOV byte ptr AX, 'n'

MOV [ES+5], AX

MOV byte ptr AX, ' ' (spacja)

MOV [ES+6]. AX

Dotąd do rejestru ES:DI powinny zostać wpisane znaki 'marcin '. Teraz reszta:

MOV word ptr AX, 'M' (word ptr oznacza, że chodzi o daną typu word, zatem dwubajtowe słowo)

MOV [ES+7], AX

MOV word ptr AX, 'A'

MOV [ES+8], AX

analogicznie reszta, aż do litery 'K'.

Wyszukiwarka