Porty równoległe i szeregowe

Jednym z możliwych sposobów przesyłania informacji i danych między dwoma komputerami bądź komputerem a innym urządzeniem zewnętrznym jest wykorzystanie portu szeregowego lub równoległego.

Szeregowy port wejścia/wyjścia służy zazwyczaj do przesyłania danych z myszki lub modemu do komputera jednak cechuje się dosyć powolną transmisją danych, dlatego zazwyczaj do podłączania urządzeń peryferyjnych, wymieniających większe ilości danych z komputerem (np. skaner lub drukarka), stosuje się port równoległy.

Port równoległy

Port równoległy (angielskie parallel port), port umożliwiający przesyłanie równoległe, mogący pełnić funkcję rejestru buforowego lub działać według obieranego programowo protokołu. Równoległość strumienia n bitów w porcie równoległym przyśpiesza przesyłanie danych; interfejs równoległy łączący np. komputer osobisty z drukarką.

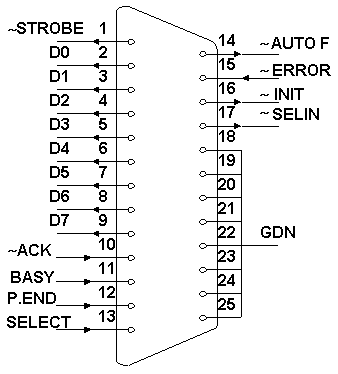

Modele prostych złącz równoległych były w użyciu wiele wcześniej niż mikrokomputery i służyły do przekazywania danych pomiarowych. Po pojawieniu się pierwszych modeli PC zaistniała potrzeba implementacji prostego złącza równoległego obsługującego drukarkę. W tym celu zastosowano uproszczoną wersję standardu Centronics posługującego się w pewnej wersji 29-liniami połączeniowymi i poziomami logicznymi TTL. Zmieniono, więc format gniazda po stronie komputera z 36-końcówkowego wtyku na bardziej kompaktowy typ SUB-D (DB-25) o 25 końcówkach. Zredukowana została liczba przewodów masy z 12 do 8. Magistrala danych jest 8-bitowa i składa się z linii D0-D7. Złącze równoległe wyposażone jest również w 4 linie sterujące (~STR, ~ALF, ~INI, ~DSL). Początkowo zadaniem łącza równoległego był wyłącznie transfer jednokierunkowy (od komputera do drukarki). Drukarka mogła zgłaszać tylko pewne sytuacje nienormalne jak np. brak papieru. Oryginalna specyfika portu równoległego definiuje 5 linii statusowych (~ERR, SEL, PAP, ~ACK, BSY), z których w trybie transmisji 2-kierunkowej półbajtowej 4 wykorzystuje się do transmisji w kierunku odwrotnym. Tryb ten pozwalał na wymianę danych w tempie około 100kB/s i dopuszcza transmisję danych na odległość około 5 metrów.

Współczesny komputer PC może wyprowadzić na zewnątrz maksymalnie 4 złącza równoległe akceptowane przez BIOS i DOS. System operacyjny identyfikuje je poprzez oznaczenia LPT1-LPT4, przy czym synonimem LPT1 jest PRN - domyślna drukarka systemu. Każde z tych łącz BIOS zatwierdza w trakcie ładowania systemu a informacja o ich liczbie jest przechowywana w bitach 7 i 6 bajta o adresie 0040:0011h. Niektóre starsze odmiany BIOS-u ignorują złącza LPT3 i LPT4. Specyfika portu równoległego została ujęta w standardzie IEEE-1284 z 1994 roku i definiuje 5 trybów pracy:

tryb kompatybilny (Compatibility Mode) tzw. Centronics - transmisja jednokierunkowa maksymalnie 200 kB/s

tryb półbajtowy (Nibble Mode) - pozwala na odbiór danych 4 liniami szybkość maksymalnie około 100 kB/s

tryb bajtowy PS/2 (Byte Mode) - korzysta ze zmodyfikowanego dwukierunkowego portu danych zaimplementowanego przez producenta sprzętu, maksymalny transfer do 200 kB/s

tryb EPP (Enhanced Parallel Port) - jest na ogół stosowany dla potrzeb skanerów, interfejsów pamięci masowej i kart sieciowych (szerokość maksymalna 2,3 MB/s)

tryb ECP (Extended Capabilities Port) - korzysta z dodatkowych buforów oraz kanału DMA, wykorzystywany głównie do profesjonalnych drukarek i urządzeń kompleksowych np. fax-skaner-drukarka, prędkość o parametrach podobnych do EPP

Pierwsze trzy tryby znajdują zastosowanie w pierwotnej maszynie określanej jako SPP (Standard Parallel Port) a dwa pozostałe wymagają kompletnej modyfikacji sprzętu (protokoły uzgadniające Handshake). Wszystkie kolejne standardy są zgodne w dół. Tryb półbajtowy i bajtowy nie były implementowane na wszystkich kartach i kontrolerach.

Klasyczny port równoległy w pierwotnej postaci(SPP) wyposażony był w 12 wyjść i 5 wejść dostępnych przez odpowiednie bity rejestrów:

a) 8 wyjść poprzez rejestr danych

b) 4 wyjścia ( z czego 3 zanegowane ) dostępne przez rejestr sterujący

c) 5 wejść ( z czego jedno zanegowane ) dostępne poprzez rejestr stanu.

Wybór trybu pracy złącza równoległego odbywa się za pośrednictwem BIOS - SETUP w punktach Onboard Parallel Mode lub Parallel Port Mode z różnych kombinacji trybów podstawowych zależnych od układów płyty głównej wersji BIOS i typu komputera.

Możliwe kombinacje trybów podstawowych:

Printer Mode (Default Mode, Standard Mode, Normal Mode, SPP) - podstawowy tryb bazowy, transmisja jednokierunkowa, manipulacje 5 bitem rejestru sterującego nie powoduje żadnej reakcji. Kanał zwrotny egzystuje jedynie w formie półbajtowej.

Standard & Bi-Directional. Pozwala na odbiór danych poprzez 8 linii magistrali. Ustawienie bitu 5 rejestru sterującego powoduje odwrócenie kierunku transmisji.

EPP 1.7 & SPP. Dostępne są tu zarówno rejestry standardowe SPP jak i dodatkowe określone dla trybu EPP. Bit 5 odwraca kierunek transmisji. Wersja 1.7 specyfikacji EPP może być pozbawiona implementacji bitu 0 rejestru stanu (Time-Out).

EPP 1.9 & SPP - tryb SPP z implementacją bitu Time-Out (wersja 1.9)

ECP (Extended Parabilities Port) - gwarantuje dostęp do portu ECR i uniemożliwia wykorzystanie trybu EPP

ECP & EPP 1.7 lub ECP & EPP 1.9 - kombinacja trybów ECP i EPP.

Tryby podstawowe

Tryb standardowy

Tryb standardowy korzysta z szeregu sygnałów pierwotnej specyfikacji Centronics:

Pin |

Sygnał |

Kier. |

Opis funkcji |

1 |

~STR |

----> |

1=zezwolenie na odczyt danych |

2 |

D0 |

----> |

Dane bit 0 (LSB) |

3 |

D1 |

----> |

Dane bit 1 |

4 |

D2 |

----> |

Dane bit 2 |

5 |

D3 |

----> |

Dane bit 3 |

6 |

D4 |

----> |

Dane bit 4 |

7 |

D5 |

----> |

Dane bit 5 |

8 |

D6 |

----> |

Dane bit 6 |

9 |

D7 |

----> |

Dane bit 7 (MSB) |

10 |

~ACK |

<---- |

0=potwierdzenie i gotowość na kolejną daną |

11 |

BSY |

<---- |

0=zajętość urządzenia lub brak połączenia |

12 |

PAP |

<---- |

Paper End: 1=brak papieru |

13 |

SEL |

<---- |

1=potwierdzenie wyboru urządzenia |

14 |

~ALF |

----> |

Auto Line Feed - 1=wymuszenie LF po CR |

15 |

~ERR

|

<---- |

0=sygnalizacja błędu |

16 |

~INI |

----> |

Initialize: 0=reset urządzenia |

17 |

~DSL |

----> |

Select Input: 1=wybór urządzenia |

18..25 |

GND |

- |

Signal Ground |

Złącze typu Centronics

D0-D7 Magistrala danych, w systemie standardowym wyłącznie jednokierunkowa

~STR Strobe. Niski poziom na tej linii nakazuje urządzeniu zewnętrznemu odebranie bajta z linii danych, minimalna szerokość impulsu - 0,5μs

~ACK Acknowledge. Niskim poziomem logicznym urządzenie zewnętrzne potwierdza odebranie bajta i gotowość do przyjęcia następnego, szerokość impulsu - 0,5μs

BSY Busy. Wysoki poziom oznacza jeden z następujących stanów:

- drukarka jest w stanie off-line (logicznie odłączona od komputera)

- wewnętrzny bufor drukarki jest pełny

- drukarka odbiera właśnie znak

- trwa inicjalizacja drukarki

- wystąpił błąd w pracy drukarki

PAP Paper Out. Wysoki poziom logiczny sygnalizuje wyczerpanie się zapasu papieru

SELL Select. Wysoki poziom logiczny oznacza, że drukarka jest w stanie On-Line (logicznie połączona z komputerem)

~ALF Auto Line Feed. Niski poziom logiczny poleca drukarce automatyczne dołączanie znaków wysuwu wiersza LF po odebraniu znaku powrotu karetki CR

~ERR Error lub Fault. Niski poziom logiczny występuje w przypadku:

- braku papieru

- przejścia drukarki w stan Off-Line

- inny błąd (wyłączenie drukarki).

~INI Inicjalization. Niski poziom logiczny uruchamia w pewnych typach drukarek procedurę inicjalizującą

~DSL Device Select. Niski poziom powoduje wybranie drukarki. Zwykle linia ta jest połączona z masą tzn. drukarka jest stale wybrana.

Dla wysłania pojedynczego bajta:

komputer wystawia bajt na magistralę danych (zapis do portu danych)

komputer sprawdza sygnał BSY dla ustalenia czy drukarka zdolna jest do przyjęcia danych. Wysłanie danych do urządzenia zajętego przetwarzaniem powoduje ich utratę

komputer aktywuje linię ~STR do wysokości logicznego zera jako informację dla drukarki o odłożeniu bajta na linię danych (minimalna długość impulsu 1μs)

drukarka potwierdza fakt przyjęcia danych niskim stanem na linii ~ACK. W wielu przypadkach kontrolery portu równoległego ignorują impuls potwierdzający.

Opisane powyżej operacje realizowane są przez procesor na rejestrach w przestrzeni wejścia-wyjścia.

Z każdym portem równoległym stowarzyszone są trzy specjalne rejestry: danych, stanu i sterujący ulokowane w spójnych obszarach przestrzeni adresowej wejścia/wyjścia, których początki wyznaczają tzw. adresy bazowe. Dla każdego z portów LPT stowarzyszony z nim rejestr danych leży pod adresem bazowym, adres bazowy +1 jest rejestrem stanu, a adres bazowy +2 rejestrem sterującym.

Adresy bazowe wyznaczone przez BIOS dla wszystkich łącz równoległych zaakceptowanych w przebiegu procedur POST przechowywane są w obszarze danych BIOS (0040:0008h - 0040:000Eh)

Adres |

Rozmiar |

Znaczenie |

Adres bazowy |

0040:0008h |

Słowo |

Adres bazowy złącza LPT1 |

LPT1 378h (3BCh) |

0040 000Ah |

Słowo |

Adres bazowy złącza LPT1 |

LPT2 278h (378h) |

0040:000Ch |

Słowo |

Adres bazowy złącza LPT1 |

LPT3 3BCh (278h) |

0040:000Eh |

Słowo |

Adres bazowy złącza LPT1 |

LPT4 2BCh (2bch) |

Aby poznać faktyczną lokalizację adresów bazowych dla konkretnego komputera możemy posłużyć się programem MSD.ECE lub DEBUG.EXE.

Rejestr danych umożliwia dostęp do magistrali danych. Ustawienie dowolnego bitu tego rejestru powoduje pojawienie się napięcia +5V na stowarzyszonej z nim końcówce. Poziom sygnałówka końcówkach: 0-niski, 1-wysoki.

Rejestr stanu dostarcza informacji o poziomie sygnałów BSY, ~ACK, PAP, SEL, ~ERR. Przeznaczony jest wyłącznie do odczytu, a wszelkie zapisywane do niego dane będą ignorowane.

Bit 7 |

Bit 6 |

Bit 5 |

Bit 4 |

Bit 3 |

Bit 2 |

x |

Bit 0 |

BSY |

~ACK |

PAP |

SEL |

~ERR |

~IRQ |

Zarezerwowane |

|

Stan niski na bicie 2 informuje o wystąpieniu przerwania, bit 0 implementuje tzw. Time-Out przy pracy w trybie EPP.

Rejestr sterujący przeznaczony jest wyłącznie do zapisu (specyfikacji SPP) pozwala na wymuszenie określonych poziomów napięcia na liniach ~DSL, INI, ~ALF i ~STR. Jeżeli sygnał na linii ~ACK zmieni się z wysokiego na niski łącze równoległe może być źródłem przerwania sprzętowego (IRQ 5 lub 7). Bit 4 umożliwia blokadę mechanizmu wyzwalania przerwania (0 - przerwanie zabronione.) Bit 5 aktywuje mechanizm pracy dwukierunkowej rejestru danych (przynosi żądany skutek tylko w układach, w których realizacji sprzętowa dopuszcza możliwość pracy dwukierunkowej).

x |

x |

Bit 5 |

Bit 4 |

Bit 3 |

Bit 2 |

Bit 1 |

Bit 0 |

|

Zarezerwowane |

|

IRQ |

~DSL |

INI |

~ALF |

~STR |

||

Bit piąty służy do aktywacji dwukierunkowej pracy portu danych. Bit czwarty to generacja sygnałów IRL.(0-zabroniona, 1-dozwolona). Pozostałe bity ustawiają poziom napięcia na końcówkach.

Tryb półbajtowy

Tryb półbajtowy (Nibble Mode) stanowi alternatywę przy odczycie ośmiu bitów bez konieczności korzystania z funkcji dwukierunkowego portu danych. W trybie tym trzeba stosować wewnętrzny multiplekser 1x8/2x4 łamiący zewnętrzną 8 bitową szynę danych na dwie porcje podawane kolejno na wejścia szyny 4 bitowej utworzonej z pinów 10, 11, 12, 13. Tryb jest stosunkowo powolny gdyż wymaga szeregu dodatkowych instrukcji dostępu do portów. Utworzona 4 bitowa magistrala doprowadzona jest do górnej połówki rejestru stanu i dlatego niezbędne jest przesunięcie.

Tryb bajtowy

Tryb bajtowy PS/2 (Byte Mode) korzysta z dwukierunkowego portu danych o ile funkcja taka została wbudowana w sprzęt. Aktywacja systemu odbywa się przy pomocy bitu 5 rejestru sterującego.

Tryb EPP

Standard EPP (Enhanced Parallel Port) - efekt wspólnych uzgodnień firm Intel, Xircom, Zenith Data Systems, przewyższa zdecydowanie wartości oferowane przez Centronics i sięga zakresu 2 MB/s. Stosuje się tu to samo okablowanie ze zmianą znaczenia niektórych linii połączeniowych.

Wysyłanie danych w tym trybie wymaga wyłącznie pojedynczej instrukcji zapisu przesyłanego bajta do odpowiedniego portu (zapis danych - adres bazowy +4, zapis adresów - adres bazowy +3).

Cykl zapisu:

zapis bajta do odpowiedniego portu,

aktywowana jest linia ~WRITE,

bajt wystawiany jest na szynę danych,

jeżeli urządzenie utrzymuje ~WAIT na poziomie niskim, wyzwalany jest sygnał zegarowy (DATA STROBE lub ADDR STROBE),

urządzenie potwierdza odbiór bajta podnosząc poziom na linii ~WAIT,

formowane jest tylne zbocze sygnału zegarowego (~DATA STROBE lub ~ADDR STROBE),

cykl zakańcza formowanie tylnego zbocza sygnału ~WAIT.

Cykl odczytu:

procesor wykonuje rozkaz odczytu portu (danych lub adresowego),

jeżeli ~WAIT jest na poziomie niskim aktywowany jest sygnał zegarowy ~STROBE,

kontroler portu EPP oczekuje potwierdzenia w postaci podniesienia poziomu na linii ~WAIT,

wystawiane przez urządzenia dane lub adres pobierane są z magistrali D0-D7,

formowane jest tylne zbocze sygnału zegarowego,

cykl zakańcza formowanie tylnego zbocza sygnału ~WAIT.

Wszystkie punkty, za wyjątkiem kroku pierwszego realizowane są przez układy sprzętowe kontrolera i nie wymagają żadnej integracji programowej.

Tryb EPP może być zaimplementowany jako wersja EPP1.7 lub EPP1.9. Odmiana 1.7 charakteryzuje się zmianą w ocenie gotowości do wyzwolenia poprzedniego zbocza sygnału zegarowego. W tym przypadku nie ma obowiązku oczekiwania na niski poziom sygnału ~WAIT. Obydwie odmiany protokołu musza natomiast odczekać do obniżenia poziomu ~WAIT jako znaku zakończenia danego cyklu.

Tryb EPP jest zgodny w dół, możemy, więc przesyłać dane w klasyczny sposób wykorzystując port adresu bazowego wraz z protokołem Centronics. Przejście do trybu EPP jest możliwe tylko, gdy przyłączone do złącza urządzenie obsługuje ten tryb. Transfer danych przebiega przez rejestr danych, a adresu przez rejestr adresu. Obydwa z tych rejestrów są dwukierunkowe. W trybie tym modyfikacji ulega znaczenie bitu 0 rejestru stanu, który ustawiany jest w wypadku przekroczenia limitu czasowego np., gdy linia ~WAIT nie ulegnie zwolnieniu po upływie określonego czasu (około 10μs) od momentu aktywowania sygnału IOR lub IOW (na magistrali ISA). Przywraca, więc ruch na magistrali, gdy urządzenie zewnętrzne nie przesyła sygnału potwierdzenia, ~WAIT, bo jest np. wyłączone. Bit 0 nie może być zaimplementowany w wersji 1.7. Dodatkowe porty ułatwiają transport słów 16 i 32 bitowych, do omawianych portów zapisujemy naraz 2 lub 4 bajty przesyłane automatycznie 8 bitową szyną łącza równoległego.

Tryb ECP

Tryb ten opracowany został przez firmę Microsoft i Hewlett Packard. Korzysta on z silnego wsparcia ze strony sprzętu, ale w odróżnieniu od EPP posiada:

możliwość korzystania z DMA, co poprawia parametry systemu pracującego pod kontrolą WINDOWS

dodatkowy bufor typu FIFO, (First In First Out) zwykle 16 stopniowy. Pozwala on na zmniejszenie uzależnienia systemu od chwilowej dyspozycji obsługiwanego urządzenia zewnętrznego

kompresję danych RLE (Run, Length Encoding), w którym łańcuch danych jest redukowany do 2 bajtów: 1 z nich jest licznikiem RLC (Run Length Count) - liczba znaków łańcucha, a 2 to wzorzec znaku. Stosowane kodowanie pozwala na osiągnięcie współczynnika kompresji 1:64.

adresowanie kanałów logicznych przez przydzielenie określonym urządzeniom adresów wewnętrznych (Channel Addressing) w celu wyszczególnienia pewnych bloków funkcjonalnych zawartych w ramach jednego zespołu (skaner-fax-drukarka), co pozwala na lepsze wykorzystanie łącza równoległego. W ECP można przydzielić do 128 adresów logicznych.

ECP używa protokołu DMA, aby uzyskać transfer danych o szybkości do 2.5Mbita/s i zapewnia symetryczną komunikację dwukierunkową.

Protokół ECP przedefiniowuje dla swoich potrzeb znaczenie linii połączeniowych i obowiązuje w nim pełna zgodność w dół tzn. port równoległy może być przełączony w tryb SPP (następuje przywrócenie znaczenia linii połączeniowych). ECP pracuje w oparciu o własny protokół transmisji danych z kompresją RLE i adresowaniem kanałów logicznych. System rozróżnia 2 rodzaje cykli w transferze: rozkazowym lub danych. Cykl danych ma miejsce, gdy na magistrali D0-D7 odłożony jest bajt danych, a w cyklu rozkazowym przesyłany może być adres kanału lub licznik RCL. Odpowiedni kierunek transmisji definiowany jest przez aktywowanie jednego z sygnałów HostACK, (0 - gdy nadaje komputer) lub PeriphACK, (0 jeśli transfer odbywa się od urządzenia).

Mechanizm odróżnienia adresu kanału logicznego od licznika RCL pracuje w oparciu o stan 7 bitu magistrali danych (0 - odkładany jest licznik RCL, 1 - transmituje się adres logiczny).

Wtyk DB-25 |

Sygnał SPP |

Sygnał ECP |

Znaczenie |

1 |

~STR |

~HostCLK |

Zegar kluczujący transmisji w kierunku od komputera do urządzenia |

2-9 |

D0-D7 |

D0-D7 |

Dwukierunkowa magistrala danych |

10 |

~ACK |

~PeriphCLK |

Zegar kluczujący transmisji w kierunku od urządzenia do komputera |

11 |

BSY |

PeriphACK |

W stanie wysokim wysyłane są dane a w stanie niskim rozkazy (transmisja od urządzenia do komputera) |

12 |

PAP |

~AckREV |

Urządzenie potwierdza gotowość do wysłania danych obniżając poziom tego sygnału |

13 |

SEL |

X-Flag |

Extensibility Flag |

14 |

~ALF |

HostACK |

W stanie wysokim wysyłane są dane a w stanie niskim rozkazy (transmisja od komputera do urządzenia) |

15 |

~ERR |

~PeriphREQ |

Sygnał ten jest obniżany przez urządzenie pragnące wysłać dane |

16 |

~INI |

~RevREQ |

Stan niski oznacza, iż dane napływają do komputera |

17 |

~DSL |

1284ACTIVE |

Gdy sygnał utrzymuje się w poziomie wysokim komputer wysyła dane. Obniżenie poziomu kończy transfer |

18-25 |

GND |

GND |

Masa |

Cykl transmisyjny ECP biegnący w kierunku od komputera do urządzenia:

przesyłany bajt umieszczany jest na magistrali danych D0-D7

w cyklu rozkazowym linia HostACK sprowadzona jest do logicznego zera, a w cyklu danych do logicznej jedynki

kontroler portu równoległego aktywuje linię ~HostCLK obniżając jej poziom do 0

urządzenie potwierdza gotowość przyjęcia bajtu aktywując linię PeriphACK

formowalne jest tylne zbocze impulsu ~HostCLK w momencie odbioru bajta przez urządzenie.

Transfer w kierunku odwrotnym przebiega podobnie, ale z dodatkową fazą negocjacji kierunku odwrotnego przy współudziale linii ~RevREQ i ~AckREV

Lokalizacja rejestru |

Nazwa |

Typ |

Adres bazowy + 0 |

Rejestr Danych - SPP (Data Register) |

zapis |

|

Rejestr Adr. FIFO (ECP Address FIFO) |

zapis / odczyt |

Adres bazowy + 1 |

Rejestr Stanu - SPP (Status Register) |

odczyt |

Adres bazowy + 2 |

Rejestr Sterujący - SPP (Control Register) |

zapis |

Adres bazowy +0x400h |

Data FIFO |

zapis / odczyt |

|

Test FIFO |

|

|

Configuration Register A |

|

Adres bazowy +0x401h |

Configuration Register B |

zapis / odczyt |

Adres bazowy +0x402h |

Rejestr ECR (Extended Control Register) |

zapis / odczyt |

Tab. Zestaw rejestrów ECP

Przejście w tryb ECP odsłania zestaw dodatkowych rejestrów rezydujących w obszarze leżącym o odległości 0x400h od adresu bazowego, a są to rejestr ECR oraz rejestry konfiguracyjne i testowe.

Rejestr ECR (Extended Control Register), adres bazowy + 0x402h

To główny element sterujący portu równoległego w trybie ECP umożliwiający konfigurację złącza podający informacje statusowe oraz zarządzający buforem FIFO.

Bit 7 |

Bit 6 |

Bit 5 |

Bit 4 |

Bit 3 |

Bit 2 |

Bit 1 |

Bit 0 |

Bity selektora trybu |

ECP Interrupt Bit |

DMA Enable Bit |

ECP Service Bit |

FIFO Full |

FIFO Empty |

||

Trzy najstarsze bity definiują tryb pracy:

000 - tryb standardowy (Standard Mode)

001 - tryb bajtowy (Byte mode)

010 - tryb standardowy z FIFO (Parallel Port FIFO Mode)

011 - tryb ECP z FIFO (ECP FIFO Mode)

100 - tryb EPP (EPP Mode)

101 - zarezerwowane

110 - tryb testowy dla FIFO (FIFO Test Mode)

111 - tryb konfiguracyjny (Configuration Mode)

Układ 8255

Układ 8255 jest programowalnym układem wejścia/wyjścia umożliwiającym równoległe, dwukierunkowe przesyłanie danych.

Wybranie modułu do pracy następuje sygnałem selekcji CS=1. Wybór rejestrów wejścia/wyjścia A, B, C oraz rejestru sterującego następuje odpowiednio adresem A1=0, A0=0 (rejestr A); A1=0, A0=1 (rejestr B); A1=1, A0=0 (rejestr C); A1=1, A0=1 (rejestr sterujący).

Kierunek przesyłania danych jest określany sygnałem ~WR (~WR=0 - zapis danych do rejestru) oraz ~ RD (~RD=0 - odczyt danych z rejestru).

Rejestr C może być używany jako dwa niezależnie sterowane rejestry czterobitowe (górna część rejestru C - bity PC7...PC4, dolna część rejestru C - bity PC3...PC0).

Wybór jednego z trzech trybów pracy 0, 1, 2 modułu 8255 odbywa się przez zapis odpowiedniego słowa sterującego b7, b6,...b1, b0 do rejestru sterującego. Bit najbardziej znaczący b7 ma zawsze wartość równą 1, a bity pozostałe mają następujące znaczenie:

b6, b5 określają tryb pracy rejestru A (00 - tryb0, 01 - tryb1, 10 - tryb2);

b4 określa funkcję rejestru A (0 - układ wejściowy, 1 - układ wyjściowy);

b3 określa funkcję górnej części rejestru C (0 - układ wejściowy, 1 - układ wyjściowy);

b2 określa tryb pracy rejestru C (0 - tryb0, 1 - tryb1);

b1 określa funkcję rejestru B (0 - układ wejściowy, 1 - układ wyjściowy);

b0 określa funkcję dolnej części rejestru C (0 - układ wejściowy, 1 - układ wyjściowy).

Port szeregowy

Pomimo tego, że łącze szeregowe cechuje się znacznie mniejszą prędkością transmisji od łącza równoległego, to znajduje ono szerokie zastosowanie w różnego typu urządzeniach. Specyfikacja tego łącza dopuszcza transmisję danych na odległość do 200 m natomiast łącze równoległe jedynie do około 5m. Tak, więc łącze tego typu jest powszechnie używane w modemach, myszkach, różnego typu urządzeniach pomiarowych, obrabiarkach cyfrowych itp.

Szeregowa forma wymiany danych może być synchroniczna lub asynchroniczna.

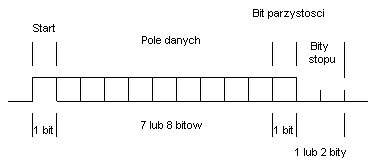

Transmisja asynchroniczna - polega na przesyłaniu pojedynczych znaków, które posiadają pewien określony format danych tzw. ramkę (ang. frame). Ramka właśnie a nie pojedynczy bit danych jest najmniejszą porcją przekazywanej jednorazowo przez łącze informacji. Początek znaku sygnalizowany jest bitem startu. Po bicie startu następują bity danych, za bitami danych może wystąpić bit kontrolny. Zakończenie transmisji znaku sygnalizowane jest jednym lub dwoma bitami stopu. Bit ten zamyka ramkę i łącze wraca do stanu początkowego lub realizuje transmisję następnej porcji danych. Bit startu nie przesyła żadnej informacji, służy celom synchronizacyjnym. Jest, więc wyraźnie zaznaczonym początkiem transmisji. Ilość bitów danych może być od 5 do 8. Pierwszy bit danych jest najstarszym bitem przesyłanego znaku. Celem bitu kontrolnego jest zabezpieczenie danych przed błędami. Bit kontrolny zwany jest także bitem parzystości i wyznaczany jest na podstawie bitów danych. Kontrola parzystości polega na sprawdzaniu ilości jedynek w bitach danych. Bit kontrolny pozwala wykryć błąd w przesyłanych bitach danych, pod warunkiem wystąpienia nieparzystej liczby błędów w czasie transmisji. Ustawienie ilości bitów danych, ilości bitów stopu, włączenie stosowania bitu kontrolnego i określenie sposobu jego obliczania, dokonywane jest przed rozpoczęciem transmisji danych i nie może się zmieniać w trakcie trwania transmisji. Bity poszczególnych znaków przesyłane są w sposób synchroniczny, zgodnie z taktem nadajnika, poszczególne znaki przesyłane są asynchronicznie. Dane (bajty) przychodzące do układu portu szeregowego zamieniane są na ciągi bitów, następnie dzielone na bloki danych o długości od 5 do 8 bitów. Do każdego bloku danych dodawane są bity sterujące - startu, stopu, kontrolny. Wynikiem tego jest mniejsza prędkość transmisji danych niż to wynika z ustawień szybkości portu szeregowego. Np. dla 8 bitów danych dodatkowo transmitowane są 4 bity sterujące: 1 bit startu, 2 bity stopu i jeden bit kontrolny. Sprawy komplikują się, gdy pomiędzy bitami startu i stopu przesyłanych jest mniej niż 8 bitów danych. Brakujące, bardziej znaczące bity rejestru buforowego odbiornika zawierają wtedy wartości przypadkowe i należy je zamaskować.

Rys. 1. Transmisja asynchroniczna jednego znaku zawierającego: 1 bit startu, 8 bitów danych, 1 bit kontrolny i 2 bity stopu (ramka danych).

W warunkach rzeczywistych nie występują oczywiście tak wyidealizowane przebiegi prostokątne. Przy dużych prędkościach transmisji zaczynają odgrywać rolę pojemności przewodów łączących. Wszystko to powoduje zniekształcenia zboczy sygnałów oraz nakładanie się na nie dodatkowych przebiegów zakłócających. Przetwarzanie szeregowego strumienia danych odbywa się, więc w sposób bardziej skomplikowany. Odbiornik pracuje z częstotliwością 16-krotnie większą niż wynikałoby to z ustalonej szybkości pracy łącza, a każdy bit ramki jest badany (próbkowany) 16 razy. Wynik pobierania tych 16 próbek jest uśredniany, a na podstawie tej operacji zapada decyzja, czy badanemu wycinkowi czasowemu przyporządkować niski czy wysoki poziom logiczny. Metoda ta podnosi znacznie odporność łącza na zakłócenia impulsowe i eliminuje niekorzystny wpływ zniekształconych zboczy.

Czas trwania jednego bitu w jednostce informacyjnej nazywa się odstępem jednostkowym i jest oznaczany przez tb. Jego odwrotność określa szybkość transmisji w bodach (1 bod = 1 bit/s). Typowe wartości szybkości transmisji przy asynchronicznej transmisji znakowej wynoszą: 300, 600, 1200, 2400, 4800, 9600,14400,19200, 38400 bodów.

Transmisja synchroniczna - polega na przesyłaniu dużych bloków danych bez transmisji bitów oznaczających początek i koniec poszczególnych znaków. Kolejne bity danych wyprowadzane są zgodnie z taktem nadawania. Po ostatnim bicie znaku poprzedniego wysyłany jest natychmiast pierwszy bit znaku następnego.

Przy asynchronicznej transmisji znakowej przyjmuje się, że odbiornik i nadajnik pracują z tą samą częstotliwością. Ponieważ długość przesyłanego znaku jest mała to niewielka różnica częstotliwości generatorów taktu w nadajniku i odbiorniku nie powoduje błędnego odbioru znaków. Natomiast przy transmisji synchronicznej umożliwiona jest dowolna zmiana prędkości transmisji. Odbiornik dostosowuje się natychmiast do częstotliwości nadajnika, o ile oczywiście nie zostanie przekroczona pewna wartość graniczna. Oprócz linii przekazującej dane istnieje też, więc dodatkowe połączenie przesyłające przebieg synchronizujący.

Transmisja synchroniczna jest szybsza od asynchronicznej ze względu na brak dużej ilości bitów sterujących. Jednak jej realizacja jest trudniejsza i wymaga złożonych układów odbiorczych do poprawnego rozpoznawania bitów i grupowania bitów w znaki.

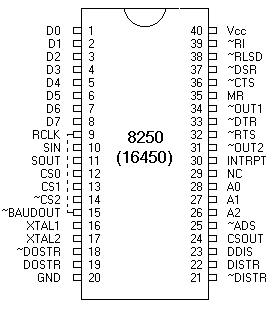

Układ scalony 8250 (UART)

W komputerach typu PC wszystkie funkcje portu szeregowego realizowane są w specjalizowanym układzie scalonym o nazwie UART (Universal Asynchronous Receiver/Transmitter). Komputer chcąc wysłać dane, na przykład do modemu, inicjalizuje port. Inicjalizacja polega na wpisaniu pod właściwe adresy odpowiednich słów sterujących. Określają one szybkość bitową portu, ile bitów danych, ile bitów stopu, kiedy UART ma zgłaszać przerwanie itp. Po ustawieniu parametrów transmisji do układu portu (UART-u) wpisywany jest znak, który należy nadać. UART automatycznie dodaje bit startu, bit protekcji, bity stopu, kontroluje i ustawia odpowiednio sygnały sterujące. Po przepisaniu danych do rejestru wyjściowego UART zgłasza przerwanie chcąc powiadomić komputer o możliwości przyjęcia następnej danej. Zgłoszenie przerwania automatycznie uruchamia program obsługi, który wykrywa przyczynę przerwania i wysyła kolejny znak. Przerwanie generowane jest także wtedy, gdy UART odbierze znak od urządzenia zewnętrznego. Przerwanie jest zgłaszane także w przypadkach wykrycia przez UART błędów.

Najstarszym układem UART jest układ 8250. Dziś można spotkać tylko w starych i powolnych urządzeniach typu IBM PC/XT. Jego następcą był układ oznaczony jako 16450, szybsza wersja układu 8250 i jego nowsza wersja oznaczona 16550 (stosowane w modelach PC/AT). Różnią się tym, że układy 16550 posiadają 16 bajtowy bufor odbiornika, pamięć FIFO, po stronie nadawczej i odbiorczej. Daje to możliwość wpisania do UART-u przez komputer 16 słów w momencie nadawania. Komputer otrzyma przerwanie, gdy UART wyśle 12 z 16 wcześniej wpisanych słów; następnie uzupełni pamięć kolejnymi 12 słowami. Minimalny czas reakcji na przerwanie jest dość długi, równy czasowi nadawania czterech słów. Taka sama sytuacja występuje po stronie odbiorczej. Czas na odczytanie odebranych słów dzięki buforowej pamięci FIFO jest znacznie wydłużony niż to był w układach 8250. Zastosowanie buforów na wejściu i wyjściu UART-u zwiększa szybkość pracy łącza szeregowego. Nie odczytanie danych z bufora przed odebraniem nowych danych powoduje utratę wiadomości. Kolejnym układem UART jest układ 16650 posiadający 32-bajtowy bufor, pozwalający na szybkość transmisji do 115000 b/s. Najnowszym układem UART jest układ 16750 posiadający bufor o wielkości 64 bajtów.

Sterowniki te przeznaczone są do asynchronicznej transmisji znakowej. W starszych komputerach sterownik ten najczęściej występował jako oddzielna karta, obecnie sterownik jest fizyczną częścią płyty głównej komputera. Bez względu na fizyczną postać sterownika, od strony programowej widziany jest on zawsze tak samo.

Rys. 2. Rozkład wyprowadzeń podstawowego układu 8250-UART (16450):

Oto znaczenie poszczególnych wyprowadzeń UART:

~CTS (Clear To Send) - wejście odpowiadające linii sterującej interfejsu RS232. Stwierdza gotowość do odbioru danych przez niski poziom logiczny.

~DSR (Data Set Read) - wejście sygnalizujące nawiązanie połączenia, niski poziom mówi, że urządzenie odbiorcze jest gotowe do przyjęcia danych od komputera.

~RLSD (Received Line Signal Detect) - tą linią odbiornik sygnalizuje odbiór fali nośnej, co oznacza, że jest w trakcie nawiązywania połączenia. Stanem aktywnym jest poziom niski.

~RI (Ring Indicator) - w przypadku połączenia dwóch modemów przez sieć telefoniczną komputer informowany jest o odebraniu sygnału odpowiadającego wywołaniu abonenta.

~RTS (Request To Send) - tą linią przekazywany jest rozmiar danych do urządzenia odbiorczego. Wyjście to jest dostępne bezpośrednio przez jeden bit rejestru wyjściowych sygnałów sterujących UART (rejestr układu o adresie 04h).

~DTR (Data Terminal Ready) - Sygnał ten wskazuje w ogólności na gotowość komputera, musi on pozostawać aktywny przez cały czas trwania połączenia. Wyjście to jest dostępne bezpośrednio przez bit 0 rejestru wyjściowych sygnałów sterujących UART (rejestr 04h)

~MR (Master Reset) - podanie na to wejście logicznej 1 powoduje inicjalizację wszystkich rejestrów wewnętrznych UART z wyjątkiem buforów odbiornika i nadajnika oraz rejestru podzielnika

~OUT1,

~OUT2 Wyjścia te mogą być swobodnie programowalne, OUT2 steruje w

komputerach PC kluczem blokującym przerwania pochodzące od UART

INTRPT (Interrupt) - wysokim poziomem napięcia sygnalizuje spełnienie warunków wywołania przerwania, określonych maską rejestru przerwań (rejestr 01h)

A2-A0 linie adresujące wewnętrzne rejestry UART, umożliwiające dostęp do nich procesorowi

~ADS (Addresses Strobe) - sygnał w stanie aktywnym (0) oznacza, że adres na liniach A2-A0 jest ustawiony i może być dekodowany przez UART

CSOUT (Chip Select Out) - wyjście to jest aktualizowane przez UART, jeżeli został on wybrany przez CPU liniami CS0,CS1,~CS2

DDIS (Driver Disable) - sygnał ten przyjmuje wartość logicznego zera w trakcie operacji odczytu wewnętrznych rejestrów UART przez procesor

DISTR,

~DISTR (Data In Strobe) - wejściowy sygnał sterujący umożliwiający w stanie

aktywnym (DISTR=1,~DISTR=0) odczyt wewnętrznych rejestrów UART

SOUT (Serial Output) - wyjście toru nadawczego UART

SIN (Serial Input) - wejście toru odbiorczego UART

CS0,CS1,

~CS2 (Chip Select) - stan aktywny oznacza wybranie układu UART przez procesor

w celu dokonania zapisu lub odczytu jednego z jego rejestrów

RCLK (Receiver Clock) - wejście sygnału synchronizującego tor odbiorczy o częstotliwości 16 razy większej od zadanej prędkością transmisji

~BAUDOUT wyjście sygnału synchronizującego tor nadawczy, o częstotliwości 16 razy większej od zadanej prędkością transmisji

XTAL1,

XTAL2 końcówki do przyłączenia zewnętrznego rezonatora kwarcowego, układ

akceptuje też w tym miejscu zewnętrznie wytwarzany sygnał synchronizujący

D0-D7 dwukierunkowa, 8-bitowa magistrala danych, służąca przekazywaniu danych, rozkazów i bajtów statusowych

Vcc wejście napięcia zasilającego (+5V)

GND masa zasilania

Źródłem częstotliwości odniesienia dla tego układu jest wewnętrzny generator synchronizowany rezonatorem kwarcowym o częstotliwości 1,8432 MHz dołączonym do końcówek XTAL1 i XTAL2 lub sygnałem z zewnętrznego źródła o tej samej częstotliwości. Sygnał o częstotliwości odniesienia kierowany jest do programowalnego 16-bitowego dzielnika częstotliwości. Podział częstotliwości dla nadajnika odbywa się dwuetapowo: w pierwszym programowalny licznik wydziela częstotliwość nadajnika, w drugim dokonywany jest podział przez stały współczynnik 16 dający właściwy sygnał synchronizujący tor nadawczy. Sygnał ten przetwarza równoległą postać danych na ramki. Tor odbiorczy układu odbiera z wejścia RCLK sygnał taktujący o częstotliwości 16 razy większej od przyjętej prędkości transmisji. Tak, więc połączenie wejścia RCLK z wyjściem licznika powoduje, że oba tory pracują z tą samą prędkością

Współpraca procesora ze sterownikiem interfejsu szeregowego odbywa się za pośrednictwem kilku rejestrów. Dla każdego łącza szeregowego przypisanych jest 8 adresów w przestrzeni adresowej wejścia/wyjścia tworzących port.

Do nadania znaku wykorzystywane są dwa rejestry: bufor nadajnika (TBR) i rejestr przesuwający (TSR). Do bufora nadajnika wpisywany jest znak przeznaczony do wysłania, następnie dodawane są bity sterujące i cała jednostka informacyjna wprowadzana jest do rejestru przesuwającego nadajnika, który posiada wejście równoległe i wyjście szeregowe. Kolejne bity jednostki informacyjnej wyprowadzane są z rejestru przesuwającego zgodnie z taktem nadawania i poprzez nadajnik linii pojawiają się na wyjściu TxD.

Do odbioru znaków również wykorzystywane są dwa rejestry. Dane z wejścia RxD wprowadzane są (poprzez odbiornik linii) na wejście rejestru szeregowo-równoległego. Po skompletowaniu całej jednostki informacyjnej (wszystkie bity od bitu startu do bitu stopu) bity zawierające dane są przekazywane do bufora odbiornika (RBR), skąd następuje odczyt znaku przez procesor. W czasie odbioru znaku dokonywana jest kontrola formatu jednostki informacyjnej i błędów transmisji. Informacje o zajęciu bufora nadajnika, odebraniu znaku i błędach transmisji zawarte są rejestrze stanu transmisji (LSR).

Do każdego portu szeregowego przyporządkowanych jest dziesięć 8-bitowych rejestrów, ale nie wszystkie bity w tych rejestrach są wykorzystywane. Każdy port szeregowy ma przypisany adres w obszarze adresów zarezerwowanych dla danego portu. Pierwszy adres jest adresem bazowym stanowiącym odniesienie dla adresów rejestrów portu. Adres rejestru sterownika podawany jest zazwyczaj jako adres bazowy portu + przesunięcie względem adresu bazowego.

Do określenia przesunięcia adresu służą trzy linie adresowe (A2,Al,A0), które pozwalają zaadresować jedynie osiem różnych rejestrów. Ale w sterowniku interfejsu szeregowego jest 10 rejestrów. Aby było możliwe adresowanie większej ilości rejestrów wprowadzono dodatkowy bit adresowy, którego rolę pełni siódmy bit w rejestrze parametrów transmisji (oznaczenie LCR7). Takie samo przesunięcie (000) względem adresu bazowego posiadają: bufor nadajnika, bufor odbiornika oraz mniej znaczący bajt dzielnika. Bufory nadajnika i odbiornika odróżnia rodzaj wykonywanych operacji: do bufora nadajnika można tylko zapisywać, a z bufora odbiornika tylko odczytywać. Można, więc dla obu tych rejestrów przypisać takie samo rozszerzenie adresu LCR7=0. Aby odróżnić mniej znaczący bajt dzielnika, rejestr przeznaczony również tylko do zapisu, od bufora nadajnika, konieczne jest wcześniejsze ustawienie LCR7=1.

Bufor nadajnika (TBR - Transmiter Data Buffer Register) jest rejestrem pośredniczącym w nadawaniu znaku. Przeznaczony do wysłania, znak wpisywany jest do TBR, po wcześniejszym sprawdzeniu, czy jest on wolny. O zajętości bufora nadajnika informuje bit 5 w rejestrze LSR (znacznik zajętości bufora). Każdy zapis do TBR powoduje ustawienie bitu LSRS na zero, co oznacza zajęcie bufora. Ustawienie znacznika zajęcia bufora nadajnika na 1 odbywa się automatycznie, po przepisaniu znaku z TBR do rejestru przesuwającego nadajnika. LSRS=1 informuje, że bufor jest gotowy do przyjęcia następnego znaku.

Bufor odbiornika (RBR - Receiver Data Buffer Register) jest rejestrem pośredniczącym w odbiorze znaku. Po skompletowaniu znaku w rejestrze przesuwającym odbiornika, przepisywany jest do bufora odbiornika i sygnalizowane jest ustawieniem bitu 0 w rejestrze LSR na 1. Odczyt bufora RBR powoduje skasowanie bitu LSRO. Jeżeli odczyt bufora odbiornika nie nastąpi przed odebraniem następnego znaku, występuje błąd nie odebrania znaku (OE - Overrun Error). Wynikiem tego jest utrata znaku poprzedniego.

Rejestr parametrów transmisji (LCR - Line Control Register) ustawia format jednostki informacyjnej: ilość bitów danych, ilość bitów stopu, występowanie bitu kontrolnego i jego znaczenie (czy sygnalizowana jest parzystość czy nieparzystość). Również w tym rejestrze jest bit pozwalający na przerwanie nadawania (Break) i wymuszenie stanu 0 na wyjściu TxD. Bit siódmy (LCR7) jest rozszerzeniem adresu.

Rejestr stanu transmisji (LSR - Line Status Register) informuje o zajęciu bufora danych, rejestr przesuwającego nadajnika, gotowości do odczytania znaku z bufora odbiornika, o przyczynach wystąpienia błędów, o wykryciu na wejściu szeregowym sygnału Break. Odczyt rejestru LSR kasuje bity określające przyczynę błędu oraz bit sygnalizujący wykrycie sygnału Break.

Rejestr sterowania modemu (MCR - Modem Control Register) ustala poziomy sygnałów DTR i RTS, umożliwia wprowadzenie sygnału przerwania INTRPT na linię IRQ3 lub IRQ4. Jeden z bitów rejestru używany jest do zamknięcia pętli sprzężenia zwrotnego w celu wykonania auto testu sterownika interfejsu szeregowego. Stan aktywny na linii DTR lub RTS (wysoki poziom napięcia) wymuszany jest poprzez wpisanie 1 na bit odpowiadający danemu sygnałowi. Nadawanie i odbiór nie są sprzętowo uzależnione od stanu sygnałów DTR i RTS, czyli można przeprowadzić transmisję przy nieaktywnych sygnałach DTR i RTS. Przy współpracy z modemem, należy sterować liniami DTR i RTS zgodnie z protokołem komunikacji z modemem.

Rejestr stanu modemu (MSR - Modem Status Register) - odwzorowanie stanu sygnałów kontrolnych odbieranych z modemu (DSR, CTS, DCD, RI) i informacja o zmianach tych sygnałów. Stan aktywny sygnałów DSR, CTS, RI oraz DCD przedstawiany jest jedynką logiczną na odpowiadających im bitach w rejestrze. Odczyt rejestru MSR kasuje znaczniki informujące o wystąpieniu zmiany sygnałów.

Rejestr aktywacji przerwań (IER - Interrupt Enable Register) - maskowanie przerwań występujących w sterowniku interfejsu szeregowego. W sterowniku możliwe są cztery przyczyny wystąpienia przerwania:

przerwanie po skompletowaniu znaku w buforze odbiornika,

wysłanie wszystkich znaków z bufora nadajnika,

wystąpienie błędu związane z odbiorem znaku (błąd parzystości PE, formatu ramki FE, błąd nie odczytania znaku przed zakończeniem odbioru następnego znaku OE, przerwanie transmisji sygnałem BREAK),

zmiana sygnału kontrolnego (DSR, CTS, DCD lub RI)

Rejestr identyfikacji przerwań (IDR - Interrupt Identification Register) umożliwia stwierdzenie, czy istnieje aktywne przerwanie oraz rozpoznanie jego przyczyny. Znacznikiem przerwania jest bit IDR0, którego stan 0 informuje o istnieniu aktywnego przerwania. Odczytanie rejestru IDR powoduje ustawienie znacznika przerwania, na 1, co oznacza brak aktywnego przerwania.

Interfejs RS-232C

Standard RS 232C (Recommended Standard) został wprowadzony w 1969 roku przez Electronic Industries Association (EIA) w celu normalizacji interfejsu pomiędzy urządzeniem końcowym dla danych (DTE - Data Terminal Equipment) a urządzeniem komunikacyjnym dla danych (DCE - Data Communication Equipment). Transmisja danych odbywa się szeregowo, bit po bicie, na nieduże odległości z prędkością do 20 kbitów/s.

Kabel RS-232C składa się maksymalnie z 25 przewodów, z których każdy spełnia określoną rolę i jest przeznaczony do przenoszenia różnych sygnałów. Standardowo zakończony jest gniazdem 25-stykowym (DB 25) opisanym przez standard ISO, 2110. Ponieważ, jak już wcześniej wspomniano, rzadko używane są wszystkie sygnały złącza, spotykane są też wtyki 9-stykowe (DB 9) zgodne ze standardem ISO 4902.

Wtyk DB-25 |

Wtyk DB-9 |

Nazwa sygnału |

Kierunek sygnału |

1 |

- |

Masa ochronna |

- |

2 |

3 |

Dane wysyłane (TxD) |

wy |

3 |

2 |

Dane otrzymywane (RxD) |

we |

4 |

7 |

Gotowość wysłania danych (RTS) |

wy |

5 |

8 |

Gotowość przyjęcia danych (CTS) |

we |

6 |

6 |

Gotowy zestaw danych (DSR) |

we |

7 |

5 |

Masa sygnałowa (SG) |

- |

8 |

1 |

Wybrany (RLSD) |

we |

20 |

4 |

Urządzenie gotowe (DTR) |

wy |

22 |

9 |

Sygnał dzwonienia (RI) |

we |

Tab. 1. Rozmieszczenie wyprowadzeń w stosowanych wtykach portu RS-232

Parametry elektryczne sygnałów

FG (styk 1) |

Styk uziemienia powinien być połączony z tym samy stykiem drugiego złącza |

GND (styk 7) |

Styk dostarcza sygnał masy, czyli napięcie referencyjne, wobec którego mierzone są napięcia innych sygnałów. Powinien być połączony na wprost z tym samym stykiem drugiego złącza.

|

Linie danych: TxD (styk 2) RxD (styk 3) |

Dla linii danych napięcie mniejsze od -3V jest przyjmowane jako logiczna jedynka, natomiast większe niż +3V jako logiczne 0. Nadajnik linii szeregowej najczęściej wystawia sygnał do poziomu 12V w celu zapewnienia odpowiedniego marginesu szumowego. |

Linie sterujące |

Dla linii sterujących dodatnie napięcie jest rozpoznawane jako stan włączenia, zaś napięcie ujemne jako stan wyłączenia. Oczywiście dzieje się tak, jeśli przekracza ono poziom 3V.

|

Transmisja danych

Linie TxD i RxD służą do transmisji danych.

Logiczne poziomy tych sygnałów interpretowane są jako bity informacji.

Urządzenie DTE używa styku 2 do nadawania, a styku 3 do odbioru, podczas, gdy urządzenie DCE dokładnie odwrotnie.

Aby dołączyć terminal lub komputer do modemu wystarczy użyć połączenia na wprost.

Aby zidentyfikować, czy jest to urządzenie DCE, czy DTE wystarczy zmierzyć napięcie na stykach 2 i 3.

Nadajnik w stanie spoczynku powinien na jednym z nich utrzymywać napięcie ujemne.

Jeśli napięcie na styku 2 jest ujemne to mamy do czynienia z urządzeniem DTE.

Jeśli napięcie na styku 3 jest ujemne to mamy urządzenie DCE.

Sterowanie modemowe

Większości urządzeń nie wystarcza jedynie przesyłanie ciągu danych. Potrzebują one sterowania przebiegiem transmisji za pomocą potwierdzeń. Po pierwsze komputer (DTE) musi wiedzieć, że dostępny jest modem. Następnie modem, który zrealizował połączenie musi przekazać komputerowi, że nawiązał połączenie z innym systemem komputerowym.

Komputer (DTE) wystawia sygnał na styku 20 (DTR), sygnalizując gotowość.

Z kolei modem (DCE) wystawia sygnał na styku 6 (DSR - gotowość modemu).

Kiedy modem nawiąże łączność z innym modemem, wystawia sygnał na styku 8 (DCD), aby powiadomić komputer, że połączenie zostało nawiązane. Najczęściej sygnał DCD pozostaje na wysokim poziomie przez cały czas trwania transmisji.

Jeśli napięcie na styku 20 (DTE) spada, dla modemu oznacza to, że komputer nie jest w stanie kontynuować transmisji. Modem wówczas rozłączy się.

Jeśli napięcie na styku 8 (DCD) spada jest to równoznaczne z przekazaniem komputerowi informacji, że modem nie ma już połączenia.

Połączenie urządzeń

Standard RS-232C wprowadzony przez EIA obejmuje 21 linii stykowych. Do poprawnej transmisji nie trzeba wykorzystywać ich wszystkich. Najczęściej wystarczy użyć 9 linii:

Przesyłanie danych w takich połączeniach może odbywać się w trzech trybach:

Tryb simpleksowy

Łącze skonfigurowane jest na stałe na jeden z możliwych kierunków transmisji DTE→DCE lub DCE→DTE. W pierwszym przypadku DTE wykorzystuje wyłącznie linię TxD, a linia RxD nie jest podłączona. Sygnały RTS i CTS bądź nie są brane pod uwagę bądź są utrzymywane w stanie aktywnym przez cały czas. Sygnał DCD modemu z założenia nigdy nie może być aktywny, a DSR albo jest stale aktywny, albo jest aktywowany w momencie nawiązania kontaktu z korespondentem (modemem). Komputer sygnałem DTR zgłasza swoją gotowość modemowi, czyli włącza i wyłącza modem. Linia RI nie ma tutaj znaczenia.

Tryb półdupleksowy

W trybie tym zarówno DTE jak i DCE są stroną nadającą oraz odbierającą, ale do dyspozycji jest tylko jeden kanał logiczny danych, który naprzemiennie wykorzystywany jest w obu kierunkach. Wyjścia TxD każdego z urządzeń połączone są z wejściami RxD partnera. Aktualny kierunek transmisji wyznacza sygnał RTS-CTS. Modem chcąc przesłać dane do PC aktywuje swój sygnał RTS i czeka na potwierdzenie na linii CTS. Uzgodnienie te upoważnia modem do wysłania danych, a komputer do ich odbioru. Pozostałe sygnały zachowują swoje naturalne znaczenie. Urządzenie DCE może tutaj robić użytek z linii RI, sygnalizując chęć nawiązania kontaktu przez partnera modemu znajdującego się po drugiej stronie łącza zwykle telefonicznego.

Tryb dupleksowy

Służy do przekazywania danych jednocześnie w obu kierunkach. Większość nowoczesnych modemów może pracować w tym trybie. Kanał logiczny połączenia otwarty jest stale w obie strony, a sygnały CTS i RTS nie mają znaczenia. Linia DSR jest stale aktywna, chyba, że sygnalizuje nawiązanie połączenia z drugim modemem. Sygnał DCD aktywowany jest jako odpowiedź na wykrycie fali nośnej, a linią DTR można sterować wyłączenie i włączenie modemu.

Przerwania generowane przez łącze szeregowe.

Układ UART może być źródłem przerwań sprzętowych, sygnalizując tym samym konieczność obsługi przez procesor. Warunki, w których UART będzie generował przerwanie sprzętowe (tj. dodatni impuls na wyjściu INTRPT) można określić programując rejestr konfiguracji przerwań IMR.

x |

x |

x |

x |

bit3 |

bit2 |

bit1 |

bit0 |

bity 7-4 bez znaczenia;

bit 3 1 = przerwanie generowane jest w wyniku zmiany stanu jednego z wejściowych sygnałów sterujących łącza RS-232C (CTS, DSR, DCD, RI);

bit 2 1 = przerwanie generowane jest w wyniku błędu parzystości, protokołu, przepełnienia lub zerwania połączenia;

bit 1 1 = przerwanie generowane jest na skutek opróżnienia rejestru przesuwnego nadajnika (ang. THRE - Transmitter Holding Register Empty);

bit 0 1 = przerwanie generowane jest, gdy w rejestrze buforowym odbiornika znajduje się odebrany bajt danych.

Rejestr identyfikacji przerwań.

Dokładną przyczynę przerwania można określić analizując rejestr identyfikacji przerwań IIR, którego budowę pokazano poniżej.

0 |

0 |

0 |

0 |

0 |

bit2 |

bit1 |

bit0 |

bity 7-3 00000;

bity 2-1 kod identyfikacyjny przerwania;

bit 0 stan przerwania:

0 = przerwanie oczekuje na obsługę,

1 = brak przerwań.

Przyczynę przerwania określa kod identyfikacyjny:

Bit 2 |

Bit 1 |

Przyczyna przerwania |

Priorytet |

0 |

0 |

zmiana stanu jednego z sygnałów sterujących łącza RS-232C |

najniższy (3) |

0 |

1 |

bufor nadajnika jest pusty |

2 |

1 |

0 |

w buforze odbiornika znajduje się nie odebrany bajt |

1 |

1 |

1 |

stwierdzono błąd parzystości, protokołu, przepełnienie bufora odbiornika lub zerwanie łączności |

najwyższy (0) |

Błędy występujące podczas transmisji

Przekroczenia czasu (Time Out)

Standardowy czas oczekiwania na reakcje korespondenta przy próbie nawiązania połączenia, wysłania lub odbioru znaku łączem szeregowym wynosi 20 sekund. Po przekroczeniu tego czasu ustawiany jest bit 7 statusu (Time Out). Wartością czasów oczekiwania dla każdego z łącz przechowywane są w obszarze danych BIOS-u.

Adres |

Znaczenie |

0040:007Ch |

Limit czasu dla łącza COM1 (w sekunach) |

0040:007Dh |

Limit czasu dla łącza COM2 (w sekunach) |

0040:007Eh |

Limit czasu dla łącza COM3 (w sekunach) |

0040:007Fh |

Limit czasu dla łącza COM4 (w sekunach) |

Czas oczekiwania dla dowolnego łącza COMn można ustawić na nieskończenie długi poleceniem DOS-u mode comn,, p.

Przerwanie połączenia (Break)

Stan ten sygnalizowany jest, gdy końcówka wejściowa RxD odbiornika znajduje się w niskim stanie logicznym przez czas dłuższy od czasu trwania jednej ramki. Oznacza to przerwanie linii danych, ewentualnie uszkodzenie nadajnika. Linia danych łącza w stanie spoczynku utrzymywana jest przez nadajnik w wysokim stanie logicznym.

Błąd protokołu (Frame Error)

Ma on miejsce, gdy oczekiwany przez odbiornik bit stopu nadejdzie za wcześnie lub zbyt późno. Oznacza to, że długość ramki jest inna od uzgodnionej, co może wskazywać na niewłaściwą liczbę bitów stopu, parzystości, danych lub odmienną od deklarowanej prędkość transmisji.

Błąd parzystości (Parity Error)

Może on oznaczać przekłamanie bitu (bitów) w bajcie danych na drodze między odbiornikiem a nadajnikiem, ewentualnie niezgodność sposobu kontroli parzystości po obu stronach łącza.

Błąd przepełnienia (Overrun Error)

Błąd ten wystąpi, gdy dane napływają do łącza szybciej, niż mogą być pobierane z bufora wejściowego odbiornika przez program obsługi łącza. Skompletowany w buforze odbiornika bajt zostanie w takiej sytuacji zamazany przez następną porcję danych.

Linie TxD (Transmitted Data) i RxD (Received Data) są właściwymi przewodami służącymi wymianie danych. Pozostałe są liniami sterującymi, posiadającymi następujące znaczenie:

RTS (Request to Send) urządzenie DTE (terminal, PC) sygnalizuje tą linią zamiar przekazywania danych do DCE (modemu). Modem przygotowuje się do odbioru danych.

CTS (Clear to Send) linią tą przesyłane jest potwierdzenie przyjęcia sygnału RTS przez DCE (modem) i stwierdzenie gotowości do odbioru danych do DTE. Komputer może rozpocząć przekazywanie danych.

Para sygnałów sterujących RTS/CTS może przy półdupleksowym trybie pracy łącza (takim, w którym dopuszczalna jest niejednoczesna transmisja w obu kierunkach) sterować kierunkiem transmisji, przydzielając połączonym korespondentom na przemian rolę nadawcy i odbiorcy.

DSR (Data Set Ready) specyfikacja RS - 232C określa ten sygnał jako meldunek urządzenia DCE (zwykle modemu), że zostało nawiązane połączenie i układ jest gotów do przyjęcia danych od DTE (zwykle komputera). W praktyce większość modemów nie wykorzystuje tej linii i jest ona sztucznie utrzymywana w stanie aktywnym, nie mówiąc nic o istnieniu połączenia z korespondentem. Po poziomie tego sygnału można co najwyżej wnioskować, czy modem jest w ogóle włączony.

DTR (Data Terminal Ready) sygnał ten wskazuje w ogólności na gotowość urządzenia DTE (komputera). Musi on pozostawać aktywny przez cały czas trwania połączenia.

Para sygnałów DTR i DSR odpowiada za utrzymanie połączenia, podczas gdy sygnały RTS i CTS są odpowiedzialne za przekazywanie danych i ewentualnie sterowanie kierunkiem ich przepływu (w trybie półdupleksowym), czyli tzw. handshaking.

DCD (Data Carrier Detect) modem (DCE) sygnalizuje tą linią odbiór fali nośnej, co oznacza, że druga strona jest w trakcie nawiązywanie połączenia. Sygnał DCD pozostaje aktywny przez cały czas trwania transmisji.

RI (Ring Indicator) w przypadku połączenia modemów przez sieć telefoniczną urządzenie DTE (komputer) informowane jest o odebraniu sygnału odpowiadającego wywołaniu abonenta (dzwonieniu).

DSRD (Data signal rate detektor) linia ta występuje tylko w 25 końcówkowej wersji łącza. Umożliwia dostosowanie się korespondentów do jednej z dwóch możliwych prędkości transmisji. Z sygnału tego mogą korzystać obie strony połączenia.

8255 - programowalny układ wejścia/wyjścia równoległego

wyprowadzenia

PA, PB, PC - 8-bitowe porty we/wy

/CS - chip select: aktywacja układu

/RD - read: odczyt

/WR - write: zapis

RESET - zerowanie układu

D0... D7 - szyna danych

A0, A1 - szyna adresowa

Vcc - zasilanie

GND - masa

opis

8-bitowe porty PA i PB mogą być ustawione jako wejścia bądź wyjścia, natomiast port PC podzielony jest na dwie 4-bitowe części, które można oddzielnie programować jako wejście lub jako wyjście.

Sygnał RESET zeruje wszystkie rejestry układu oraz porty i ustawia je jako wyjścia.

Sygnałami A0 i A1 wybiera się port lub rejestr sterujący do odczytu lub zapisu danych:

/RD |

/WR |

A0 |

A1 |

operacja |

0 |

1 |

0 |

0 |

odczyt PA |

0 |

1 |

0 |

1 |

odczyt PB |

0 |

1 |

1 |

0 |

odczyt PC |

0 |

1 |

1 |

1 |

operacja zabroniona |

1 |

0 |

0 |

0 |

zapis PA |

1 |

0 |

0 |

1 |

zapis PB |

1 |

0 |

1 |

0 |

zapis PC |

1 |

0 |

1 |

1 |

zapis rejestru sterującego |

1 |

1 |

x |

x |

brak operacji |

rejestr sterujący

D7 |

1 - zapis do rejestru sterującego |

|

D6 |

wybór trybu: 00-tryb0, 01-tryb1, 1x-tryb2 |

|

D5 |

|

|

D4 |

PA: |

0-wy, 1-we |

D3 |

PC7..PC4: |

0-wy, 1-we |

D2 |

wybór trybu PB dla trybu 2-go |

|

D1 |

PB: |

0-wy, 1-we |

D0 |

PC3..PC0: |

0-wy, 1-we |

W trybie 1 i 2 poszczególne bity PC mogą być ustawiane lub zerowane poprzez rejestr sterujący. Z możliwości tej korzysta się w celu programowego blokowania i odblokowywania żądań przerwania.

D7 |

0 - ustawianie bitów PC |

D6 |

x |

D5 |

|

D4 |

|

D3 |

numer bitu |

D2 |

|

D1 |

|

D0 |

wstawiana wartość: 0/1 |

tryby pracy

każdy z portów może pracować jako we lub wy proste

PA, PB: we lub wy z potwierdzeniem

PC: port sterujący

PA: transmisja dwukierunkowa z potwierdzeniem

PB: tryb 0 lub 1

PC: port sterujący

tryb 0

Jest on przeznaczony do realizacji bezwarunkowych operacji wejścia/wyjścia.

dwa porty 8-bitowe i dwa porty 4-bitowe

możliwość zaprogramowania każdego portu jako wejścia lub jako wyjścia

wyjścia z rejestrami zatrzaskowymi

wejścia bez rejestrów zatrzaskowych

tryb 1

Jest przeznaczony do realizacji operacji wejścia/wyjścia z przerwaniem, przy jednym kierunku przesyłania danych. Potrzebne do tego celu sygnały są wyprowadzane lub wprowadzane z wykorzystaniem linii portu C.

dwie grupy wyprowadzeń: A i B. Obie grupy składają się z odpowiedniego portu 8-bitowego do przesyłania danych i z pomocniczego portu 4-bitowego przeznaczonego do przesyłania sygnałów sterujących

możliwość zaprogramowania każdego 8-bitowego portu jako wejścia lub wyjścia, przy czym zarówno wejścia jak i wyjścia mają rejestry zatrzaskowe

możliwość zaprogramowania jako wejścia lub wyjścia tych linii portu C, które służą do przekazywania sygnałów sterujących

jedna grupa końcówek składająca się z dwukierunkowego portu A oraz z pięciu bitów portu C

możliwość zaprogramowania portu A jako wejścia i wyjścia równocześnie, przy czym zarówno wejście jak i wyjście mają rejestry zatrzaskowe

możliwość zaprogramowania jako wejścia lub jako wyjścia tych linii portu C, które nie służą do przekazywania sygnałów sterujących

/OBF jest ustawiany przez narastające zbocze /WR i zerowany przez /ACK

IBF jest ustawiany przez /STB i zerowany przez narastające zbocze /RD

/ACK jest sygnałem potwierdzającym przyjęcie danych przez element zewnętrzny

/STB jest sygnałem wpisującym dane do bufora wejściowego

INTE jest sygnałem umożliwiającym genereację sygnału INT

jest zmieniany przez ustawianie i zerowanie odpowiedniego bitu PC poprzez rejestr sterujący

INT

dla we: ustawiany, gdy /STB, IBF i INTE są aktywne; zerowany przez opadające zbocze /RD

dla wy: ustawiany, gdy /ACK, OBF i INTE są aktywne; zerowany przez opadające zbocze /WR

„Anatomia PC”

PA i PB pracują jako wejścia |

||

PC7 |

we/wy proste |

|

PC6 |

|

|

PC5 |

IBF A |

input buffer full |

PC4 |

INTE A, /STB A |

interrup enable, strobe |

PC3 |

INT A |

interrupt |

PC2 |

INTE B, /STB B |

interrupt enable, strobe |

PC1 |

IBF B |

input buffer full |

PC0 |

INT B |

interrupt |

PA i PB pracują jako wyjścia |

||

PC7 |

/OBF A |

output buffer full |

PC6 |

INTE A, /ACK A |

interrup enable, acknowledge |

PC5 |

we/wy proste |

|

PC4 |

|

|

PC3 |

INT A |

interrupt |

PC2 |

INTE B, /ACK B |

interrupt enable, acknowledge |

PC1 |

/OBF B |

output buffer full |

PC0 |

INT B |

interrupt |

tryb 2

Jest on przeznaczony do realizacji operacji wejścia/wyjścia z przerwaniem, tylko poprzez port A - przy dwóch kierunkach przesyłu danych. Umożliwia on wymianę danych z elementem zewnętrznym za pomocą jednej, 8-bitowej magistrali danych. Potrzebne do tego celu sygnały są również wyprowadzane przez port C.

PC7 |

/OBF |

output buffer full |

wy |

PC6 |

INTE, /ACK |

interrup enable / acknowledge |

wy |

PC5 |

IBF |

input buffer full |

we |

PC4 |

INTE, /STB |

interrup enable / strobe |

we |

PC3 |

INT |

interrupt |

dla we i wy |

PC2 |

tryb 0 PB: we/wy proste tryb 1 PB: jak w trybie 1 dla PB |

||

PC1 |

|

||

PC0 |

|

||

we/wy z potwierdzeniem

LITERATURA:

Szukasz gotowej pracy ?

To pewna droga do poważnych kłopotów.

Plagiat jest przestępstwem !

Nie ryzykuj ! Nie warto !

Powierz swoje sprawy profesjonalistom.

- 2 -

Szukasz gotowej pracy ?

To pewna droga do poważnych kłopotów.

Plagiat jest przestępstwem !

Nie ryzykuj ! Nie warto !

Powierz swoje sprawy profesjonalistom.

Wyszukiwarka