POLITECHNIKA SZCZECIŃSKA Wydział Elektryczny Laboratorium Teorii Układów Logicznych

|

|||

Temat ćwiczenia: |

UKŁADY SYNCHRONICZNE

US-2 |

||

Data wykonania ćwiczenia: 13.01.2002 |

Data oddania: |

Ocena: |

Prowadzący ćw.

Dr. inż. G.Żegliński

|

|

26.01.2002 |

|

Ćw. wykonali:

Andrzej Resiak Artur Pieśkiewicz |

Cel ćwiczenia:

Zaprojektuj programowalny dzielnik częstotliwości o dwóch wejściach wyboru sposobu dzielenia a i b:

a |

b |

dzielnik |

0 |

0 |

1/2 |

0 |

1 |

1/3 |

1 |

0 |

1/4 |

Zadanie zrealizuj na przerzutnikach JK.

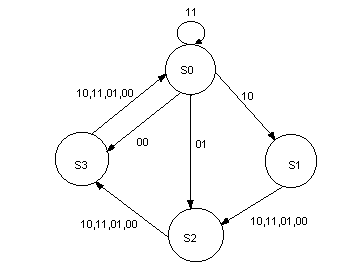

1) Graf stanów przejść:

Nie kodowana tabela przejść - wyjść:

St |

St+1 |

Y |

|

a b |

a b |

a b |

a b |

|

|

0 0 |

0 1 |

1 0 |

1 1 |

|

S0 |

S3 |

S2 |

S1 |

S0 |

0 |

S1 |

S2 |

S2 |

S2 |

S2 |

1 |

S2 |

S3 |

S3 |

S3 |

S3 |

1 |

S3 |

S0 |

S0 |

S0 |

S0 |

1 |

Tabela wzbudzeń przerzutnika JK:

Qt |

Qt+1 |

J |

K |

0 |

0 |

0 |

-- |

0 |

1 |

1 |

-- |

1 |

0 |

-- |

1 |

1 |

1 |

-- |

0 |

Kodowanie stanów:

S |

|

Q1 Q2 |

S0 |

00 |

00 |

S1 |

01 |

01 |

S2 |

10 |

10 |

S3 |

11 |

11 |

Zakodowana tabela przejść - wyjść:

St |

Q1t Q2t |

Q1t+1 Q2 |

J1 |

K1 |

J2 |

K2 |

Y |

||||||||||||||||

|

|

00 |

01 |

11 |

10 |

00 |

01 |

11 |

10 |

00 |

01 |

11 |

10 |

00 |

01 |

11 |

10 |

00 |

01 |

11 |

10 |

|

|

S0 |

0 |

0 |

11 |

10 |

00 |

01 |

1 |

1 |

0 |

0 |

-- |

-- |

-- |

-- |

1 |

0 |

0 |

1 |

-- |

-- |

-- |

-- |

0 |

S1 |

0 |

1 |

10 |

10 |

10 |

10 |

1 |

1 |

1 |

1 |

-- |

-- |

-- |

-- |

-- |

-- |

-- |

-- |

1 |

1 |

1 |

1 |

1 |

S2 |

1 |

1 |

-- |

-- |

-- |

-- |

-- |

-- |

-- |

-- |

-- |

-- |

-- |

-- |

-- |

-- |

-- |

-- |

-- |

-- |

-- |

-- |

1 |

S3 |

1 |

0 |

11 |

11 |

11 |

11 |

-- |

-- |

-- |

-- |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

-- |

-- |

-- |

-- |

1 |

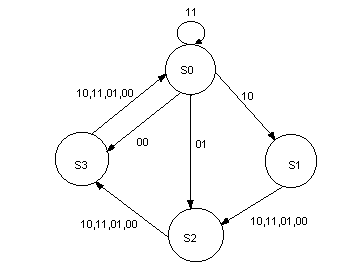

Minimalizacja:

minimalizacja wejść:

minimalizacja wyjść:

Y = Q1 + Q2

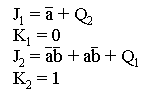

) na podstawie danych realizujemy schemat ideowy:

WNIOSKI:

W zrealizowanym ćwiczeniu poznaliśmy metody projektowania dzielników

częstotliwości w zależności od stanów wejść a i b programowanych na przerzut-

nikach JK. W naszym przypadku sygnał zegarowy był sygnałem, dla którego

realizowaliśmy dzielnik częstotliwości w zależności od wejść a i b.

Symulacja w programie Pspice nie dała jednak oczekiwanych rezultatów.