Rozdział 2.

Funkcje układów TTL

Rodzina układów TTL serii 74xx zawiera bardzo dużo różnorodnych układów. Prezentacja wszystkich rozwiązań znacznie wykracza poza ramy niniejszej książki. Dlatego też przedstawionych zostanie tylko kilka ważniejszych grup układów, które będą używane również w następnych rozdziałach.

Wśród układów serii 74xx wyróżnić można:

układy kombinacyjne, w których stan wyjść w każdej chwili zależy wyłącznie od stanu wejść:

bramy[Author ID1: at Thu Dec 13 21:00:00 2001 ]

i[Author ID1: at Thu Dec 13 21:00:00 2001 ] logiczne (nie wymagają szerszego opisu),bufory z wyjściami trójstanowymi,

układy porównujące (komparatory),

multipleksery i demultipleksery,

kodery, dekodery i transkodery (konwertery kodów),

sterowniki wyświetlaczy 7-segmentowych,

układy sprawdzania parzystości;[Author ID1: at Thu Dec 13 21:01:00 2001 ]

,[Author ID1: at Thu Dec 13 21:01:00 2001 ]układy sekwencyjne, w których stan wyjść w danej chwili zależy nie tylko od stanu wejść, lecz także od poprzednich stanów układu:

liczniki asynchroniczne i synchroniczne,

przerzutniki,

rejestry z wyjściami trójstanowymi,

układy czasowe —[Author ID1: at Thu Dec 13 21:00:00 2001 ]

-[Author ID1: at Thu Dec 13 21:00:00 2001 ] generatory impulsów.

Sterowniki wyświetlaczy

Podstawową funkcją sterownika wyświetlacza 7-segmentowego jest włączenie odpowiednich segmentów wyświetlacza zależnie od cyfry podanej na wejście. Cyfra ta jest w kodzie BCD. Prócz tego sterownik ma jeszcze dodatkowe funkcje sterujące:

test wyświetlacza (włączenie wszystkich segmentów),

bezwarunkowe wygaszenie wszystkich segmentów,

warunkowe wygaszenie wszystkich segmentów, jeżeli cyfra wejściowa jest równa 0 (tzw. wygaszenie zera nieznaczącego).

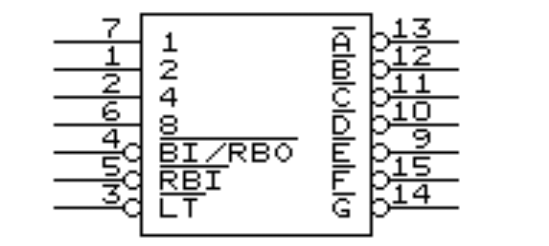

Sterowniki są produkowane w wersji dla obu wersji wyświetlacza (ze wspólną katodą lub anodą). Ponadto poszczególne układy sterowników różnią się między sobą maksymalnymi prądami i napięciami wyjściowymi oraz kształtem cyfr „6” i „9”. Wyprowadzenia przykładowego sterownika 7447 ilustruje rysunek 2.1.[Author ID1: at Thu Dec 13 21:04:00 2001

][Author ID1: at Thu Dec 13 21:06:00 2001

][Author ID1: at Thu Dec 13 21:06:00 2001

][Author ID1: at Thu Dec 13 21:06:00 2001

][Author ID1: at Thu Dec 13 21:06:00 2001

]Rysunek [Author ID1: at Thu Dec 13 21:06:00 2001

]1[Author ID1: at Thu Dec 13 21:06:00 2001

][Author ID1: at Thu Dec 13 21:06:00 2001

].[Author ID1: at Thu Dec 13 21:06:00 2001

]

Rysunek 2.1.[Author ID1: at Thu Dec 13 21:05:00 2001

][Author ID1: at Thu Dec 13 21:06:00 2001

][Author ID1: at Thu Dec 13 21:06:00 2001

][Author ID1: at Thu Dec 13 21:06:00 2001

]1[Author ID1: at Thu Dec 13 21:06:00 2001

][Author ID1: at Thu Dec 13 21:06:00 2001

].[Author ID1: at Thu Dec 13 21:06:00 2001

] Wyprowadzenia sterownika wyświetlacza 7-segmentowego

Wejścia 1, 2, 4 i 8 to wejścia BCD (1 —[Author ID1: at Thu Dec 13 21:13:00 2001

]-[Author ID1: at Thu Dec 13 21:13:00 2001

] najmniej znaczące, 8 —[Author ID1: at Thu Dec 13 21:13:00 2001

]-[Author ID1: at Thu Dec 13 21:13:00 2001

] najbardziej znaczące). Wejście ![]()

(ang. Light Test) służy do przeprowadzenia testu wyświetlacza (włącza wszystkie segmenty). Wejście ![]()

(ang. Ripple Blank Input) służy do wygaszenia zera nieznaczącego. Natomiast sygnał ![]()

(ang. Blank Input/Ripple Blank Output) pełni dwie funkcje. Jest on mianowicie wejściem bezwarunkowego wygaszenia wyświetlacza oraz wyjściem informującym o wygaszeniu warunkowym. Sygnały ![]()

i ![]()

można zatem wykorzystać do szeregowego łączenia kilku sterowników, jeżeli liczba zer nieznaczących może być większa niż 1.

Układy porównywania cyfr

W pewnych przypadkach w układach wyświetlania może okazać się konieczne sprawdzenie, czy cyfra (liczba) do wyświetlenia spełnia określony warunek (np. czy jest mniejsza od zadanej wartości). Przykładowo, wyświetlacz obrotomierza może migać, jeżeli obroty są w zakresie niebezpiecznym dla silnika.

Do sprawdzenia relacji wystarczy skonstruowanie układu kombinacyjnego. Można tu wykorzystać m. [Author ID1: at Thu Dec 13 21:16:00 2001

]in. bramki sumy modulo 2 (XOR), umożliwiające porównanie pojedynczych bitów. Takie podejście jest [Author ID1: at Thu Dec 13 21:17:00 2001

]daje nam jednak układ mało elastyczny —[Author ID1: at Thu Dec 13 21:17:00 2001

]-[Author ID1: at Thu Dec 13 21:17:00 2001

] zmiana jednego z argumentów relacji, lub też zmiana samej relacji, wymaga powtórnego zaprojektowania układu. Dlatego też warto zastosować tzw. komparator.

Komparator 4-bitowy

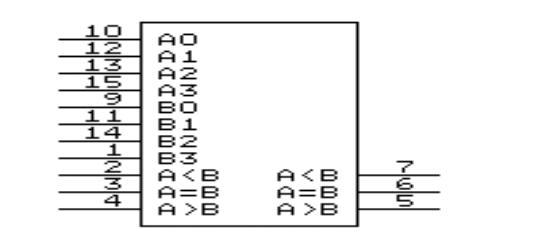

Przykładowy komparator, powiedzmy [Author ID1: at Thu Dec 13 23:11:00 2001

] [Author ID1: at Fri Dec 14 14:31:00 2001

]7485, umożliwia porównanie dwóch cyfr 4-bitowych. Oprócz 8 wejść połączonych w dwie grupy (A —[Author ID1: at Thu Dec 13 21:19:00 2001

]-[Author ID1: at Thu Dec 13 21:19:00 2001

] jedna cyfra, B —[Author ID1: at Thu Dec 13 21:19:00 2001

]-[Author ID1: at Thu Dec 13 21:19:00 2001

] druga) ma on trzy wejścia sterujące (A [Author ID1: at Thu Dec 13 21:23:00 2001

]< [Author ID1: at Thu Dec 13 21:23:00 2001

]B, A [Author ID1: at Thu Dec 13 21:23:00 2001

]= [Author ID1: at Thu Dec 13 21:23:00 2001

]B i A [Author ID1: at Thu Dec 13 21:23:00 2001

]> [Author ID1: at Thu Dec 13 21:23:00 2001

]B) służące do zadania relacji wejściowej oraz trzy wyjścia o takich samych oznaczeniach, pokazujące wynik porównania. Podczas stosowania jednego komparatora wejście A [Author ID1: at Thu Dec 13 21:24:00 2001

]= [Author ID1: at Thu Dec 13 21:24:00 2001

]B podłącza się do „1” logicznej, pozostałe zaś —[Author ID1: at Thu Dec 13 21:20:00 2001

]-[Author ID1: at Thu Dec 13 21:20:00 2001

] do „0”. Zależnie od relacji zachodzącej między badanymi cyframi jedno z wyjść przyjmie stan „1”, pozostałe natomiast —[Author ID1: at Thu Dec 13 21:20:00 2001

]-[Author ID1: at Thu Dec 13 21:20:00 2001

] „0”. Podejście takie umożliwia połączenie większej liczby komparatorów w celu porównania cyfr o większej liczbie bitów. Wyjścia sterujące układu podłącza się wówczas do odpowiednich (o takiej samej nazwie) wejść w układzie następnym. Wyprowadzenia komparatora 7485 ilustruje rysunek 2.2.[Author ID1: at Thu Dec 13 21:26:00 2001

][Author ID1: at Thu Dec 13 21:26:00 2001

][Author ID1: at Thu Dec 13 21:26:00 2001

][Author ID1: at Thu Dec 13 21:26:00 2001

][Author ID1: at Thu Dec 13 21:26:00 2001

]Rysunek [Author ID1: at Thu Dec 13 21:26:00 2001

]2[Author ID1: at Thu Dec 13 21:26:00 2001

][Author ID1: at Thu Dec 13 21:26:00 2001

].[Author ID1: at Thu Dec 13 21:26:00 2001

]

Rysunek 2.2.[Author ID1: at Thu Dec 13 21:27:00 2001

] [Author ID1: at Thu Dec 13 21:27:00 2001

][Author ID1: at Thu Dec 13 21:27:00 2001

][Author ID1: at Thu Dec 13 21:27:00 2001

]2[Author ID1: at Thu Dec 13 21:27:00 2001

][Author ID1: at Thu Dec 13 21:27:00 2001

]. [Author ID1: at Thu Dec 13 21:27:00 2001

]Wyprowadzenia komparatora 4-bitowego

Jeżeli A [Author ID1: at Thu Dec 13 21:28:00 2001 ]≠ [Author ID1: at Thu Dec 13 21:28:00 2001 ]B, to stan wyjść nie zależy od relacji wejściowej, tylko od relacji między cyframi A i B. Jeżeli natomiast A [Author ID1: at Thu Dec 13 21:28:00 2001 ]= [Author ID1: at Thu Dec 13 21:28:00 2001 ]B, to wyjścia powielają stan wejść sterujących. Wynika z tego, że w połączeniu kaskadowym pierwszy komparator powinien sprawdzać relację między cyframi najmniej znaczącymi.

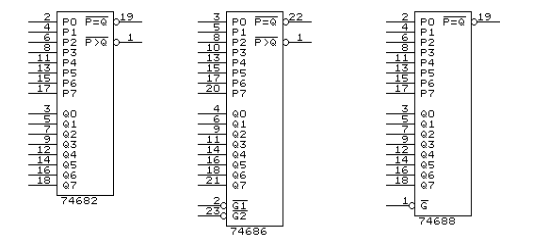

Komparatory 8-bitowe

Komparatory 8-bitowe pozwalają na porównywanie cyfr o długości 8 bitów. W przeciwieństwie do układu 7485 nie mają one tak wielu sygnałów sterujących.Ważniejsze cechy układów zebrano w tabeli, a rozkład wyprowadzeń poszczególnych grup układów ilustruje rysunek 2.3.[Author ID1: at Thu Dec 13 21:29:00 2001

][Author ID1: at Thu Dec 13 21:29:00 2001

][Author ID1: at Thu Dec 13 21:29:00 2001

][Author ID1: at Thu Dec 13 21:29:00 2001

][Author ID1: at Thu Dec 13 21:29:00 2001

]Rysunek [Author ID1: at Thu Dec 13 21:29:00 2001

]3[Author ID1: at Thu Dec 13 21:29:00 2001

][Author ID1: at Thu Dec 13 21:29:00 2001

].[Author ID1: at Thu Dec 13 21:29:00 2001

]

Rysunek 2.3. [Author ID1: at Thu Dec 13 21:30:00 2001

][Author ID1: at Thu Dec 13 21:30:00 2001

][Author ID1: at Thu Dec 13 21:30:00 2001

][Author ID1: at Thu Dec 13 21:30:00 2001

]3[Author ID1: at Thu Dec 13 21:30:00 2001

][Author ID1: at Thu Dec 13 21:30:00 2001

]. [Author ID1: at Thu Dec 13 21:30:00 2001

]Wyprowadzenia komparatorów 8-bitowych

Wszystkie komparatory mają dwie grupy wejść dla porównywanych cyfr, oznaczone P i Q.

Układy 74682, 74683, 74684 i 74685 mają dwa wyjścia wyniku

-->

porównania: [Author:EK]

[Author ID1: at Fri Dec 14 15:40:00 2001

]![]()

oraz ![]()

. Tabela określa stan tych wyjść w zależności od relacji między P a Q.

W układach 74686 i 74687 wyjścia relacji są identyczne, ale każde z nich można indywidualnie bramkować. Jeżeli na wejściu ![]()

jest „1”, to wyjście ![]()

jest w stanie wysokim, a stan wyjścia ![]()

nie jest określony. Jeżeli natomiast „1” jest na wejściu ![]()

, to wyjście ![]()

jest w stanie wysokim, a stan wyjścia ![]()

nie jest określony.

W układach 74688 i 74689 jest tylko jedno wejście bramkujące i tylko jedno wyjście ![]()

. Układ pracuje tylko wtedy, gdy na wejściu ![]()

jest „0”.

Multipleksery i demultipleksery

Multipleksery

Podstawowa funkcja multipleksera polega na przesłaniu na wyjście stanu logicznego tego wejścia informacyjnego, którego numer jest podany na wejściach adresowych. Liczba wejść informacyjnych jest równa 2a, gdzie a jest liczbą wejść adresowych. Ponadto niektóre multipleksery mają także wejścia bramkujące.

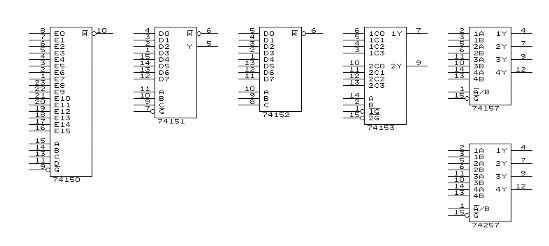

Produkowane obecnie multipleksery mają 1, 2, 3 lub 4 wejścia adresowe, a więc liczba wejść informacyjnych może być równa 2, 4, 8 lub 16. Wyjścia są najczęściej przeciwsobne, aczkolwiek spotyka się także układy z wyjściami trójstanowymi. Rozkład wyprowadzeń niektórych multiplekserów przedstawia rysunek 2.4.[Author ID1: at Thu Dec 13 21:36:00 2001 ]

Rysunek 2.4. [Author ID1: at Thu Dec 13 21:37:00 2001

][Author ID1: at Thu Dec 13 21:37:00 2001

][Author ID1: at Thu Dec 13 21:37:00 2001

][Author ID1: at Thu Dec 13 21:37:00 2001

]4[Author ID1: at Thu Dec 13 21:37:00 2001

][Author ID1: at Thu Dec 13 21:37:00 2001

].[Author ID1: at Thu Dec 13 21:37:00 2001

] [Author ID1: at Thu Dec 13 19:33:00 2001

] [Author ID1: at Thu Dec 13 19:33:00 2001

]Wyprowadzenia wybranych multiplekserów

Układy 74157 i 74257

Układ 74157 zawiera cztery multipleksery, z których każdy posiada:

dwa wejścia informacyjne (A i B),

jedno wyjście (Y).

Ponadto układ ma wejścia:[Author ID1: at Thu Dec 13 21:38:00 2001

]e[Author ID1: at Thu Dec 13 21:38:00 2001

] adresowe (![]()

) i bramkujące (![]()

), które są wspólne dla wszystkich czterech multiplekserów. Gdy na wejściu ![]()

jest stan wysoki, wszystkie wyjścia przyjmują stan niski. Gdy natomiast na wejściu tym jest stan niski, to wyjścia powielają stan wejść A lub B zależnie od stanu wejścia adresowego.

Układ 74257 ma wyjścia trójstanowe, które są w stanie wysokiej impedancji, gdy na wejściu ![]()

jest „1”. Poza tym działanie tego układu jest identyczne z działaniem [Author ID1: at Fri Dec 14 14:37:00 2001

]układu[Author ID1: at Fri Dec 14 14:35:00 2001

] [Author ID1: at Fri Dec 14 14:36:00 2001

]74157.

Układ 74153

Układ 74153 zawiera dwa multipleksery, z których każdy posiada:

cztery wejścia informacyjne (C0 [Author ID1: at Thu Dec 13 21:51:00 2001 ]- [Author ID1: at Thu Dec 13 21:51:00 2001 ]

-[Author ID1: at Thu Dec 13 21:51:00 2001 ]C3),jedno wyjście (Y),

jedno wejście bramkujące (

).

Ponadto układ ma dwa wejścia adresowe (A i B), wspólne dla obu multiplekserów. Stan niski na wejściu ![]()

włącza odpowiedni multiplekser, stan wysoki —[Author ID1: at Thu Dec 13 21:52:00 2001

]-[Author ID1: at Thu Dec 13 21:52:00 2001

] powoduje pojawienie się „0” na wyjściu.

Układy 74151 i 74152

Układy 74151 i 74152 zawierają po jednym multiplekserze, który posiada:

osiem wejść informacyjnych (D0 [Author ID1: at Thu Dec 13 21:52:00 2001 ]- [Author ID1: at Thu Dec 13 21:52:00 2001 ]

-[Author ID1: at Thu Dec 13 21:52:00 2001 ]D7),trzy wejścia adresowe (A, B i C),

wyjście zanegowane (

).

Układ 74151 ma ponadto wejście bramkujące ![]()

oraz wyjście proste Y.

Układ 74150

Układ 74150 zawiera jeden multiplekser, który posiada:

16 wejść informacyjnych (D0 - [Author ID1: at Thu Dec 13 21:53:00 2001 ]

-[Author ID1: at Thu Dec 13 21:53:00 2001 ]D7),cztery wejścia adresowe (A, B i C),

wyjście proste (Y) i zanegowane (

),wejście bramkujące (

).

Demultipleksery

Demultipleksery pełnią funkcję przeciwną do multiplekserów —[Author ID1: at Thu Dec 13 21:54:00 2001

]-[Author ID1: at Thu Dec 13 21:54:00 2001

] mają one za zadanie przesyłanie sygnału wejściowego na wybrane wyjście.

-->

W dalszej części książki demultipleksery będą używane wyłącznie jako dekodery kodu dwójkowego na kod „1 z n”. [Author:EK]

[Author ID1: at Thu Dec 13 22:01:00 2001

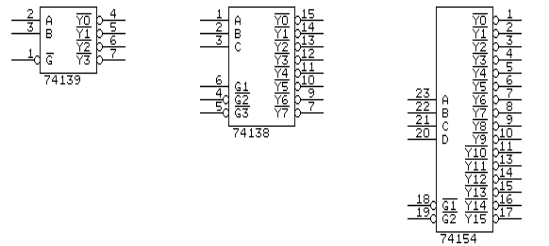

]Wyprowadzenia przykładowych demultiplekserów ilustruje rysunek 2.5.[Author ID1: at Thu Dec 13 22:05:00 2001

][Author ID1: at Thu Dec 13 22:05:00 2001

][Author ID1: at Thu Dec 13 22:05:00 2001

][Author ID1: at Thu Dec 13 22:05:00 2001

][Author ID1: at Thu Dec 13 22:05:00 2001

]Rysunek [Author ID1: at Thu Dec 13 22:05:00 2001

]5[Author ID1: at Thu Dec 13 22:05:00 2001

][Author ID1: at Thu Dec 13 22:05:00 2001

].[Author ID1: at Thu Dec 13 22:05:00 2001

]

Rysunek 2.5. [Author ID1: at Thu Dec 13 22:05:00 2001

][Author ID1: at Thu Dec 13 22:05:00 2001

][Author ID1: at Thu Dec 13 22:05:00 2001

][Author ID1: at Thu Dec 13 22:05:00 2001

]5[Author ID1: at Thu Dec 13 22:05:00 2001

][Author ID1: at Thu Dec 13 22:05:00 2001

]. [Author ID1: at Thu Dec 13 22:05:00 2001

]Wyprowadzenia niektórych demultiplekserów

Układ 74139

Układ 74139 zawiera dwa identyczne i całkowicie niezależne od siebie demultipleksery o dwóch wejściach adresowych A i B (o wadze odpowiednio 20 i 21). Każdy z nich posiada wejście bramkujące ![]()

, aktywne w [Author ID1: at Thu Dec 13 22:37:00 2001

]stani[Author ID1: at Thu Dec 13 22:37:00 2001

]em[Author ID1: at Thu Dec 13 22:37:00 2001

] niskim. Podanie „1” na to wejście powoduje, że wszystkie wyjścia ![]()

są nieaktywne (znajdują się w stanie wysokim). Jeżeli natomiast na wejściu ![]()

jest „0”, to wybrane (za pomocą wejść adresowych) wyjście przyjmie stan niski.

Układ 74138

Układ 74138 jest demultiplekserem o trzech wejściach adresowych A, B i C (o wadze odpowiednio 20, 21 i 22). Układ posiada trzy wejścia bramkujące: G1 aktywne w [Author ID1: at Thu Dec 13 22:38:00 2001

]stani[Author ID1: at Thu Dec 13 22:38:00 2001

]em[Author ID1: at Thu Dec 13 22:38:00 2001

] wysokim oraz ![]()

i ![]()

aktywne w [Author ID1: at Thu Dec 13 22:38:00 2001

]stani[Author ID1: at Thu Dec 13 22:38:00 2001

]em[Author ID1: at Thu Dec 13 22:38:00 2001

] niskim. Aby wybrane (za pomocą wejść adresowych) wyjście przyjęło stan niski, wszystkie wejścia bramkujące muszą być w stanie aktywnym (G [Author ID1: at Thu Dec 13 22:30:00 2001

]= [Author ID1: at Thu Dec 13 22:30:00 2001

]1, ![]()

[Author ID1: at Thu Dec 13 22:30:00 2001

]= [Author ID1: at Thu Dec 13 22:30:00 2001

]![]()

[Author ID1: at Thu Dec 13 22:30:00 2001

]= [Author ID1: at Thu Dec 13 22:30:00 2001

]0). Każda inna kombinacja stanów wejść bramkujących powoduje, że wszystkie wyjścia ![]()

są nieaktywne (znajdują się w stanie wysokim). Dzięki dużej liczbie wejść bramkujących układ jest bardzo często stosowany w dekoderach adresów.

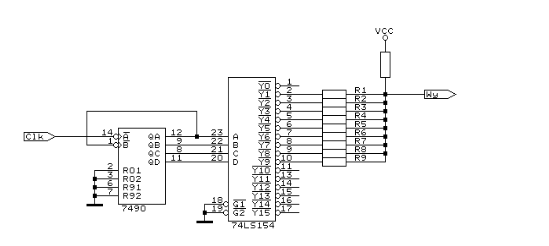

Układ 74154

Układ 74154 jest demultiplekserem o czterech wejściach adresowych A, B, C i D (o wadze odpowiednio 20, 21, 22 i 23). Układ posiada dwa wejścia bramkujące ![]()

i ![]()

, aktywne w [Author ID1: at Thu Dec 13 22:39:00 2001

]stani[Author ID1: at Thu Dec 13 22:39:00 2001

]em[Author ID1: at Thu Dec 13 22:39:00 2001

] niskim. Aby wybrane (za pomocą wejść adresowych) wyjście przyjęło stan niski, wszystkie wejścia bramkujące muszą być w stanie (![]()

[Author ID1: at Thu Dec 13 22:33:00 2001

]= [Author ID1: at Thu Dec 13 22:33:00 2001

]![]()

[Author ID1: at Thu Dec 13 22:34:00 2001

]= [Author ID1: at Thu Dec 13 22:34:00 2001

]0). Każda inna kombinacja stanów wejść bramkujących powoduje, że wszystkie wyjścia ![]()

są nieaktywne (znajdują się w stanie wysokim).

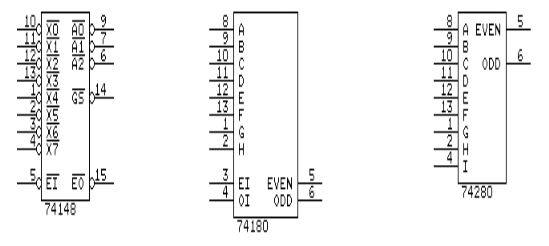

Kodery i generatory parzystości

Wśród pozostałych układów znajduje się wiele interesujących rozwiązań, które będą przydatne do tworzenia układów w dalszych rozdziałach. Należą do nich kodery priorytetowe 74148 i 74348 oraz układy kontroli parzystości 74180 i 74280. Wyprowadzenia tych układów ilustruje rysunek 2.6.[Author ID1: at Thu Dec 13 22:40:00 2001

] [Author ID1: at Thu Dec 13 22:40:00 2001

][Author ID1: at Thu Dec 13 22:40:00 2001

][Author ID1: at Thu Dec 13 22:40:00 2001

][Author ID1: at Thu Dec 13 22:40:00 2001

][Author ID1: at Thu Dec 13 22:40:00 2001

]Rysunek [Author ID1: at Thu Dec 13 22:40:00 2001

]6[Author ID1: at Thu Dec 13 22:40:00 2001

][Author ID1: at Thu Dec 13 22:40:00 2001

].[Author ID1: at Thu Dec 13 22:40:00 2001

]

Rysunek 2.6. [Author ID1: at Thu Dec 13 22:41:00 2001

][Author ID1: at Thu Dec 13 22:41:00 2001

][Author ID1: at Thu Dec 13 22:41:00 2001

][Author ID1: at Thu Dec 13 22:41:00 2001

]6[Author ID1: at Thu Dec 13 22:41:00 2001

][Author ID1: at Thu Dec 13 22:41:00 2001

]. [Author ID1: at Thu Dec 13 22:41:00 2001

]Wyprowadzenia koderów i generatorów parzystości

Kodery priorytetowe 74148 i 74348

Układ 74148 jest koderem priorytetowym o 8 wejściach informacyjnych ![]()

i 3 wyjściach adresowych ![]()

. Ma on ponadto wejście bramkujące ![]()

, a także wyjścia ![]()

i ![]()

, informujące o stanie układu. Wszystkie te sygnały są aktywne w [Author ID1: at Thu Dec 13 22:59:00 2001

]stani[Author ID1: at Thu Dec 13 22:59:00 2001

]em[Author ID1: at Thu Dec 13 22:59:00 2001

] niskim. Jeżeli na wejściu ![]()

jest „1”, to układ jest zablokowany, a wszystkie wyjścia (![]()

,![]()

i ![]()

) są także w stanie „1”. Układ pracuje, gdy na wejściu ![]()

jest „0”. Wówczas stan wyjść zależy od stanu wejść informacyjnych. Jeżeli na każdym z nich jest „1”, to wyjścia ![]()

i ![]()

są w stanie wysokim, natomiast ![]()

—[Author ID1: at Thu Dec 13 23:00:00 2001

]-[Author ID1: at Thu Dec 13 23:00:00 2001

] w niskim. Jeżeli natomiast jedno z wejść ![]()

jest w stanie niskim, to jego numer przekazywany jest na wyjścia ![]()

. Jednocześnie wyjście ![]()

[Author ID1: at Thu Dec 13 23:01:00 2001

]przyjmuje stan niski, a ![]()

—[Author ID1: at Thu Dec 13 23:01:00 2001

]-[Author ID1: at Thu Dec 13 23:01:00 2001

] wysoki.

Z przedstawionego opisu wynika, że wyjście ![]()

informuje o pojawieniu się stanu aktywnego na wejściach ![]()

. Natomiast wyjście ![]()

można wykorzystać do dołączenia następnych układów 74148, gdyby istniała potrzeba zakodowania większej liczby wejść niż 8. Wówczas wyjście to dołącza się do wejścia ![]()

następnego układu.

Dzięki wbudowanemu mechanizmowi kontroli priorytetów dopuszcza się, aby więcej niż jedno wejście ![]()

było aktywne. Wówczas ze wszystkich wejść aktywnych wybiera się to, które ma najwyższy priorytet. W układach 74148 i 74348 jest to wejście o najniższym numerze.

W układzie 74348 wyjścia adresowe są trójstanowe. Znajdują się one w stanie wysokiej impedancji, gdy na wejściu ![]()

jest „1”, lub gdy wszystkie wejścia informacyjne są nieaktywne. Innymi słowy, wyjścia adresowe przekazują informację tylko wówczas, gdy układ koduje adres wybranego wejścia informacyjnego.

Układy kontroli parzystości 74180 i 74280

Układy kontroli parzystości pozwalają generować i sprawdzać bit parzystości. Można je stosować w modułach pamięci, w których istnieje potrzeba ciągłego sprawdzania poprawności przechowywanej informacji.

Układ 74180 ma 8 wejść informacyjnych A - [Author ID1: at Thu Dec 13 23:04:00 2001

]-[Author ID1: at Thu Dec 13 23:04:00 2001

]H oraz [Author ID1: at Thu Dec 13 19:33:00 2001

] [Author ID1: at Thu Dec 13 19:33:00 2001

]dwa wejścia sterujące EI i OI, służące do

-->

zadawania [Author:EK]

[Author ID1: at Thu Dec 13 23:06:00 2001

]stanu wejściowego (EI —[Author ID1: at Thu Dec 13 23:05:00 2001

]-[Author ID1: at Thu Dec 13 23:05:00 2001

] parzysty, OI —[Author ID1: at Thu Dec 13 23:05:00 2001

]-[Author ID1: at Thu Dec 13 23:05:00 2001

] nieparzysty). Jeżeli na wejściach informacyjnych liczba bitów o wartości „1” jest parzysta, to wyjścia EVEN i ODD powielają stan wejść odpowiednio EI i OI. Jeżeli natomiast liczba „1” jest nieparzysta, wyjście EVEN powiela stan sygnału OI, a ODD —[Author ID1: at Thu Dec 13 23:07:00 2001

]-[Author ID1: at Thu Dec 13 23:07:00 2001

] EI. Wyjątkiem jest sytuacja, gdy oba wejścia EI i OI mają taki sam stan logiczny. Wówczas wyjścia EVEN i ODD przyjmują jednocześnie stan przeciwny do stanu wejść.

Układ 74280 nie ma wejść sterujących, posiada natomiast 9 wejść informacyjnych A - [Author ID1: at Thu Dec 13 23:08:00 2001

]-[Author ID1: at Thu Dec 13 23:07:00 2001

]I. Jeżeli liczba bitów o wartości „1” na wejściach jest parzysta, to wyjście EVEN przyjmuje stan „1”, a ODD —[Author ID1: at Thu Dec 13 23:08:00 2001

]-[Author ID1: at Thu Dec 13 23:08:00 2001

] „0”. Jeśli natomiast liczba „1” jest nieparzysta, to wyjście EVEN przyjmuje wartość „0”, natomiast ODD —[Author ID1: at Thu Dec 13 23:08:00 2001

]-[Author ID1: at Thu Dec 13 23:08:00 2001

] „1”. Wybrane wejście informacyjne można więc użyć jako wejście sterujące.

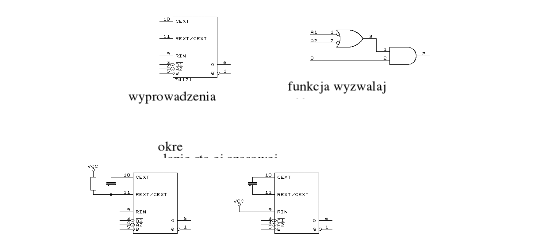

Układy czasowe

Układy czasowe można zastosować w wielu przypadkach. Mogą one pełnić m. [Author ID1: at Thu Dec 13 23:20:00 2001

]in. funkcje generatorów fali prostokątnej o zadanej częstotliwości lub sygnałów o zadanym czasie trwania. Przy użyciu układów czasowych można też porównywać częstotliwość przebiegu wejściowego z zadaną wartością.

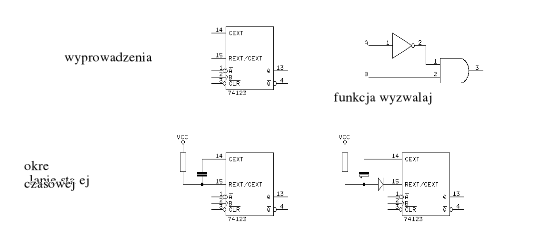

Układ 74121

Układ 74121 jest monostabilnym przerzutnikiem, który może być wyzwolony zboczem narastającym lub opadającym zależnie od wyboru wejścia wyzwalającego. Układ można wyzwolić zboczem narastającym na wejściu B, jeżeli na co najmniej jednym z wejść A1 lub A2 jest stan niski. Natomiast wyzwolenie zboczem opadającym jest możliwe przy użyciu wejść A1 lub A2, o ile na wejściu B jest stan wysoki. Wejście B zawiera ponadto układ Schmitta, dzięki któremu szybkość narastania sygnału wejściowego może wynosić nawet 1 V/s, podczas gdy na pozostałych wejściach —[Author ID1: at Thu Dec 13 23:22:00 2001

]-[Author ID1: at Thu Dec 13 23:22:00 2001

] 1 μV/s. Czas trwania impulsu wyjściowego nie zależy od sposobu wyzwolenia, a tylko od wartości dołączonego do układu opornika RT i kondensatora CT użytych do określenia stałej czasowej. Czas ten może wynosić od 40 ns do 40 s i można obliczyć go według następującego wzoru:

![]()

Ze względu na obecność w układzie opornika wewnętrznego o wartości około 2 kΩ dołączanie elementów zewnętrznych nie jest konieczne, a czas tw wynosi wówczas 30 ns. Czas ten można wydłużyć przez dołączenie kondensatora. Rysunek 2.7 [Author ID1: at Thu Dec 13 23:25:00 2001

][Author ID1: at Thu Dec 13 23:25:00 2001

][Author ID1: at Thu Dec 13 23:25:00 2001

][Author ID1: at Thu Dec 13 23:25:00 2001

][Author ID1: at Thu Dec 13 23:25:00 2001

]Rysunek [Author ID1: at Thu Dec 13 23:25:00 2001

]7[Author ID1: at Thu Dec 13 23:25:00 2001

][Author ID1: at Thu Dec 13 23:25:00 2001

] [Author ID1: at Thu Dec 13 23:25:00 2001

]ilustruje opis wyprowadzeń układu oraz funkcję logiczną wejść wyzwalających, a także sposoby dołączenia opornika i kondensatora.

Rysunek 2.7. [Author ID1: at Thu Dec 13 23:26:00 2001

][Author ID1: at Thu Dec 13 23:26:00 2001

][Author ID1: at Thu Dec 13 23:26:00 2001

][Author ID1: at Thu Dec 13 23:26:00 2001

]7[Author ID1: at Thu Dec 13 23:26:00 2001

][Author ID1: at Thu Dec 13 23:26:00 2001

]. [Author ID1: at Thu Dec 13 23:26:00 2001

]Układ 74121

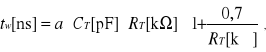

Układ 74123

Układ 74123 zawiera dwa identyczne i niezależne od siebie przerzutniki monostabilne. Od przerzutnika w [Author ID1: at Thu Dec 13 23:31:00 2001

]układzie[Author ID1: at Thu Dec 13 23:31:00 2001

]u[Author ID1: at Thu Dec 13 23:31:00 2001

] 74121 różnią się one m. [Author ID1: at Thu Dec 13 23:30:00 2001

]in. tym, że wyzwolenie układu w czasie generowania impulsu powoduje wydłużenie

-->

go[Author:EK]

[Author ID1: at Thu Dec 13 23:34:00 2001

] o czas tw od chwili tego wyzwolenia. Można także skrócić czas trwania impulsu wyjściowego, używając wejścia zerującego. Sposób ustalenia czasu tw zależy od rodzaju kondensatora

-->

(rys.). [Author:EK]

[Author ID1: at Thu Dec 13 23:38:00 2001

]Dla kondensatora zwykłego korzystamy z zależności:

przy czym a [Author ID1: at Thu Dec 13 23:41:00 2001

]= [Author ID1: at Thu Dec 13 23:41:00 2001

]0,32, RT [Author ID1: at Thu Dec 13 23:41:00 2001

]= [Author ID1: at Thu Dec 13 23:41:00 2001

]5-50 kΩ, a CT [Author ID1: at Thu Dec 13 23:42:00 2001

]≥ [Author ID1: at Thu Dec 13 23:42:00 2001

]1000 pF (dla mniejszych wartości kondensatorów tw należy odczytać z wykresów). W przypadku kondensatora elektrolitycznego należy dodatkowo dołączyć diodę

-->

(rys.), [Author:EK]

[Author ID1: at Thu Dec 13 23:47:00 2001

]a współczynnik a [Author ID1: at Thu Dec 13 23:43:00 2001

]= [Author ID1: at Thu Dec 13 23:43:00 2001

]0,28. Maksymalna wartość RT wynosi wówczas 30 [Author ID1: at Thu Dec 13 19:33:00 2001

] [Author ID1: at Thu Dec 13 19:33:00 2001

]kΩ.

Rysunek 2.8.[Author ID1: at Thu Dec 13 23:48:00 2001

][Author ID1: at Thu Dec 13 23:48:00 2001

][Author ID1: at Thu Dec 13 23:48:00 2001

][Author ID1: at Thu Dec 13 23:48:00 2001

][Author ID1: at Thu Dec 13 23:48:00 2001

]Rysunek [Author ID1: at Thu Dec 13 23:48:00 2001

]8[Author ID1: at Thu Dec 13 23:48:00 2001

][Author ID1: at Thu Dec 13 23:48:00 2001

] ilustruje opis wyprowadzeń jednego przerzutnika i funkcji wyzwalającej oraz sposoby dołączenia opornika i kondensatora.

Rysunek 2.8. [Author ID1: at Thu Dec 13 23:49:00 2001

][Author ID1: at Thu Dec 13 23:49:00 2001

][Author ID1: at Thu Dec 13 23:49:00 2001

][Author ID1: at Thu Dec 13 23:49:00 2001

]8[Author ID1: at Thu Dec 13 23:49:00 2001

][Author ID1: at Thu Dec 13 23:49:00 2001

]. [Author ID1: at Thu Dec 13 23:49:00 2001

]Układ 74123

Układ NE555

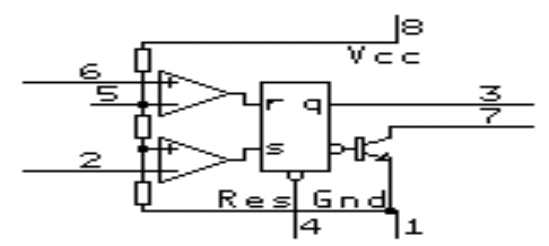

Układ NE555 nie jest układem cyfrowym serii TTL, potrafi jednak współpracować z takimi układami, o ile jest zasilany napięciem 5 V. Strukturę układu ilustruje rysunek 2.9[Author ID1: at Thu Dec 13 23:55:00 2001

] [Author ID1: at Thu Dec 13 23:55:00 2001

][Author ID1: at Thu Dec 13 23:55:00 2001

][Author ID1: at Thu Dec 13 23:55:00 2001

][Author ID1: at Thu Dec 13 23:55:00 2001

][Author ID1: at Thu Dec 13 23:55:00 2001

]Rysunek [Author ID1: at Thu Dec 13 23:55:00 2001

]9[Author ID1: at Thu Dec 13 23:55:00 2001

][Author ID1: at Thu Dec 13 23:55:00 2001

], a funkcje poszczególnych wyprowadzeń

-->

zebrano w tabeli[Author:EK]

[Author ID1: at Thu Dec 13 23:56:00 2001

].

Rysunek 2.9.[Author ID1: at Thu Dec 13 23:56:00 2001

] [Author ID1: at Thu Dec 13 23:56:00 2001

][Author ID1: at Thu Dec 13 23:56:00 2001

][Author ID1: at Thu Dec 13 23:56:00 2001

][Author ID1: at Thu Dec 13 23:56:00 2001

]9[Author ID1: at Thu Dec 13 23:56:00 2001

][Author ID1: at Thu Dec 13 23:56:00 2001

]. [Author ID1: at Thu Dec 13 23:56:00 2001

]Struktura układu NE555

Układ zawiera trzy rezystory o wartości 5 kΩ, dwa komparatory analogowe, przerzutnik i tranzystor. Jeżeli napięcie na wejściu wyzwalającym (2) jest mniejsze niż 1/3 VCC, następuje wpisanie „1” do przerzutnika. Na wyjściu (3) pojawia się stan „1”, natomiast tranzystor nie przewodzi — [Author ID1: at Fri Dec 14 00:01:00 2001

]([Author ID1: at Fri Dec 14 00:01:00 2001

]przez wyprowadzenie ([Author ID1: at Fri Dec 14 00:01:00 2001

]7)[Author ID1: at Fri Dec 14 00:01:00 2001

] nie płynie prąd)[Author ID1: at Fri Dec 14 00:01:00 2001

]. Jeżeli natomiast napięcie na wejściu ([Author ID1: at Fri Dec 14 00:02:00 2001

]6)[Author ID1: at Fri Dec 14 00:02:00 2001

]

przekracza 2/3 VCC, to do przerzutnika wpisuje się „0”. Stan ten pojawia się też na wyjściu (3), a tranzystor przewodzi.

Układ można wykorzystać jako generator pojedynczego impulsu lub generator fali prostokątnej. Oba zastosowania wymagają odpowiedniego dołączenia zewnętrznych oporników i kondensatorów. Przykładowe schematy pokazano na rysunku [Author ID1: at Fri Dec 14 00:04:00 2001

]2.10.[Author ID1: at Fri Dec 14 00:04:00 2001

]rys.[Author ID1: at Fri Dec 14 00:03:00 2001

]

Rysunek 2.10. [Author ID1: at Fri Dec 14 00:04:00 2001

][Author ID1: at Fri Dec 14 00:04:00 2001

][Author ID1: at Fri Dec 14 00:04:00 2001

][Author ID1: at Fri Dec 14 00:04:00 2001

]10[Author ID1: at Fri Dec 14 00:04:00 2001

][Author ID1: at Fri Dec 14 00:04:00 2001

]. [Author ID1: at Fri Dec 14 00:04:00 2001

]Przykłady połączeń układu NE555

Pierwszy układ to generator pojedynczego impulsu. Wyzwolenie układu następuje na [Author ID1: at Fri Dec 14 19:13:00 2001

]w[Author ID1: at Fri Dec 14 19:13:00 2001

]skutek pojawienia się stanu „0” na wejściu ([Author ID1: at Fri Dec 14 00:07:00 2001

]We)[Author ID1: at Fri Dec 14 00:07:00 2001

]. Powoduje to ustawienie wewnętrznego przerzutnika i zatkanie tranzystora, dzięki czemu kondensator C2 ładuje się przez opornik R3. W tym czasie na wyjściu ([Author ID1: at Fri Dec 14 00:07:00 2001

]Wy)[Author ID1: at Fri Dec 14 00:07:00 2001

] jest stan wysoki, czyli generowany jest impuls o czasie trwania zależnym od wartości przyłączonego opornika i kondensatora. Gdy napięcie na kondensatorze wzrośnie do 2/3 VCC, następuje wyzerowanie przerzutnika i zakończenie generowania impulsu, a tranzystor wprowadzony w stan przewodzenia rozładowuje kondensator.

Drugi układ to generator fali prostokątnej. Po włączeniu zasilania napięcie na kondensatorze wynosi około 0 V, a więc nastepuje wyzwolenie układu NE555. Na wyjściu pojawia się „1”, a kondensator C1 ładuje się poprzez oporniki R1 i R2. Gdy napięcie na kondensatorze wzrośnie powyżej 2/3 VCC, następuje wyzerowanie przerzutnika. Na wyjściu pojawia się „0”, a kondensator rozładowuje się poprzez opornik R2 aż do chwili, gdy napięcie spadnie poniżej 1/3 VCC i nastąpi ponowne wyzwolenie układu.

Przerzutniki

Przerzutniki są podstawowymi układami zapamiętywania informacji. Wyróżnia się:

przerzutniki asynchroniczne, w których zmiana stanu wejść może spowodować natychmiastową zmianę stanu wyjść;[Author ID1: at Fri Dec 14 00:08:00 2001 ]

,[Author ID1: at Fri Dec 14 00:08:00 2001 ]przerzutniki synchroniczne, w których stan wyjść może ulec zmianie wyłącznie w określonych chwilach, wyznaczonych aktywnym zboczem sygnału taktującego.

W dalszej części książki uwzględniany [Author ID1: at Fri Dec 14 00:13:00 2001

]wykorzystywany [Author ID1: at Fri Dec 14 00:13:00 2001

]będzie tylko przerzutnik synchroniczny typu D.

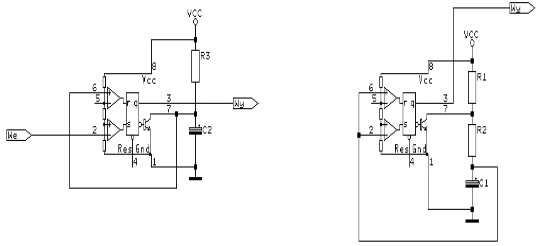

Układ 7474

Układ 7474 zawiera dwa identyczne i całkowicie niezależne od siebie przerzutniki synchroniczne typu D. Każdy z nich [Author ID1: at Thu Dec 13 19:33:00 2001

] [Author ID1: at Thu Dec 13 19:33:00 2001

]ma wejście informacyjne D, którego[Author ID1: at Fri Dec 14 00:14:00 2001

] stan jest zapamiętywany w czasie trwania narastającego zbocza sygnału taktującego (zegarowego) CLK. Przerzutnik posiada dwa wyjścia: proste Q i zanegowane ![]()

, jest także wyposażony w dwa wejścia asynchroniczne: zerujące ![]()

i ustawiające ![]()

, aktywne stanem niskim. Podanie „0” na któreś z tych wejść powoduje natychmiastowe wpisanie do przerzutnika stanu „0” lub „1” niezależnie od jego poprzedniej zawartości. Jednoczesne podanie „0” na oba wejścia asynchroniczne jest zabronione —[Author ID1: at Fri Dec 14 00:15:00 2001

]-[Author ID1: at Fri Dec 14 00:15:00 2001

] reakcja układu nie jest wówczas zdefiniowana. Dzięki istnieniu tych wejść układ może także pełnić funkcję przerzutnika asynchronicznego typu RS.

Rysunek 2.1[Author ID1: at Fri Dec 14 00:15:00 2001

]1. [Author ID1: at Fri Dec 14 00:15:00 2001

][Author ID1: at Fri Dec 14 00:15:00 2001

][Author ID1: at Fri Dec 14 00:15:00 2001

][Author ID1: at Fri Dec 14 00:15:00 2001

]11[Author ID1: at Fri Dec 14 00:15:00 2001

][Author ID1: at Fri Dec 14 00:15:00 2001

]. [Author ID1: at Fri Dec 14 00:15:00 2001

]Wyprowadzenia przerzutnika 7474

Liczniki

Liczniki są układami sekwencyjnymi, służącymi do zliczania impulsów wejściowych. Wystąpienie aktywnego zbocza sygnału wejściowego powoduje zwiększenie zawartości licznika o 1. Są też dostępne liczniki, w których można wybrać kierunek zliczania (zwiększanie lub zmniejszanie zawartości).

Wśród układów scalonych pełniących funkcję liczników wyróżniamy:

liczniki asynchroniczne,

liczniki synchroniczne jednokierunkowe,

liczniki synchroniczne dwukierunkowe.

Liczniki asynchroniczne

Licznik asynchroniczny charakteryzuje się tym, że nie wszystkie wejścia zegarowe przerzutników są dołączone do sygnału wejściowego. W związku z tym --> , ze względu na czasy propagacjio sygnałów przez przerzutniki,[Author:EK] [Author ID1: at Fri Dec 14 00:18:00 2001 ] zmiana stanu poszczególnych stopni licznika nie następuje jednocześnie.

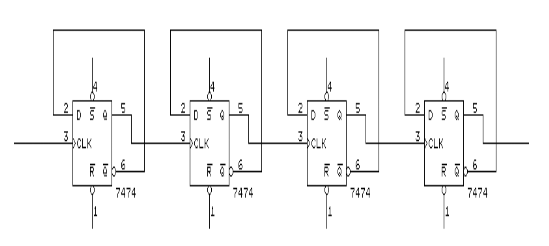

Najprostszy licznik asynchroniczny można zbudować z przerzutników synchronicznych typu D, łącząc wyjścia Q z wejściami zegarowymi CLK następnych stopni. Wyjście ![]()

łączy się z wejściem D tego samego przerzutnika. Każdy stopień takiego licznika jest zatem dzielnikiem częstotliwości wejściowej przez 2 (licznikiem modulo 2). Rysunek 2.12 [Author ID1: at Fri Dec 14 00:20:00 2001

][Author ID1: at Fri Dec 14 00:19:00 2001

][Author ID1: at Fri Dec 14 00:19:00 2001

][Author ID1: at Fri Dec 14 00:19:00 2001

][Author ID1: at Fri Dec 14 00:19:00 2001

]Rysunek [Author ID1: at Fri Dec 14 00:19:00 2001

]12[Author ID1: at Fri Dec 14 00:19:00 2001

][Author ID1: at Fri Dec 14 00:19:00 2001

] [Author ID1: at Fri Dec 14 00:19:00 2001

]ilustruje strukturę takiego licznika.

Rysunek 2.12. [Author ID1: at Fri Dec 14 00:20:00 2001

][Author ID1: at Fri Dec 14 00:20:00 2001

][Author ID1: at Fri Dec 14 00:20:00 2001

][Author ID1: at Fri Dec 14 00:20:00 2001

]12[Author ID1: at Fri Dec 14 00:20:00 2001

][Author ID1: at Fri Dec 14 00:20:00 2001

]. [Author ID1: at Fri Dec 14 00:20:00 2001

]Licznik asynchroniczny zbudowany z przerzutników synchronicznych typu D

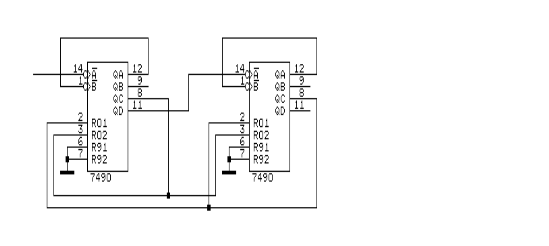

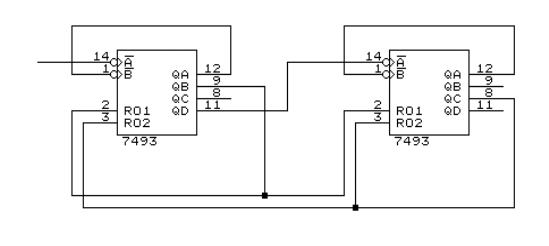

Istnieją także gotowe układy scalone, realizujące funkcje liczników asynchronicznych. Są to układy:

7490 (licznik mod 2 mod 5),

7492 (mod 2 mod 6),

7493 (mod 2 mod 8).

Rysunek 2.13. [Author ID1: at Fri Dec 14 00:22:00 2001

][Author ID1: at Fri Dec 14 00:22:00 2001

][Author ID1: at Fri Dec 14 00:22:00 2001

][Author ID1: at Fri Dec 14 00:22:00 2001

]13[Author ID1: at Fri Dec 14 00:22:00 2001

][Author ID1: at Fri Dec 14 00:22:00 2001

]. [Author ID1: at Fri Dec 14 00:22:00 2001

]Scalone liczniki asynchroniczne

Liczniki te są wykonane jako dwa niezależne liczniki. Jeden z nich jest zawsze licznikiem modulo 2. Ma on wejście zegarowe ![]()

oraz wyjście QA. Sygnał ![]()

jest wejściem zegarowym do drugiego licznika, którego wyjściami są [Author ID1: at Fri Dec 14 00:24:00 2001

] to [Author ID1: at Fri Dec 14 00:24:00 2001

]QB, QC oraz QD. Wejścia zegarowe reagują na zbocze opadające. Wejścia R01 i R02 służą do asynchronicznego wyzerowania całego licznika. Jeżeli oba te sygnały mają stan „1” logicznej, to wyzerowanie licznika następuje natychmiast, czyli asynchronicznie względem przebiegu zegarowego. Licznik 7490 ma dodatkowo wejścia R91 i R92, służące do ustawienia licznika w stan maksymalny „9”.

W zależności od połączenia sygnałów licznik 7490 może pracować w kodzie 8421 (kod BCD) lub w kodzie 5421. Podobnie licznik 7492 może pracować w kodzie 6421 lub 6321, natomiast 7493 pracuje zawsze w naturalnym kodzie dwójkowym (8421).

Liczniki synchroniczne

Przyglądając się strukturze licznika synchronicznego można stwierdzić, [Author ID1: at Thu Dec 13 19:33:00 2001

] [Author ID1: at Thu Dec 13 19:33:00 2001

]że wejścia zegarowe wszystkich jego przerzutników są połączone razem. Dzięki temu zmiana stanu wszystkich elementów licznika następuje w tym samym momencie. Dzieje się tak oczywiście pod warunkiem, że częstotliwość sygnału taktującego nie jest za duża. W układach synchronicznych zakłada się jednak, że warunek ten jest zawsze spełniony, gdyż w przeciwnym przypadku nie można zagwarantować poprawnej i stabilnej pracy układu.

Wejścia sterujące liczników synchronicznych mogą być zarówno synchroniczne, jak i asynchroniczne. Stan aktywny na wejściu asynchronicznym wywołuje natychmiast [Author ID1: at Fri Dec 14 00:28:00 2001

]określony skutek (np. zerowanie licznika),[Author ID1: at Fri Dec 14 00:29:00 2001

] natychmiast, [Author ID1: at Fri Dec 14 00:29:00 2001

]natomiast na wejściu synchronicznym —[Author ID1: at Fri Dec 14 00:27:00 2001

]-[Author ID1: at Fri Dec 14 00:27:00 2001

] dopiero w chwili wystąpienia aktywnego zbocza sygnału zegarowego. W prezentowanych licznikach synchronicznych jest to zawsze zbocze narastające.

Cenną zaletą liczników synchronicznych jest możliwość wpisania do układu pewnej wartości początkowej. Dzięki temu skrócenie cyklu licznika można osiągnąć nie tylko przez ograniczenie od góry, lecz także od dołu.

Wśród liczników synchronicznych wyróżnia się:

liczniki jednokierunkowe, w których kolejne impulsy zegarowe powodują inkrementację zawartości układu;[Author ID1: at Fri Dec 14 00:30:00 2001 ]

,[Author ID1: at Fri Dec 14 00:30:00 2001 ]liczniki dwukierunkowe, w których można wybrać kierunek zliczania.

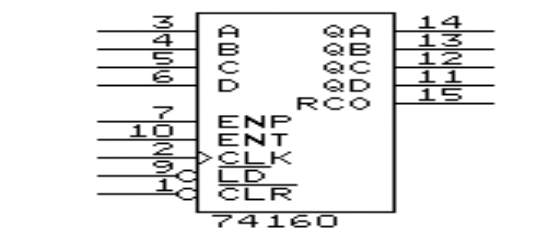

Liczniki synchroniczne jednokierunkowe

Rodzina liczników synchronicznych jednokierunkowych obejmuje cztery układy, różniące się stanem maksymalnym (10 w l[Author ID1: at Fri Dec 14 00:32:00 2001

]iczniku dziesiętnym lub 16 w dwójkowym) oraz rodzajem wejścia zerującego (synchroniczne lub asynchroniczne). Ważniejsze cechy układów podaje

-->

tabela.[Author:EK]

[Author ID1: at Fri Dec 14 00:32:00 2001

]

Pomimo wymienionych różnic, wszystkie układy mają takie same wyprowadzenia (rysunek 2.14[Author ID1: at Fri Dec 14 00:33:00 2001

][Author ID1: at Fri Dec 14 00:33:00 2001

][Author ID1: at Fri Dec 14 00:33:00 2001

][Author ID1: at Fri Dec 14 00:33:00 2001

][Author ID1: at Fri Dec 14 00:33:00 2001

]Rysunek [Author ID1: at Fri Dec 14 00:33:00 2001

]14[Author ID1: at Fri Dec 14 00:33:00 2001

][Author ID1: at Fri Dec 14 00:33:00 2001

]). [Author ID1: at Thu Dec 13 19:33:00 2001

] [Author ID1: at Thu Dec 13 19:33:00 2001

]Wejścia A, B, C i D to wejścia służące do podnia początkowej zawartości licznika. Zawartość ta wpisywana jest synchronicznie z sygnałem zegarowym CLK, jeżeli na wejściu ![]()

jest „0”. Do zerowania licznika [Author ID1: at Fri Dec 14 00:34:00 2001

](zależ[Author ID1: at Fri Dec 14 00:34:00 2001

]z[Author ID1: at Fri Dec 14 00:34:00 2001

]nie od układu synchronicznego lub asynchronicznego) licznika [Author ID1: at Fri Dec 14 00:34:00 2001

]służy wejście ![]()

, także aktywne w [Author ID1: at Fri Dec 14 00:35:00 2001

]stani[Author ID1: at Fri Dec 14 00:35:00 2001

]em[Author ID1: at Fri Dec 14 00:35:00 2001

] niskim. Zerowanie i wpis wartości początkowej są niezależne od stanu wejść ENT i ENC, które jednak muszą być aktywne (stan „1”), aby licznik mógł zliczać w takt zmian sygnału zegarowego.

Rysunek 2.14. [Author ID1: at Fri Dec 14 00:36:00 2001

][Author ID1: at Fri Dec 14 00:35:00 2001

][Author ID1: at Fri Dec 14 00:35:00 2001

][Author ID1: at Fri Dec 14 00:35:00 2001

]14[Author ID1: at Fri Dec 14 00:35:00 2001

][Author ID1: at Fri Dec 14 00:35:00 2001

]. [Author ID1: at Fri Dec 14 00:35:00 2001

]Wyprowadzenia liczników synchronicznych jednokierunkowych

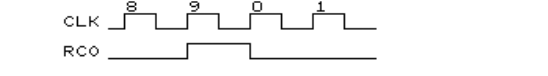

Wyjścia QA, QB, QC i QD informują o aktualnej zawartości licznika. Jeżeli jest to wartość maksymalna (zależnie od układu 9 lub 15), to dodatkowo sygnał RCO ustawiany jest w stan wysoki zgodnie z przebiegiem czasowym, który ilustruje rysunek 2.15.[Author ID1: at Fri Dec 14 00:37:00 2001

] [Author ID1: at Fri Dec 14 00:37:00 2001

][Author ID1: at Fri Dec 14 00:37:00 2001

][Author ID1: at Fri Dec 14 00:37:00 2001

][Author ID1: at Fri Dec 14 00:37:00 2001

]Rysunek [Author ID1: at Fri Dec 14 00:37:00 2001

]15[Author ID1: at Fri Dec 14 00:37:00 2001

][Author ID1: at Fri Dec 14 00:37:00 2001

].[Author ID1: at Fri Dec 14 00:37:00 2001

]

Rysunek 2.15. [Author ID1: at Fri Dec 14 00:38:00 2001

][Author ID1: at Fri Dec 14 00:38:00 2001

][Author ID1: at Fri Dec 14 00:38:00 2001

][Author ID1: at Fri Dec 14 00:38:00 2001

]15[Author ID1: at Fri Dec 14 00:38:00 2001

][Author ID1: at Fri Dec 14 00:38:00 2001

]. [Author ID1: at Fri Dec 14 00:38:00 2001

]Przebieg czasowy na wyjściu RCO

Liczniki synchroniczne dwukierunkowe (rewersyjne)

Rodzina liczników synchronicznych dwukierunkowych obejmuje dwa układy z wyborem kierunku zliczania oraz dwa z rozdzielonymi wejściami zegarowymi dla obu kierunków. W każdym układzie wejścia wpisujące i zerujące są asynchroniczne. Cechy poszczególnych układów zebrano --> w tabeli.[Author:EK] [Author ID1: at Fri Dec 14 09:31:00 2001 ]

Jak łatwo się domyślić, układy z wejściem wyboru mają nieco inne wyprowadzenia niż układy z wejściami rozdzielonymi. Rozkład wyprowadzeń tych układów ilustruje rysunek 2.16.[Author ID1: at Fri Dec 14 09:32:00 2001

][Author ID1: at Fri Dec 14 09:32:00 2001

][Author ID1: at Fri Dec 14 09:32:00 2001

][Author ID1: at Fri Dec 14 09:32:00 2001

][Author ID1: at Fri Dec 14 09:32:00 2001

]Rysunek [Author ID1: at Fri Dec 14 09:32:00 2001

]16[Author ID1: at Fri Dec 14 09:32:00 2001

][Author ID1: at Fri Dec 14 09:32:00 2001

].[Author ID1: at Fri Dec 14 09:32:00 2001

]

Rysunek 2.16. [Author ID1: at Fri Dec 14 09:32:00 2001

][Author ID1: at Fri Dec 14 09:32:00 2001

][Author ID1: at Fri Dec 14 09:32:00 2001

][Author ID1: at Fri Dec 14 09:32:00 2001

]16[Author ID1: at Fri Dec 14 09:32:00 2001

][Author ID1: at Fri Dec 14 09:32:00 2001

]. [Author ID1: at Fri Dec 14 09:32:00 2001

]Wyprowadzenia liczników synchronicznych dwukierunkowych

We wszystkich układach wyprowadzenia A, B, C i D to wejścia służące do podania wartości początkowej, wpisywanej, gdy wejście ![]()

jest w stanie „0” niezależnie od stanu pozostałych sygnałów. Sygnały QA, QB, QC i QD to wyjścia informujące o aktualnej zawartości licznika.

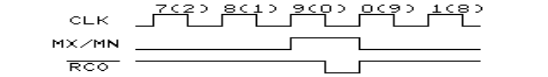

W układach 74190 i 74191 wejście ![]()

służy do wyboru kierunku zliczania („0” —[Author ID1: at Fri Dec 14 09:34:00 2001

]-[Author ID1: at Fri Dec 14 09:34:00 2001

] do góry, „1” —[Author ID1: at Fri Dec 14 09:34:00 2001

]-[Author ID1: at Fri Dec 14 09:34:00 2001

] w dół) w takt sygnału zegarowego CLK. Zliczanie jest możliwe tylko wtedy, gdy na wejściu ![]()

jest stan „0”. Jeżeli zawartość licznika jest równa stanowi maksymalnemu (9 lub 15) przy zliczaniu w górę lub wynosi „0” przy zliczaniu w dół, to wyjście MX/MN przyjmuje stan „1” przez okres sygnału zegarowego. Jeżeli MX/MN [Author ID1: at Fri Dec 14 09:36:00 2001

]= [Author ID1: at Fri Dec 14 09:36:00 2001

]1 oraz CLK [Author ID1: at Fri Dec 14 09:36:00 2001

]= [Author ID1: at Fri Dec 14 09:36:00 2001

]0, to wyjście ![]()

przyjmuje stan „0”. Można powiedzieć, [Author ID1: at Thu Dec 13 19:33:00 2001

] [Author ID1: at Thu Dec 13 19:33:00 2001

]że MX/MN jest w stanie aktywnym przez cały okres sygnału zegarowego, natomiast ![]()

tylko w drugiej połowie tego okresu. Zachowanie sygnałów wyjściowych ilustruje rysunek 2.17.[Author ID1: at Fri Dec 14 09:36:00 2001

][Author ID1: at Fri Dec 14 09:36:00 2001

][Author ID1: at Fri Dec 14 09:36:00 2001

][Author ID1: at Fri Dec 14 09:36:00 2001

][Author ID1: at Fri Dec 14 09:36:00 2001

]Rysunek [Author ID1: at Fri Dec 14 09:36:00 2001

]17[Author ID1: at Fri Dec 14 09:36:00 2001

][Author ID1: at Fri Dec 14 09:36:00 2001

].[Author ID1: at Fri Dec 14 09:36:00 2001

]

Rysunek 2.17. [Author ID1: at Fri Dec 14 09:37:00 2001

][Author ID1: at Fri Dec 14 09:37:00 2001

][Author ID1: at Fri Dec 14 09:37:00 2001

][Author ID1: at Fri Dec 14 09:37:00 2001

]17[Author ID1: at Fri Dec 14 09:37:00 2001

][Author ID1: at Fri Dec 14 09:37:00 2001

]. [Author ID1: at Fri Dec 14 09:37:00 2001

]Przebiegi wyjściowe liczników 74190 i 74191

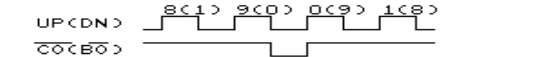

Układy 74192 i 74193 mają rozdzielone wejścia zegarowe dla obu kierunków zliczania: UP w górę i DN w dół. Odpowiadają im wyjścia ![]()

oraz ![]()

, aktywne w [Author ID1: at Fri Dec 14 09:39:00 2001

]stani[Author ID1: at Fri Dec 14 09:39:00 2001

]em[Author ID1: at Fri Dec 14 09:39:00 2001

] niskim. Wyjście ![]()

jest aktywne, gdy w liczniku jest wartość maksymalna (9 lub 15). Podobnie wyjście ![]()

jest aktywne, jeżeli licznik zawiera 0 (rysunek 2.18[Author ID1: at Fri Dec 14 09:40:00 2001

][Author ID1: at Fri Dec 14 09:40:00 2001

][Author ID1: at Fri Dec 14 09:40:00 2001

][Author ID1: at Fri Dec 14 09:40:00 2001

][Author ID1: at Fri Dec 14 09:40:00 2001

][Author ID1: at Fri Dec 14 09:40:00 2001

]Rysunek [Author ID1: at Fri Dec 14 09:40:00 2001

]18[Author ID1: at Fri Dec 14 09:40:00 2001

][Author ID1: at Fri Dec 14 09:40:00 2001

]). Liczniki zawierają też asynchroniczne wejście zerowania CLR, aktywne w [Author ID1: at Fri Dec 14 09:40:00 2001

]stani[Author ID1: at Fri Dec 14 09:40:00 2001

]em[Author ID1: at Fri Dec 14 09:40:00 2001

] wysokim.

Rysunek 2.18. [Author ID1: at Fri Dec 14 09:41:00 2001

][Author ID1: at Fri Dec 14 09:41:00 2001

][Author ID1: at Fri Dec 14 09:41:00 2001

][Author ID1: at Fri Dec 14 09:41:00 2001

]18[Author ID1: at Fri Dec 14 09:41:00 2001

][Author ID1: at Fri Dec 14 09:41:00 2001

]. [Author ID1: at Fri Dec 14 09:41:00 2001

]Przebiegi wyjściowe liczników 74192 i 74193

Bufory i rejestry z wyjściami trójstanowymi

Bufory

Bufory stosuje się przede wszystkim do zwiększania obciążalności wyjść układów większej skali integracji, np. mikroprocesorów, pamięci itp. Dzięki wyjściom trójstanowym można stosować je w złożonych układach zawierających magistrale.

Rysunek 2.19. [Author ID1: at Fri Dec 14 09:43:00 2001

][Author ID1: at Fri Dec 14 09:43:00 2001

][Author ID1: at Fri Dec 14 09:43:00 2001

][Author ID1: at Fri Dec 14 09:43:00 2001

]19[Author ID1: at Fri Dec 14 09:43:00 2001

][Author ID1: at Fri Dec 14 09:43:00 2001

]. [Author ID1: at Fri Dec 14 09:43:00 2001

]Wyprowadzenia buforów trójstanowych

Układ 74244

Układ 74244 jest podwójnym, 4-bitowym buforem z wyjściami trójstanowymi. Ma on dwie grupy wejść (1A i 2A) oraz dwie grupy wyjść (1Y i 2Y). Otwarcie wyjść nastę[Author ID1: at Fri Dec 14 09:44:00 2001

]e[Author ID1: at Fri Dec 14 09:44:00 2001

]puje na [Author ID1: at Fri Dec 14 19:14:00 2001

]w[Author ID1: at Fri Dec 14 19:14:00 2001

]skutek podania stanu „0” na wejście bramkujące ![]()

(grupa 1.[Author ID1: at Sun Dec 16 22:23:00 2001

]) lub ![]()

(grupa 2.[Author ID1: at Sun Dec 16 22:23:00 2001

]). Układ można też stosować jako bufor 8-bitowy, jeżeli oba wejścia bramkujące są połączone. Układ nadaje się do buforowania magistrali adresowej lub sygnałów sterujących mikroprocesora.

Układy 74540 i 74541

Układy 74540 i 74541 są buforami 8-bitowymi z wyjściami trójstanowymi. Układ 74540 powoduje dodatkową zmianę stanu logicznego wszystkich bitów na przeciwny, natomiast 74541 nie ma tej funkcji. Otwarcie wyjść następuje, gdy oba wejścia bramkujące ![]()

i ![]()

znajdują się jednocześnie w stanie niskim. Układy te nadają się m.[Author ID1: at Fri Dec 14 09:45:00 2001

]. [Author ID1: at Fri Dec 14 09:45:00 2001

]in. do buforowania magistrali adresowej mikroprocesora.

Układ 74245

Układ 74245 jest 8-bitowym, dwukierunkowym buforem z wyjściami trójstanowymi. Ma on dwie grupy sygnałów wejścia-wyjścia: A i B. Jeżeli wejście bram[Author ID1: at Fri Dec 14 09:46:00 2001

]kujące ![]()

[Author ID1: at Fri Dec 14 09:46:00 2001

]znajduje się w stanie wysokim, to obie grupy wyjść są w stanie wysokiej impedancji. Jeżeli natomiast na wejście bramkujące podany jest stan „0”, to układ może przesyłać informację przez otwarcie wyjść jednej z grup. Kierunek przesyłu zależy od stanu wejścia wyboru kierunku ![]()

(„1” —[Author ID1: at Fri Dec 14 09:46:00 2001

]-[Author ID1: at Fri Dec 14 09:46:00 2001

] w kierunku A [Author ID1: at Fri Dec 14 09:47:00 2001

]→ [Author ID1: at Fri Dec 14 09:47:00 2001

]B, „0” —[Author ID1: at Fri Dec 14 09:47:00 2001

]-[Author ID1: at Fri Dec 14 09:47:00 2001

] B [Author ID1: at Fri Dec 14 09:47:00 2001

]→ [Author ID1: at Fri Dec 14 09:47:00 2001

]A). Układ nadaje się do buforowania magistrali danych lub jakiegokolwiek innego zbioru sygnałów dwukierunkowych, może też być stosowany jako bufor jednokierunkowy, jeżeli wejście wyboru kierunku ma ustalony poziom logiczny.

Rejestry

Rejestry służą do przechowywania (pamiętania) informacji, najczęściej stanowią więc zbiór przerzutników synchronicznych typu D ze wspólnym wejściem wpisującym. Często spotykane są rejestry z wyjściami trójstanowymi, sterowanymi wspólnym sygnałem. Układy takie są chętnie stosowane w układach mikroprocesorowych, ponieważ mogą być bezpośrednio dołączane do magistrali.

Rysunek 2.20. [Author ID1: at Fri Dec 14 09:48:00 2001

][Author ID1: at Fri Dec 14 09:48:00 2001

][Author ID1: at Fri Dec 14 09:48:00 2001

][Author ID1: at Fri Dec 14 09:48:00 2001

]20[Author ID1: at Fri Dec 14 09:48:00 2001

][Author ID1: at Fri Dec 14 09:48:00 2001

]. [Author ID1: at Fri Dec 14 09:48:00 2001

]Wyprowadzenia rejestrów z wyjściami trójstanowymi

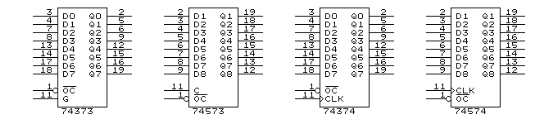

Układy 74373 i 74573

Układy 74373 i 74573 są 8-bitowymi rejestrami zatrzaskowymi z wyjściami trójstanowymi. Gdy wejście wpisujące C jest w stanie „1”, układ pełni funkcję bufora trójstanowego, czyli powiela na wyjściach stan wejść (pod warunkiem, że wyjścia są otwarte). Gdy natomiast sygnał wpisujący jest w stanie „0”, układ przekazuje na wyjścia zapamiętany stan wejść. Jest to ostatni stan, jaki wystąpił przed zmianą poziomu logicznego sygnału wpisującego z „1” na „0”. Otwarcie wyjść trójstanowych następuje, gdy sygnał ![]()

jest w stanie „0”. Układ nadaje się do buforowania magistral adresowych w niektórych mikroprocesorach, szczególnie w tych, które wymagają zapamiętania stanu magistrali adresowej w układach zewnętrznych.

Układy 74374 i 74574

Układy 74374 i 74574 są 8-bitowymi rejestrami z wyjściami trójstanowymi. Gdy na wejściu wpisującym CLK występuje zbocze narastające, układ zapamiętuje stan wejść. Otwarcie wyjść trójstanowych następuje, gdy sygnał ![]()

jest w stanie „0”.

Przykłady

Przykład 1.[Author ID1: at Fri Dec 14 09:50:00 2001 ]

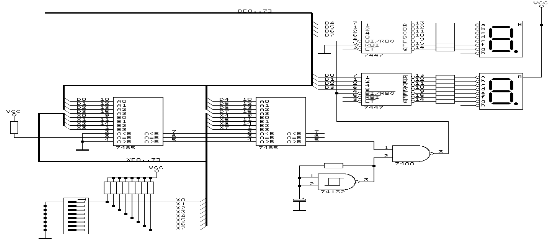

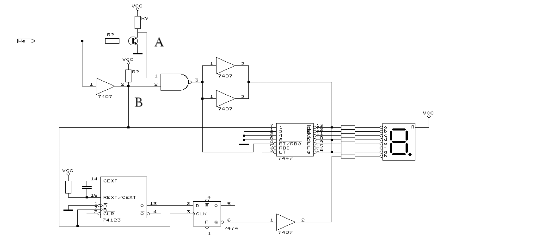

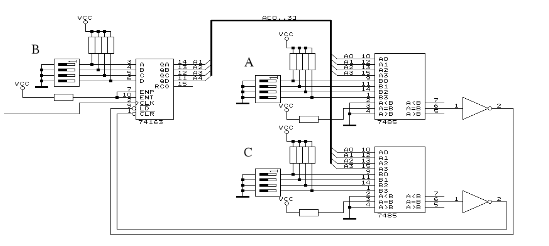

Zaprojektować układ wyświetlający dwucyfrową liczbę dziesiętną. Cyfry kodowane są w kodzie BCD. Jeżeli liczba wejściowa przekroczy wartość 80, wyświetlacz powinien pulsować z częstotliwością kilku Hz. Zero nieznaczące należy wygasić.

Zasadnicza część układu jest odpowiedzialna za wyświetlanie dwóch cyfr. Do jej zbudowania potrzebne są dwa wyświetlacze 7-segmentowe (ze wspólną anodą) wraz ze sterownikami 7447. Układ porównywania liczby wejściowej z liczbą progową (w naszym przykładzie 80) można zrealizować jako zwykły układ kombinacyjny. Rozwiązanie z wykorzystaniem komparatorów 4-bitowych 7485 jest jednak ciekawsze i bardziej przejrzyste. Ponadto można dowolnie ustawić wartość progową —[Author ID1: at Fri Dec 14 09:52:00 2001

]-[Author ID1: at Fri Dec 14 09:52:00 2001

] służą do tego przełączniki podłączone do wejść obu komparatorów. Liczba wejściowa jest większa od wartości progowej, jeżeli zachodzi jeden z poniższych warunków:

cyfra dziesiątek liczby wejściowej jest większa od cyfry dziesiątek wartości progowej;[Author ID1: at Fri Dec 14 09:52:00 2001 ]

,[Author ID1: at Fri Dec 14 09:52:00 2001 ]cyfry dziesiątek są równe, ale cyfra jedności liczby wejściowej jest większa od cyfry jedności wartości progowej.

Pierwszy komparator sprawdza pierwszy z wymienionych warunków. Jeżeli jest on spełniony, na wyjściu A [Author ID1: at Fri Dec 14 09:52:00 2001 ]> [Author ID1: at Fri Dec 14 09:52:00 2001 ]B komparatora pojawi się „1”. Drugi komparator nie musi już porównywać cyfr i przekazuje na wyjście wynik z pierwszego komparatora. Jeżeli natomiast pierwszy warunek nie jest spełniony, to drugi komparator sprawdza drugi warunek i ustawia swoje wyjścia w zależności od wyniku porównania w pierwszym komparatorze, jak i w zależności [Author ID1: at Fri Dec 14 10:09:00 2001 ]od relacji między cyframi jedności porównywanych liczb.

Jeżeli w wyniku porównania okaże się, że liczba wejściowa jest większa od wartości progowej, to [Author ID1: at Fri Dec 14 10:10:00 2001

]na wyjściu A [Author ID1: at Fri Dec 14 15:58:00 2001

]> [Author ID1: at Fri Dec 14 15:58:00 2001

]B drugiego komparatora jest „1” logiczna. Pozwala to na przepuszczenie fali generowanej przez bramkę Schmitta. Dzięki temu stan wejść ![]()

obu sterowników zmienia się w takt tej fali, co powoduje pulsowanie wyświetlacza. Jeżeli natomiast liczba wejściowa nie przekracza wartości progowej, na wejściach tych utrzymuje się stan „1”, a więc obie cyfry są wyświetlane. Jedynie w przypadku, gdy liczba wejściowa jest mniejsza od 10, a więc cyfra dziesiątek jest równa 0, wyświetlana jest tylko cyfra jedności. Zapewnia to stan „0” na wejściu ![]()

.

--> Rysunek 2.21.[Author ID1: at Fri Dec 14 10:12:00 2001 ][Author:EK] [Author ID1: at Fri Dec 14 10:13:00 2001 ][Author ID1: at Fri Dec 14 10:12:00 2001 ]

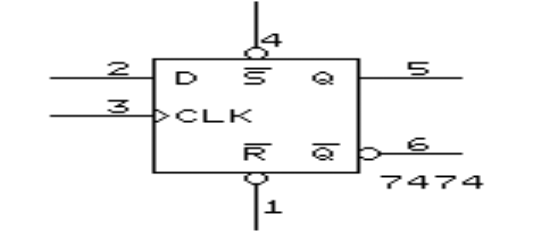

Przykład 2.[Author ID1: at Fri Dec 14 10:13:00 2001 ]

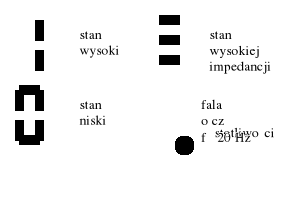

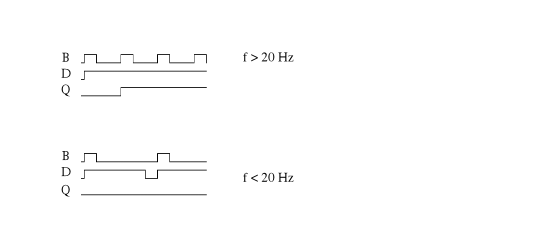

Zaprojektować próbnik stanów logicznych. Sposób wyświetlania stanu badanego sygnału określa rysunek 2.22.[Author ID1: at Fri Dec 14 10:14:00 2001

][Author ID1: at Fri Dec 14 10:14:00 2001

][Author ID1: at Fri Dec 14 10:14:00 2001

][Author ID1: at Fri Dec 14 10:14:00 2001

][Author ID1: at Fri Dec 14 10:14:00 2001

]Rysunek [Author ID1: at Fri Dec 14 10:14:00 2001

]21[Author ID1: at Fri Dec 14 10:14:00 2001

][Author ID1: at Fri Dec 14 10:14:00 2001

].[Author ID1: at Fri Dec 14 10:14:00 2001

]

Rysunek 2.22. [Author ID1: at Fri Dec 14 10:14:00 2001

][Author ID1: at Fri Dec 14 10:14:00 2001

][Author ID1: at Fri Dec 14 10:14:00 2001

][Author ID1: at Fri Dec 14 10:14:00 2001

]21[Author ID1: at Fri Dec 14 10:14:00 2001

][Author ID1: at Fri Dec 14 10:14:00 2001

]. [Author ID1: at Fri Dec 14 10:14:00 2001

]Sposób wyświetlania stanu badanego sygnału

Tranzystor i przyłączone do niego oporniki powinny być dobrane tak, aby w stanie niskim lub w stanie[Author ID1: at Fri Dec 14 10:15:00 2001 ] wysokiej impedancji na wejściu tranzystor był w stanie odcięcia (zatkania). Jeżeli natomiast na wejściu jest stan wysoki, tranzystor powinien przewodzić (być w stanie nasycenia).

--> Rysunek 2.23.[Author ID1: at Fri Dec 14 10:16:00 2001 ][Author:EK] [Author ID1: at Fri Dec 14 10:16:00 2001 ][Author ID1: at Fri Dec 14 10:16:00 2001 ]

Jeżeli na wejściu jest stan niski, tranzystor jest w stanie odcięcia, a więc w punkcie A napięcie jest bliskie napięciu zasilania. Mamy tu więc „1” logiczną. Z kolei w punkcie B jest stan niski, ponieważ bramka 7407 powiela sygnały wejściowe. Na wyjściu bramki NAND jest zatem stan „1”, a wyświetlacz pokazuje cyfrę 0.

W stanie wysokim na wejściu tranzystor przewodzi, a więc w punkcie A jest „0”, natomiast w punkcie B —[Author ID1: at Fri Dec 14 10:17:00 2001

]-[Author ID1: at Fri Dec 14 10:17:00 2001

] „1”. Na wyjściu bramki NAND jest „1”, a wyświetlacz pokazuje cyfrę 1.

Nieco inaczej jest w stanie wysokiej impedancji sygnału wejściowego. Tranzystor wówczas nie przewodzi, gdyż nie płynie prąd bazy. Natomiast bramka 7407 traktuje tę sytuację tak, jak gdyby na wejściu była „1”. W związku z tym w punktach A i B jest stan wysoki. Sterownik 7447 wyłącza wyświetlacz, gdyż na wejściu ![]()

jest „0”. Wyświetlacz pokazuje jednak kombinację odpowiadającą stanowi wysokiej impedancji, a to dzięki temu, że określone jego segmenty podłączone są do wyjść dwóch bramek 7407.

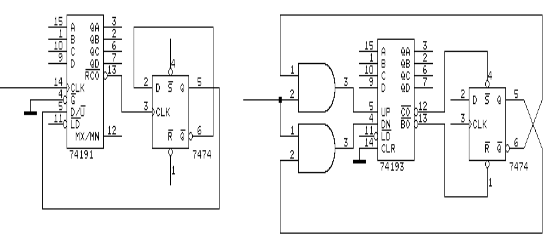

Do wykrycia fali użyty jest tu dodatkowy układ składający się z układu czasowego 74123 oraz przerzutnika synchronicznego typu D (7474). Długość impulsów generowanych przez układ czasowy musi odpowiadać częstotliwości granicznej (w naszym przypadku 20 Hz). Jeżeli częstotliwość wejściowa jest większa od granicznej, układ jest wyzwalany kolejnymi impulsami przed zakończeniem impulsu wyjściowego (rysunek 2.24[Author ID1: at Fri Dec 14 10:22:00 2001

][Author ID1: at Fri Dec 14 10:22:00 2001

][Author ID1: at Fri Dec 14 10:22:00 2001

][Author ID1: at Fri Dec 14 10:22:00 2001

][Author ID1: at Fri Dec 14 10:22:00 2001

]Rysunek [Author ID1: at Fri Dec 14 10:22:00 2001

]22[Author ID1: at Fri Dec 14 10:22:00 2001

][Author ID1: at Fri Dec 14 10:22:00 2001

]). Każde zbocze narastające sygnału wejściowego powoduje zapisanie stanu tego impulsu w przerzutniku. Przy częstotliwości wyższej niż graniczna wyjście Q przerzutnika jest w stanie wysokim, co powoduje świecenie kropki dziesiętnej.

Rysunek 2.24. [Author ID1: at Fri Dec 14 10:22:00 2001

][Author ID1: at Fri Dec 14 10:22:00 2001

][Author ID1: at Fri Dec 14 10:22:00 2001

][Author ID1: at Fri Dec 14 10:22:00 2001

]22[Author ID1: at Fri Dec 14 10:22:00 2001

][Author ID1: at Fri Dec 14 10:22:00 2001

]. [Author ID1: at Fri Dec 14 10:22:00 2001

]Przebiegi czasowe w układzie komparatora częstotliwości

Jeżeli częstotliwość wejściowa jest mniejsza od granicznej, kolejne wyzwolenia układu czasowego występują po zakończeniu impulsu wyjściowego. W chwili wystąpienia zbocza narastającego na wejściu przerzutnika jest zatem „0”, ponieważ układ czasowy rozpoczyna generowanie impulsu z pewnym opóźnieniem w stosunku do chwili wystąpienia zbocza wyzwalającego. Tak więc wyjście Q przerzutnika pozostaje w stanie niskim, a kropka dziesiętna wyświetlacza jest zgaszona.

Przykład 3.[Author ID1: at Fri Dec 14 10:24:00 2001 ]

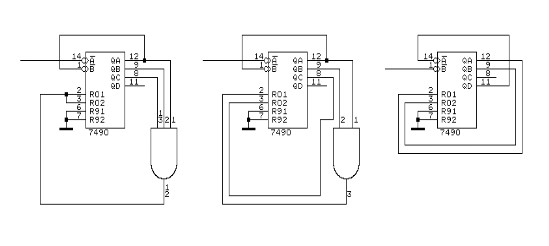

Zaprojektować liczniki asynchroniczne mod 7 liczące w kodzie 8421 i 5421.

Pierwszy układ liczy w kodzie 8421. Wyjście QA jest najmniej znaczące, wejście QD —[Author ID1: at Fri Dec 14 10:29:00 2001

]-[Author ID1: at Fri Dec 14 10:29:00 2001

] najbardziej. Po osiągnięciu przez licznik stanu 7.[Author ID1: at Fri Dec 14 10:30:00 2001

] wytwarzany jest sygnał zerowania licznika. Podobnie działa układ drugi. Jest on jednak mniej stabilny ze względu na różnice czasów propagacji sygnałów zerujących.

Układ trzeci liczy w kodzie 5421. Wyjściem najbardziej znaczącym jest teraz QA, najmniej —[Author ID1: at Fri Dec 14 10:30:00 2001

]-[Author ID1: at Fri Dec 14 10:30:00 2001

] QB. Kod ten pozwala na wykrycie stanu 7.[Author ID1: at Fri Dec 14 10:30:00 2001

] bez użycia dodatkowych elementów.

--> Rysunek 2.25.[Author ID1: at Fri Dec 14 10:31:00 2001 ][Author:EK] [Author ID1: at Fri Dec 14 10:31:00 2001 ][Author ID1: at Fri Dec 14 10:31:00 2001 ]

Przykład 4.[Author ID1: at Fri Dec 14 10:33:00 2001 ]

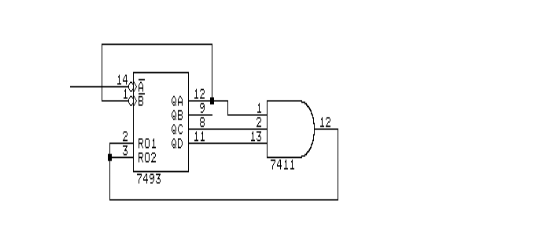

Zaprojektować licznik asynchroniczny mod 13.

--> Rysunek 2.26.[Author ID1: at Fri Dec 14 10:33:00 2001 ][Author:EK] [Author ID1: at Fri Dec 14 10:34:00 2001 ][Author ID1: at Fri Dec 14 10:33:00 2001 ]

Licznik ten działa podobnie,[Author ID1: at Fri Dec 14 10:33:00 2001

] jak pierwszy licznik z poprzedniego przykładu. Wykrycie stanu 13.[Author ID1: at Fri Dec 14 10:33:00 2001

] powoduje wyzerowanie całego licznika.

Przykład 5.[Author ID1: at Fri Dec 14 10:34:00 2001 ]

Zaprojektować licznik asynchroniczny mod 44, nie korzystając z dodatkowych elementów (np. bramek).

--> Rysunek 2.27.[Author ID1: at Fri Dec 14 10:35:00 2001 ][Author:EK] [Author ID1: at Fri Dec 14 10:35:00 2001 ][Author ID0: at Thu Nov 30 00:00:00 1899 ]

Do zbudowania takiego licznika potrzebne są dwa układy. Pierwszy z nich, zliczający cyfry jedności, można potraktować jak dzielnik częstotliwości przez 10. Drugi licznik zatem zlicza cyfry dziesiątek. Wykrycie stanu 44.[Author ID1: at Fri Dec 14 16:00:00 2001 ] wymaga sprawdzenia, czy w obu licznikach jest stan 4. Jeżeli tak, oba liczniki powinny być równocześnie wyzerowane.

Przykład 6.[Author ID1: at Fri Dec 14 10:36:00 2001 ]

Zaprojektować licznik asynchroniczny mod 66, nie korzystając z dodatkowych elementów (np. bramek).

--> Rysunek 2.28.[Author ID1: at Fri Dec 14 10:36:00 2001 ][Author:EK] [Author ID1: at Fri Dec 14 10:37:00 2001 ][Author ID1: at Fri Dec 14 10:36:00 2001 ]

Licznik ten działa podobnie,[Author ID1: at Fri Dec 14 10:37:00 2001

] jak licznik mod 44 z poprzedniego przykładu. Jedyna różnica polega na tym, że pierwszy licznik jest dzielnikiem częstotliwości mod 16. Tak więc wykrycie stanu 66.[Author ID1: at Fri Dec 14 15:31:00 2001

] wymaga sprawdzenia, czy w pierwszym liczniku jest stan 2.[Author ID1: at Fri Dec 14 10:38:00 2001

], a [Author ID1: at Fri Dec 14 10:38:00 2001

]w drugim [Author ID1: at Fri Dec 14 10:38:00 2001

] zaś [Author ID1: at Fri Dec 14 10:38:00 2001

]—[Author ID1: at Fri Dec 14 10:38:00 2001

]-[Author ID1: at Fri Dec 14 10:38:00 2001

] 64. Spełnienie obu tych warunków powoduje jednoczesne wyzerowanie obu liczników.

Przykład 7.[Author ID1: at Fri Dec 14 10:39:00 2001 ]

Zaprojektować licznik mod 5. W zadaniu należy również w[Author ID1: at Sun Dec 16 22:39:00 2001

]W[Author ID1: at Sun Dec 16 22:39:00 2001

]ykorzystać układy liczników synchronicznych z zerowaniem synchronicznym i asynchronicznym.

--> Rysunek 2.29.[Author ID1: at Fri Dec 14 10:39:00 2001 ][Author:EK] [Author ID1: at Fri Dec 14 10:39:00 2001 ][Author ID1: at Fri Dec 14 10:39:00 2001 ]

Układ 74160 jest licznikiem z zerowaniem asynchronicznym. Oznacza to, że wyzerowanie licznika następuje, gdy tylko pojawi się sygnał zerujący, niezależnie od stanu sygnału zegarowego. Dlatego też sposób rozwiązania jest taki sam, jak w przypadku liczników asynchronicznych —[Author ID1: at Fri Dec 14 10:41:00 2001

]-[Author ID1: at Fri Dec 14 10:41:00 2001

] stan wykrywany jest stanem niedozwolonym. W rozpatrywanym przykładzie wystąpienie stanu 5.[Author ID1: at Fri Dec 14 10:41:00 2001

] powoduje natychmiastowe wyzerowanie licznika.

Inaczej jest w przypadku układu 74162, który jest licznikiem z zerowaniem synchronicznym. Tutaj wyzerowanie nastąpi dopiero w chwili wystąpienia narastającego zbocza sygnału zegarowego, o ile sy[Author ID1: at Fri Dec 14 10:41:00 2001

]t[Author ID1: at Fri Dec 14 10:41:00 2001

]gnał zerujący będzie wówczas aktywny. Dlatego też należy wykryć ostatni stan dozwolony —[Author ID1: at Fri Dec 14 10:42:00 2001

]-[Author ID1: at Fri Dec 14 10:42:00 2001

] w tym przypadku 4. Liczniki z zerowaniem synchronicznym mają więc tę zaletę, że nie występują w nich stany niedozwolone. Może to mieć znaczenie, jeżeli wyjście licznika steruje wejściem demultiplek[Author ID1: at Fri Dec 14 10:42:00 2001

]sera.

Przykład 8.[Author ID1: at Fri Dec 14 10:42:00 2001 ]

Zaprojektować licznik synchroniczny zliczający w następujący sposób: 0, ..., A, B, ..., C, 0 itd. gdzie A, B, i C są dowolnymi cyframi szesnastkowymi spełniającymi warunek A [Author ID1: at Fri Dec 14 10:43:00 2001 ]< [Author ID1: at Fri Dec 14 10:43:00 2001 ]B [Author ID1: at Fri Dec 14 10:43:00 2001 ]< [Author ID1: at Fri Dec 14 10:43:00 2001 ]C. Zerowanie i wpis są synchroniczne.

--> Rysunek 2.30.[Author ID1: at Fri Dec 14 10:44:00 2001 ][Author:EK] [Author ID1: at Fri Dec 14 10:44:00 2001 ][Author ID1: at Fri Dec 14 10:44:00 2001 ]

Wyjścia licznika podłączone są do wejść A obu komparatorów 7485. Stan wejść B tych komparatorów może być ustawiany za pomocą przełączników, podobnie jak stan wejść A, B, C i D licznika. Jeżeli pierwszy komparator wykryje równość między zawartością licznika a cyfrą A, uaktywnia poprzez bramkę negacji wejście wpisujące licznika, co powoduje wpisanie do niego cyfry B. Wpis ten nastąpi w chwili wystąpienia zbocza narastającego sygnału zegarowego. Jeżeli następnie drugi komparator wykryje równość między zawartością licznika a cyfrą C, uaktywni poprzez drugą bramkę negacji wejście zerujące. Spowoduje to wyzerowanie licznika, gdy wystąpi zbocze narastające sygnału zegarowego.

Przykład 9.[Author ID1: at Fri Dec 14 10:45:00 2001 ]

Zaprojektować licznik synchroniczny zliczający w następujący sposób: 0, 1, ..., 14, 15, 14, ..., 1, 0, 1 itd. Zerowanie i wpis są asynchroniczne. W zadaniu należy również w[Author ID1: at Sun Dec 16 22:40:00 2001

]W[Author ID1: at Sun Dec 16 22:40:00 2001

]ykorzystać liczniki z wyborem kierunku zliczania oraz z podwójnym wejściem zegarowym.

Układ 74191 zlicza impulsy wejściowe zgodnie ze stanem wejścia ![]()

. Załóżmy początkowo, że na wejściu tym jest „0” i licznik zlicza do góry. Gdy wystąpi stan maksymalny (15), sygnał [Author ID1: at Thu Dec 13 19:33:00 2001

] [Author ID1: at Thu Dec 13 19:33:00 2001

]![]()

przyjmie stan „1” na czas równy okresowi zegara. Zbocze narastające tego sygnału powoduje zanegowanie stanu przerzutnika (wpisanie „1”), dzięki czemu od najbliższego zbocza narastającego sygnału zegarowego licznik będzie zmniejszał zawartość. Dopiero wyzerowanie licznika spowoduje ponowne wygenerowanie sygnału ![]()

i wpisanie do przerzutnika stanu „0”. Wówczas licznik powróci do zliczania do góry.

Zastanówmy się, czy do sterowania pracą przerzutnika można także wykorzystać sygnał ![]()

. Przyjmuje on stan „0” w czasie, gdy ![]()

[Author ID1: at Fri Dec 14 10:48:00 2001

]= [Author ID1: at Fri Dec 14 10:48:00 2001

]1, a sygnał zegarowy CLK [Author ID1: at Fri Dec 14 10:48:00 2001

]= [Author ID1: at Fri Dec 14 10:48:00 2001

]0. Zbocze narastające ![]()

wystąpi zatem równocześnie ze zboczem narastającym sygnału zegarowego. Jest to zbyt późno, aby przerzutnik zdążył się przełączyć na czas. Gdyby istniała konieczność użycia ![]()

zamiast ![]()

, na wejście zegarowe przerzutnika sygnał ten powinien zostać podany poprzez bramkę negacji, co przyspieszy zmianę stanu przerzutnika o pół okresu sygnału zegarowego.

--> Rysunek 2.31.[Author ID1: at Fri Dec 14 10:49:00 2001 ][Author:EK] [Author ID1: at Fri Dec 14 10:49:00 2001 ][Author ID1: at Fri Dec 14 10:49:00 2001 ]

Drugi układ zawiera licznik z osobnymi wejściami zegarowymi dla każdego kierunku zliczania. Początkowo w przerzutniku jest „0”, a więc wejściowe bramki AND przepuszczają sygnały zegarowe tylko do wejścia inkrementującego (UP). Wystąpienie stanu maksymalnego powoduje wygenerowanie sygnału ![]()

powodującego wpisanie do przerzutnika wartości „1”. Teraz do wejść licznika sygnały przepuszczane są tylko do wejścia dekrementującego (DN). Wystąpienie w liczniku stanu „0” powoduje wygenerowanie sygnału ![]()

i ponowne wpisanie „0” do przerzutnika.

Przykład 10.[Author ID1: at Fri Dec 14 10:51:00 2001 ]

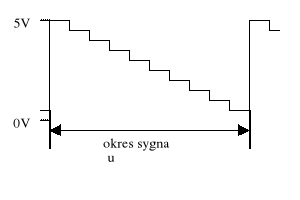

Zaprojektować układ generowania przebiegu schodkowego piłokształtnego, wykorzystując licznik i demultiplekser. Przebieg wyjściowy ilustruje

-->

rysunek 2.32.[Author ID1: at Fri Dec 14 10:55:00 2001

][Author:EK]

[Author ID1: at Fri Dec 14 10:56:00 2001

][Author ID1: at Fri Dec 14 10:55:00 2001

][Author ID1: at Fri Dec 14 10:55:00 2001

][Author ID1: at Fri Dec 14 10:55:00 2001

]Błąd! Nie można odnaleźć źródła odsyłacza.[Author ID1: at Fri Dec 14 10:55:00 2001

][Author ID1: at Fri Dec 14 10:55:00 2001

].[Author ID1: at Fri Dec 14 10:55:00 2001

]

Rysunek [Author ID1: at Fri Dec 14 10:52:00 2001

][Author ID1: at Fri Dec 14 10:52:00 2001

][Author ID1: at Fri Dec 14 10:52:00 2001

]23[Author ID1: at Fri Dec 14 10:52:00 2001

][Author ID1: at Fri Dec 14 10:52:00 2001

].[Author ID1: at Fri Dec 14 10:52:00 2001

] [Author ID1: at Thu Dec 13 19:33:00 2001

]2.32. [Author ID1: at Fri Dec 14 10:52:00 2001

]Przebieg schodkowy piłokształtny

--> Rysunek 2.33. [Author ID1: at Fri Dec 14 10:58:00 2001 ][Author:EK] [Author ID1: at Fri Dec 14 10:59:00 2001 ][Author ID1: at Fri Dec 14 10:58:00 2001 ]

Z rysunku wynika, że najwyższe napięcie wynosi 5 V, a najniższe —[Author ID1: at Fri Dec 14 11:00:00 2001

]-[Author ID1: at Fri Dec 14 11:00:00 2001

] 0,5 V. Kolejne poziomy napięć różnią się o 0,5 V. Do wytworzenia potrzebnych napięć można wykorzystać rezystorowe dzielniki napięcia. Napięcie odniesienia jest różnicą między napięciem zasilania (UCC [Author ID1: at Fri Dec 14 11:00:00 2001

]= [Author ID1: at Fri Dec 14 11:00:00 2001

]5 V) a napięciem wyjściowym w stanie niskim (UOL [Author ID1: at Fri Dec 14 11:01:00 2001

]= [Author ID1: at Fri Dec 14 11:01:00 2001

]0,5 [Author ID1: at Thu Dec 13 19:33:00 2001

] [Author ID1: at Thu Dec 13 19:33:00 2001

]V), wynosi zatem 4,5 V. Przy stałej wartości rezystora R [Author ID1: at Fri Dec 14 11:01:00 2001

]= [Author ID1: at Fri Dec 14 11:01:00 2001

]1 kΩ wartości rezystorów R1 - [Author ID1: at Fri Dec 14 11:01:00 2001

]-[Author ID1: at Fri Dec 14 11:01:00 2001

]R9 powinny być takie, jak podaje

-->

tabela 6.[Author:EK]

[Author ID1: at Sun Dec 16 22:34:00 2001

]

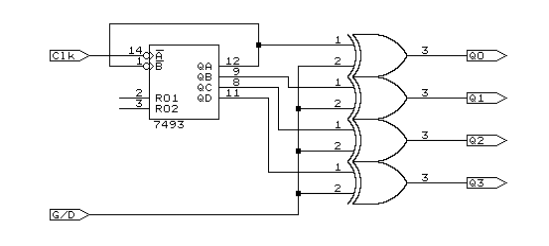

Przykład 11.[Author ID1: at Fri Dec 14 11:02:00 2001 ]

Zaprojektować asynchroniczny licznik dwójkowy dwukierunkowy.

-->

Rysunek 2.34. [Author ID1: at Fri Dec 14 11:03:00 2001

][Author:EK]

[Author ID1: at Fri Dec 14 11:03:00 2001

][Author ID1: at Fri Dec 14 11:03:00 2001

]

Do wyboru kierunku służy dodatkowy sygnał G/D. Stan niski tego sygnału powoduje, że bramki XOR przekazują na wyjścia stany odpowiednich wyjść licznika. Odpowiada to zliczaniu w górę. Gdy natomiast sygnał G/D jest w stanie wysokim, na wyjściach bramek pojawiają się zanegowane stany wyjść licznika. Odpowiada to zliczaniu w dół.

2 Część I ♦ Podstawy obsługi systemu WhizBang (Nagłówek strony)

2 C:\Moje dokumenty\Korekta\Uklady mikro\1 Od autora\r2-1.doc

[Author ID1: at Fri Dec 14 15:40:00 2001 ][Author ID1: at Fri Dec 14 15:40:00 2001 ][Author ID1: at Fri Dec 14 15:40:00 2001 ][Author ID1: at Fri Dec 14 15:40:00 2001 ][Author ID1: at Fri Dec 14 15:40:00 2001 ] W calym tekście w zapisie typu P = Q, P > Q, Y0 [Author ID1: at Fri Dec 14 15:40:00 2001 ]- Y7, A0 [Author ID1: at Fri Dec 14 15:42:00 2001 ]-A2 należy przed i po znakach rowności, większości, mniejszości, półpauzy wstawić spację. Ja nie mogę tego zrobić, ponieważ działania te zostały zamieszczone w tekście na zasadzie rysunków.[Author ID1: at Fri Dec 14 15:43:00 2001 ]

[Author ID1: at Thu Dec 13 22:01:00 2001 ][Author ID1: at Thu Dec 13 22:01:00 2001 ][Author ID1: at Thu Dec 13 22:01:00 2001 ][Author ID1: at Thu Dec 13 22:01:00 2001 ][Author ID1: at Thu Dec 13 22:01:00 2001 ] Może lepiej: W dalszej części książki słowem demultipleksery będą określane wyłącznie dekodery kodu dwójkowego zamieniające kod na [Author ID1: at Thu Dec 13 22:01:00 2001 ]„1 z[Author ID1: at Thu Dec 13 22:03:00 2001 ] n”.[Author ID1: at Thu Dec 13 22:04:00 2001 ]

[Author ID1: at Thu Dec 13 23:06:00 2001 ][Author ID1: at Thu Dec 13 23:06:00 2001 ][Author ID1: at Thu Dec 13 23:06:00 2001 ][Author ID1: at Thu Dec 13 23:06:00 2001 ][Author ID1: at Thu Dec 13 23:06:00 2001 ] Może: do określania?[Author ID1: at Thu Dec 13 23:06:00 2001 ]

[Author ID1: at Thu Dec 13 23:34:00 2001 ][Author ID1: at Thu Dec 13 23:34:00 2001 ][Author ID1: at Thu Dec 13 23:34:00 2001 ][Author ID1: at Thu Dec 13 23:34:00 2001 ][Author ID1: at Thu Dec 13 23:34:00 2001 ] Impulsu czy układu?[Author ID1: at Thu Dec 13 23:34:00 2001 ]

[Author ID1: at Thu Dec 13 23:38:00 2001 ][Author ID1: at Thu Dec 13 23:38:00 2001 ][Author ID1: at Thu Dec 13 23:38:00 2001 ][Author ID1: at Thu Dec 13 23:38:00 2001 ][Author ID1: at Thu Dec 13 23:38:00 2001 ] O ktorym rysunku jest mowa? Na rysunku[Author ID1: at Thu Dec 13 23:38:00 2001 ] 2.8[Author ID1: at Thu Dec 13 23:39:00 2001 ] chyba nie ma [Author ID1: at Thu Dec 13 23:39:00 2001 ]wielu rodz[Author ID1: at Thu Dec 13 23:40:00 2001 ]a[Author ID1: at Thu Dec 13 23:41:00 2001 ]jów kondensatorów.[Author ID1: at Thu Dec 13 23:40:00 2001 ]

[Author ID1: at Thu Dec 13 23:47:00 2001 ][Author ID1: at Thu Dec 13 23:47:00 2001 ][Author ID1: at Thu Dec 13 23:47:00 2001 ][Author ID1: at Thu Dec 13 23:47:00 2001 ][Author ID1: at Thu Dec 13 23:47:00 2001 ] Który rysunek?[Author ID1: at Thu Dec 13 23:47:00 2001 ]

[Author ID1: at Thu Dec 13 23:56:00 2001 ][Author ID1: at Thu Dec 13 23:56:00 2001 ][Author ID1: at Thu Dec 13 23:56:00 2001 ][Author ID1: at Thu Dec 13 23:56:00 2001 ][Author ID1: at Thu Dec 13 23:56:00 2001 ] Gdzie jest ta tabela?[Author ID1: at Thu Dec 13 23:56:00 2001 ]

[Author ID1: at Fri Dec 14 00:18:00 2001 ][Author ID1: at Fri Dec 14 00:18:00 2001 ][Author ID1: at Fri Dec 14 00:18:00 2001 ][Author ID1: at Fri Dec 14 00:18:00 2001 ][Author ID1: at Fri Dec 14 00:18:00 2001 ] ???[Author ID1: at Fri Dec 14 00:18:00 2001 ]

[Author ID1: at Fri Dec 14 00:32:00 2001 ][Author ID1: at Fri Dec 14 00:32:00 2001 ][Author ID1: at Fri Dec 14 00:32:00 2001 ][Author ID1: at Fri Dec 14 00:32:00 2001 ][Author ID1: at Fri Dec 14 00:32:00 2001 ] Gdzie [Author ID1: at Fri Dec 14 00:32:00 2001 ]jest [Author ID1: at Fri Dec 14 00:33:00 2001 ]ta tabela?[Author ID1: at Fri Dec 14 00:32:00 2001 ]

[Author ID1: at Fri Dec 14 09:31:00 2001 ][Author ID1: at Fri Dec 14 09:31:00 2001 ][Author ID1: at Fri Dec 14 09:31:00 2001 ][Author ID1: at Fri Dec 14 09:31:00 2001 ][Author ID1: at Fri Dec 14 09:31:00 2001 ] W której tabeli?[Author ID1: at Fri Dec 14 09:31:00 2001 ]

[Author ID1: at Fri Dec 14 10:13:00 2001 ][Author ID1: at Fri Dec 14 10:13:00 2001 ][Author ID1: at Fri Dec 14 10:13:00 2001 ][Author ID1: at Fri Dec 14 10:13:00 2001 ][Author ID1: at Fri Dec 14 10:13:00 2001 ] Brak podpisu [Author ID1: at Fri Dec 14 10:13:00 2001 ]pod [Author ID1: at Fri Dec 14 10:32:00 2001 ]rysunkiem.[Author ID1: at Fri Dec 14 10:13:00 2001 ] W całej książce należy uzupełnić [Author ID1: at Fri Dec 14 23:55:00 2001 ]brakujące [Author ID1: at Fri Dec 14 23:57:00 2001 ]podpisy[Author ID1: at Fri Dec 14 23:55:00 2001 ] pod rysunkami, ktore tych podpisów nie mają.[Author ID1: at Fri Dec 14 23:57:00 2001 ]

[Author ID1: at Fri Dec 14 10:16:00 2001 ][Author ID1: at Fri Dec 14 10:16:00 2001 ][Author ID1: at Fri Dec 14 10:16:00 2001 ][Author ID1: at Fri Dec 14 10:16:00 2001 ][Author ID1: at Fri Dec 14 10:16:00 2001 ] Brak podpisu [Author ID1: at Fri Dec 14 10:16:00 2001 ]pod [Author ID1: at Fri Dec 14 10:32:00 2001 ]rysunkiem.[Author ID1: at Fri Dec 14 10:16:00 2001 ]

[Author ID1: at Fri Dec 14 10:31:00 2001 ][Author ID1: at Fri Dec 14 10:31:00 2001 ][Author ID1: at Fri Dec 14 10:31:00 2001 ][Author ID1: at Fri Dec 14 10:31:00 2001 ][Author ID1: at Fri Dec 14 10:31:00 2001 ] Brak podpisu [Author ID1: at Fri Dec 14 10:31:00 2001 ]pod [Author ID1: at Fri Dec 14 10:32:00 2001 ]rysunkiem.[Author ID1: at Fri Dec 14 10:31:00 2001 ]

[Author ID1: at Fri Dec 14 10:34:00 2001 ][Author ID1: at Fri Dec 14 10:34:00 2001 ][Author ID1: at Fri Dec 14 10:34:00 2001 ][Author ID1: at Fri Dec 14 10:34:00 2001 ][Author ID1: at Fri Dec 14 10:34:00 2001 ] Brak podpisu [Author ID1: at Fri Dec 14 10:34:00 2001 ]pod rysunkiem.[Author ID1: at Fri Dec 14 10:34:00 2001 ]

[Author ID1: at Fri Dec 14 10:35:00 2001 ][Author ID1: at Fri Dec 14 10:35:00 2001 ][Author ID1: at Fri Dec 14 10:35:00 2001 ][Author ID1: at Fri Dec 14 10:35:00 2001 ][Author ID1: at Fri Dec 14 10:35:00 2001 ] Brak podpisu pod rysunkiem.[Author ID1: at Fri Dec 14 10:35:00 2001 ]

[Author ID1: at Fri Dec 14 10:37:00 2001 ][Author ID1: at Fri Dec 14 10:37:00 2001 ][Author ID1: at Fri Dec 14 10:37:00 2001 ][Author ID1: at Fri Dec 14 10:37:00 2001 ][Author ID1: at Fri Dec 14 10:37:00 2001 ] Brak podpisu pod rysunkiem.[Author ID1: at Fri Dec 14 10:37:00 2001 ]

[Author ID1: at Fri Dec 14 10:39:00 2001 ][Author ID1: at Fri Dec 14 10:39:00 2001 ][Author ID1: at Fri Dec 14 10:39:00 2001 ][Author ID1: at Fri Dec 14 10:39:00 2001 ][Author ID1: at Fri Dec 14 10:39:00 2001 ] Brak podpisu pod rysunkiem.[Author ID1: at Fri Dec 14 10:39:00 2001 ]

[Author ID1: at Fri Dec 14 10:44:00 2001 ][Author ID1: at Fri Dec 14 10:44:00 2001 ][Author ID1: at Fri Dec 14 10:44:00 2001 ][Author ID1: at Fri Dec 14 10:44:00 2001 ][Author ID1: at Fri Dec 14 10:44:00 2001 ] Brak podpisu pod rysunkiem.[Author ID1: at Fri Dec 14 10:44:00 2001 ]