24 (56)

|

12 |

1 |

0 |

0 |

|

13 |

1 |

0 |

1 |

|

14 |

1 |

1 |

0 |

|

15 |

1 |

1 |

1 |

Tab 7 Tablica kodu 4-bit owego licznika binarnego. SUMATORY

Dodawanie liczb binarnych odbywa się w urządzeniach nazywanych arytmometrami (sumatorami) Podstawowym problemem w projektowaniu arytmometrów (wpływający w istotny sposób na czas realizacji dodawania), jest uwzględnienie przeniesienia wytworzonego przy pozycyjnym sumowaniu liczb. Rozważmy jednak najpierw sumowanie pozycyjne bez uwzględnienia przeniesienia (tab 8).

|

Xn |

Yn |

Sn |

Cn+l |

|

0 |

0 |

0 |

0 |

|

0 |

1 |

1 |

0 |

|

1 |

0 |

1 |

0 |

|

1 |

1 |

0 |

1 |

o

Xn, Yn - są bitami na pozycjach o wadze 2" w' sumowanych liczbach,

Sn - jest bitem na pozycji 2" będącym rezultatem sumowania,

Cn+l - jest przeniesieniem na pozycję 2“‘‘

Zgodnie z tab 8 funkcje opisujące sumę pozycyjną (Sn) oraz przeniesienie (Cn+l) można zapisać w postaci:

s. -X,®Y.=x;y„ + X,,Y, C.łl = X„Y„ gdzie: © - suma modulo 2.

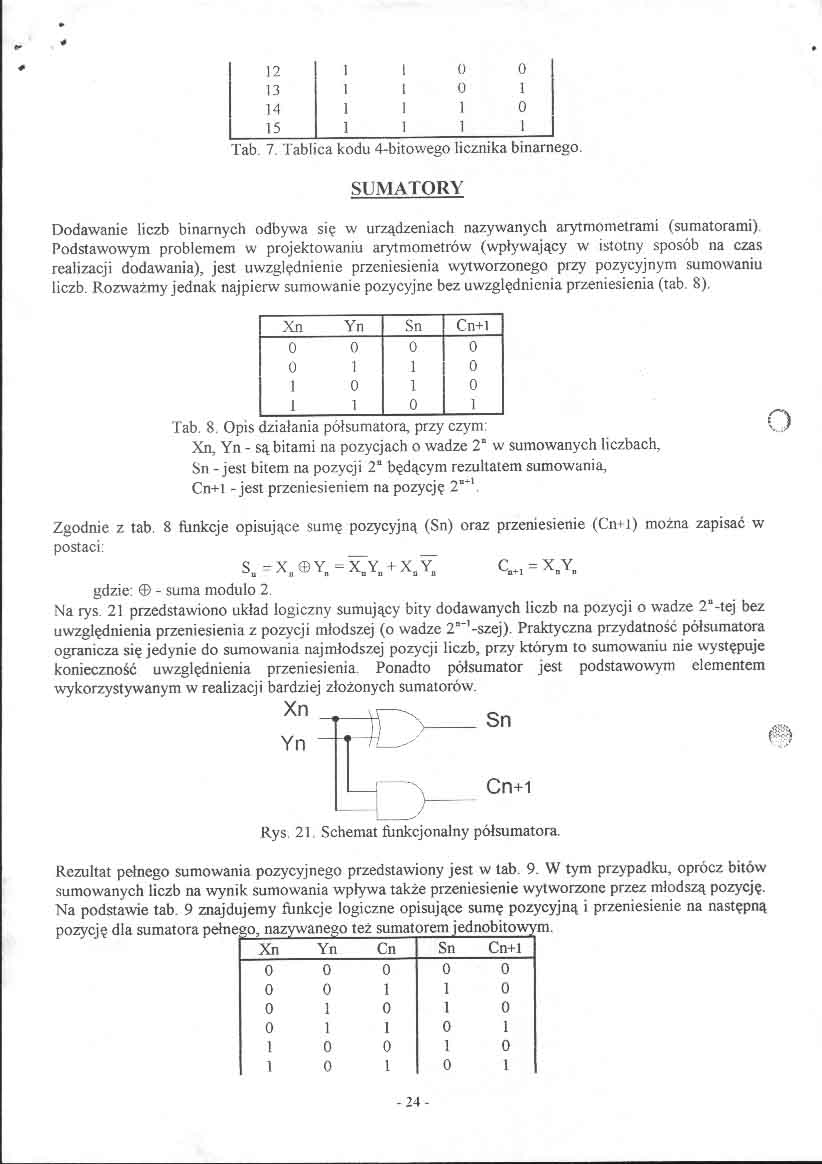

Na rys. 21 przedstawiono układ logiczny sumujący bity dodawanych liczb na pozycji o wadze 2“-tej bez uwzględnienia przeniesienia z pozycji młodszej (o wadze 2B"'-szej). Praktyczna przydatność półsumatora ogranicza się jedynie do sumowania najmłodszej pozycji liczb, przy którym to sumowaniu nie występuje konieczność uwzględnienia przeniesienia Ponadto półsumator jest podstawowym elementem wykorzystywanym w realizacji bardziej złożonych sumatorów.

|

1 \ |

Sn |

|

_JJ / —pi, |

Cn+1 |

Xn

Yn

m

Rys 21 Schemat funkcjonalny półsumatora.

Rezultat pełnego sumowania pozycyjnego przedstawiony jest w tab 9. W tym przypadku, oprócz bitów sumowanych liczb na wynik sumowania wypływa także przeniesienie wytworzone przez młodszą pozycję. Na podstawie tab 9 znajdujemy funkcje logiczne opisujące sumę pozycyjną i przeniesienie na następną

|

Xn |

Yn |

Cn |

Sn |

Cn+l |

|

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

1 |

0 |

|

0 |

1 |

0 |

1 |

0 |

|

0 |

1 |

1 |

0 |

1 |

|

1 |

0 |

0 |

1 |

0 |

|

1 |

0 |

l |

0 |

1 |

-24 -

Wyszukiwarka

Podobne podstrony:

24 (56) 12 1 0 0 13 1 0 1 14 1 1 0 15 1 1 1 Tab 7 Tablica kodu 4-bit owego licznika

24 (57) 12 1 0 0 13 1 0 1 14 1 1 0 15 1 1 1 Tab 7 Tablica kodu 4-bit owego licznika

kalendarz 11?lla styczeń 7 M 10 11 12 13 14 15 16 17 18 19 20 21 2^23 24 25 26 27 28 29 30

KALENDARZ 11 (7) January M Tu W Th Fr Sa Su 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20

Kuroko no Basket full 1355501 ATSUSHIMURASAKIBARA SEIJURO AKASHI 12 3 4 5 6 7 8 9 10 11 12 13 1

dzien europy plakat MAY 2012 S M r w T F sEUROPY - , 1 2 3 4 5 13 L,! 9 to u 12 13 14 15 16 17 18 ig

1 1 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 Styczeń

_ JANUARY, __ 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 CM CM CM o CM 23 24 1 Fizyka Ogólna 3w+2c

10 pazdziernik 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 f

3 H10, 11 12 13 14 15 16, 17’•! 19, 20. 21, <2. 23. 24 J 23 J

S 8 10 11 12 23 24 la 16 13 14 15 i i 16 17 25 13a 14 a 15a 16a 17a 26 18

DAMA W SWETRZE 9 10 08 28 Sweter dla dziewczynki 21-22-23-24-25 20-21-22-23-24 16-17-18-19-20 12-13

rys5 5 6 ’ 7 8 9 1011 12 13 14 15 16 17 18 19 1021 22 23 24 25 26 27 28 29 0331 32 33 34 35 36 37 38

więcej podobnych podstron